adc采样是12bits 3Gsps,采用jmode0模式,分8路serdes传给fpga。fpga内部时钟是150MHz,依据jmode0映射图案所以分成20路并行数据。

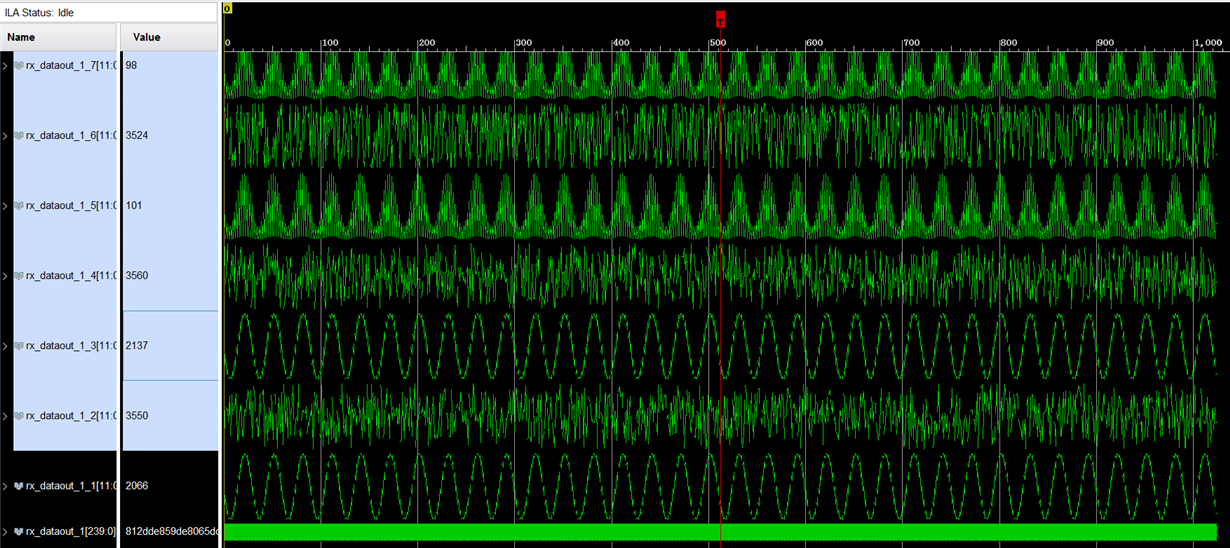

现在adc测试输入是一cw波,fpga通过vivado抓数分析,对于20路并行数据,我理解每一路都应该是cw波,但实际抓取的数据只有前几路的几路是正常的。

不知道错误在哪儿,是按照demoXilinx KCU105 + ADC12DJ3200 JMODE0/JMODE2 Design Firmware里的工程来做的,有遇到过这种情况的么