大家好,我需要用C6748 EMIF 16bit宽度 从FPGA拿数据,需要40MB/S 带宽

CS用4 BANK

以下是我配置代码

void PSCInit(void)

{

// 使能 GPIO 模块

PSCModuleControl(SOC_PSC_1_REGS, HW_PSC_GPIO, PSC_POWERDOMAIN_ALWAYS_ON, PSC_MDCTL_NEXT_ENABLE);

// 使能 EMIFA 模块

PSCModuleControl(SOC_PSC_0_REGS, HW_PSC_EMIFA, PSC_POWERDOMAIN_ALWAYS_ON, PSC_MDCTL_NEXT_ENABLE);

}

void EMIFAInit(void)

{

// 配置 EMIFA 相关复用引脚

//AD7606PinMuxSetup();

// 配置数据总线 16bit

EMIFAAsyncDevDataBusWidthSelect(SOC_EMIFA_0_REGS,EMIFA_CHIP_SELECT_4, EMIFA_DATA_BUSWITTH_16BIT);

// 选择 Normal 模式

EMIFAAsyncDevOpModeSelect(SOC_EMIFA_0_REGS,EMIFA_CHIP_SELECT_4, EMIFA_ASYNC_INTERFACE_NORMAL_MODE);

// 禁止WAIT引脚

EMIFAExtendedWaitConfig(SOC_EMIFA_0_REGS,EMIFA_CHIP_SELECT_4, EMIFA_EXTENDED_WAIT_DISABLE);

// 配置 W_SETUP/R_SETUP W_STROBE/R_STROBE W_HOLD/R_HOLD TA 等参数

EMIFAWaitTimingConfig(SOC_EMIFA_0_REGS,EMIFA_CHIP_SELECT_4, EMIFA_ASYNC_WAITTIME_CONFIG(1, 2 , 1, 1, 2, 1, 0 ));

}

main

{ PSCInit();

EMIFAInit();

while(1)

{emif_rbuffer[0] = ((short *)SOC_EMIFA_CS4_ADDR)[0];

}

}

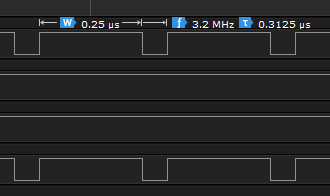

通过逻辑分析仪看 RD 和CS4的波形,如下:

RD和CS 频率是3.2MHz, x 16bit = 6.4MB/s,不足以满足要求

我看到可以使用 EDMA的方式来对EMIF进行操作,总带宽可以到40MB/S

请问有相关的例程可以参考吗?谢谢