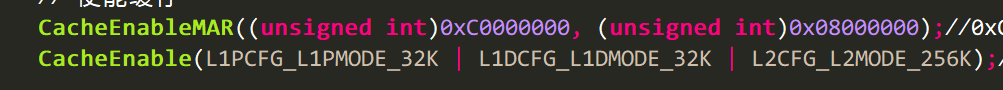

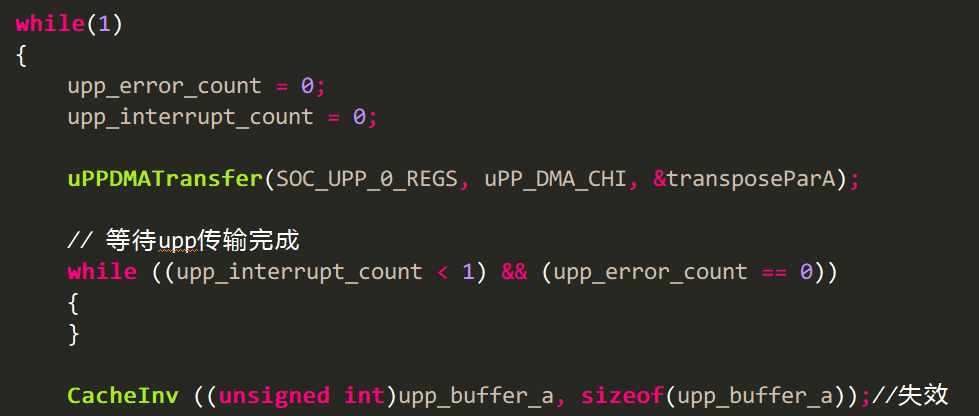

背景:FPGA控制四路ADC采集数据(16bit),采样率128k,数据经过FPGA时加入高16位的标识符标记其来源,32位的数据通过UPP传输给DSP,此时DSP的UPP内置DMA设置为8bit接收模式(I通道),upp外部时钟为12MHz,将L1、L2、DDR2都设置为缓存,缓存窗buffer设置为1280byte × 6行,line_offset为1280byte

问题:

根据DSP计算结果来看,参与DSP计算的数据严重滞后于ADC采集到的数据。(如定位时,目标耗时3s从12点钟方向移动到1点钟方向,DSP结果的变化趋势与目标一致,但是该趋势耗费的时间可能为1min),觉得应该是缓存的数据更新没跟上,怎么才能保证DSP每次参与计算的数据都是最新的呢?(每个循环都启动DMA传输)