在为下一代服务器和交换机实现从10G到25G系统的转换时,硬件设计工程师们必须满足以下这些目标:尽可能降低数据延迟、保持或减小功耗、以及尽可能地降低成本。为了给数据中心用户提供世界一流的具有成本优势产品,从根本上来说,必须用小的成本来多做事。

以下是5个小窍门,它能使你在设计25G系统时做出很好的平衡:

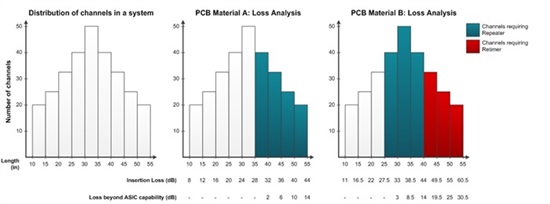

1.确定系统中的哪条链路将会需要信号调节;这将取决于走线长度和印刷电路板 (PCB) 材质。低损耗材料需要较少的信号调节,不过它们的价格也比标准材料要贵。损耗大于专门用途集成电路 (ASIC) 的内在补偿功能的通道将需要某种形式的信号调节。例如,如果你的ASIC能够实现30dB的补偿,你就有可能希望为损耗达到27dB或以上的通道增加信号调节,而其中的3dB差异可以作为安全裕量。

图1是一个PCB材料A和B之间的通道损耗预算分析比较示例图。

图1:一个系统内通道的示例分布,假定ASIC损耗补偿能力:12.9GHz时为30dB,PCB材料A损耗:12.9GHz时为每英寸0.8dB,PCB材料B损耗:12.9GHz时为每英寸1.1dB。

2.对于那些需要信号调节的通道,用小型封装实现设计灵活性。小型封装提供高通道密度,并且使你能够使用重定时器或引脚兼容中继器。

3.设计一个适应重定时器或中继器需要的电源解决方案。例如,TPS53513同步降压转换器能够提供8A电流,已足够一组6个重定时器或中继器的用电需要。

4.确定SMBus寻址机制,这个机制需要对电路板上的每个重定时器/中继器器件进行单独寻址。你可以用每个器件进行引脚配置选择16个唯一SMBus地址中的一个。如果一块电路板上有超过16个器件,可以考虑使用一个诸如TCA/PCA系列I2C/SMBus开关的I2C扩展器来将这个SMBus分为多个总线。

5.在电路板上放置一个单个低成本25MHz (±100ppm) 2.5V单端时钟,以支持多达20个重定时器器件。由于它不用于恢复数据,所以这个时钟没有任何抖动需要。这个重定时器将接收时钟用于计时,对其进行缓冲,并且将其复制在一个输出引脚上,以便轻松级联到下一个重定时器。无需用到多个晶振或扇出缓冲器。如果你最终决定使用中继器,而不是重定时器的话,那么你可以选择不组装这个组件来降低成本。

为了使以上这些技巧在实现起来更加简单,TI已经引入了业内首款引脚兼容中继器 (DS280BR810) 和重定时器 (DS250DF810) 解决方案产品组合,以实现25G背板和前端口应用。而这些是如何帮助实现功耗、性能和成本之间的平衡呢?这一切都与设计简便性和灵活性相关。

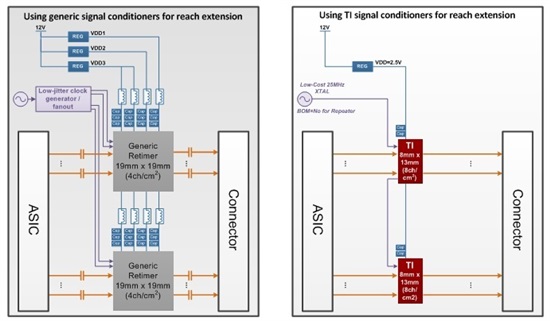

TI的引脚兼容中继器和重定时器解决方案使你能够在尽可能减小延迟和降低物料清单 (BOM) 成本的同时,选择一款满足你性能目标的解决方案。硬件工程师知道,周围元件的成本、尺寸和复杂度与中继器或重定时器本身同样重要。可以考虑一下图2中的电路板设计示例。

图2:图示一个TI解决方案(右侧)相对于一个普通解决方案(左侧)的简便性和节约的成本

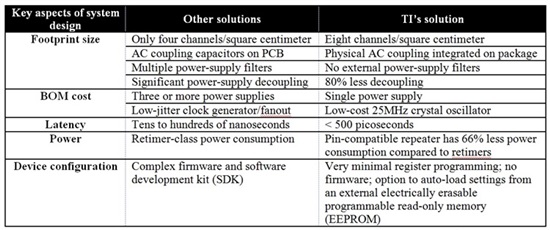

表1:TI的25G信号调节解决方案与其它解决方案间的比较

TI的25G DS280BR810中继器和DS250DF810重定时器解决方案的引脚兼容属性使你能够生成一个电路原理图,以评估这两个选项,从而实现针对最终产品的成本、功耗、和性能优化。信号完整性工程师们能够用中继器解决方案来开始测试,这个解决方案提供更低成本和功耗。如果系统中的抖动和串扰需要更高性能,那么它们可以升级到一个引脚兼容重定时器解决方案。

小的优化确实很重要。可以想象一个典型的、有20000台服务器的数据中心。使用中继器,而不使用重定时器能够使一个服务器网络接口卡 (NIC) 节省大约1W的功耗,累加在一起每年节省的电费超过21000美元(每度电0.12美元),这其中还不包括所节省的冷却方面的开销。如果你将BOM的元件成本减少5美元,就能多节省100000美元。最后,50ns延迟与500ps延迟之间的差异在于,满足整个数据中心服务请求的同时,每天会“浪费”8个小时的时间(假定每秒有2000个请求,每天每台服务器的总使用时间为4小时)。

通过使用以上这些技巧,你应该能够设计出一款在成本、功耗和性能之间做出很好平衡的电路板。

其它资源

- 进一步了解TI的信号调节产品

- 查看DS280BR810数据手册

- 查看DS250DF810数据手册

- 用TI WEBENCH接口设计工具来简化设计

- 观看TI 25G重定时器和中继器产品的视频演示

- 下载TI的100GbE QSFP28参考设计