作者:Wanda Wang 华南区模拟工程师

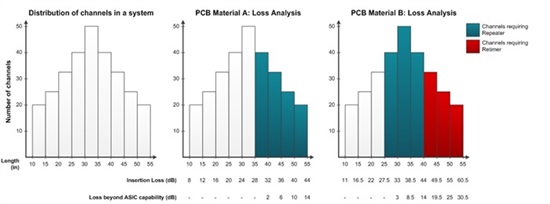

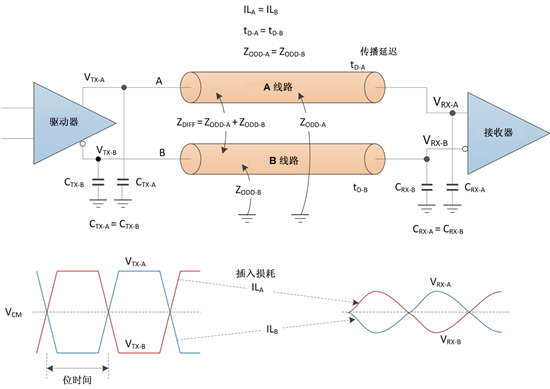

在高速信号电路设计中,TI的信号调理产品被广泛使用。其中retimer类产品涉及到寄存器配置,因此相比较而言,它的使用最为复杂。本文将以DS125DF1610为例,具体讲解retimer类产品的电路设计与寄存器配置。

下图是DS125DF1610产品资料中的典型应用图。

硬件电路设计可以概括为四个关键部分:

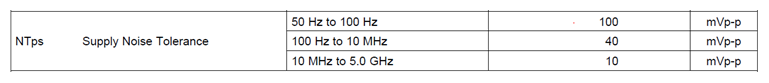

1. 电源:TI的retimer产品供电方式都非常简单,一般只需2.5V单电源,像DS125DF111还可以支持单3.3V供电。从下表可以看到,retimer对电源噪声性能要求不高,通常情况下可以采用DC/DC电源方案,在供电管脚增加适当的滤波电容即可。

另外,电源选型时还需要注意功耗问题,在芯片资料中都会给出各种功能组合下的功耗,那么我们就可以根据实际应用计算出最大的功耗…