在分布式网络中,由于网络传输时延的不确定性,导致采用网络命令触发的同步精度差;同时,由于分布式网络各节点位置的分散性,不适合采用各节点硬件同步提供高精度的同步触发。基于时间信息的同步触发方式特别适合于分布式远距离同步系统,其触发方式灵活,不受距离的限制。

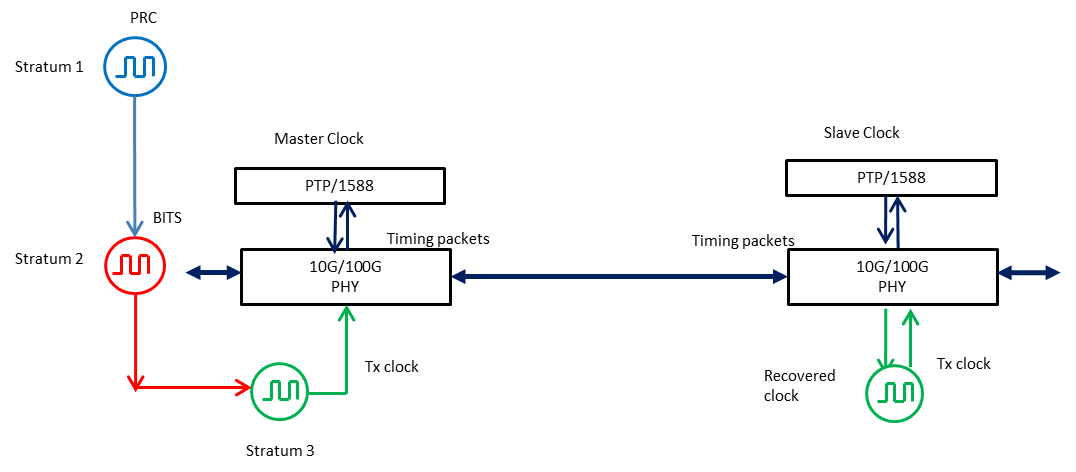

同步以太网是一种采用以太网链路码流恢复时钟的技术, 简称SyncE。同步以太网通过从串行数据码流中恢复出发送端的时钟,从而实现网络时钟同步。但SyncE不能提供时间同步。IEEE1588v2是统一提供时间同步和频率同步的方法,能适合于不同传送平台的时频传送,既可以基于1588v2的时间戳以基于分组的时间传送(TOP)方式单向传递频率,也可使用IEEE1588v2的协议实现时间同步。IEEE1588v2时间同步的核心思想是采用主从时钟方式,对时间信息进行编码,利用网络的对称性和延时测量技术,通过报文消息的双向交互实现主从时间的同步。

同步网络的时钟传递系统

线卡时钟方案必须能自动选择合适的参考时钟输入,尽可能地平滑地进行主备时钟切换以避免引起输出时钟瞬态跳变。同时,时钟必须满足线卡各种工作模式下对时钟抖动jitter的要求,以保证业务链路的误码率。

线卡的频率控制电路会基于优先级,选取线卡的主参考频率;如果主参考频率故障,线卡频率控制电路会切换到备参考频率。主参考频率和备参考频率之间的相差可能在时钟的输出端造成相位瞬时突变而影响系统性能,例如误码率升高,因此系统对参考频率切换过程照成的频率输出相位抖动变化率要求极为严格。比如:SONET规定频率输出相位的峰对峰值最大变动幅度必须小于GR-1244-CORE指定的最大时间间隔误差 MTIE。

除此之外,系统还要求线卡在输入参考频率发生故障时,能手动或自动在主参考输入频率和备参考频率之间进行切换。自动切换可以包含复原功能,此时系统会在主参考频率出现故障时切换到备参考频率,等到主参考频率恢复正常后再切换回主参考频率。自动切换也可以不包含复原功能,此时系统从主参考频率切换到备参考频率后,就算主参考频率恢复正常也会继续使用备参考频率。

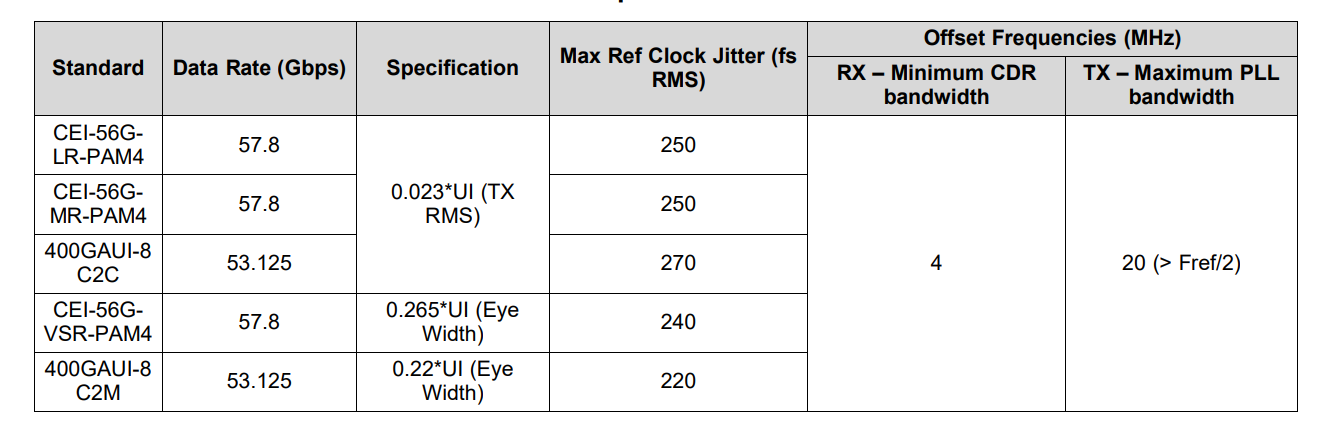

下表列出了56G PAM-4链路中针对不同走线和电缆长度的参考时钟需求。可以看到,56G PAM-4 SerDes的交换机ASIC供应商要求在12 kHz至20 MHz的频带内最大参考时钟抖动为150 fs RMS。

串行链路中的总允许抖动由IEEE协议或CEI协议决定。 例如,IEEE 802.3bs在400GAUI-8中规定,对于芯片到芯片(C2C)数据传输,最大发送抖动(RMS)应不大于0.023UI,这相当于链路总抖动为865 fs RMS。通常分配到时钟模块的抖动很低,对于SNR通常较低的PAM-4系统,甚至可低至10%总抖动。 因此,对于10%时钟抖动预算,允许的参考时钟抖动为270 fs RMS。

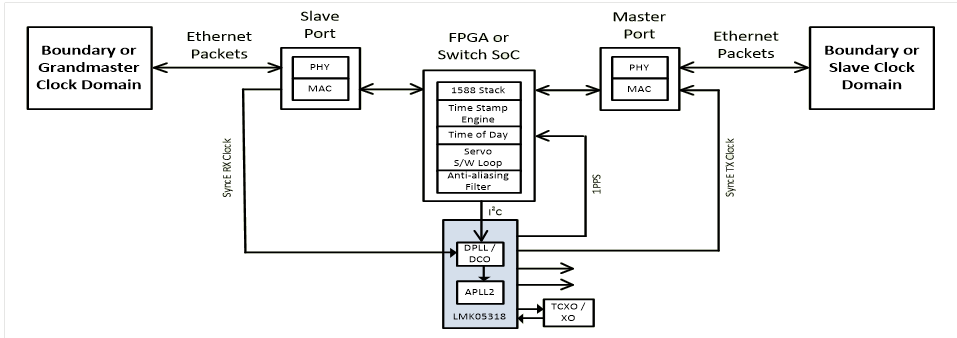

TI的LMK05318 是一款高性能网络同步器时钟器件,提供抖动消除、时钟生成、先进的时钟监控和卓越的无中断切换性能,可满足通信基础设施的严格计时要求。该器件可使用 TI 专有的体声波 (BAW) VCO 技术生成具有 50fs RMS 抖动的输出时钟,而不受 XO 和基准输入的抖动和频率的影响。DPLL 支持抖动和漂移衰减的可编程环路带宽,而两个 APLL 支持分频率转换,从而可以实现灵活的时钟生成。DPLL 支持的同步选项包括采用相位消除的无中断切换、数字保持和频率阶跃小于 0.001ppb(十亿分之一)的 DCO 模式,从而实现精确的时钟控制(IEEE 1588 PTP 从运行)。DPLL 可以锁相到 1 PPS(每秒脉冲数)基准输入,并且在一个输出上支持可选零延迟模式,以实现具有可编程失调电压的确定性输入到输出相位校准。先进的基准输入监控块可确保稳健的时钟故障检测并在发生基准缺失 (LOR) 时帮助将输出时钟干扰降至最低。

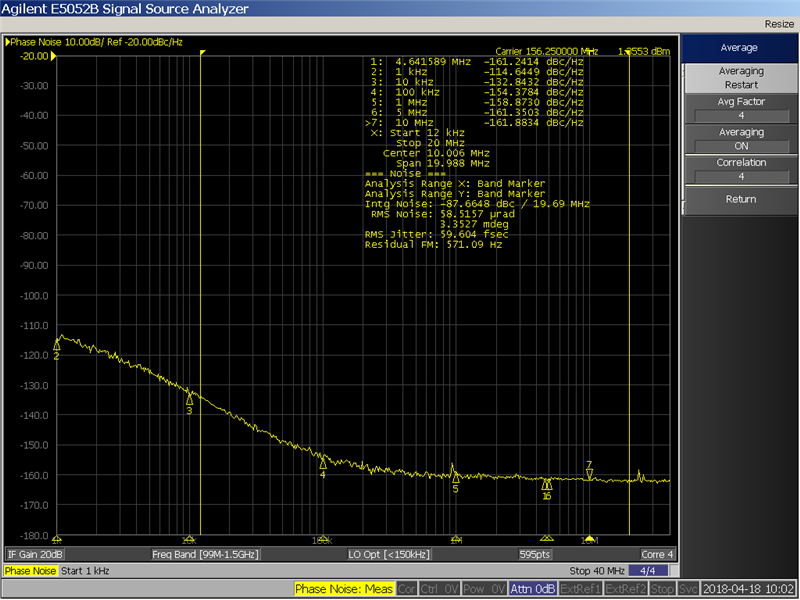

下图是LMK045318 输出相位噪声,时钟输出频点156.25MHZ,在(12KHz~20MHz)积分区间,均值抖动是59fs,PLL1 2.5GHz BAW。Jitter性能能很好地满足高速线卡时钟方案的抖动需求。

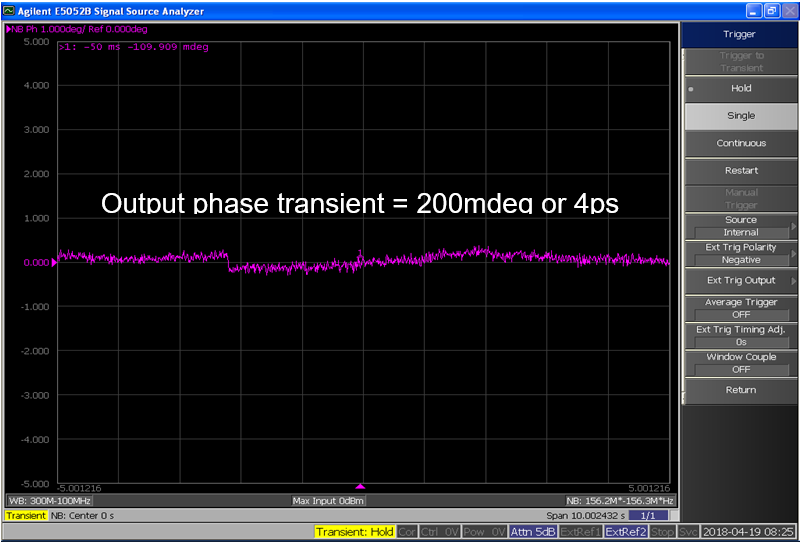

采用相位对消功能,LMK05318具有行业领先的±50ps相位瞬态切换。下图是156.25MHz时钟输出,手动强制从主参考切换到备参考时的切换性能。可以看到完全符合ITU-T G.8262要求。

用于 IEEE1588 和同步以太网的德州仪器的DPLL(数字 PLL)芯片LMK05318专为实现整个分组交换网络中的同步化而设计。对于 IEEE1588 应用,可将嵌入式 DCO(数控振荡器)用作低抖动合成器来完成 IEEE1588 时钟恢复算法。对于同步以太网应用,DPLL 符合EEC(同步以太网设备时钟)的ITU-T建议;这些器件还符合SONET/SDH同步要求。TI的DPLL可在IEEE1588 DCO与 SyncE 模式之间切换,并提供了下列功能:可选环路滤波器、延迟、不中断参考切换、相位斜率限制和时钟冗余。这些特点大大简化同步网络业务线卡时钟的设计。

- LMK05318 datasheet http://www.ti.com/product/LMK05318/description

- Supported Synchronization Modes With LMK05318 http://www.ti.com/lit/an/snaa324/snaa324.pdf

- 同步网络中的高性能线卡时钟解决方案http://www.ti.com.cn/cn/lit/an/zhca493/zhca493.pdf

- Clocking High-Speed 56G PAM-4 Serial Links With LMK05318http://www.ti.com/lit/an/snaa325/snaa325.pdf

- 2.5G和10G线路卡设计的频率讯号管理http://www.dzsc.com/data/2007-4-30/26605.html

-

欢迎登录进行评论