# Serial Boot Loader For CC2530 SoC

**Document Number: SWRA-TBD**

Version 1.1

# TABLE OF CONTENTS

| 1.         | PURPOSE                                                                                                                                                         | 4      |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| 2.         | FUNCTIONAL OVERVIEW                                                                                                                                             | 4      |

| 3.         | ASSUMPTIONS                                                                                                                                                     | 4      |

| 4.         | DEFINITIONS, ABBREVIATIONS, ACRONYMS                                                                                                                            | 4      |

| 5.         | REFERENCES                                                                                                                                                      | 4      |

| 6.         | REVISION HISTORY                                                                                                                                                | 4      |

| 7.         | DESIGN CONSTRAINTS                                                                                                                                              | 5      |

|            | 7.1       External Constraints / Features         7.2       Internal Constraints / Requirements                                                                 |        |

| 8.         | DESIGN                                                                                                                                                          | 5      |

|            | 3.1       SBL CONTEXT                                                                                                                                           | 5<br>5 |

| 9.         | PRODUCING SBL BOOT CODE TO BE PROGRAMMED.                                                                                                                       |        |

|            | 9.1 SEPARATE BUILD & DEBUG OF BOOT CODE                                                                                                                         |        |

| 10.        |                                                                                                                                                                 |        |

| 1          | 10.1 CONFIGURE LINKER OPTIONS FOR THE SBL FUNCTIONALITY.                                                                                                        |        |

|            | <ul> <li>10.1.1 Configure the linker to generate extra output.</li> <li>10.1.2 Configure the linker extra output file format.</li> </ul>                        |        |

|            | <ul> <li>10.1.2 Configure the linker extra output file format</li> <li>10.1.3 Configure the linker command file for SBL-compatible mapping</li> </ul>           |        |

| 1          | 10.2 CONFIGURE BUILD ACTIONS TO INVOKE THE POST-PROCESSING TOOL.                                                                                                |        |

| 1          | 10.3 ADD THE CRC SHADOW TO THE BUILD.                                                                                                                           |        |

| 1          | 10.4 BUILDING THE APPLICATION CODE FOR SBL                                                                                                                      |        |

| 1          | 10.5 DEBUGGING THE APPLICATION CODE WITH SBL.                                                                                                                   |        |

|            | 10.5.1       Preserve the SBL.         10.5.2       Force the CRC Shadow.                                                                                       |        |

|            |                                                                                                                                                                 |        |

| 11.<br>12. |                                                                                                                                                                 |        |

| 1          | 12.1 BUILD THE APPLICATION CODE HEX IMAGE.                                                                                                                      |        |

|            | 12.1.1 Configure the linker to generate Intel-hex output.                                                                                                       |        |

|            | <ul> <li>12.1.2 Generate output compatible for the SmartRF Programmer tool.</li> <li>12.1.3 Re-build the Application Code to generate the .hex file.</li> </ul> |        |

| 1          | 12.1.3       Re-build the Application Code to generate the .hex file         12.2       PRE-PEND THE BOOT CODE HEX IMAGE TO THE APPLICATION CODE HEX IMAGE      |        |

|            |                                                                                                                                                                 | -      |

# TABLE OF FIGURES

| Figure 1: Architectural Placement of the SBL & SBL-compatible Z-Stack image    | 6  |

|--------------------------------------------------------------------------------|----|

| Figure 2: Configuring the linker to generate an extra output file              | 7  |

| Figure 3: Configuring the linker extra output file format                      | 8  |

| Figure 4: Changing the linker command file to implement SBL-compatible mapping | 9  |

| Figure 5: Configuring the build actions to invoke the post-processing tool     | 10 |

| Figure 6: Preserving boot code while debugging                                 | 11 |

| Figure 7: Configuring the linker to generate Intel-hex output.                 | 14 |

| Figure 8: Enabling –M option for SmartRF Programmer tool                       | 15 |

# 1. Purpose

The purpose is to provide a developer's guide to implement SBL compatibility in any sample or proprietary Z-Stack Application for the CC2530 SoC.

#### 2. Functional Overview

SBL is provided as a value-enhancing sample solution that enables the updating of code in devices without the cost of maintaining any download-related code in the user application other than ensuring a compatible flash memory mapping of the final output. SBL is effected as a managed client-server mechanism which requires a serial master to drive the process (i.e. a PC GUI application with access to the serial connection to the CC2530.)

#### 3. Assumptions

SBL is a generic feature that should deviate as little as possible from one implementation to another by only supporting the idiosyncrasies of the specific medium (e.g. USB) crucial to the level of service necessary to complete a code image download in a reasonable amount of time. For the sake of example only, the USB SBL specific references will be made in this document, although merely changing the medium-specific verbiage and paths should allow this document to sufficiently describe any Z-Stack SBL.

# 4. Definitions, Abbreviations, Acronyms

| Term | Definition                                                     |

|------|----------------------------------------------------------------|

| PC   | Personal Computer                                              |

| NV   | Non-volatile (e.g. memory that persists through power cycles.) |

| SBL  | Serial Boot Load(er)                                           |

#### 5. References

[1] Z-Stack Developer's Guide (SWRA176)

# 6. Revision History

| Date       | Writer's name | Document<br>Version | Description of changes                                 |  |  |  |  |  |

|------------|---------------|---------------------|--------------------------------------------------------|--|--|--|--|--|

| 05/20/09   | S Löhr        | 1.0                 | w document – used "OAD for CC2430" as a template.      |  |  |  |  |  |

| 03/18/2010 | S Löhr        | 1.1                 | Update according to latest SBL behavior from Bug 3204. |  |  |  |  |  |

|            |               |                     |                                                        |  |  |  |  |  |

|            |               |                     |                                                        |  |  |  |  |  |

# 7. Design Constraints

#### 7.1 External Constraints / Features

- 1. A serial bus master must drive the download across the serial bus to the CC2530 the means by which to design or implement such an application is beyond the scope of this document.

- 2. The Boot Code requires at least the first flash page so that it can intercept the startup vector.

# 7.2 Internal Constraints / Requirements

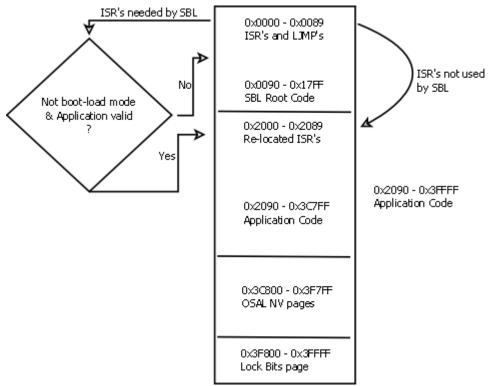

- 1. The image to be loaded via SBL must conform to a flash memory mapping compatible with the serial boot loader. Compatibility includes flash memory usage and ISR vector relocation (see Figure 1.)

- 2. The SBL must allow the bus master to force boot-load mode or an immediate jump to valid Application code after a powerup.

- 3. When not in boot-load mode, the SBL must immediately forward any ISR vectors that it consumes to the known relocation in the Application code (note that the Application code may not even enable such an ISR vector (e.g. USB ISR) in which case, it wouldn't need to define an ISR for it either.)

# 8. Design

#### 8.1 SBL Context

The SBL system is comprised of two images: the 'boot loader code' and the Z-Stack with its Application(s) built with a compatible flash mapping – the 'Application Code'. The placement of each of the two images into the internal flash is handled by the unique IAR linker command file used by each.

# 8.2 Functional Description

#### 8.2.1 Boot Code

The SBL solution requires the use of boot code to check the integrity of the active code image before jumping to it. This check guards against an incomplete or incorrect programming of the active image area. The SBL boot code provides the following functionality:

- 1. Boot Code will be the target of the reset vector (as well as any vector necessary for communicating on the chosen serial bus), and therefore contains startup and ISR code.

- 2. When the serial bus connection is detected and the master application commands it, Boot Code will program the SBL image into the active image area and will thusly complete the final step of the SBL process: code instantiation.

- 3. (Optional) Boot Code will guard against interrupted, incomplete or incorrect programming of the active image area by checking the validity of the active application code image via CRC. If the image is not valid then the boot code will not allow it to run.

# 8.2.2 SBL-compatible Z-Stack

An SBL-compatible Z-Stack is implemented as a standard ZigBee Application build with the exception of the linker command file and some ancillary settings.

Figure 1: Architectural Placement of the SBL & SBL-compatible Z-Stack image.

# 9. Producing SBL Boot Code to be programmed.

# 9.1 Separate Build & Debug of Boot Code

The Boot Code is separately built and debugged or programmed via the IAR IDE by opening the SBL Boot Project here:

\$INSTALL\_DIR\$\Projects\zstack\Utilities\BootLoad\CC2530USB\Boot.eww

The default configuration is with the download option to erase flash in order to start a CC2530 SoC with clean flash (and thus clean NV). Before debugging or physically programming the SBL-compatible Application code produced in the next section, this SBL Boot code must first be programmed into the flash (but only this once, since, as the following section mentions, the default option for application code is to preserve this SBL Boot code on successive debugging or programming.)

# 10. Producing SBL-compatible Application Code to debug or load by SBL.

The "RouterEB" build of the Z-Stack sample application known as GenericApp is used below for demonstration purposes only - the Customer would apply the following steps in her own, proprietary Z-Stack application and make the corresponding changes to all of the paths below that are specific to GenericApp. The CC2530USB is also used below for demonstration only – these same steps apply to any of the CC2530 targets supported by the Z-Stack release and a conforming SBL. It is only requisite that the paths specific to the CC2530USB target be changed accordingly.

10.1 Configure linker options for the SBL functionality.

#### 10.1.1 Configure the linker to generate extra output.

Check the checkbox to "Allow C-SPY-specific extra output file" as shown below.

| Options for node "Gene                                                                                                                          | ricApp"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | × |

|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Category:<br>General Options<br>C/C++ compiler<br>Assembler<br>Custom Build<br>Build Actions<br>Linker<br>Debugger<br>FET Debugger<br>Simulator | Factory Settings         Output       Extra Output       #define       Diagnostics       List       Config       Proce       Image: Config         Output file       Override       Override       Secondary output file:       Image: Config       Proce       Image: Config       Image: Confi |   |

|                                                                                                                                                 | OK Cancel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |

Figure 2: Configuring the linker to generate an extra output file.

# 10.1.2 Configure the linker extra output file format.

Check the checkbox to "Generate extra output file" and choose the "Output format:" as *simple-code* as shown below.

| Options for node "GenericApp"                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Category:<br>General Options<br>C/C++ compiler<br>Assembler<br>Custom Build<br>Build Actions<br>Linker<br>Debugger<br>FET Debugger<br>Simulator | Factory Settings         Output       Extra Output         #define       Diagnostics       List       Config       Proce         ©       Generate extra output file         Output file       Output file         ©       Oyerride default         GenericApp.sim         Eormat       Output format:         Simple-code       Image: Code         Format variant:       None |  |  |  |  |  |

|                                                                                                                                                 | OK Cancel                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

Figure 3: Configuring the linker extra output file format.

# 10.1.3 Configure the linker command file for SBL-compatible mapping.

Use the following line for the "Override default" command string: \$PROJ\_DIR\$\..\..\Tools\CC2530DB\cc2530-sb.xcl

| Category:<br>General Options<br>C/C++ Compiler                                                                                                                                 | Options for node "SerialApp"                                                                                                                                                             |                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Assembler         Custom Build         Build Actions         Linker         Debugger         Third-Party Driver         Texas Instruments         Infineon         ROM-Monitor | Category:<br>General Options<br>C/C++ Compiler<br>Assembler<br>Custom Build<br>Build Actions<br>Linker<br>Debugger<br>Third-Party Driver<br>Texas Instruments<br>Infineon<br>ROM-Monitor | Factory Settings         Output       Extra Output       #define       Diagnostics       List       Config       Proce ▲ ▶         Linker command file       ✓       Override default                                                                                                                 < |  |  |  |  |  |  |

|                                                                                                                                                                                | ROM-Monitor<br>Analog Devices<br>Silabs                                                                                                                                                  | Entry label program_start     Defined by application     Search paths: (one per line)     \$TOOLKIT_DIR\$\LIB\     Raw binary image     Eile: Symbol: Segment: Align:                                                                                                                                   |  |  |  |  |  |  |

Figure 4: Changing the linker command file to implement SBL-compatible mapping.

10.2 Configure build actions to invoke the post-processing tool.

Use the following line for the "Post-build command line:"

```

"$PROJ_DIR$\..\..\Tools\CC2530DB\oad.exe"

"$PROJ_DIR$\RouterEB\Exe\GenericApp.sim"

"$PROJ_DIR$\RouterEB\Exe\GenericApp.bin"

```

The above lines must be pasted as a single line into the dialog box with one space separating each block in parenthesis.

| Options for node "Gene                                                                                                                                                                                                            | ricApp"                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Category:<br>General Options<br>C/C++ Compiler<br>Assembler<br>Custom Build<br>Build Actions<br>Linker<br>Debugger<br>Third-Party Driver<br>Texas Instruments<br>Infineon<br>ROM-Monitor<br>Analog Devices<br>Silabs<br>Simulator | Build Actions Configuration Pre-build command line: Post-build command line: ['\$PR0J_DIR\$\\\Tools\CC2530DB\oad.exe'' ''\$PR0J_DIR\$\E 0K Cancel |

|                                                                                                                                                                                                                                   |                                                                                                                                                   |

Figure 5: Configuring the build actions to invoke the post-processing tool.

# 10.3 Add the CRC Shadow to the build.

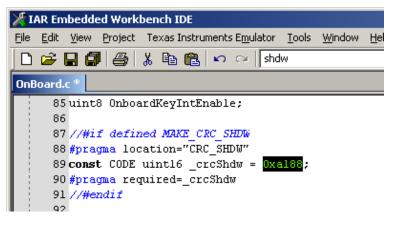

The CRC-shadow in OnBoard.c must be enabled by defining MAKE\_CRC\_SHDW somewhere (e.g. in OnBoard.c, hal\_board\_cfg.h, f8wConfig.cfg, or IAR project options to name a few possible locations.)

10.4 Building the Application Code for SBL.

Simply build from the IAR IDE as you normally would. The binary file produced, which is to be loaded by SBL, is found here:

**\$PROJ\_DIR\$**\RouterEB\Exe\GenericApp.bin

# 10.5 Debugging the Application Code with SBL.

# 10.5.1 Preserve the SBL.

In order to run or debug the Application Code, a Boot Code image must have already been downloaded to the CC2530 SoC (see the previous section.) So as not to destroy the Boot Code image, preserve the space by checking the "Retain unchanged memory" option as follows:

| Options for node "Gene                                                                                                                                                                                                            | ricApp"                                                                                                                         |                       |                               | × |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------|---|

| Category:<br>General Options<br>C/C++ Compiler<br>Assembler<br>Custom Build<br>Build Actions<br>Linker<br>Debugger<br>Third-Party Driver<br>Texas Instrument:<br>Infineon<br>ROM-Monitor<br>Analog Devices<br>Silabs<br>Simulator | Download Target<br>Erase flash<br>Retain unchanged memory<br>Suppress download<br>Verify download<br>CRC-16<br>Read back memory | Flash Lock Protection | e lock<br>lory<br>(all pages) |   |

|                                                                                                                                                                                                                                   |                                                                                                                                 | OK                    | Cancel                        |   |

Figure 6: Preserving boot code while debugging.

# 10.5.2 Force the CRC Shadow.

In order for the SBL to jump to the Application code after intercepting the reset vector, it must be able to verify that the Application code is valid. This validation takes over a minute and can be short-circuited by forcing the CRC-shadow to match the calculated CRC. **NOTE** that it is crucial that the CRC shadow be restored to its default value of 0xFFFF after debugging is complete. After each and every compile it is necessary to inspect the .map file to learn the new CRC:

| A IAR Embedded Workbench IDE |        |       |       |                   |        |                |                    |                   |     |                  |       |          |       |             |

|------------------------------|--------|-------|-------|-------------------|--------|----------------|--------------------|-------------------|-----|------------------|-------|----------|-------|-------------|

| File                         | Edit   | ⊻iew  | Proje | ect Tex           | (as Ir | istrumei       | nts E <u>m</u> ula | tor <u>T</u> ools | ₩in | dow <u>H</u> elp |       |          |       |             |

| Ď                            | 🖻 🖌    | 3 🖨   | I     | \$   <del>X</del> |        | <b>r</b> 2   × | ာလ။                | shdw              |     |                  | -     | <u> </u> | • \$4 | <b>&gt;</b> |

| Ser                          | ialApp | .map  |       |                   |        |                |                    |                   |     |                  |       |          |       |             |

| :                            | 33158  | Symbo | 51    | Ch                | eck:   | sum P          | femory             | Start             |     | End              | Init  | ial      | valu  | le          |

|                              | 33159  |       |       |                   |        |                |                    |                   |     |                  |       |          |       | -           |

| - 13                         | 33160  | che   | ecksu | m                 | 0xa.   | 188            | CODE               | 00001800          | ) - | 00001889         | 0x00  | 00 (     | #0x0  | 000)        |

| 13                           | 33161  |       |       |                   |        |                | CODE               | 00001894          | 1 - | 00007FFF         |       |          |       |             |

| - 13                         | 33162  |       |       |                   |        |                | CODE               | 00018000          | ) - | 0001FFFF         |       |          |       |             |

| 13                           | 33163  |       |       |                   |        |                | CODE               | 00028000          | ) – | 0002FFFF         |       |          |       |             |

| 13                           | 33164  |       |       |                   |        |                | CODE               | 00038000          | ) – | 0003FFFF         |       |          |       |             |

|                              | 33165  |       |       |                   |        |                | CODE               | 00048000          | ) – | 0004FFFF         |       |          |       |             |

| 13                           | 33166  |       |       |                   |        |                | CODE               | 00058000          | ) – | 0005FFFF         |       |          |       |             |

| 13                           | 33167  |       |       |                   |        |                | CODE               | 00068000          | ) – | 0006FFFF         |       |          |       |             |

|                              | 33168  |       |       |                   |        |                | CODE               | 00078000          | ) – | 0007C7FF         |       |          |       |             |

| 13                           | 33169  |       |       |                   |        |                |                    |                   |     |                  |       |          |       |             |

| 13                           | 33170  |       |       |                   | **     | *****          | ******             | *******           | *** | *******          | ***** | *        |       |             |

|                              | 33171  |       |       |                   | *      |                |                    |                   |     |                  |       | *        |       |             |

| 13                           | 33172  |       |       |                   | *      |                | END                | OF CROSS          | REI | FERENCE          |       | *        |       |             |

| 13                           | 33173  |       |       |                   | *      |                |                    |                   |     |                  |       | *        |       |             |

|                              | 33174  |       |       |                   | **     | *****          | ******             | *******           | *** | *******          | ***** | *        |       |             |

|                              | 33175  |       |       |                   |        |                |                    |                   |     |                  |       |          |       |             |

| - 13                         | 33176  | 112   | 325   | bytes             | of     | CODE           | memor              | у (+              |     | 141              | 635 r | ange     | fil   | 1)          |

|                              | 33177  |       | 25    | bytes             | of     | DATA           | memor              | y (+ 61 a         | њз  | olute )          |       |          |       |             |

|                              | 33178  | 6     | 617   | bytes             | of     | XDATA          | a memor            | У                 |     |                  |       |          |       |             |

|                              | 33179  |       | 192   | bytes             | of     | IDATA          | a memor            | У                 |     |                  |       |          |       |             |

|                              | 33180  |       | 8     | bits              | of     | BIT            | memor              | У                 |     |                  |       |          |       |             |

| i:                           | 33181  |       | 102   | bytes             | of     | CONST          | C memor            | У                 |     |                  |       |          |       |             |

|                              | 33182  |       |       | _                 |        |                |                    |                   |     |                  |       |          |       |             |

|                              | 33183  | Erro  | rs: 1 | none              |        |                |                    |                   |     |                  |       |          |       |             |

|                              | 33184  | Warn: | ings: | none              |        |                |                    |                   |     |                  |       |          |       |             |

|                              | 20105  |       | -     |                   |        |                |                    |                   |     |                  |       |          |       |             |

Then copy the CRC into the CRC Shadow and only now can you run the IAR debugger with this build:

# 11. Forcing boot-mode or early jump to Application code.

The SBL receives control from the reset vector and verifies whether valid Application code is present. If so, then the SBL gives the bus master a window in which to force boot mode or an immediate jump to Application code.

- 1. If the CRC is not 0x0000 or 0xFFFF and the CRC-shadow is identical, then the Application code is valid.

- 2. If the CRC is not 0x0000 of 0xFFFF and the CRC-shadow is 0xFFFF, then the CRC is calculated over the Application code image area (this will take over a minute.)

- a. If the calculated CRC matches the read CRC, program the CRC-shadow to this identical value to speed-up future power-ups.

- 3. If the Application code is valid, wait for the bus master to send a 0xF8 to force boot-mode or an 0x07 to force an immediate jump to the Application code.

- a. The default wait for UART and USB transport is 1 minute.

- b. The default wait for SPI is 50 milliseconds.

- 4. If the Application code is valid and the wait expires, jump to the Application code.

- 5. If the Application code is not valid, immediately jump to the boot-code without waiting as described above.

# 12. Producing SBL Application Code with Boot Code to be programmed.

For mass-production programming, it will be important to have a single image containing both the SBL Boot and Application code so that the part must only be programmed once. The following example assumes that the SmartRF04/05 Programming Tools will be used for programming an Intel-hex formatted file into the CC2530 SoC.

- 12.1 Build the Application Code hex image.

- 12.1.1 Configure the linker to generate Intel-hex output.

Check the checkbox to "Override default" and make the suffix ".hex" Also check the radio button for "Other" Output file Format and choose the Output format drop-down selection for 'intel-extended' as shown below.

| Options for node "Gene                                                                                                                                                                                                            | ericApp"                               | ×                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|------------------|

| Category:<br>General Options<br>C/C++ Compiler<br>Assembler<br>Custom Build<br>Build Actions<br>Linker<br>Debugger<br>Third-Party Driver<br>Texas Instruments<br>Infineon<br>ROM-Monitor<br>Analog Devices<br>Silabs<br>Simulator | Output Extra Output #define Diagnostic | Factory Settings |

|                                                                                                                                                                                                                                   |                                        | OK Cancel        |

Figure 7: Configuring the linker to generate Intel-hex output.

# 12.1.2 Generate output compatible for the SmartRF Programmer tool.

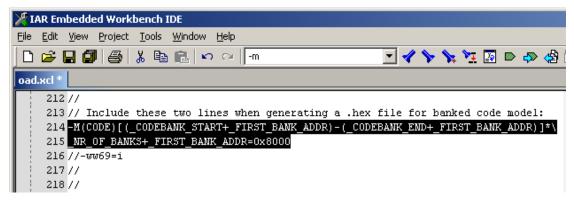

Remove the comments from the –M option in cc2530-sb.xcl as shown in hi-light.

Figure 8: Enabling –M option for SmartRF Programmer tool.

12.1.3 Re-build the Application Code to generate the .hex file.

Having already been built, just pressing the 'F7' key and linking will be sufficient

- 12.2 Pre-pend the Boot Code hex image to the Application Code hex image.

- Use any text editor to open the Application Code file produced here: \$PROJ\_DIR\$\RouterEB\Exe\GenericApp.hex

- 2) Delete this first line from the file: :020000040000FA

- 3) Use any text editor to open the SBL Boot Code file.

- 4) Delete these last two lines from the file::040000050000079E52:00000001FF

- 5) Copy the edited contents of the SBL Boot Code file to the top of the Application Code file and save it.

- 6) Use the SmartRF Programmer to install the edited Application Code hex image into the CC2530 SoC.