# HDVPSS DRIVER

## USER GUIDE

handle和通道：

handle(instance)就是该类型的硬件模块，handle的个数就是该类型的硬件模块的个数

通道channel：多通道是指视频流来自多个流，如通过network的decoder流，具有不同帧高、帧宽参数的捕获流。见P91

一个handle可以处理多个通道，也就是多个流

# Contents

## Articles

|                                   |     |

|-----------------------------------|-----|

| TI81xx-HDVPSS-UserGuide           | 1   |

| T181xx-HDVPSS Overview            | 15  |

| T1816X-HDVPSS-HW Overview         | 19  |

| T1814X-HDVPSS-HW Overview         | 23  |

| UserGuideHdvpssFolderOrg          | 27  |

| UserGuideFVID2                    | 36  |

| UserGuideHdvpssPlatformAPIs       | 57  |

| UserGuideHdvpssDisplayDriver      | 60  |

| UserGuideHdvpssM2mDriver          | 89  |

| UserGuideHdvpssTi816xDeiM2mDriver | 119 |

| UserGuideHdvpssTi814xDeiM2mDriver | 134 |

| UserGuideHdvpssCaptureDriver      | 149 |

| TI81xx-external video drivers     | 177 |

| UserGuideHdvpssIntegExample       | 181 |

| TI81xx-HDVPSS MultiCore Arch      | 200 |

## References

|                                          |     |

|------------------------------------------|-----|

| Article Sources and Contributors         | 205 |

| Image Sources, Licenses and Contributors | 206 |

# TI81xx-HDVPSS-UserGuide

本文件描述了如何在ti81xx\_evl上安装和使用德州仪器ti81xx\_hdvpss驱动程序。

hdvpss软件包为视频应用程序的开发、部署和执行提供了一个基本的软件平台。

hdvpss抽象了硬件提供的功能，并构成了在此平台上开发所有视频应用程序的基础。

## About this Manual

This document describes how to install and work with the Texas Instruments TI81xx HDVPSS drivers on TI81xx EVM. The HDVPSS package serves to provide a fundamental software platform for development, deployment and execution of video applications. HDVPSS abstracts the functionality provided by the hardware and forms the basis for all video applications development on this platform.

In this context, the document contains instructions to:

- Install the HDVPSS package

- Build the HDVPSS package

The document provides overview of HDVPSS and the following drivers contained in HDVPSS package:

- HDVPSS introduction

- HDVPSS Display drivers

- HDVPSS Memory to Memory drivers

- HDVPSS Capture drivers

Please note that ES 1 refer to PG 1.0 Silicon, ES 1.1 refer to PG 1.1 silicon, ES 2.0 refer to PG 2.0 silicon, ES 2.1 refer to PG 2.1 silicon. If no ES qualifier is used, it is applicable to all the known silicon versions.

## Getting Started

### System Requirements

Refer to 'Dependencies' section of release notes.

### Installation

HDVPSS device driver installation package is a self extracting EXE. Double click the installation package and install the package in the directory where various Texas Instruments tools are installed like CCS, BIOS, etc.

Following are the installation steps:

- Double click the installer package. Language screen appears. Select the language and click OK.

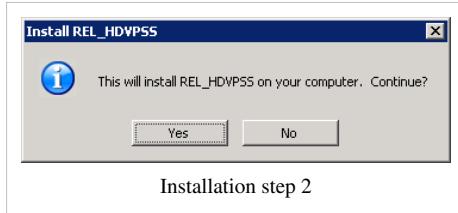

- Dialogue box appears to confirm the package installation click Yes to install.

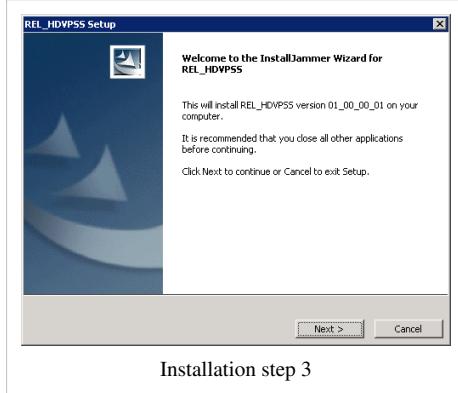

- Welcome screen appears. Click next to continue.

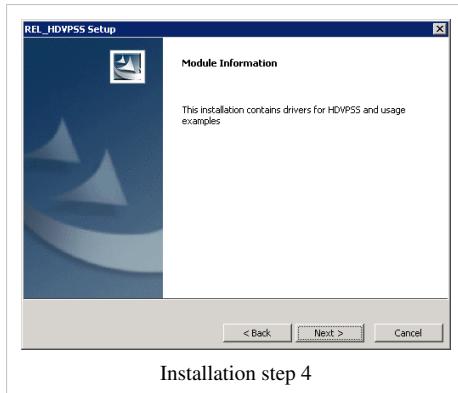

- Module information appears for the installation package. Click next to continue.

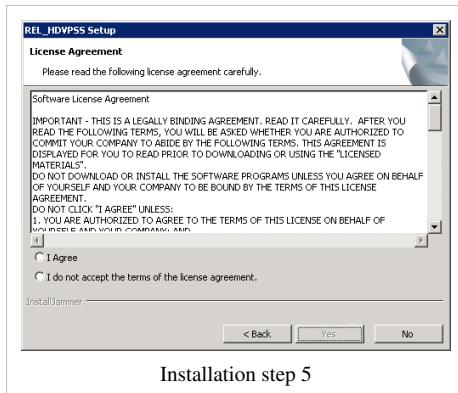

- License agreement appears. Accept the terms of agreement after reading and click yes to continue.

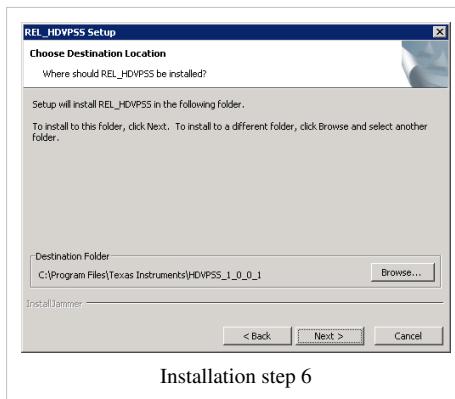

- Destination folder screen appears. Select the installation folder where other TI tools like CCS, BIOS are installed.

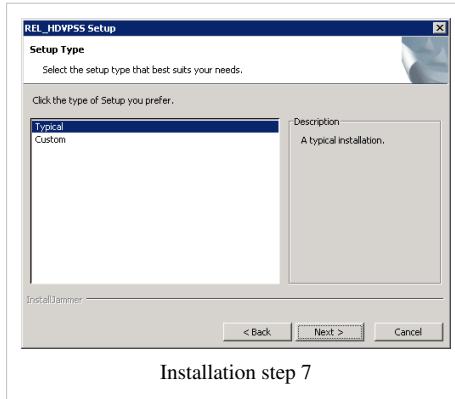

- Select Typical type of installation.

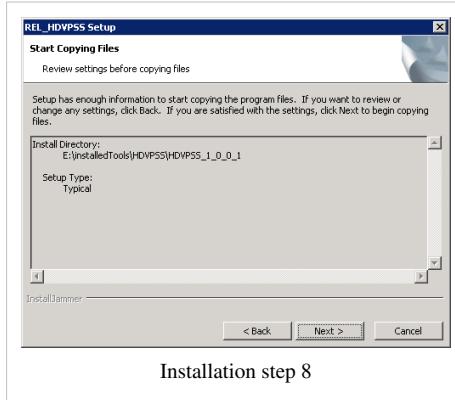

- Confirmation screen appears. Click next to install the package.

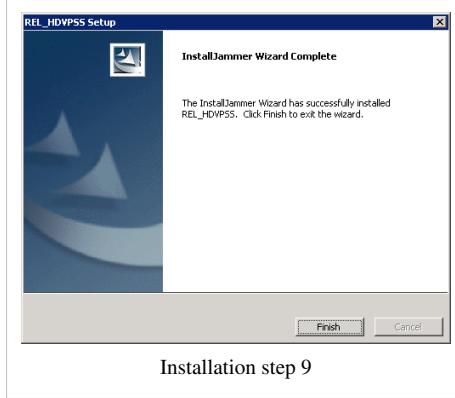

- Click on Finish to complete the installation

This completes the installation of the package.

hdvpss驱动的第一个应用程序

## Running First HDVPSS Application on TI816x

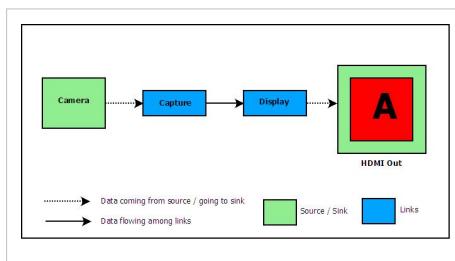

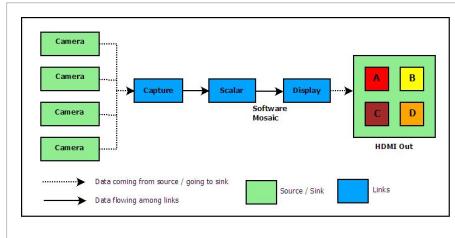

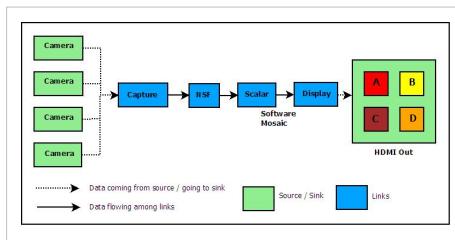

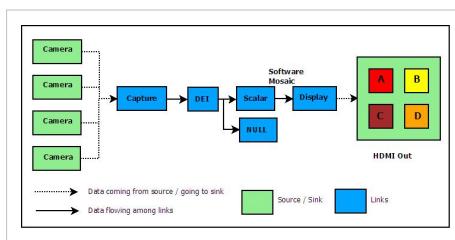

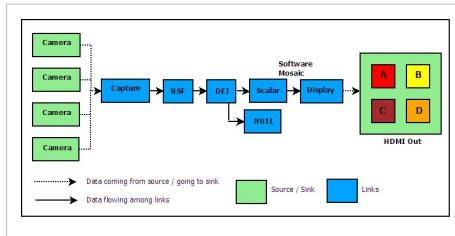

This section describes the out of the box experience for the HDVPSS drivers. It shows how to run the first HDVPSS application involving major HDVPSS drivers.

### Demo application on Video Surveillance (VS) Application board

视频监控(VS)应用板的演示应用

Following are the application details which is running on the VS application board:

- 16 channels NTSC interlaced input to VIP capture driver using TVP5158 in line mode.

- VIP capture outputs all the buffers in the memory in YUV422 interlaced format.

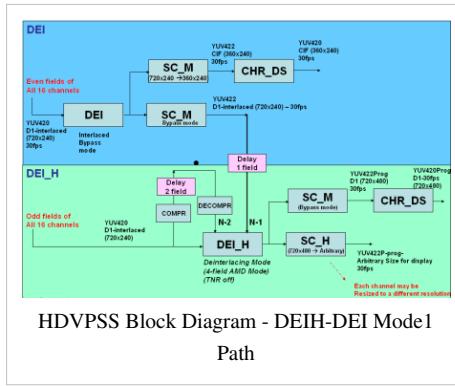

- DEI high quality and DEI medium quality picks 8 channels each out of 16 channels and scales it to CIF size and outputs it to memory.

- Display operates in multi window mode of 4X4 window picking up one buffer from each of the 16 channels and displays it in mosaic fashion at 1080p30 resolution.

16通道ntsc在行复用模式下使用tvp5158将输入到vip捕获驱动程序。

VIP捕获以yuv 422交错格式输出内存中的所有缓冲区。

DEI高质量和中等质量从16个通道中各挑选8个通道，去带隔行图像并将其缩放到cif大小并输出到内存中。

显示器以4x4窗口的多窗口模式工作，从16个通道中每个通道取一个缓冲器，以镶嵌方式显示，分辨率为1080p30。

More about the integration application is explained at Integration Application

### Steps to run the Demo on Video Surveillance Board

#### Common Steps for all examples

- Switch on the board.

- Open the CCS and connect to TI816x (CortexA8) using the CCS and debugger.

- Load gel file **TI816x\_evm\_A8\_ddr3.gel** under directory **\$HDVPSS\_INSTALL\_DIR/docs/TI816x** for A8 processor.

- Run *Scripts > TI816x HDVPSS Init > HDVPSSInit*. This will enable the DDR, Ducati and HDMI.

- Connect to CortexM3\_ISS

- Load gel file **TI816x\_evm\_ducati.gel** file in ISS\_M3 processor under directory **\$HDVPSS\_INSTALL\_DIR/docs/TI816x**.

- Run *scripts > UnicacheEnableDisable > Ducati\_cache\_enable*. This enables the cache on Ducati.

#### Steps for specific application

- Connect 16 input sources to the composite input of the video surveillance board.

- Connect the HDMI output of the VS board to the HDMI input of the TV.

- Load and Run

\$HDVPSS\_INSTALL\_DIR/pspdrivers/\_build/hdvpss\_examples\_chains/bin/ti816x-evm/hdvpss\_examples\_chains\_m3vpss\_debug

- Select option 7 at " Enter Choice:" option.

- You can see the 4X4 window of the 16 captured channels.

#### Important

Currently frame drops is observed on all the channels because of the DDR2 bandwidth limitation and/or the application issue.

## Running First HDVPSS Application TI814x

This section describes the out of the box experience for the HDVPSS drivers. It shows how to run the first HDVPSS application involving major HDVPSS drivers.

### Demo application on Video Surveillance (VS) Application board

Following are the application details which is running on the VS application board:

- 4 channels NTSC interlaced input to VIP capture driver using TVP5158 in pixel multiplexed mode.

- VIP capture outputs all the buffers in the memory in YUV422 interlaced format.

- DEI de-interlaces the interlaced image and scales it to CIF size and outputs it to memory.

- Scaler scales the images to fit into 1080P window

- Display operates in single window mode and display at 1080P30 resolution.

More about the integration application is explained at Integration Application

### Steps to run the Demo on Video Surveillance Board

#### Common Steps for all examples

- Switch on the board.

- Open the CCS and connect to TI814x (CortexA8) using the CCS and debugger.

- Load gel file *TI814x\_ES\_xx\_evm\_A8\_ddrX.gel* under directory *\$HDVPSS\_INSTALL\_DIR/docs/TI814x* for A8 processor.

- Use *TI814x\_ES\_1\_evm\_A8\_ddr2.gel* for ES 1 DDR 2 board

- Use *TI814x\_ES\_2x\_evm\_A8\_ddr2.gel* for ES 2.1 DDR 2 board

- Use *TI814x\_ES\_2x\_evm\_A8\_ddr3.gel* for ES 2.1 DDR 3 board

- Run *Scripts > TI814x HDVPSS Init > HDVPSSInit*. This will enable the DDR, Ducati and HDMI.

- Connect to CortexM3\_ISS

- Load gel file *TI814x\_evm\_ducati.gel* file in ISS\_M3 processor under directory *\$HDVPSS\_INSTALL\_DIR/docs/TI814x*.

- Run *scripts > UnicacheEnableDisable > Ducati\_cache\_enable*. This enables the cache on Ducati.

#### Steps for specific application

- Connect 8 input sources to the composite input of the video surveillance board.

- Connect the HDMI output of the VS board to the HDMI input of the TV.

- Load and Run

*\$HDVPSS\_INSTALL\_DIR/pspdrivers/\_build/hdvpss\_examples\_chains/bin/ti814x-evm/hdvpss\_examples\_chains\_m3vpss\_debug*

- Select option 4 at " Enter Choice:" option.

- You can see the 2X2 window of the 4 captured channels.

## Running First HDVPSS Application on TI8107

This section describes the out of the box experience for the HDVPSS drivers. It shows how to run the first HDVPSS application involving major HDVPSS drivers.

### Demo application on Video Surveillance (VS) Application board

Following are the application details which is running on the VS application board:

- 4 channels NTSC interlaced input to VIP capture driver using TVP5158 in pixel multiplexed mode.

- VIP capture outputs all the buffers in the memory in YUV422 interlaced format.

- DEI de-interlaces the interlaced image and scales it to CIF size and outputs it to memory.

- Scaler scales the images to fit into 1080P window

- Display operates in single window mode and display at 1080P60 resolution.

More about the integration application is explained at Integration Application

## Steps to run the Demo on Video Surveillance Board

### Common Steps for all examples

- Switch on the board.

- Open the CCS and connect to CortexA8 using the CCS and debugger.

- Load gel file **TI8107\_ES\_1\_evm\_A8\_ddr3.gel** under directory `$HDVPSS_INSTALL_DIR/docs/TI8107` for A8 processor.

- Run *Scripts > TI8107 System Initialization > TI8107HdvpssInit*. This will enable the DDR, Ducati and HDMI.

- Run *Scripts > TI8107 VDB DDR Configurations > EVM\_DDR3\_EMIF0\_400MHz\_Config\_256MB*. This will enable DDR for 256MB size. Please note that this option is required only for NetCam card.

- Connect to CortexM3\_ISS

- Load gel file **TI8107\_evm\_ducati.gel** file in ISS\_M3 processor under directory `$HDVPSS_INSTALL_DIR/docs/TI8107`.

- Run *scripts > UnicacheEnableDisable > Ducati\_cache\_enable*. This enables the cache on Ducati.

### Steps for specific application

- Connect 4 input sources to the composite input of the video surveillance board.

- Connect the HDMI output of the VS board to the HDMI input of the TV.

- Load and Run

`$HDVPSS_INSTALL_DIR/pspdrivers_/build/hdvpss_examples_chains/bin/ti8107-evm/hdvpss_examples_chains_m3vpss_debug`

- Select option 5 at " Enter Choice:" option.

- You can see the 2X2 window of the 4 captured channels.

编译HDVPSS驱动：hdvpss驱动程序和示例可以使用hdvpss安装目录中的Makefile构建。在这样做之前，用户可能必须修改规则.make文件(出现在安装目录中)，这取决于他的构建环境。

## Compiling HDVPSS Drivers

HDVPSS drivers and examples can be built using the *Makefile* present in the HDVPSS installation directory. Before doing so, user may have to modify the *Rules.make* file (present in the installation directory), depending upon his build environment.

Open the *Rules.make* file and make sure that the paths for the following tool-chains are correct (default installation paths for all the required tool-chains can be found in this file):

- **CODEGEN\_PATH\_M3** := Points to the Codegen toolchain for M3.

- **hdvpss\_PATH** := Points to the HDVPSS installation directory.

- **bios\_PATH** := Points to the BIOS installation directory.

- **xdc\_PATH** := Points to the XDC installation directory.

- **ipc\_PATH** := Points to the IPC installation directory.

**Important** 确保上面提到的路径中没有空格。如果安装目录中有任何空白，请在DOS命令提示符上使用dir /x生成的短名称，这将用~.替换空白。此外，在所有上述路径中使用正斜杠'/'而不是反斜杠'\'。

Make sure that the above mentioned paths don't have white spaces in them. In case the installation directory has any white space, use the short names generated by issuing `dir /X` on the DOS command prompt, which replaces the white spaces by ~. Also, use forward slash '/' instead of back slash '\' in all the above paths.

To build on Linux, an additional step is required to set the `OS` environment variable to `Linux`. Alternatively, it can be passed to the `gmake` command as indicated in the below steps:

After editing the *Rules.make* file, open a command prompt and `cd` (change directory) to the HDVPSS installation directory.

```

>cd $(HDVPSS_INSTALL_DIR)

```

Provide the command `gmake -s all`. This will clean and recursively build all the libraries and examples for the default platform (ti816x-evm) and default profile (whole\_program\_debug).

```

>gmake -s all

```

To build on Linux, if the `OS` environment variable is not set, the `gmake` command can be invoked as:

```

>gmake -s all OS=Linux

```

gmake所在路径的问题

通过修改规则中的Platform和Profile \$ (Core) , 可以更改默认平台和概要文件。

If the command prompt can't locate `gmake` command, then add the directory where `gmake` is present in the PATH environmental variable. Typically, `gmake` comes along with CCS/XDC installation and can be found at `$(CCS_INSTALL_DIR)/xdctools_XX_YY_ZZ_WW`.

**Note** Default platform and profile can be changed by modifying `PLATFORM` and `PROFILE_$(CORE)` in the `Rules.make` file respectively.

During development, the below `gmake` targets can also be used for convenience:

- `gmake -s hdvpss` - incrementally builds only HDVPSS drivers

- `gmake -s examples` - incrementally builds HDVPSS drivers and all examples

- `gmake -s examples_netcam` - incrementally builds HDVPSS drivers and all examples for the netcam/vcam usecase

- `gmake -s clean` - clean all drivers and examples

- `gmake -s examplesclean` - clean all examples ONLY

- `gmake -s example_name` - incrementally builds HDVPSS drivers and the specific example ONLY. Values for `example_name` can be - i2c, captureVip, chains, display etc.

包含所有支持选项的详细构建说明可以在hdvpss安装目录的README.txt文件中找到。

### Important

The detailed build instructions with all the supported options can be found in the `README.txt` file in the HDVPSS installation directory.

下面显示了用于各部门和系统中的不同的处理器的DDR / OCMC记忆内存映射。

假设一个1GB的DDR内存和512 KB的ocmc内存。视频/DSSM3MMU被配置成1GB DDR被分成两个部分--第一512 MB被缓存，下一个512 MB被非缓存。

## Memory Map for TI816x

The following shows the memory map of the DDR/OCMC memory used for the various sections and for the different processors in the system. This assumes a 1GB DDR memory and 512KB OCMC memory. The Video/DSS M3 MMU is configured such away that the 1GB DDR is split into two sections - 1st 512MB is cached and the next 512MB is non-cached.

- 1st 512MB - Cached:

- Linux: Used by the linux kernel running from A8. This is not used by M3.

- Tiler 16-bit, CMEM, DSP: These are not used by M3.

- Syslink IPC [SR0, SR1]: Shared memory used by syslink module to perform inter processor communication.

- DSS M3 Code: DSS M3 code program section (driver text section resides here)

- Video M3 Code: Video M3 code program section

- Video M3 Data: Video M3 bss and other data section

- DSS M3 Data: DSS M3 bss and other data section (driver bss, const and other global variables reside here)

- SHARED CTRL DUCATI, Shared Data, Debug: These are not used by M3.

- 2nd 512MB - Non-Cached:

- Notify Mem: Used as notify shared memory

- HDVPSS Shared Mem: Shared memory used for IPC between HDVPSS proxy server and client on A8 like FBDEV driver.

- VPDMA Desc Mem: HDVPSS driver VPDMA descriptor memory section used to store descriptors and overlay memory

- Frame Buffer: Frame buffer heap used for non-tiled video buffers

- Tiler 8-bit/Tiler page: Tiler memory for the different tiler view

DDR: 0x80000000 (1st 512MB - Cached)

+-----+

|                |       |

|----------------|-------|

|                |       |

| Linux          | 256MB |

|                |       |

| +-----+        |       |

| Tiler 16-bit   | 64MB  |

| +-----+        |       |

| CMEM           | 10MB  |

| +-----+        |       |

| DSP            | 32MB  |

| +-----+        |       |

| IPC (SR1)      | 12MB  |

| +-----+        |       |

| IPC (SR0)      | 16MB  |

| +-----+        |       |

| DSS M3 Code    | 4MB   |

| +-----+        |       |

| Video M3 Code  | 4MB   |

| +-----+        |       |

| Video M3 Data  | 32MB  |

| +-----+        |       |

| DSS M3 Data    | 60MB  |

| +-----+        |       |

| SHARED CTRL    |       |

| DUCATI         | 11MB  |

| +-----+        |       |

| Shared Data    | 1MB   |

| +-----+        |       |

| Debug/NOT USED | 10MB  |

| +-----+        |       |

DDR: 0xA0000000 (2nd 512MB - Non-Cached)

|                |       |

|----------------|-------|

| -----+         |       |

| Notify Mem     | 2MB   |

|                |       |

| +-----+        |       |

| HDVPSS Shared  | 3MB   |

| Mem            |       |

| +-----+        |       |

| VPDMA Desc Mem | 3MB   |

| +-----+        |       |

| FrameBuffer    | 248MB |

| +-----+        |       |

| Tiler PAGE     | 128MB |

|                |       |

| +-----+        |       |

| Tiler 8-bit    | 128MB |

|                |       |

| +-----+        |       |

```

OCMC: 0x40300000

+-----+

| OCMC0           | 256KB

+-----+

OCMC: 0x40400000

+-----+

| OCMC1           | 256KB

+-----+

```

## Memory Map for TI814x

The following shows various sections defined and used by HDVPSS drivers and its sample applications. This assumes a 512 MB of DDR memory and 128KB OCMC memory. The Video/DSS M3 MMU is configured such away that the 512MB DDR is split into two sections - 1st 256MB is cached and the next 256MB is non-cached.

- 1st 256MB - Cached:

- Linux: Used by the linux kernel running from A8. This is not used by M3.

- Sections EVENT\_LIST\_CORE0, PRIVATE\_CORE0\_DAT and EXTMEM\_CORE0 is not used by M3 HDVPSS

- Syslink IPC [SR0]: Shared memory used by syslink module to perform inter processor communication.

- VPSS M3 Data: VPSS M3 bss and other data section (driver bss, const and other global variables reside here)

- VPSS M3 Code: VPSS M3 code program section (driver text section resides here)

- Debug: Not used

- 2nd 256MB - Non-Cached:

- Notify Mem: Used as notify shared memory

- Tiler 8-bit/16-bit: Tiler memory for the different tiler view

- Frame Buffer: Frame buffer heap used for non-tiled video buffers

- VPDMA Desc Mem: HDVPSS driver VPDMA descriptor memory section used to store descriptors and overlay memory

- HDVPSS Shared Mem: Shared memory used for IPC between HDVPSS proxy server and client on A8 like FBDEV driver.

```

DDR: 0x80000000 (1st 256MB - Cached)

+-----+

|           |

| Linux      | 83MB

|           |

+-----+

| EVENT_LIST_CORE0 | 10MB

+-----+

| PRIVATE_CORE0_DAT | 37MB

+-----+

| EXTMEM_CORE0     | 0.625MB - or 625KB

+-----+

| Syslink IPC     | 16MB - SHARED_CTRL

+-----+

|           |

```

```

| VPSS M3 Data    | 53MB

|

+-----+

| VPSS M3 Code    | 53MB

+-----+

| Debug/NOT USED  | 3MB

+-----+

```

DDR: 0xC0000000 (2nd 256MB - Non-Cached)

```

+-----+

|           |

|   Tiler    | 128MB

+-----+

|           |

| Frame Buffer | 123MB

+-----+

| Notify Shared | 1MB

|     Mem       |

+-----+

| VPDMA Desc Mem | 2MB

+-----+

| HDVPSS Shared  | 2MB

|     Mem       |

+-----+

```

OCMC: 0x00300000

```

+-----+

| OCMC0 (Not used) | 128KB

+-----+

```

## Memory Map for TI8107

The following shows various sections defined and used by HDVPSS drivers and its sample applications. This assumes a 512 MB of DDR memory and 256KB OCMC memory. The Video/DSS M3 MMU is configured such away that the 512MB DDR is split into two sections - 1st 256MB is cached and the next 256MB is non-cached.

- 1st 256MB - Cached:

- Linux: Used by the linux kernel running from A8. This is not used by M3.

- Syslink IPC [SR0]: Shared memory used by syslink module to perform inter processor communication.

- VPSS M3 Data: VPSS M3 bss and other data section (driver bss, const and other global variables reside here)

- VPSS M3 Code: VPSS M3 code program section (driver text section resides here)

- Debug: Not used

- 2nd 256MB - Non-Cached:

- Notify Mem: Used as notify shared memory

- Tiler 8-bit/16-bit: Tiler memory for the different tiler view

- Frame Buffer: Frame buffer heap used for non-tiled video buffers

- VPDMA Desc Mem: HDVPSS driver VPDMA descriptor memory section used to store descriptors and overlay memory

- HDVPSS Shared Mem: Shared memory used for IPC between HDVPSS proxy server and client on A8 like FBDEV driver.

```

DDR: 0x80000000 (1st 256MB - Cached)

+-----+

|           |

| Linux      | 130.625MB

|           |

+-----+

| Syslink IPC | 16MB - SHARED_CTRL

+-----+

|           |

| DSS M3 Data | 53MB

|           |

+-----+

| DSS M3 Code | 53MB

+-----+

| Video M3 Data | 1MB

+-----+

| Video M3 Code | 1MB

+-----+

| Debug/NOT USED | 1MB

+-----+

```

```

DDR: 0xA0000000 (2nd 256MB - Non-Cached)

```

```

+-----+

|           |

| Tiler      | 128MB

+-----+

|           |

| Frame Buffer | 123MB

+-----+

| Notify Shared | 1MB

|     Mem      |

+-----+

| VPDMA Desc Mem | 2MB

+-----+

| HDVPSS Shared | 2MB

|     Mem      |

+-----+

```

```

OCMC: 0x00300000

```

```

+-----+

| OCMC0 (Not used) | 256KB

+-----+

```

## Directory Organization

The following expands on the directory structure of → [HDVPSS Folders](#) [链接](#)

## HDVPSS Overview

This section provides top level information about HDVPSS hardware architecture and software architecture.

### HDVPSS Hardware Overview

HDVPSS hardware overview explains the HDVPSS hardware blocks in brief. It is not necessary to have a full knowledge of the HDVPSS hardware architecture to use HDVPSS drivers. HDVPSS hardware overview can be found at [HDVPSS Hardware Overview](#). [hdvpss硬件概述](#)简要解释hdvpss硬件块。不需要完全了解hdvpss硬件体系结构来使用hdvpss驱动。hdvpss硬件概述可以在hdvpss硬件概述中找到。

这两个

链接打

不开

### HDVPSS Software Overview

HDVPSS software overview explains the HDVPSS software and the major class of drivers supported by the HDVPSS software interfaces to the application. It is not important to have a full understanding of the HDVPSS software architecture for using HDVPSS drivers. HDVPSS Software overview could be found at [HDVPSS Software Overview](#). [hdvpss软件概述](#)解释了hdvpss软件和hdvpss软件接口支持的主要驱动程序类。对hdvpss软件体系结构有充分的理解对于使用hdvpss驱动并不重要。hdvpss软件概述可以在hdvpss软件概述中找到。

[fvid 2](#)是专门为视频设备类设计的一组API或框架。它以标准的方式公开视频设备的数量，以便应用程序在从曾经的视频设备类别迁移到其他类型的视频设备时，所需的更改最少，它们都与fvid 2接口保持一致。有关fvid 2的更多详细信息可以在。

[userguidefvid 2](#)

### FVID2 Overview

FVID2 are the set of APIs or framework specifically designed for the video class of devices. It exposes number of features of the video devices in a standard way so that application needs a minimum changed while migrating from the once class of video devices to other class of video devices, both of them adhering to the FVID2 interfaces. More details about the FVID2 can be found at → [UserGuideFVID2](#)

## HDVPSS Drivers

[HDVPSS package 支持的不同类型的 HDVPSS drivers](#)

This section explains about the different class of the HDVPSS drivers supported by the HDVPSS package.

### Platform APIs and Drivers

[平台 APIs和Drivers](#)

This section describes about APIs and driver which are required to initialize and setup platform for HDVPSS drivers. These API and drivers doesn't fit into FVID2 drivers since they are very much dependent on SoC and board. Users needs to modify these APIs based on their boards. Description of platform APIs and Drivers could be found at → [HDVPSS Platform APIs and Drivers](#)

[This section describes about APIs and driver which are required to initialize and setup platform for HDVPSS drivers.](#)

[These API and drivers doesn't fit into FVID2 drivers since they are very much dependent on SoC and board. Users needs to modify these APIs based on their boards. Description of platform APIs and Drivers could be found at \[HDVPSS Platform APIs and Drivers\]\(#\)](#)

显示驱动程序是指从内存中提取输入缓冲区并在外部设备(如tv、lcd等)上显示该缓冲区的驱动程序，hdvpss包支持的显示驱动程序的详细信息可在。 [显示驱动程序用户指南](#)

## Display Drivers

Display drivers refers to the drivers which takes the input buffer from the memory and displays that buffer on the external device like TV, LCD etc. Details of the display drivers supported by the HDVPSS packages can be found at → [HDVPSS Display Driver UserGuide](#)

内存驱动程序是指从内存中提取输入，对输入进行缩放处理，对图像进行色度采样，并将其放回内存的驱动程序。

## Memory Drivers

Memory drivers refers to the drivers which takes the input from the memory, processes the input like scale the image, chroma up samples the image and puts it back to the memory. Details of the memory drivers supported by the HDVPSS package can be found at → [HDVPSS M2M Driver UserGuide](#)

捕获驱动：捕获驱动程序是指从摄像机、DVD播放机等外部源获取输入并将捕获图像放入内存的驱动程序。hdvpss包支持的捕获驱动程序的详细信息可在。 [hdvpss捕获驱动程序用户指南](#)

## Capture Driver

Captures drivers refers to the drivers which takes the input from the external sources like camera, dvd players etc and puts the capture images in the memory. Details of the capture drivers supported by the HDVPSS package can be found at → [HDVPSS Capture Driver UserGuide](#)

外部视频设备驱动：外部视频设备驱动程序是指hdvpss外部的设备，如tvp 5158解码器、sil9022a hdmi编码器等。

外部视频设备驱动程序

## External video device drivers

External video device drivers refers to the devices which are external to the HDVPSS like the TVP5158 decoder, sil9022a HDMI encoder etc. Details about the external video device drivers could be found at → [External Video Device Drivers](#)

集成的例子：集成示例演示了不同组合中使用的不同驱动程序。它展示了

一些具体的应用，如16通道捕获、噪声过滤、隔行捕获，并在电视上

以马赛克格式显示。不同集成应用的详细信息可在。 [hdvpss集成示例](#)

## Integration Examples

Integration examples demos the different drivers used in various combination. It shows some specific real world applications like 16 channel capture, noise filter it, de-interlace the interlaced capture and show it on the TV in mosaic format. [Details of the different integration applications can be found at → HDVPSS Integration Examples](#)

hdvpss驱动程序支持多核体系结构。使用hdvpss多核软件体系结构，所有hdvpss驱动程序接口都可以在运行不同os的任何其他处理器上公开。其中一个用例是通过运行在A8处理器上的linux os控制hdvpss的图形平面。有关hdvpss多核体系结构的详细信息可以在。 [hdvpss软件多核体系结构](#)

## HDVPSS Software Support on MultiCore Architecture

HDVPSS drivers supports the multi core architecture. All the HDVPSS driver interfaces can be exposed on any other processor running different OS, using the HDVPSS multi core software architecture. One such use-case is controlling the graphics plane of the HDVPSS through the Linux Os running on the A8 processor. Details about the HDVPSS multi core architecture can be found at → [HDVPSS Software MultiCore Architecture](#)

## HDVPSS Linux Drivers

### Build ProxyServer BIOS Application

建立代理服务器

BIOS的应用

#### Installation

- Change the IPC path in Rules.make to the installed directory

- Run command prompt and cd (change directory) to the HDVPSS install directory

```

>cd $(HDVPSS_INSTALL)

```

- Provide the command `gmake -s proxy`. This will build proxyserver BIOS application, which is loaded by the syslink slaveloader user space application.

```

>gmake -s proxy

```

To build on Linux, if the `OS` environment variable is not set, the `gmake` command can be invoked as:

```

>gmake -s all OS=Linux

```

这个示例应用程序的目的是在M3上运行hdvpss应用程序，当另一个应用程序hdvpss运行在A8上时。这个应用程序从平台上的片外HDMI运行马赛克显示测试。用户可以在A8上运行另一个Linux应用程序(for ex: fbdev应用程序)，它可以在片上hdmi上输出，并检查两个应用程序是否可以并行运行。

## Proxy with Display App

**Introduction** This sample app is intended to run an HDVPSS application on M3 when there is one more application HDVPSS running on A8. This application runs the mosaic display test from Off-Chip HDMI on the platform. The user can run another linux application on A8 (for ex: fbdev application) which can output on On-Chip HDMI and check whether both the application can run in parallel.

**Compilation** To compile the application for linux type the following on command line

```

>gmake -s proxyDisplay OS=Linux

```

**Running the application on the board** To run this application the following are the steps to be done

- Boot up linux on the board

- Load Syslink module

- Load VPSS-M3 firmware (this module)

- load VPSS-M3 module

- Load fbdev module

- Load on-chip HDMI module

(有关如何完成上述操作的更多信息，请参阅psp视频驱动程序用户指南中的“加载vpss和fbdev驱动模块”一节)。当完成上述操作时，将从片外hdmi输出到display。现在，用户可以在a8上运行另一个应用程序，以测试a8和m3上的应用程序是否可以并行运行(例如：fbdev应用程序，它输出到片上hdmi)。

(For more information on how the above can be done refer to the section "Load VPSS and Fbdev Driver Modules" in PSP Video Driver User guide) When the above is done there will be output from the off-chip HDMI to display. Now the user can run another application on A8 to test whether the application on A8 and M3 can run in parallel (for ex: fbdev application which outputs to On-chip HDMI)

本节主要描述的驱动程序不是hdvpss包的一部分，而是使用hdvpss驱动程序。这些驱动程序包括图形管道上的linux框架缓冲区驱动程序、显示上的V4L2显示和捕获驱动程序以及VIP管道。有关所有驱动程序的详细信息，请参阅

[http://processors.wiki.ti.com/index.php/ti81xx\\_psp\\_us](http://processors.wiki.ti.com/index.php/ti81xx_psp_us)

## Linux FrameBuffer Driver

This section primarily describes about the drivers which are not the part of HDVPSS package but uses the HDVPSS drivers. Those drivers includes Linux framebuffer driver on Graphics pipeline, V4L2 display and capture driver on display and VIP pipelines respectively. Details about all those drivers can be found at [http://processors.wiki.ti.com/index.php/TI81XX\\_PSP\\_User\\_Guide](http://processors.wiki.ti.com/index.php/TI81XX_PSP_User_Guide)

## HDMI Driver

HDMI driver is another driver which is controlled from the Linux running the on A8. Currently the HDMI driver interfaces are exposed as a part of the Linux standard Character driver interface. Details about the same can be found at [HDMI Driver](#)

# T181xx-HDVPSS Overview

## HDVPSS Hardware Introduction

### TI814X/TI8107 HDVPSS Hardware

→ TI814X/TI8107 HDVPSS Hardware Overview

### TI816X HDVPSS Hardware

→ TI816X HDVPSS Hardware Overview

## HDVPSS Driver Introduction

HDVPSS drivers could be divided at top level in three categories:

- Display Driver

- Memory Driver

- Capture Driver

有几个显示驱动程序路径可以通过dei aux和main , 422 bp路径和次要路径。除此之外，还有三条只支持rgb不同数据格式的grpx路径支持。下面将讨论显示驱动程序的更多细节：显示驱动程序将支持不同的标准分辨率，如HD venc的1080 p60、1080 i60、720 p60等，而sd venc则支持sd分辨率。

### Display Driver

There are several display drivers path are possible going through DEI Aux and main,422BP path and Secondary path. Apart from this, there is support for three GRPX path which supports only RGB different data format. More details about display driver is discussed in respective section. Some of salient features are mentioned below:

- Display driver will support different standard resolution like 1080p60, 1080i60, 720p60 etc for HD VENC and SD resolution for SD VENC

- All Display drivers are non-blocking i.e. asynchronous drivers. Blocking calls are not supported.

- Notification of operation completion is done through callbacks.

- Different paths within display drivers could be configured using display controller. 使用显示控制器控制显示路径

- Once the display operation is started, the display driver always retains the last buffer and displays the same buffer continuously till the application gives a new buffer to display.

- Some of display driver will have capability for inline scaling and de-interlacing. These capabilities are based on whether specific IPs are available in the path or not. 一些显示驱动程序将具有内联缩放和去隔行功能。这些功能是基于特定的ips是否可用在路径上的。

- Display drivers will also be supported on the path having graphics IPs. 在具有图形ips的路径上也将支持显示驱动程序。

- All Display drivers including graphics are supported on:

- Interfaces : FVID2

- OS :BIOS6

- Processor : Ducati M3

与显示驱动程序一样，有几种路径可用于内存到内存的操作。一些标准的M2M操作，如缩放、噪声过滤、去交错等，在各自的部分中讨论了不同支持的M2M驱动程序。以下是大多数内存驱动程序的顶级特性：

所有mem-mem驱动程序都是非阻塞的，即异步驱动。不支持阻塞调用！！！

M2M驱动程序可以多次打开 - 支持同一驱动程序的多个句柄(N) - 每个句柄可以有不同的配置。

内存驱动程序支持来自多个句柄的输入请求排队，并立即返回。调用方/请求者将通过回调函数被告知内存操作完成(调整大小/nf/去交错)，每个句柄有不同的回调。

## Memory (M2M) Driver

Like display driver, there are several paths which could be used for memory to memory operation. Some of standard M2M operations are like scaling, noise filtering, de-interlacing etc. Different supported M2M drivers are discussed in the respective section. Following are top level features of most of memory drivers:

- All Mem-Mem drivers are non-blocking i.e. asynchronous drivers. Blocking calls not supported!!

- M2M drivers could be opened multiple times – supports multiple handles (N) for the same driver - Each handle can have different configuration.

- Memory driver supports queuing of input request from several handles and calls returns immediately. Caller/Requester will be informed about completion of memory operation (Resizing/NF/ de-interlacing) through callbacks and there are different callbacks for each handles.

- Each call/requests to Mem Driver can consist of set of buffers.

- N ( Maximum Number of picture or frame in each request) is fixed per handle at time of driver open. For example, its possible to submit a request 16CH buffer to NF and get only one notification at the end of 16CH NF processing. Thus reducing interrupts from 960 interrupts/sec to 60 interrupts/sec. This results in lower CPU load and higher HW utilization.

- Callback will be generated after processing all requests in a given set.

- All M2M drivers are supported on:

- Interfaces : FVID2

- OS : BIOS6

- Processor : Ducati M3

对mem驱动程序的每个调用/请求可以由一组缓冲区组成。

n(每个请求中的最大图片或帧数)在驱动程序打开时每个句柄固定，例如，它可以向nf提交一个请求16 ch缓冲区，并在16 ch nf处理结束时只收到一个通知，从而将中断从960个中断/秒减少到60个中断/秒，从而降低CPU负载，提高hw利用率。

回调将在处理给定集合中的所有请求后生成。

捕获驱动程序用于从外部世界捕获数据。关于每个捕获驱动程序特性的详细信息将在各自的部分中讨论。这里只提到了几个重要的特性。

## Capture Driver

VIP捕获驱动程序是非阻塞的，即异步驱动程序。不支持阻塞调用。

捕获帧的通知是通过回调完成的。

Capture drivers are used for capturing data from external world. Details about each of capture driver features are discussed in the respective section. Only few of important features are mentioned here.

- VIP Capture drivers are non-blocking i.e. asynchronous drivers. Blocking calls are not supported.

- Notification of captured frames is done through callbacks.

- Multi-channel line multiplexed capture - 2CH, 4CH, 8CH - upto D1 (NTSC/PAL) resolution

- Single channel capture upto 1080P (1920x1080) resolution

- Single source (RGB 24-bit or YUV422 8/16-bit), dual output (RGB 24-bit and/or YUV422 and/or YUV420) support

- Multi-instance (VIP0, VIP1), multi-port capture (Port A, Port B), with ability to configure each instance, port independently.

- Capture drivers are supported on:

- Interfaces : FVID2

- OS : BIOS6

- Processor : Ducati M3

多通道线路复用捕获

使用hdvpss驱动程序不需要完全了解hdvpss驱动程序体系结构。这里只提供了顶级的驱动程序体系结构。对于应用程序的开发或hdvpss驱动程序的使用，了解fvid 2接口就足够了。fvid 2接口将在不同的部分中详细解释。

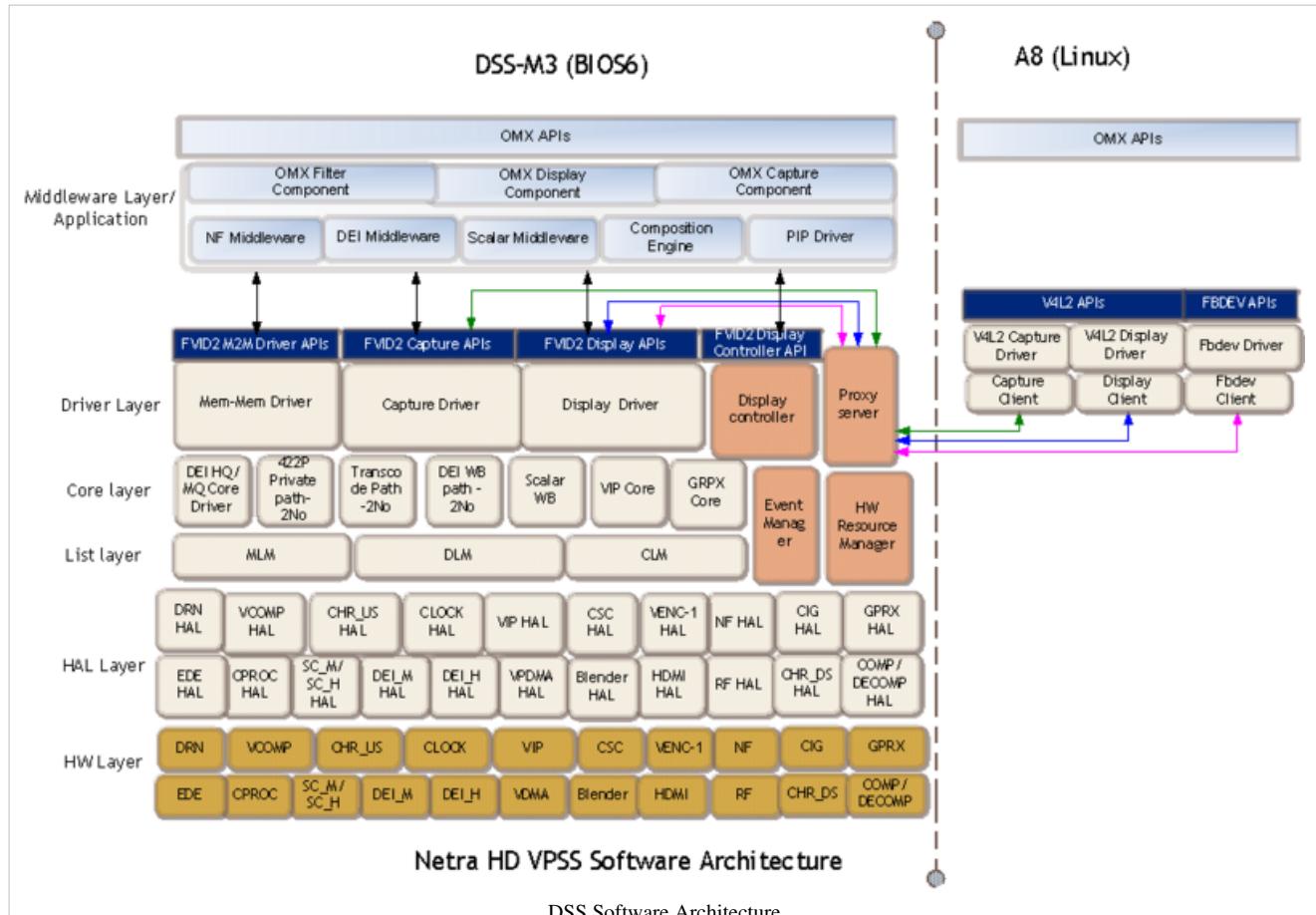

## HDVPSS Driver Architecture Introduction

It is not necessary to have a full understanding of the HDVPSS driver architecture to use HDVPSS drivers. Only top level driver architecture has been put here. It is sufficient to have understanding of FVID2 interface for development of application or use of HDVPSS drivers. FVID2 interface is explained in details in different section.

HDVPSS Driver architecture follows layered architecture.

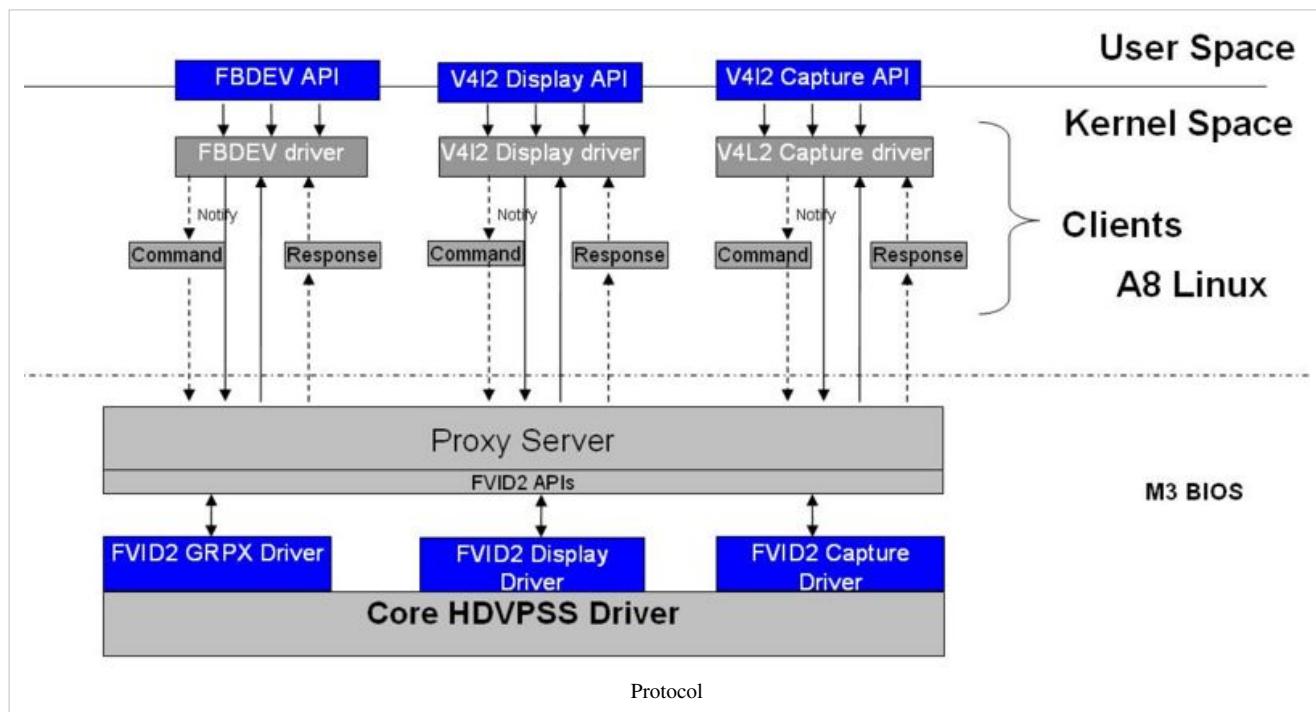

DSS Software Architecture

hdvpss的不同层或组件/模块如下：

Different layers or components/modules of HDVPSS are:

驱动层 - 它是hdvpss驱动程序体系结构的最上层，fvid 2接口在此层公开

fvid 2接口用于与应用程序的交互，除了公开fvid 2接口外，驱动层还负责

请求的入队和出队，处理内核和列表管理层与驱动层之间的交互。

- **Driver layer**- It is top most layer of HDVPSS driver architecture and FVID2 interface is exposed at this layer.

FVID2接口

FVID2 interface is used for interaction with application. Apart from exposing FVID2 interface, driver layer is also responsible for queue and de-queuing of request, handling of interaction between cores and list manager

核心层 - 它负责创建描述符。描述符的长度为32或16字节，并在内存中创建，并提供给vpdma进行最终操作。此外，描述符可以理解为对hdvpss dma引擎的命令，用于数据传输或设置不同的配置，如帧的高度和宽度。

**Core layer**- It is responsible for creation of descriptors. Descriptors are 32 or 16 bytes in length and are created in the memory and provided to VPDMA for final action. Further, descriptors could be understood as command to

HDVPSS DMA engine for data transfer or for setting different configuration like height and width of frame.

**List layer**- These descriptors are required to be arranged in specific sequence for different kind of operation or drivers like display, capture and M2M. For example, configuration descriptor for setting frame size should be placed before data descriptor which is responsible for actual data movement. These special arrangement of descriptors for different kind of operations are handled through list manager. As explained above, descriptors could be understood as command to HDVPSS DMA engine for data transfer or for setting different configuration like height and width of frame.

描述符排序

**HAL layer**- Hardware Abstraction layer – as name suggest – it abstracts multiple IPs of HDVPSS and provides interfaces for upper layer of stacks.

硬件抽象层 - 顾名思义 - 它抽象出hdvpss的多个ips，并为上层堆栈提供接口。

**HW layer**- It is HDVPSS H/w layer.

列表层 - 这些描述符需要按照特定的顺序排列，用于不同类型的操作或驱动程序，如显示、捕获和m2m。例如，设置帧大小的配置描述符应放在数据描述符之前，该描述符负责实际的数据移动。这些特殊的描述符安排是通过列表管理器来处理的。如上所述，描述符可以理解为hdvpss命令。数据传输或设置不同配置（如帧高和帧宽）的DMA引擎

事件管理器-有一个中断流到hdvpss的Ducati m3中。事件管理器解析中断状态寄存器以找出不同类型的中断，并传播到hdvpss堆栈的不同模块。资源管理器-因为不同的路径可能有多个驱动程序。不同的路径可以使用相同的IP(把IP理解为HDVPSS的视频处理硬件子模块)，例如在显示和内存驱动程序中在DEI\_H路径中的DEI。这意味着在任何时候只有一个驱动程序可以活动。资源管理器处理分配给不同驱动程序的资源。代理服务器;hdvpss协议栈支持多核驱动程序体系结构，这意味着驱动程序可以从不同的内核调用，例如在M3的BIOS6中调用FVID2接口或者Linux上使用V4L2/fbdev驱动程序，通过m3与a8之间的通信已经实现了。这是hdvpss软件堆栈的内部模块，它侦听来自V4L2/fbdev驱动程序的IPC请求，转换成适当的fvid 2请求并发送到M3的hdvpss驱动程序。好像请求是在M3本地发出的。它再次使用Notification通知请求的完成

解析中断

- **Event Manager**- There is single interrupt flowing into Ducati M3 for HDVPSS. Event manager parses the interrupt status register to figure out different kind of interrupts and propagates to different modules of HDVPSS stack.

只允许一个驱动程序有效

- **Resource Manager**- There are multiple driver possible because of various paths. Different path may use same IP like DEI in DEI\_H path in Display and Memory driver. It means only one of driver could active at any point of time. Resource manager handles allocation resources to different drivers.

驱动程序可以从不同的内核调用，例如在M3的BIOS6中调用FVID2接口或者Linux上使用V4L2/fbdev驱动程序

- **Proxy Server**- HDVPSS stack supports multi core driver architecture. It means that driver could be invoked from different core i.e. using FVID2 interface on M3 hosting BIOS6 or v4l2/fbdev driver on A8 hosting Linux. This has been achieved using IPC communication between M3 and A8. This is internal module of HDVPSS software stack. It listen IPC request from V4L2/fbdev driver. It translates into appropriate FVID2 request and sends to HDVPSS driver on Ducati M3 as if request has originated locally on Ducati M3. It uses Notify again to inform back completion of request.

将A8对HDVPSS的请求通过IPC转为M3的fvid2请求，好像请求是从M3发出的

## HDVPSS Driver Co-existence rule hdvpss驱动共存规则

多个驱动需要相同的ip块-相同的路径不能同时在两个驱动程序中使用。例如，dei不能同时用于m2m去隔行，和显示时的去隔行。换句话说，两个驱动程序不应该同时使用相同的IP。在不同的驱动程序中使用相同IP的情况有几种。这已经得到了管理。通过资源管理器。资源管理器在打开驱动程序时检查资源的

这些列表是在资源管理器打开驱动程序时动态地分配给不同的驱动程序的。每个显示器有一个列表，有独立的显示器。这意味着如果三个显示是活动的，显示最多可以包含3个列表。这种配置取决于每个电视的，不取决于像422bp或grpx平面这样的视频平面是如何连接到同一台电视的。

here are several drivers possible out DSS block diagram as discussed earlier. It is very obvious that all drivers can't exit mainly because of two reasons. 前面已经讨论过，有几个驱动程序可能是DSS的。很明显，所有的驱动程序都不能同时退出，主要是因为两个原因。

**Same IP block required in more drivers** - Same paths can't be used in two drivers at same time. For example, DEI can't be used for M2M de-interlacing and also for online de-interlacing during display at same time. In other words, same IP should not be used by two drivers at same time. There are several such instances where same IP are used in different drivers. This has been managed through **resource manager**. Resource manager checks for availability of resources while opening driver. 两个驱动程序不应该同时使用相同的IP(HDVPSS的硬件处理单

**Number of list** – As discussed earlier, descriptors are used for programming of HDVPSS DMA engine i.e. VPDMA. Descriptors could be understood as command to HDVPSS DMA engine for data transfer or for setting different configuration like height and width of frame. Further to this, these descriptors are required to be arranged in specific sequence for different kind of operation or drivers like display, capture and M2M. These specific arrangements of descriptors in memory should be in contiguous and start address of this buffer holding several descriptors should be given to VPDMA. These contiguous buffers which hold descriptors are called as

**list**. HDVPSS could handle such eight lists which represents eight different set of descriptors.

**list**:组合在一起的描述符。描述符被放在一起完成工作，而且放置的内存地址通过寄存器告知VPDMA

These lists are allocated dynamically to different drivers while opening of driver by resource manager. In general,

- One list for each display and there are independent displays are possible. It means that display could take maximum of 3 lists in the case three display are active. This configuration is per TV and does not depend upon how video planes like 422BP or GRPX plane are connected to same TV.

- One list for irrespective of number or kind of captures. In other words, two 1080p capture and 16 channels D1 capture will also use one list. 一个列表，不管捕获的数量或种类。换句话说，两个1080 p捕获和16个通道D1捕获也将使用一个列表。

- Each memory driver requires different list. 不同的内存驱动程序需要不同的列表

- Note that list could be for activating more memory drivers in the case one of TV say SD display is not active.

There is co-existence matrix for drivers which help in showing which driver could co-exist. It could be found at Media:HDVPSS-Coexistence.xls.

列表数--正如前面所讨论的，描述符用于hdvpss dma引擎的编程，即vpdma。描述符可以理解为对hdvpss dma引擎的命令或设置不同的配置，如帧高和帧宽。此外，对于不同类型的操作或驱动程序(如显示、捕获和m2m)，这些描述符需要放在一起，描述符起始地址应该告知VPDMA(通过寄存器)。这些连续的缓冲区包含描述符被称为list。list.hdvpss可以处理这八个表示八个不同的描述符集的列表。

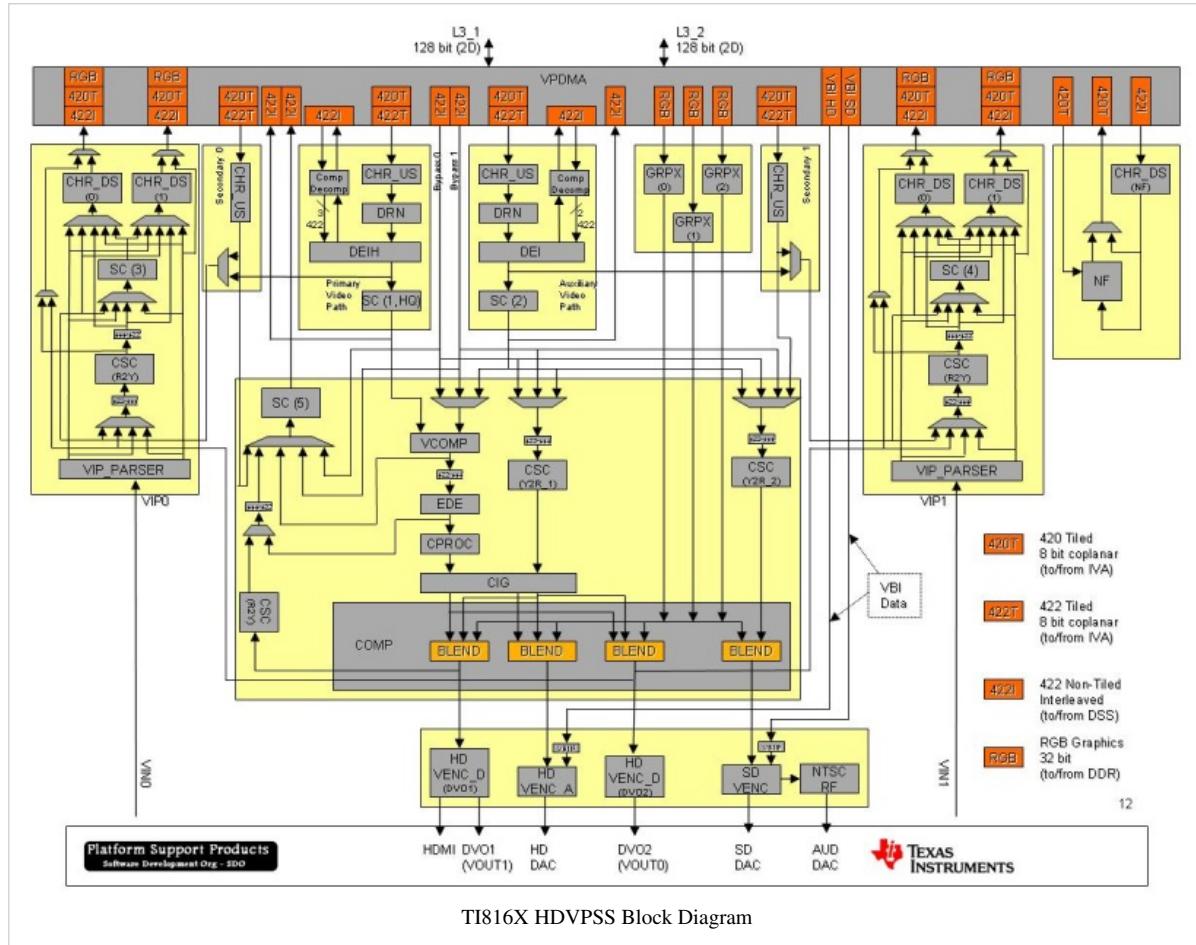

# T1816X-HDVPSS-HW Overview

---

## TI816X HDVPSS Hardware Introduction

The display sub system includes video display processing modules using the latest TI developed algorithms, flexible compositing and blending engine, full range of external video interfaces in order to deliver a high quality video contents to the end devices. This document covers various aspects of HD-related requirements in addition to SD-related requirements.

Each of the components are explained in detail along with its features in the Netra display subsystem overview documents.

## HDVPSS Features

**Few top features** are mentioned below

- The HDVPSS supports HD (up to 1080p) and SD (NTSC/PAL) outputs simultaneously

- The HDVPSS handles both video and graphics efficiently to create high-quality user interfaces. This includes (but not limited to) deinterlacing, scaling, noise reduction, alpha blending, chroma keying, flicker filtering, and pixel format conversion.

- It supports tiled and raster data formats, scan format conversion, aspect-ratio conversion, and frame size conversion.

- The HDVPSS generate secure video signal with proper content protection mechanisms,i.e., HDCP and Macrovision/CGMS-a for digital and analog outputs, respectively.

- Four independently controlled compositors (HDMI, HD-comp, DVO2, SD) shall be supported.

- Two parallel video processing pipelines (main and aux) for concurrent video stream processing is supported.

- Both the main and auxiliary video pipelines shall include a write-back path to the external memory to support memory to memory scaling of video frames independently from the display output frame timing.

- It supports three graphics plane and include an up/down scaler optimized for graphics application with each graphics path. Multiple regions in a graphics layer are supported to reduce the amount of data transfer from the external memory.

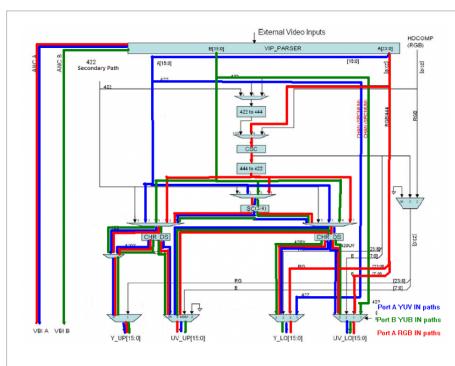

- HDVPSS supports two independently configurable external video input capture ports.Each video input capture port can be operated as one 16/24-bit input channel (with separate Y and Cb/Cr inputs) or two clock independent 8-bit input channels (with interleaved Y/C data input). Embedded sync and external sync modes are supported for all input configurations.

- The video capture port channel shall support de-multiplexing of both pixel-to-pixel and line-to-line multiplexed streams. It could support upto 16 D1 or 32 CIF multiplexed mode capture. It could also support upto 2 channel 1080p60 capture.

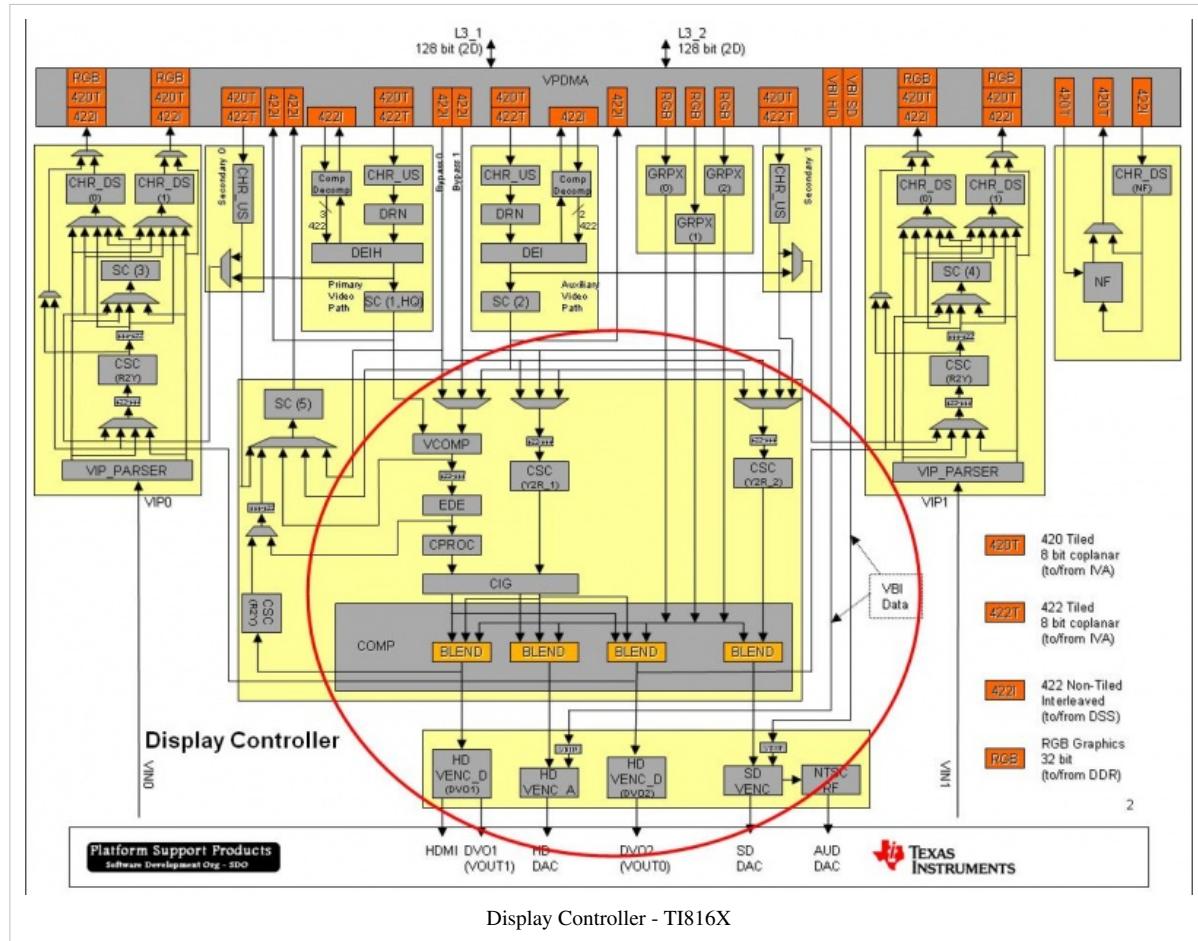

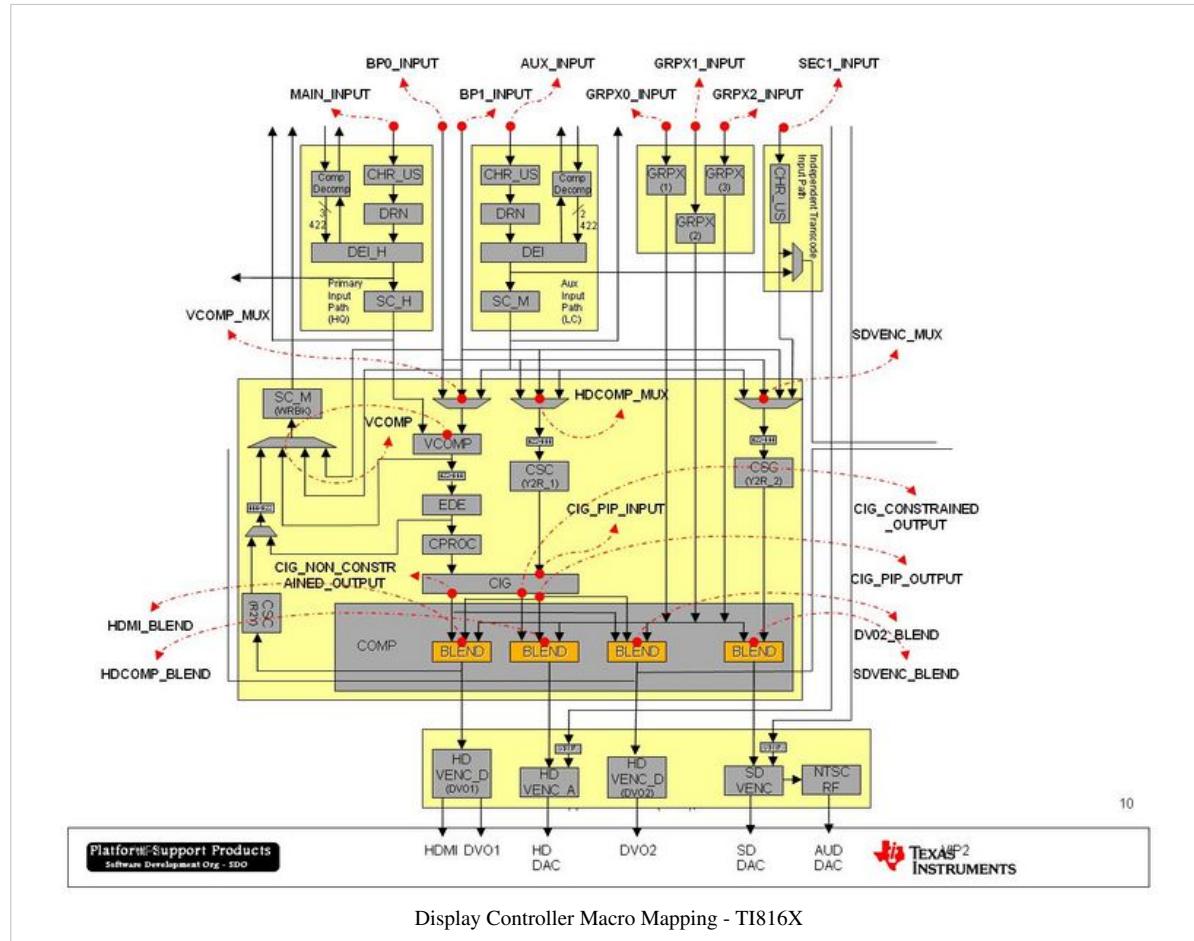

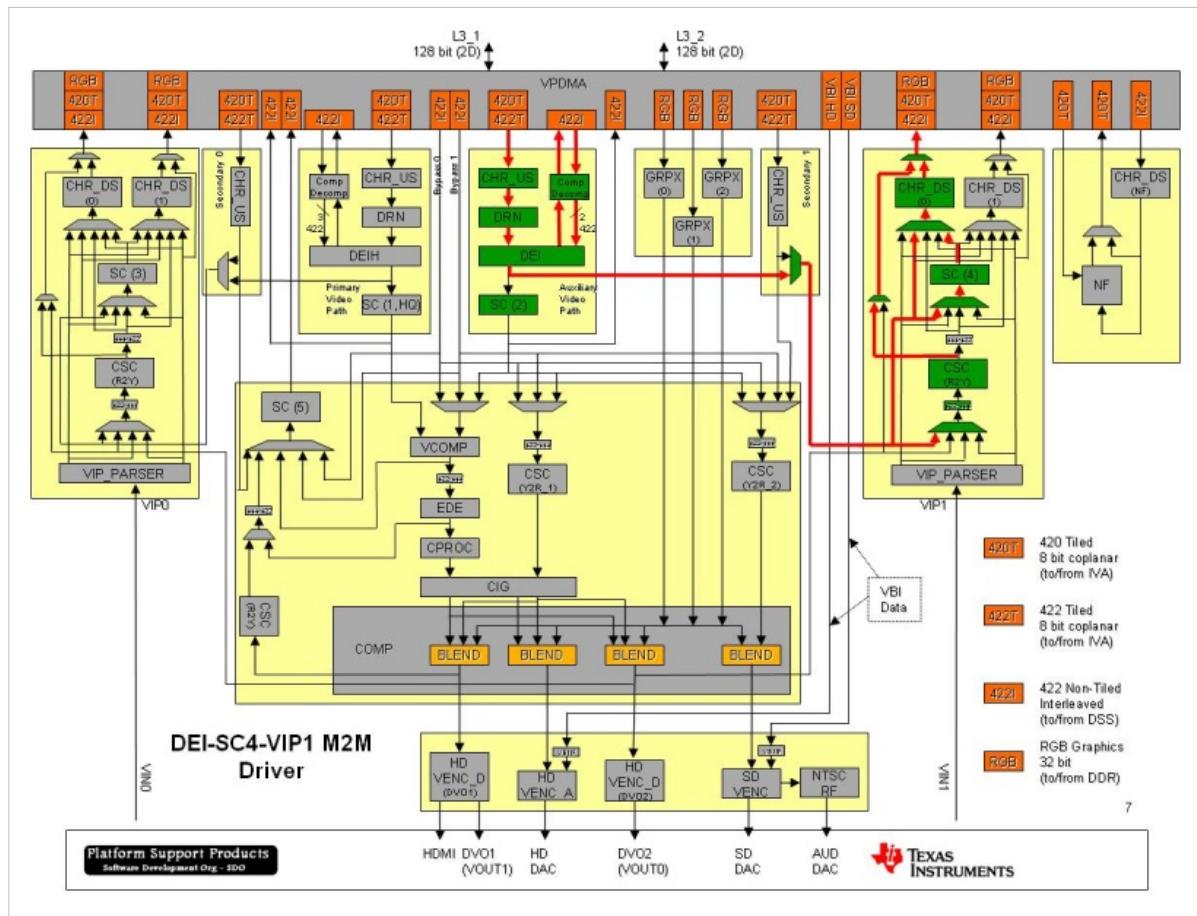

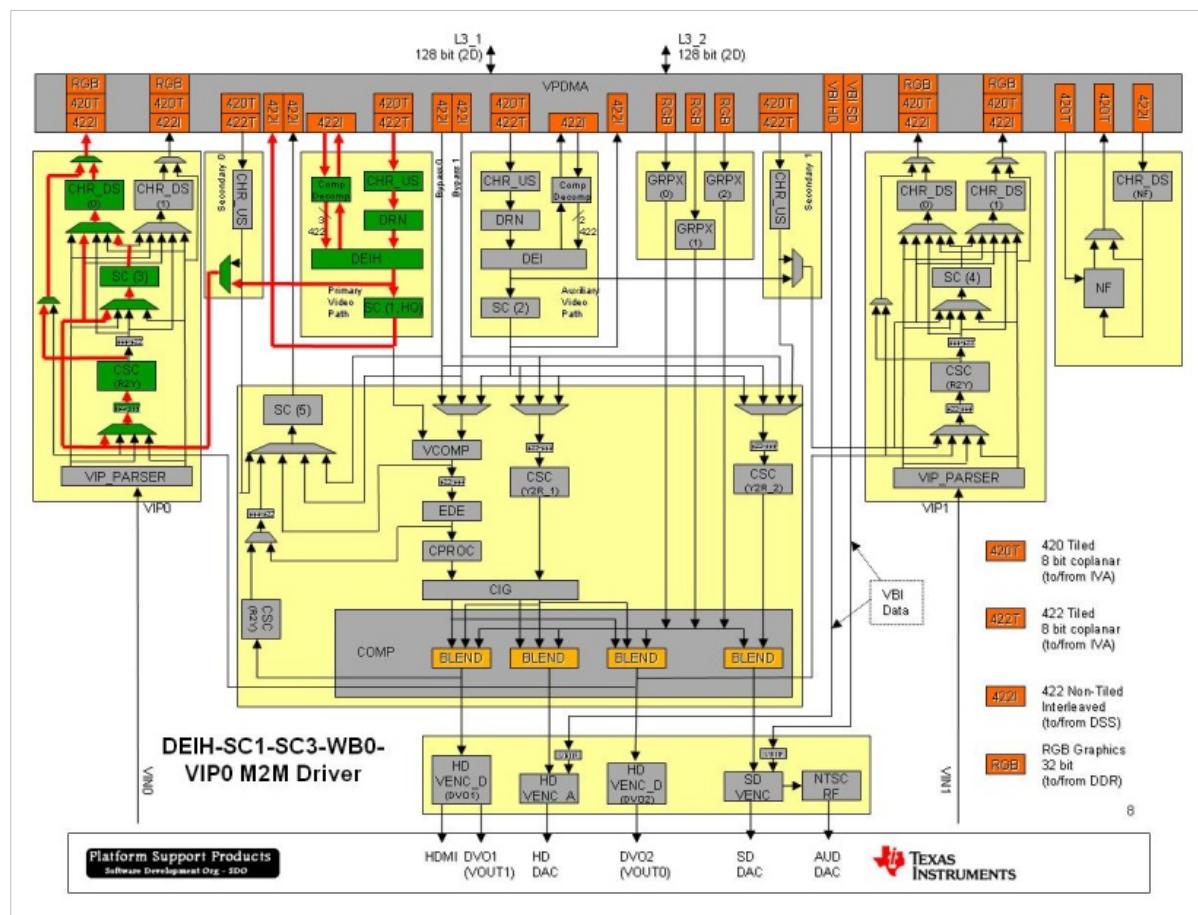

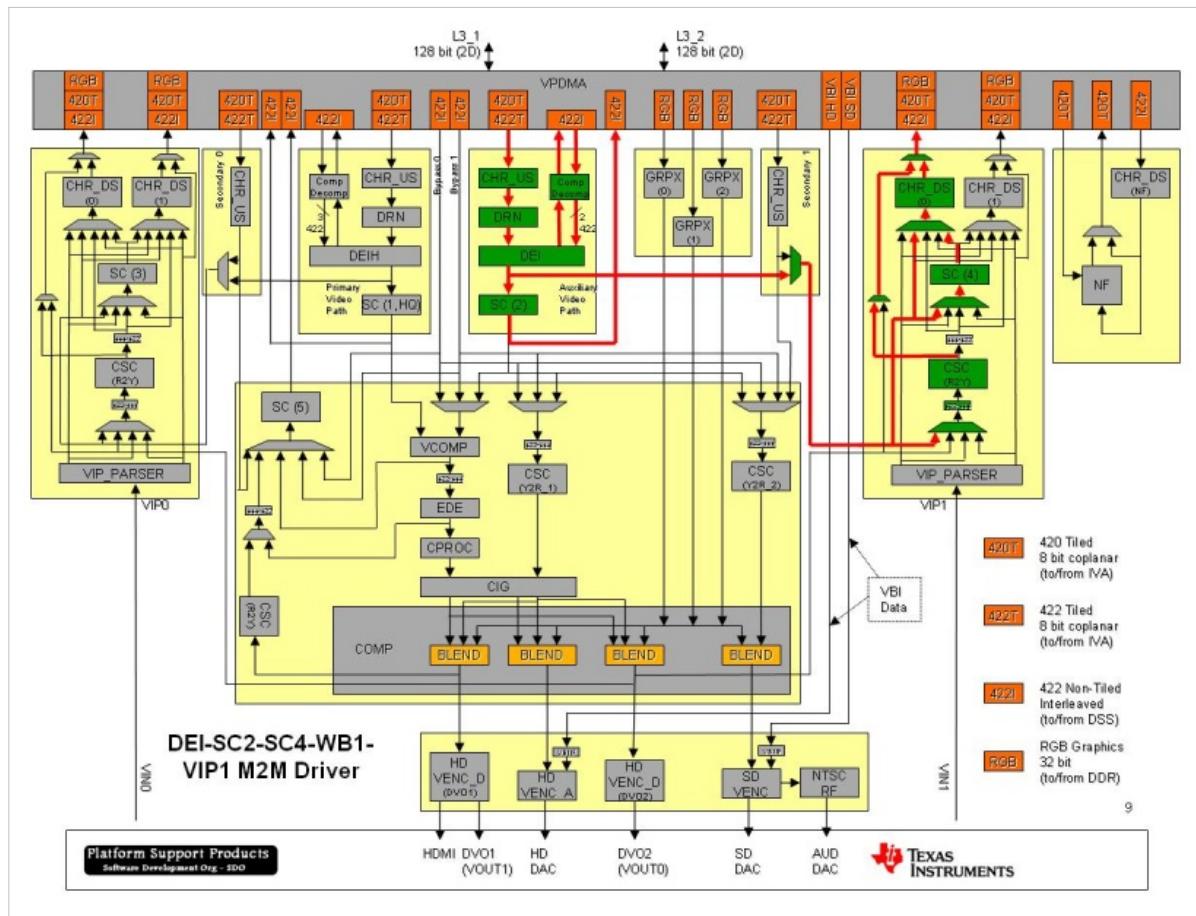

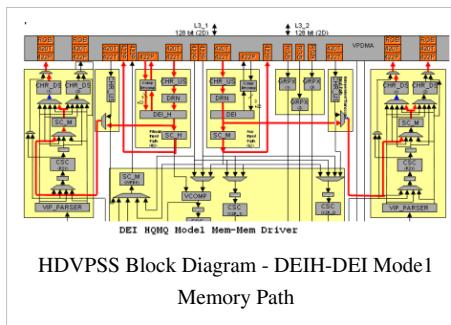

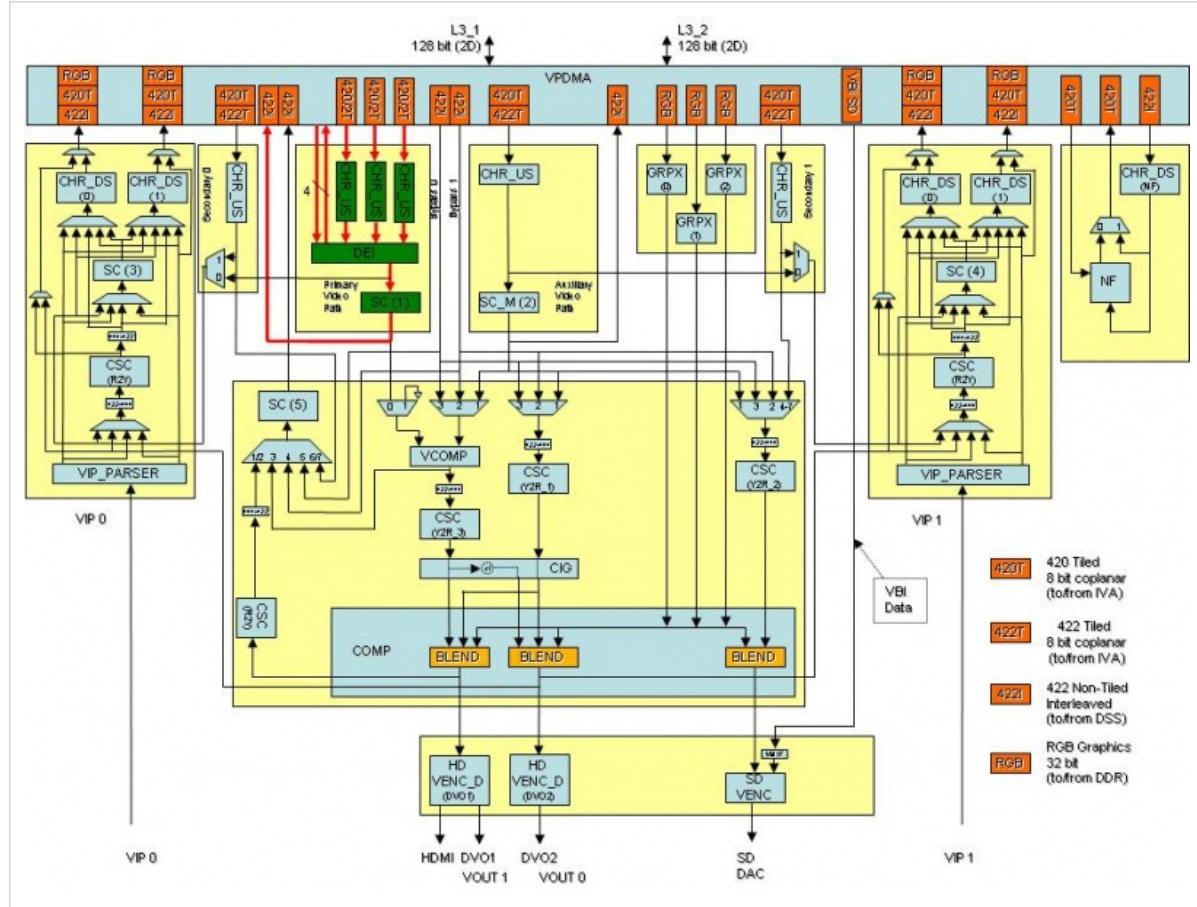

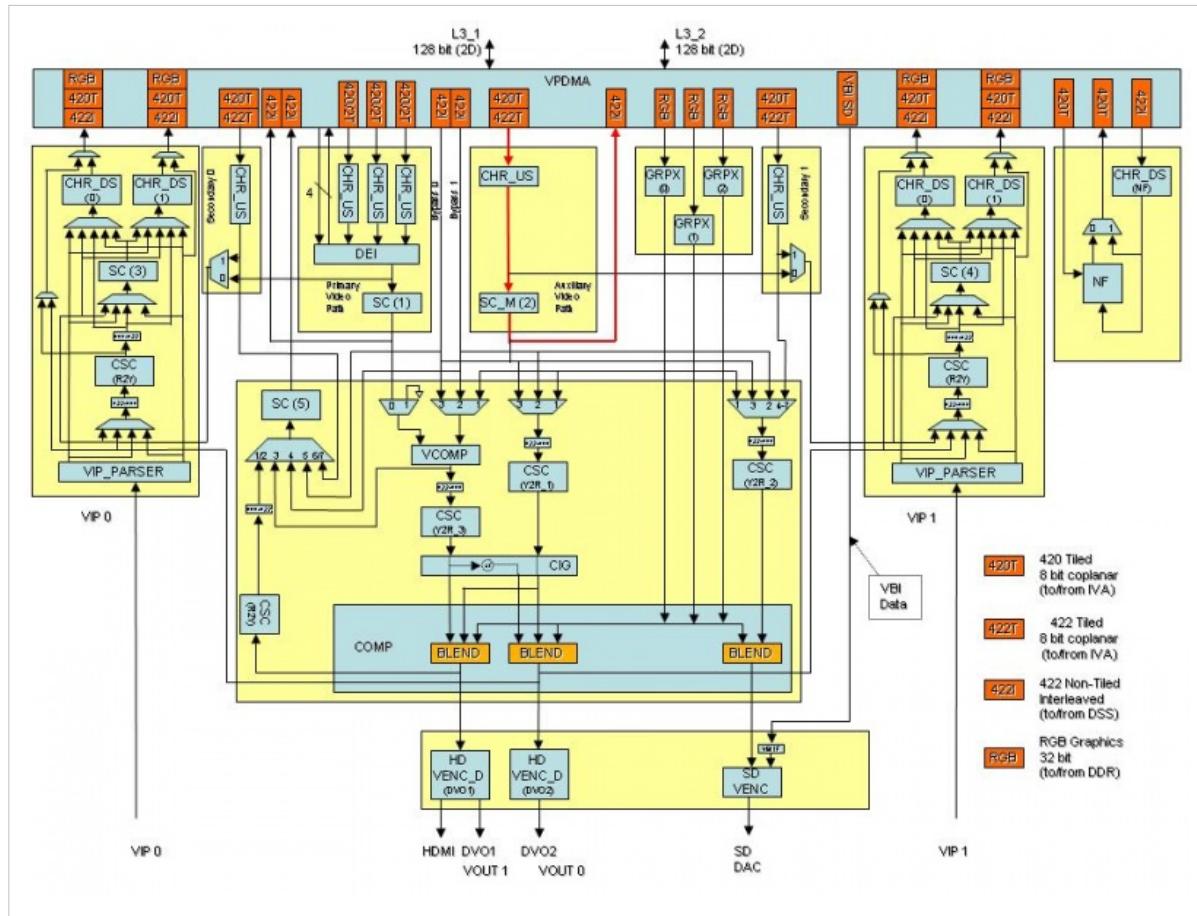

## HDVPSS Block Diagram

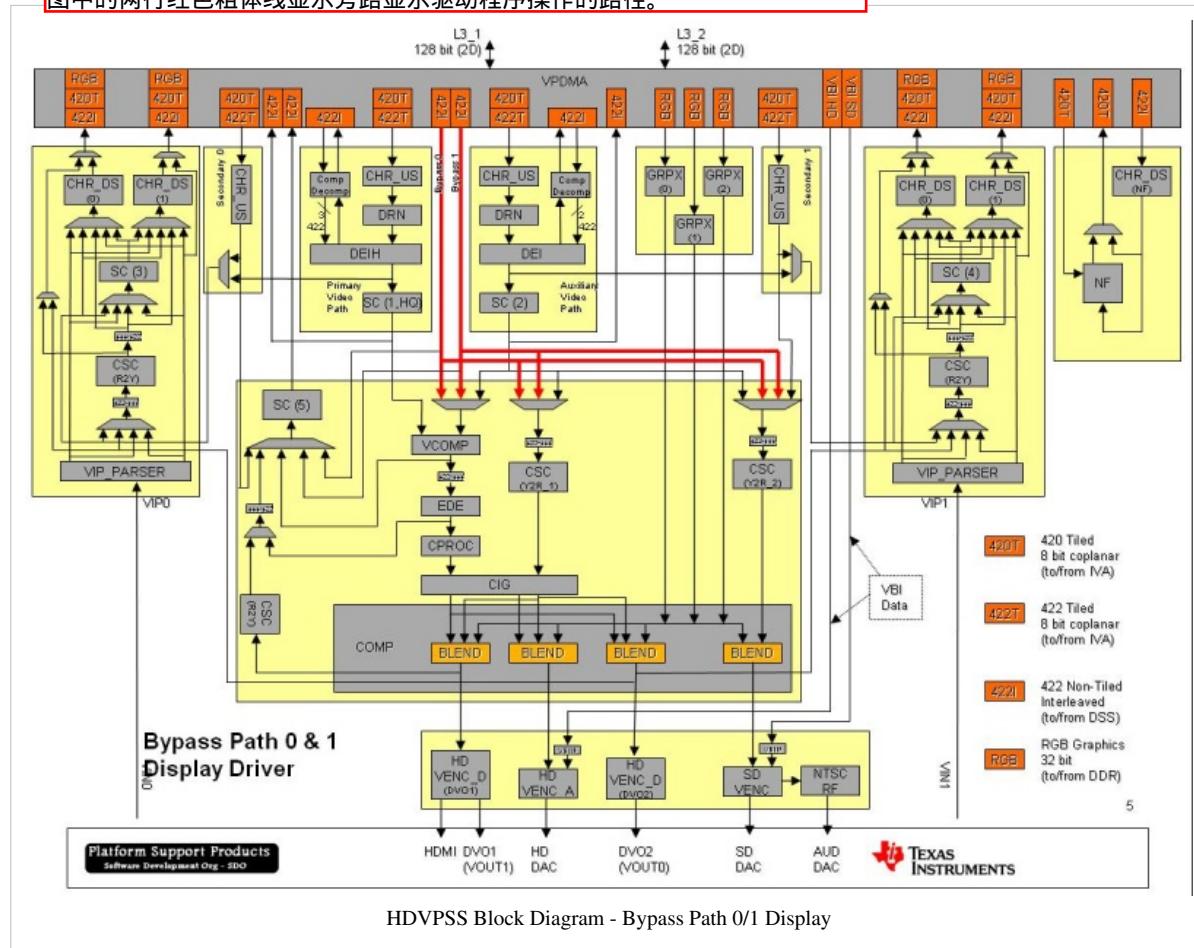

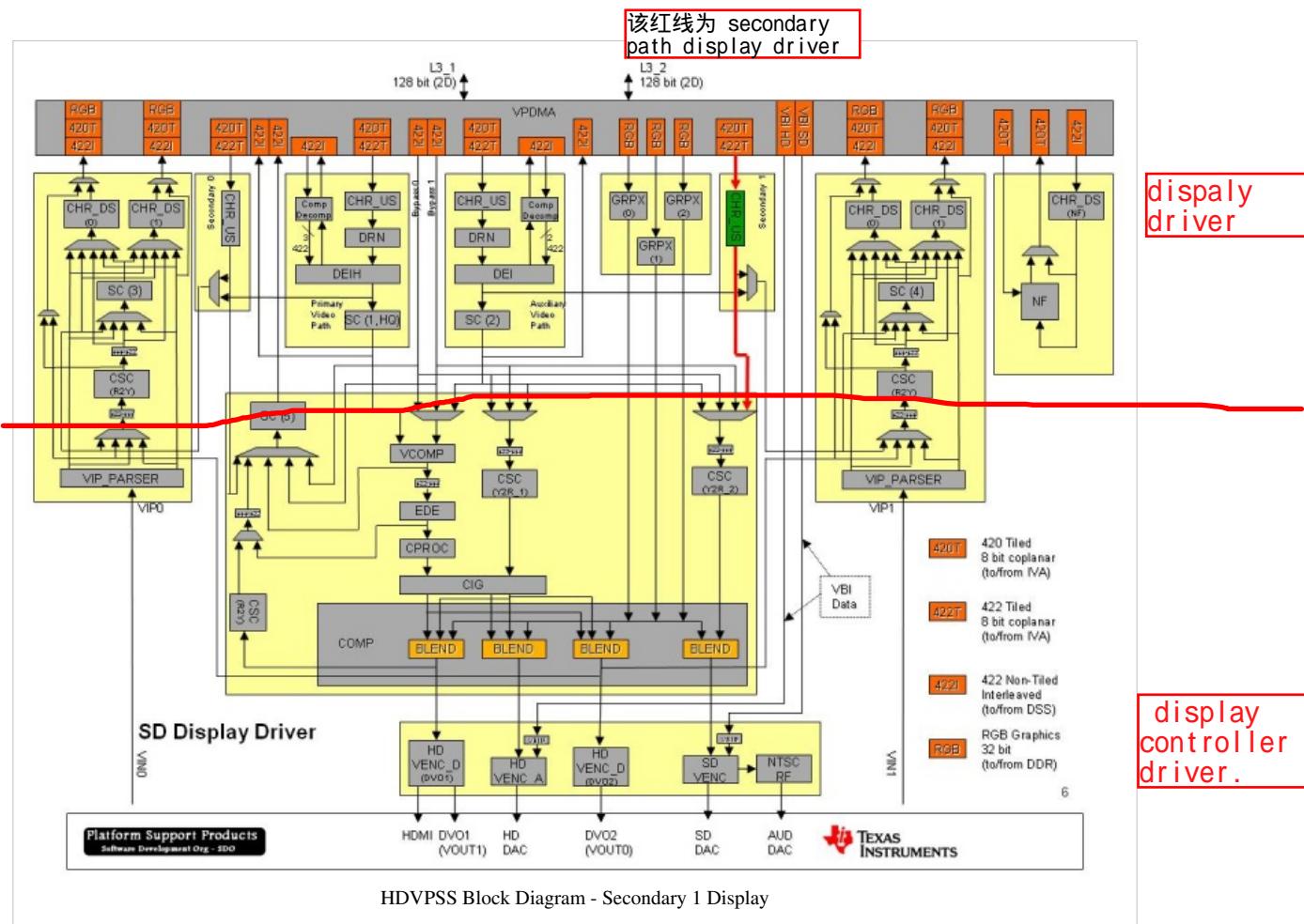

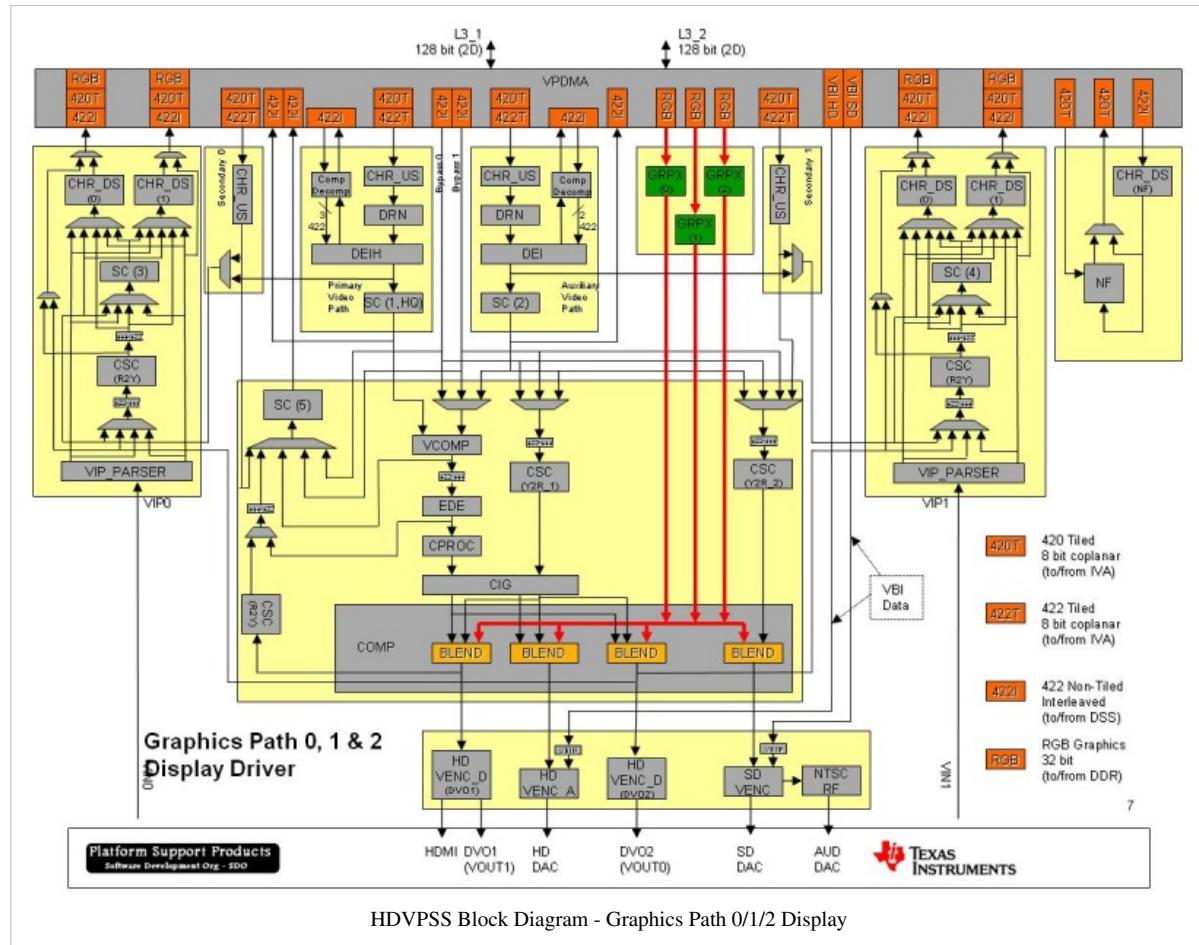

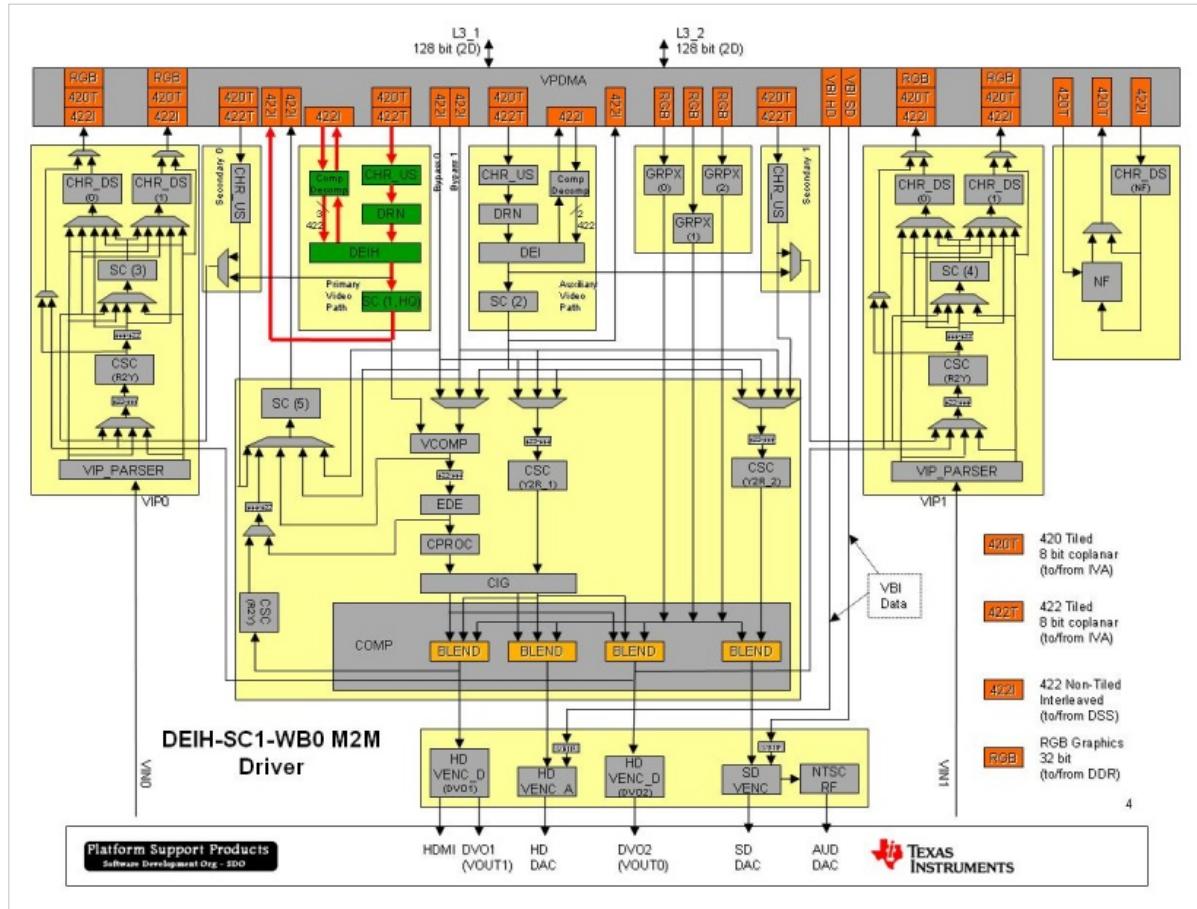

Below figure shows the full blown block diagram of the HDVPSS. Driver uses this diagram to point out the paths used by respective drivers for the different HDVPSS components.

### DEI\_H

The DEI\_H (High Quality De-interlacer) is primarily used to convert interlaced video source material to progressive form. This particular module incorporates features such as Temporal Noise Reduction, 4 and 5 field motion detection and very fine edge detection capabilities to produce a very high quality deinterlaced output. In addition, it performs film mode detection and film mode deinterlacing. It can perform deinterlacing on up to 1080i video input source, producing 1080p video output.

### DEI\_M

The DEI (De-interlacer) is primarily used to convert interlaced video source material to progressive form. This particular module is a reduced feature set of the DEI\_H module, in that it does not perform Temporal Noise Reduction and is limited to 4 field motion detection. It performs edge directed interpolation, but utilizes a simpler (and smaller) algorithm compared to the DEI\_H module. In addition, it performs film mode detection and film mode deinterlacing. It can perform deinterlacing on up to 1080i video input source, producing 1080p video output.

## **CHR\_US**

The CHR\_US (Chroma Upsampler) converts YUV420 data format input to YUV422 data format output.

## **DRN**

The DRN (De-Ringing) applies a de-ringing algorithm on input video data to reduce noise.

## **SC\_H**

The SC\_H (High Quality Scaler) takes the data from the upstream module. The input image is resized to the desired output size. The module sends the output image to the downstream module. It can scale full HD (1080p) and output full HD (1080p) and uses edge-directed vertical scaling to create a high quality result.

## **SC\_M**

The SC\_M (Scaler) takes the data from the upstream module. The input image is resized to the desired output size. The module sends the output image to the downstream module. It can scale full HD (1080p) and output full HD (1080p).

## **VCOMP**

The VCOMP (Video Compositor) module composites two sources of input video over a background color layer. Both input sources are in 4:2:2 YUV format. The output of the module is also 4:2:2 YUV.

## **EDE**

The EDE (Edge Detail Enhancer) module performs edge detail enhancement on the input video source.

## **CPROC**

Color processing is to provide

- color space conversion,

- dynamic contrast control, and

- color-related processing such as flesh tone detection, memory color enhancement, white point control.

Advanced color processing is performed in the CIE Color Appearance Model 2.0 (CIECAM 2.0).

## **CIG**

The CIG module takes in a single non-constrained video and generates following two outputs:

- The same non-constrained video which may optionally be interlaced

- The same or constrained version of the source video which may optionally interlaced

The first output is sent to the HDMI digital output (via COMP/HD\_VENC\_D) and the second output is sent to the analog HD component output (via COMP/HD\_VENC\_A). In addition, the CIG modules takes in a second video input and positions the video in a full display output screen if the input video is a PIP sized.

## **CSC**

The CSC (Color Space Conversion) converts from either YUV444 format to RGB format or RGB format to YUV444 format.

## **COMP**

The COMP (Compositor) blends video from the two video sources with the Graphics sources (GRPX) to form the final video streams going to the three video encoders. COMP has independent compositor/blender, each of them could upto 5 input layers ( 2 video and 3 graphics).

## **GRPX**

GRPX is a region-based graphics processor that composes one or more graphics regions to create a display plane input for the video compositor. Regions are rectangular in size. GRPX module could handle multiple rectangular “regions” and composite them into one full screen sized image. GRPX inserts blank pixel data (zero pixel) where region data is unavailable. It supports color formats on Graphics pipeline: RGB565, ARGB1555, RGBA5551, ARGB4444, RGBA4444, ARGB6666, RGBA6666, RGB888, ARGB8888 and RGBA8888, Palette of 1/2/4/8 bits per pixel.

## **HD\_VENC\_D\_DVO1**

The HD\_VENC\_D\_DVO1(High Definition Video Encoder HDMI/DVO1) converts internally processed video to both an HDMI format or DVO format.

## **HD\_VENC\_A**

The HD\_VENC\_A (High Definition Video Encoder Analog) converts internally processed video to Component format

## **HD\_VENC\_D\_DVO2**

The HD\_VENC\_D\_DVO2 (Hish Definition Video Encoder DVO2) converts internally processed video to DVO format

## **SD\_VENC**

The SD\_VENC (Standard Definition Video Encoder) converts internally processed video to composite, S-Video and component format outputs.

## **NTSC\_RF**

The NTSC\_RF (NTSC R/F Modulator) performs R/F modulation on the output of the SD\_VENC

## **VIP (PARSER)**

The VIP Parser (Video Input Port Parser) provides an input for external video sources. Each Video Input Port can receive from 16 CIF streams to 1 1080p60 streams. There are two instance of VIP Parser.

## **CHR\_DS**

The CHR\_DS (Chroma Downampler) converts YUV422 data format input to YUV420 data format output.

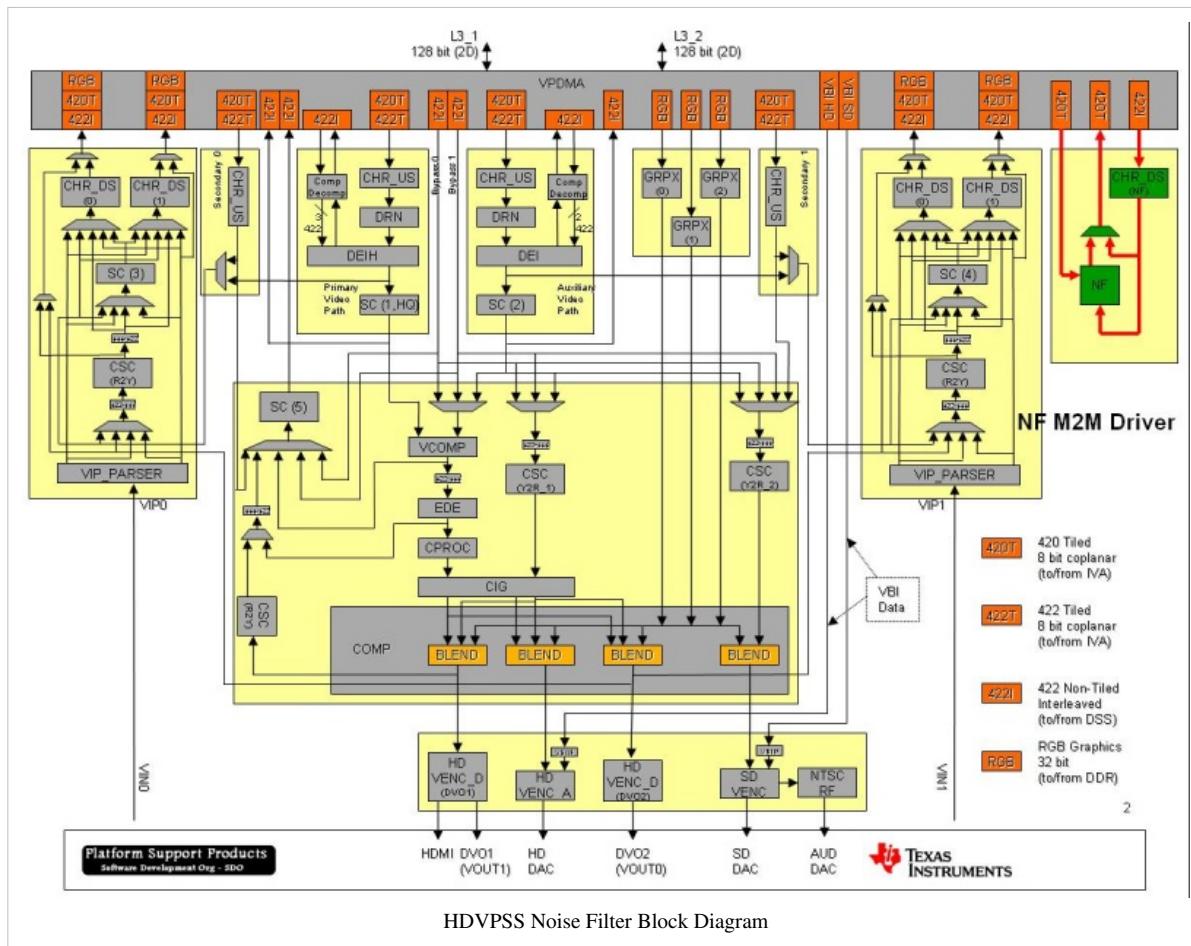

## **NF**

The NF (Noise Filter) performs a memory to memory spatial/temporal noise filter algorithm on a 422 raster input source and produces a 420 tiled output source. Its primary use mode is part of the Video Input Port processing.

## COMP/DECOMP

COMP/DECOMP (Compress/Decompress) are modules that are used to perform compression on DEI private YUV422 private data outbound and decompression on inbound DEI private YUV422 data.

## VPDMA

The VPDMA shall be capable of transporting data to and from an external memory location, most often an EMIF, buffering this data and then delivering the data as demanded to Application Modules as programmed.

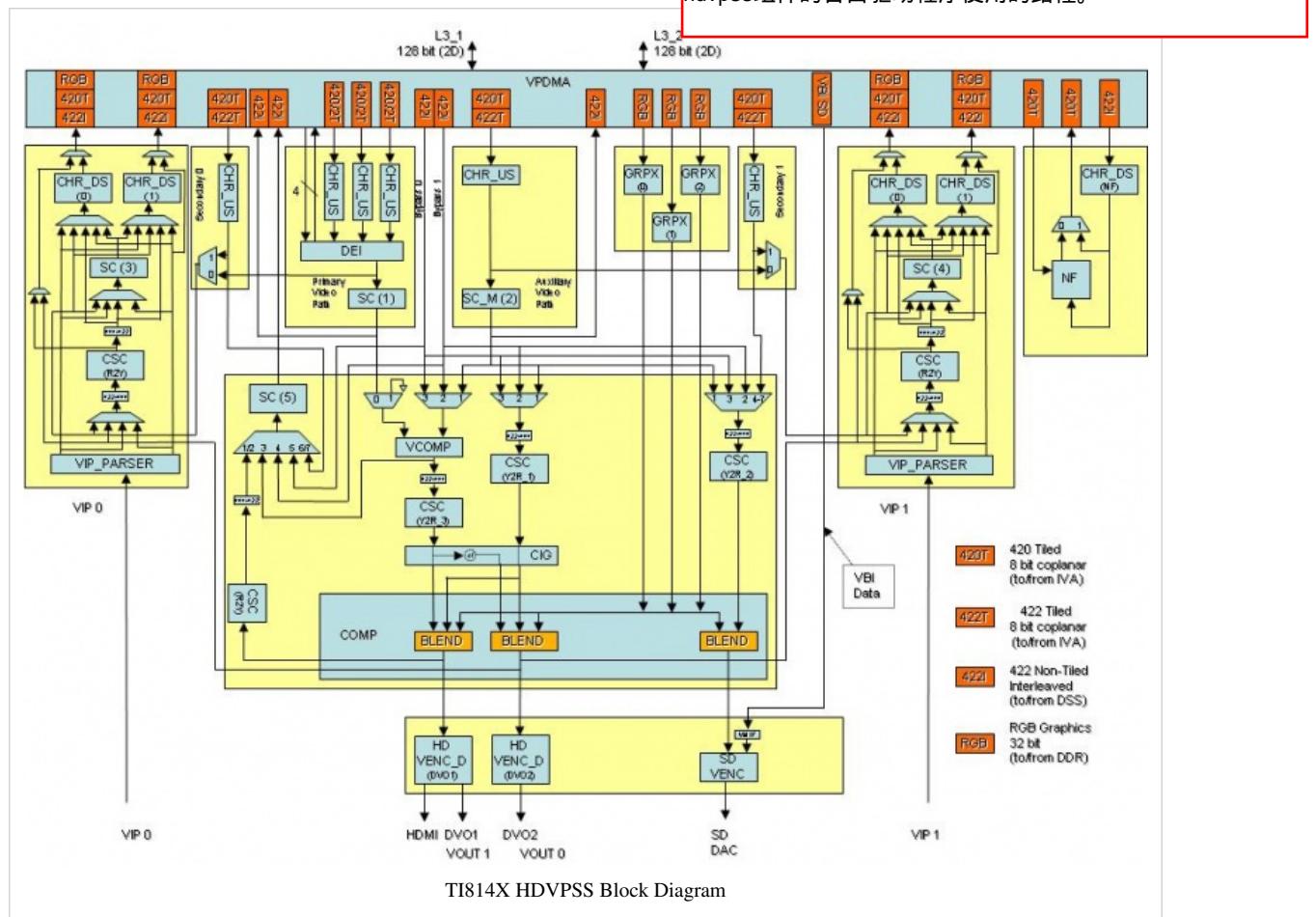

# T1814X-HDVPSS-HW Overview

## TI814X/TI8107 HDVPSS Hardware Introduction

显示子系统包括使用最新TI开发算法的视频显示处理模块、灵活的合成和混合引擎、全方位的外部视频接口，以便向终端设备提供高质量的视频内容。本文件除SD相关需求外，还涵盖了与HD相关的各个方面的要求。每个组件以及其在ti814x显示子系统概述文档中的特性都将得到详细解释。

The display sub system includes video display processing modules using the latest TI developed algorithms, flexible compositing and blending engine, full range of external video interfaces in order to deliver a high quality video contents to the end devices. This document covers various aspects of HD-related requirements in addition to SD-related requirements.

Each of the components are explained in detail along with its features in the TI814x display subsystem overview documents.

## HDVPSS Features

**Few top features** are mentioned below:

- The HDVPSS supports HD (up to 1080p) and SD (NTSC/PAL) outputs simultaneously

- The HDVPSS handles both video and graphics efficiently to create high-quality user interfaces. This includes (but not limited to) deinterlacing, scaling, noise reduction, alpha blending, chroma keying, flicker filtering, and pixel format conversion.

- It supports tiled and raster data formats, scan format conversion, aspect-ratio conversion, and frame size conversion. 它支持平铺和栅格数据格式。

- The HDVPSS generate secure video signal with proper content protection mechanisms, i.e., HDCP and Macrovision/CGMS-a for digital and analog outputs, respectively. hdvpss产生安全的视频信号，并具有适当的内容保护机制，即HDCP和宏视觉/CGMS-a，分别用于数字和模拟输出。

- Three independently controlled compositors (HDMI, DVO2, SD) is supported.

- TI8107 supports four compositors (HDMI, HDCOMP, DVO2, SD) is supported.

- Two parallel video processing pipelines (main and aux) for concurrent video stream processing is supported.

- Both the main and auxiliary video pipelines shall include a write-back path to the external memory to support memory to memory scaling of video frames independently from the display output frame timing.

- It supports three graphics plane and include an up/down scaler optimized for graphics application with each graphics path.

- HDVPSS supports two independently configurable external video input capture ports. Each video input capture port can be operated as one 16/24-bit input channel (with separate Y and Cb/Cr inputs) or two clock independent 8-bit input channels (with interleaved Y/C data input). Embedded sync and external sync modes are supported for all input configurations.

- The video capture port channel shall support de-multiplexing of both pixel-to-pixel and line-to-line multiplexed streams. It could support upto 16 D1 or 32 CIF multiplexed mode capture. It could also support upto 2 channel 1080p60 capture. 视频捕获端口通道应支持像素对像素和逐行复用流的解复用。它可以支持多达16 d1或32 cif复用模式捕获，还可以支持最多2通道1080p60捕获。

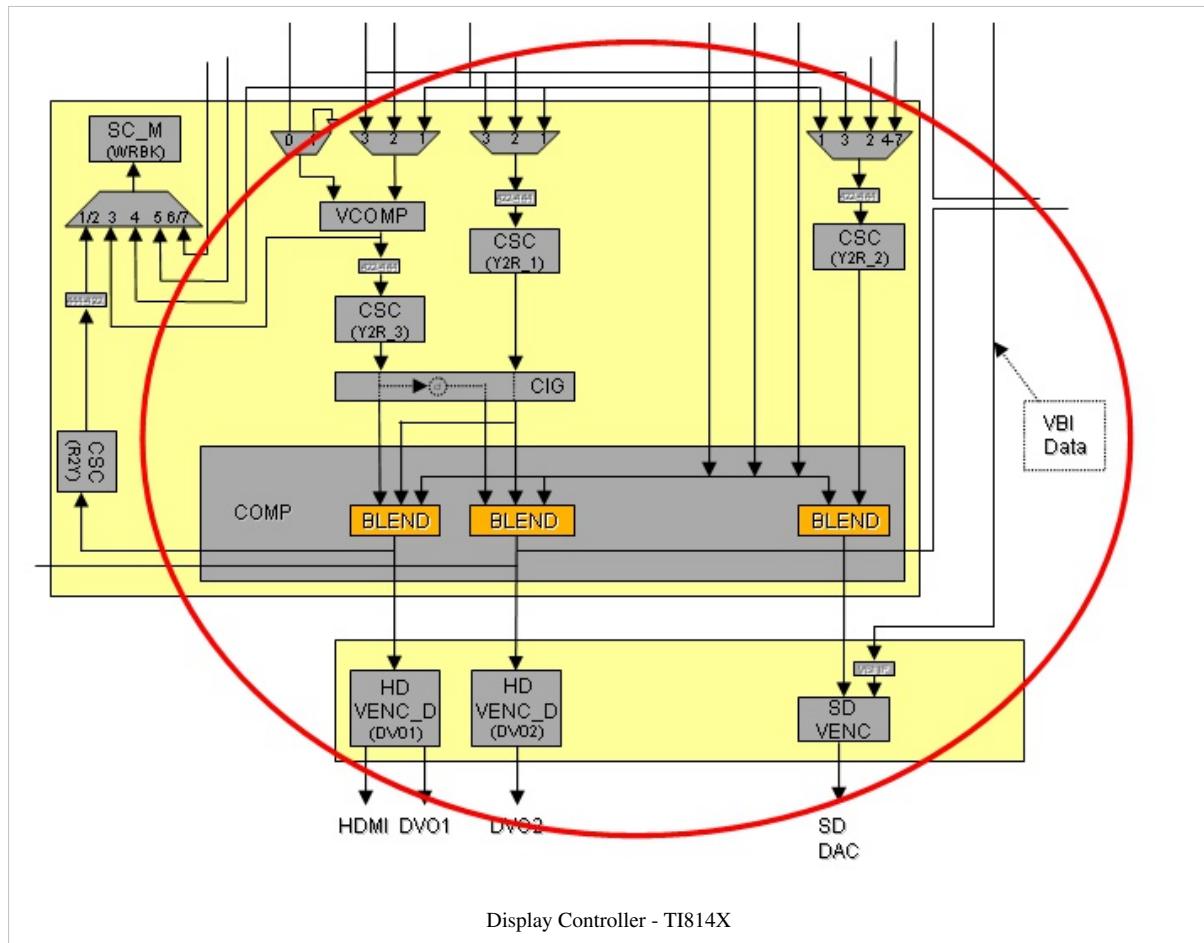

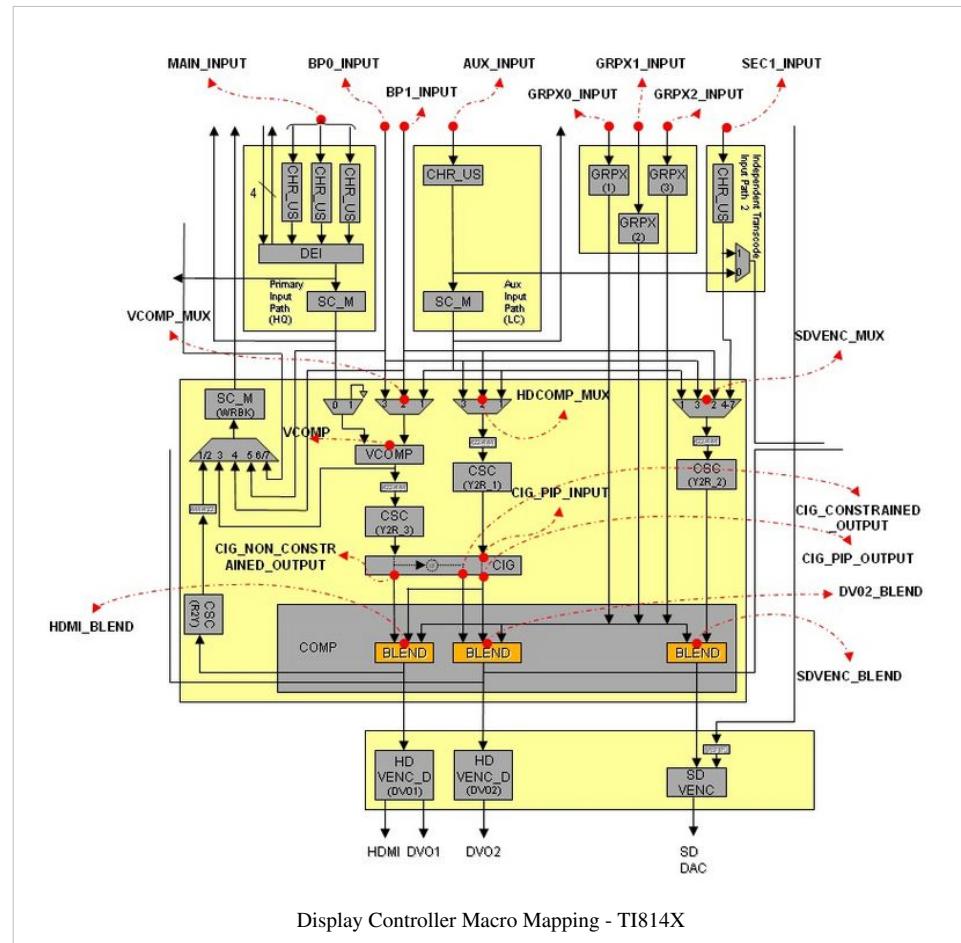

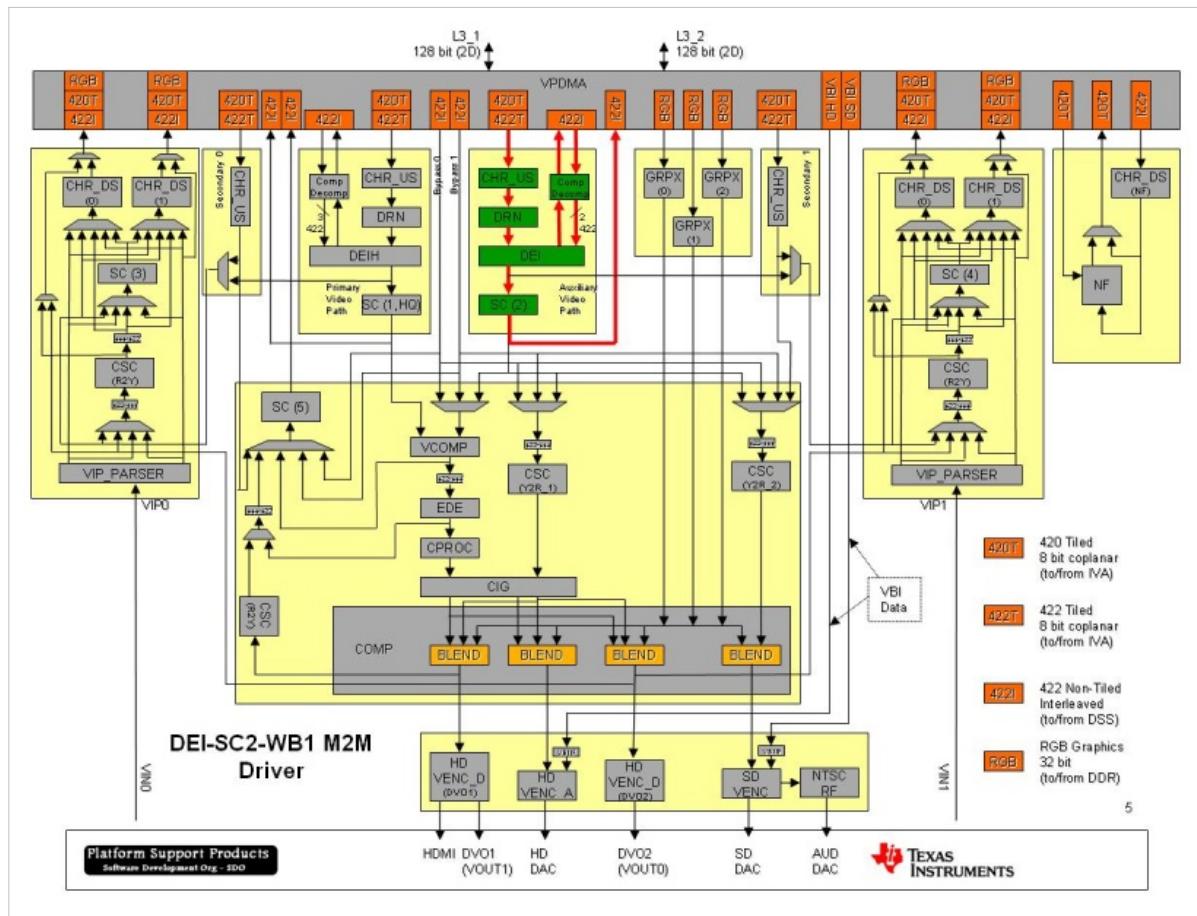

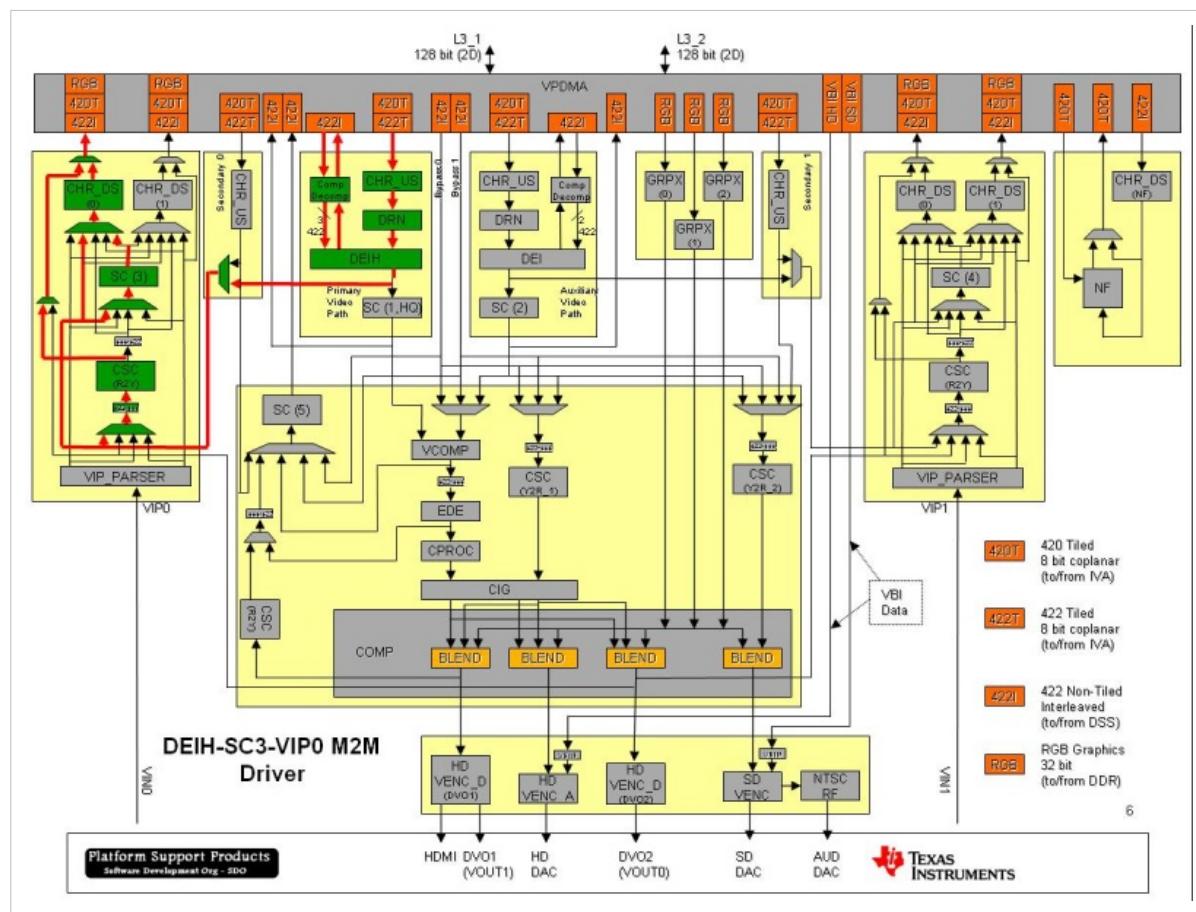

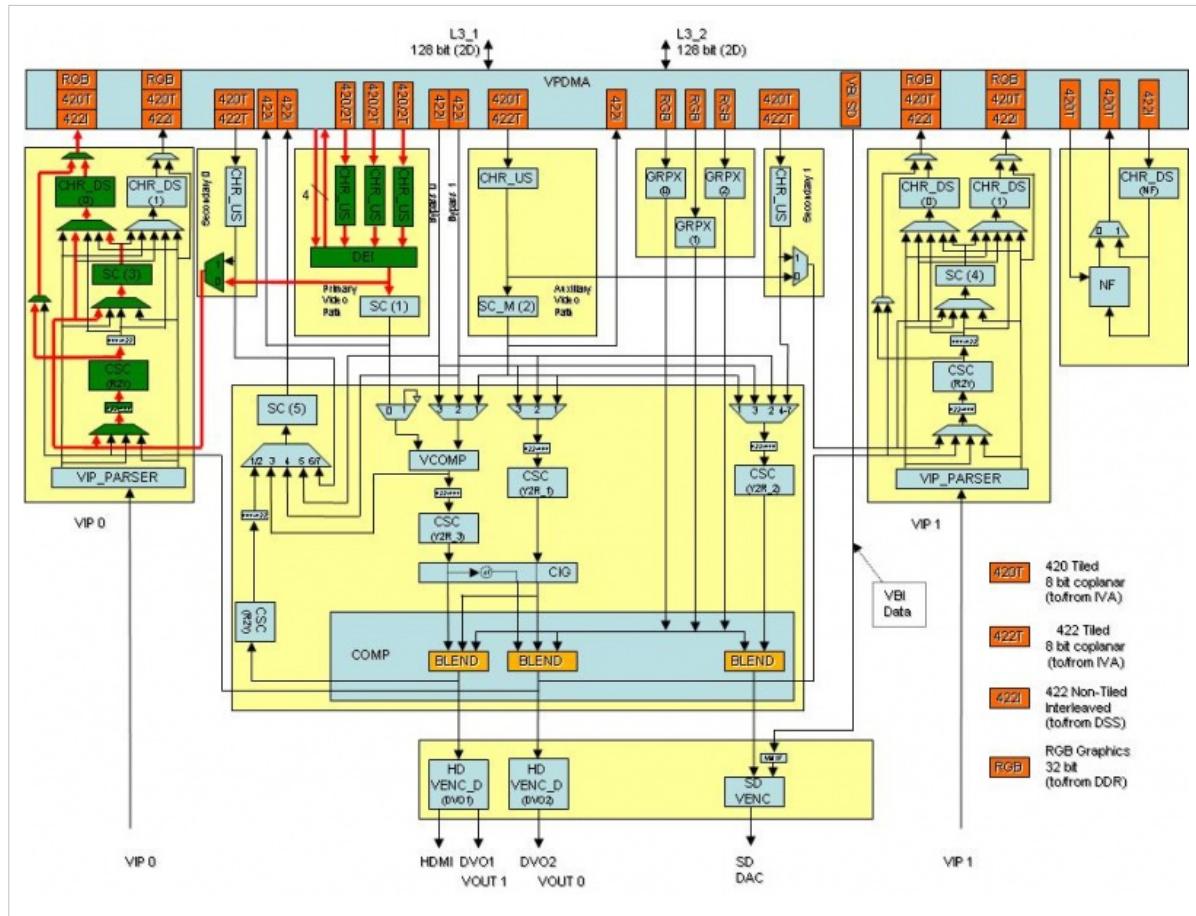

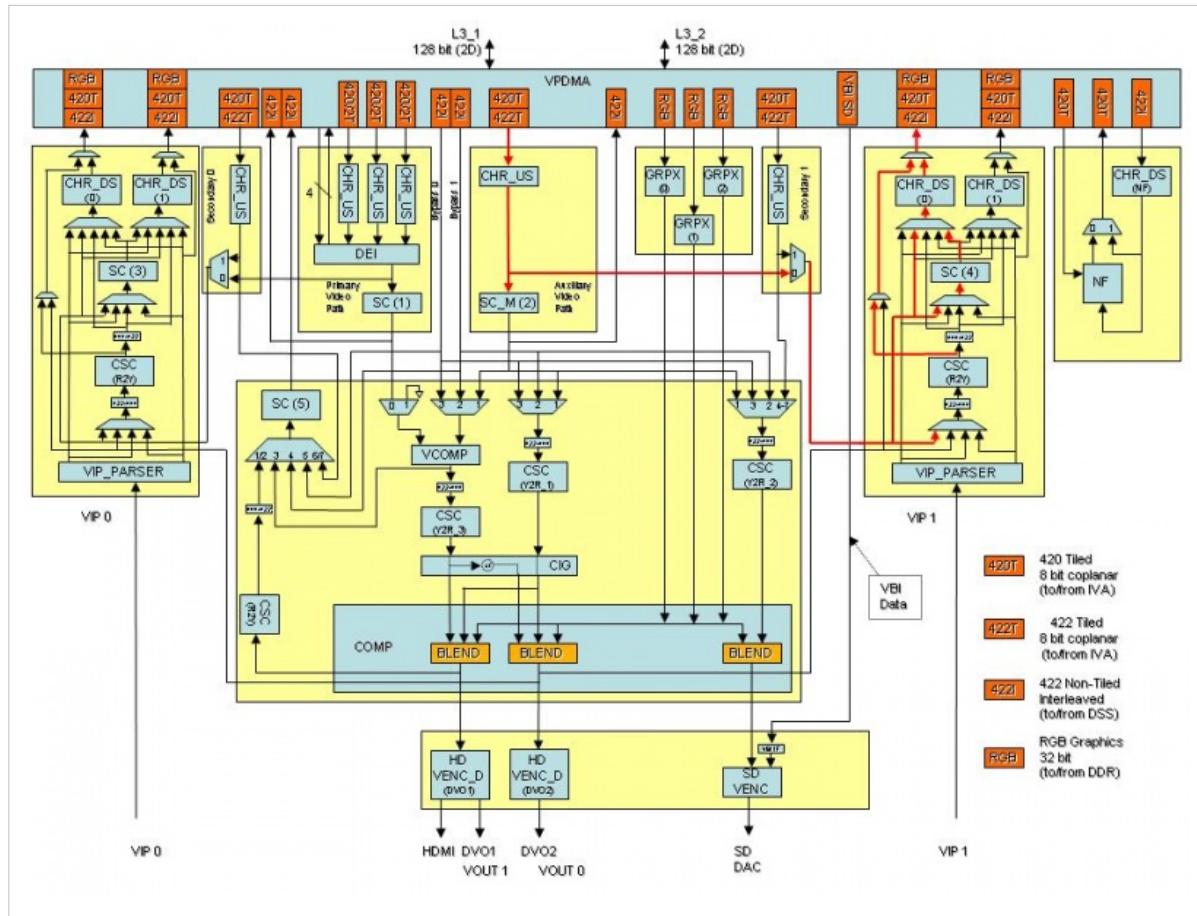

## TI814x HDVPSS Block Diagram

Below figure shows the full blown block diagram of the HDVPSS. Driver uses this diagram to point out the paths used by respective drivers for the different HDVPSS components.

下图显示了hdvpss的完整框图。驱动程序使用此图指出不同hdvpss组件的各自驱动程序使用的路径。

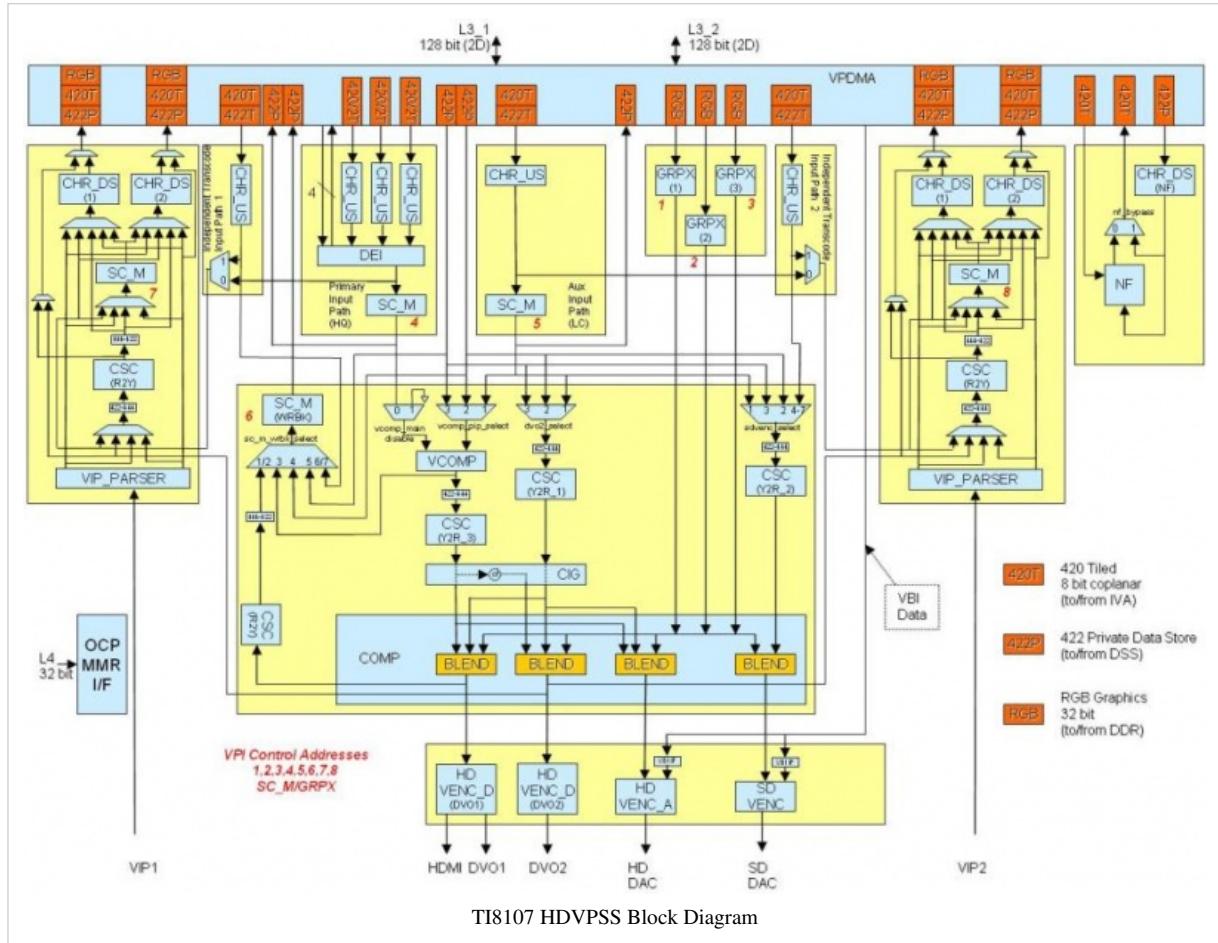

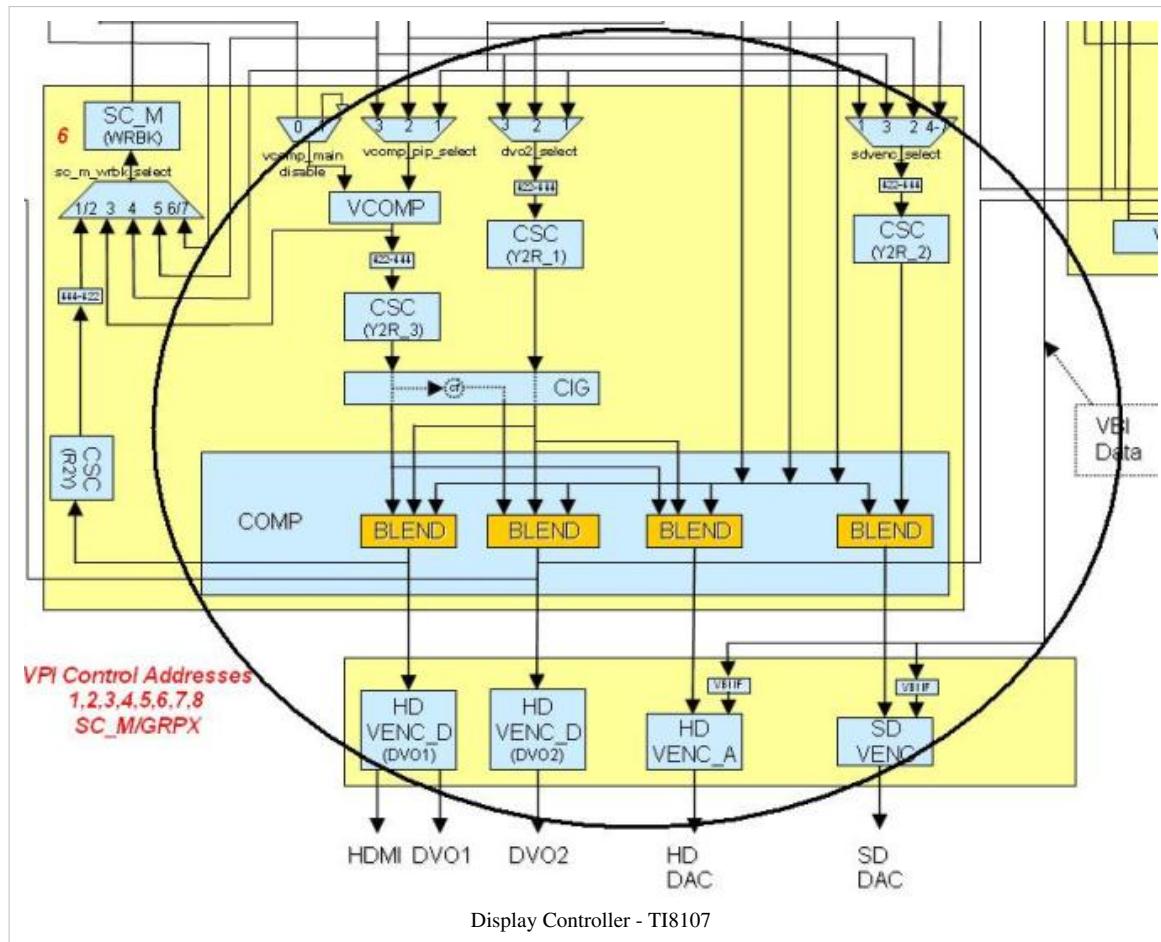

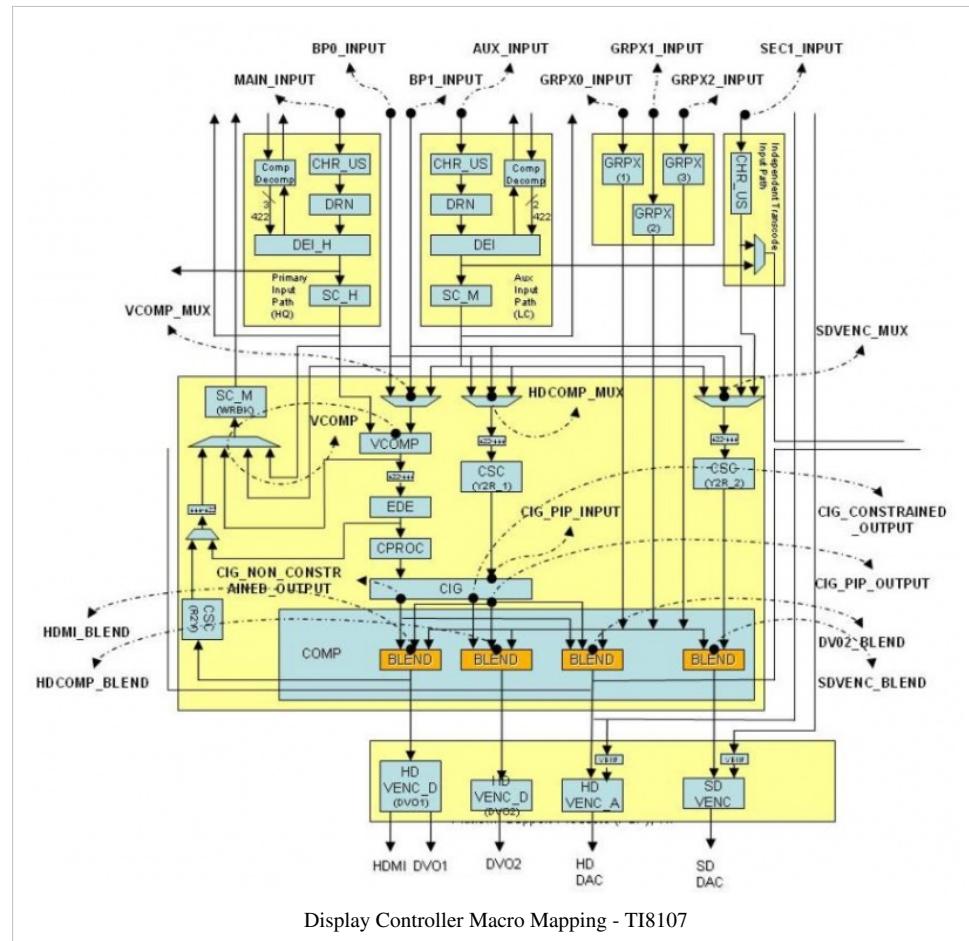

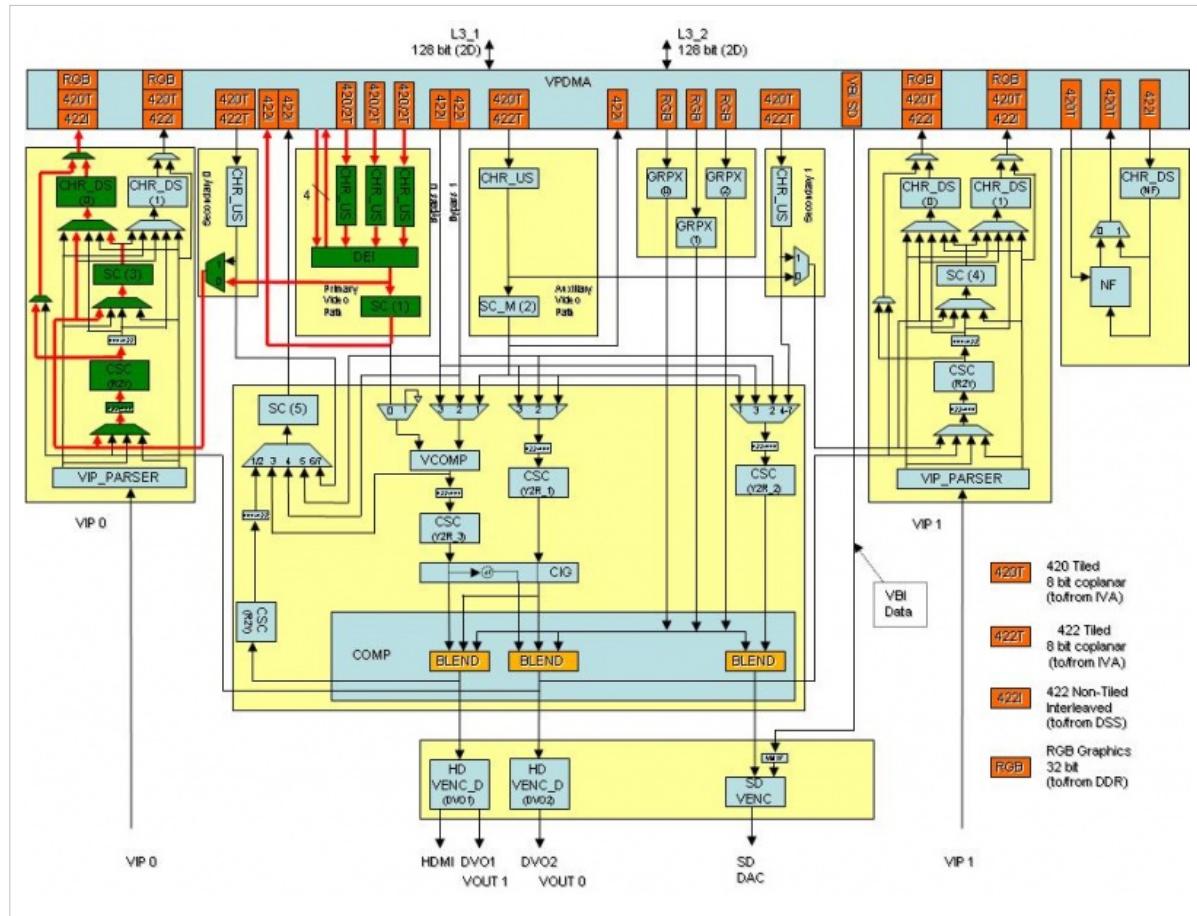

## TI8107 HDVPSS Block Diagram

Below figure shows the full blown block diagram of the HDVPSS. Driver uses this diagram to point out the paths used by respective drivers for the different HDVPSS components.

### DEI

The DEI (De-interlacer) is primarily used to convert interlaced video source material to progressive form. Performs motion adaptive de-interlacing. Supports 4 field motion detection. It performs edge directed interpolation, detects edges in seven direction in 2X7 window. In addition, it performs film mode detection and film mode deinterlacing. It can deinterlace on up to 1080i video input source, producing 1080p video output.

### CHR\_US

The CHR\_US (Chroma Upsampler) converts YUV420 data format input to YUV422 data format output.

## SC

The SC (Scaler) takes the data from the upstream module. The input image is **resized to the desired output size**. The module sends the output image to the downstream module. It can scale full HD (1080p) and output full HD (1080p).

## VCOMP

The VCOMP (Video Compositor) module **composites two sources of input video over a background color layer**. Both input sources are in 4:2:2 YUV format. The output of the module is also 4:2:2 YUV.

## CIG

The CIG module takes in a single non-constrained video and generates following two outputs:

- The same non-constrained video which may optionally be interlaced

- The same or constrained version of the source video which may optionally interlaced

The first output is sent to the HDMI digital output (via COMP/HD\_VENC\_D) and the second output is sent to the analog HD component output (via COMP/HD\_VENC\_A). In addition, the CIG modules takes in a second video input and positions the video in a full display output screen if the input video is a PIP sized.

## CSC

The CSC (Color Space Conversion) converts from either YUV444 format to RGB format or RGB format to YUV444 format.

## COMP

The COMP (Compositor) blends video from the two video sources with the Graphics sources (GRPX) to form the final video streams going to the three video encoders. COMP has independent compositor/blender, each of them them could upto 5 input layers ( 2 video and 3 graphics).

GRPX **grpx是一种基于区域的图形处理器，它由一个或多个图形区域组成，用于为视频排序器创建显示平面输入。** **创建平面输入图形**

GRPX is a region-based graphics processor that composes one or more graphics regions to create a display plane input for the video compositor. Regions are rectangular in size. GRPX module could handle multiple rectangular “regions” and composite them into one full screen sized image. GRPX inserts blank pixel data (zero pixel) where region data is unavailable. It supports color formats on Graphics pipeline: RGB565, ARGB1555, RGBA5551, ARGB4444, RGBA4444, ARGB6666, RGBA6666, RGB888, ARGB8888 and RGBA8888, Palette of 1/2/4/8 bits per pixel.

## HD\_VENC\_D\_DVO1

The HD\_VENC\_D\_DVO1(High Definition Video Encoder HDMI/DVO1) converts internally processed video to both an HDMI format or DVO format.

## HD\_VENC\_D\_DVO2

The HD\_VENC\_D\_DVO2 (Hish Definition Video Encoder DVO2) converts internally processed video to DVO format

## HD\_VENC\_A

This output is supported only on TI8107. The HD\_VENC\_A (High Definition Video Encoder Analog) converts internally processed video to Component format. This output runs in synchronous with either HDMI VENC or DVO2 VENC. It is not possible to run this VENC independently.

### SD\_VENC

The SD\_VENC (Standard Definition Video Encoder) converts internally processed video to composite, S-Video and component format outputs. Only Composite output supported on TI8107.

### VIP (PARSER)

The VIP Parser (Video Input Port Parser) provides an input for external video sources. Each Video Input Port can receive from 16 CIF streams to 1 1080p60 streams. There are two instance of VIP Parser.

### CHR\_DS

The CHR\_DS (Chroma Downampler) converts YUV422 data format input to YUV420 data format output.

### NF

The NF (Noise Filter) performs a memory to memory spatial/temporal noise filter algorithm on a 422 raster input source and produces a 420 tiled output source. Its primary use mode is part of the Video Input Port processing.

vpdma应该能够将数据传输到外部存储器位置，通常是从外部存储器位置，缓冲该数据，然后按编程的要求将数据传送到应用模块。

### VPDMA

The VPDMA shall be capable of transporting data to and from an external memory location, most often an EMIF, buffering this data and then delivering the data as demanded to Application Modules as programmed.

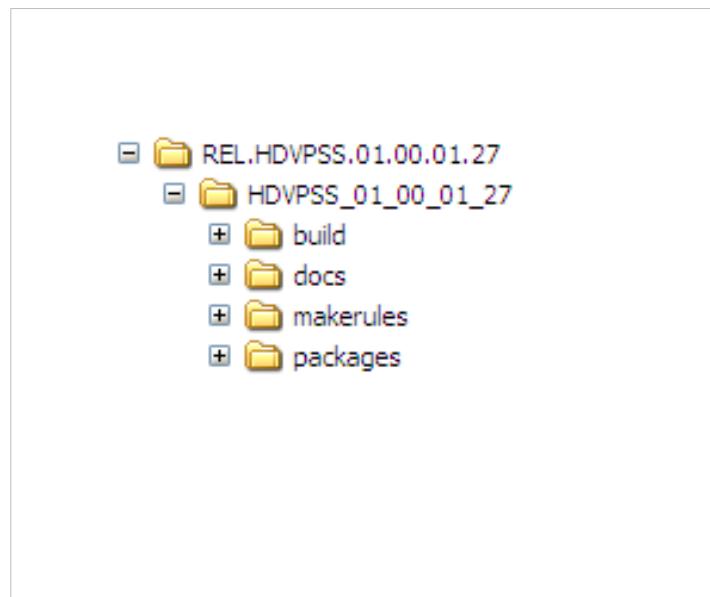

## UserGuideHdvpssFolderOrg

### HDVPSS Code / Directory Organization

#### Top Level

On successful installation of HDVPSS source code, in the installed directory following folders would be created. Lets consider 01\_00\_01.27 versioned release as an example.

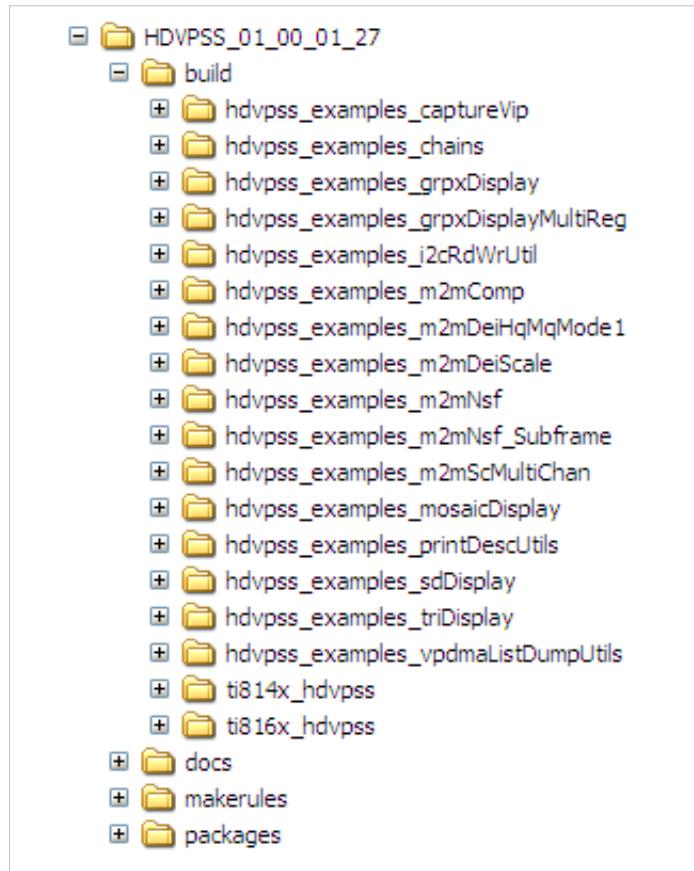

## Build

Build directory essentially holds all the generated binaries and libraries. For each sample application that comes with this HDVPSS release, will have separate folder under build directory. Each example in turn will have platform specific folder, which will hold the binary for that platform.

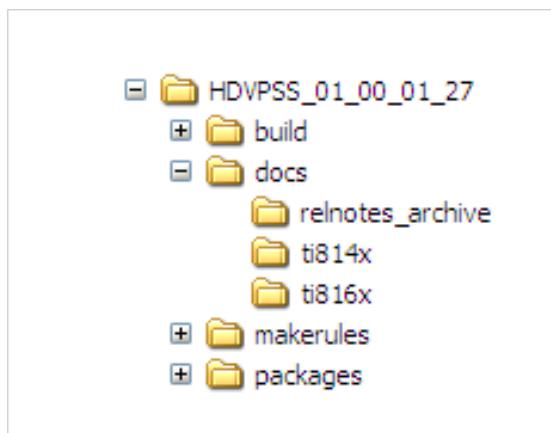

## Docs

The docs folder contains release notes, user guide, API guide, gel files and other for all the platforms. The relnotes\_archive folder contains the user guides for the previous releases. The platform specific folders (such as ti814x, ti8107, ti816x) contains the gels files (for both A8 and M3 cores), binary to configure on-chip HDMI from A8 and other utilities

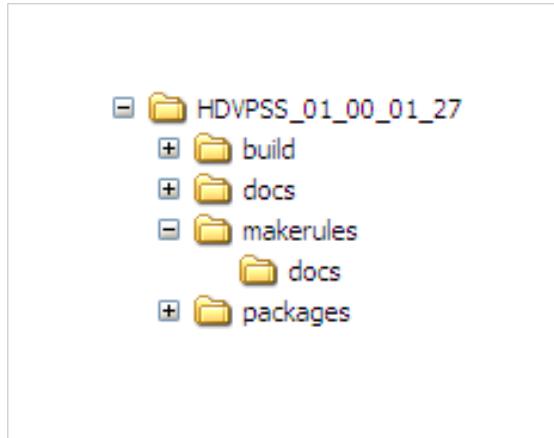

## Makerules

The folder contains the make files required to compile HDVPSS drivers, sample applications and other utilities. The docs folder under makerules folder contain makerules\_spec.doc document that elaborates on the make files used.

## Packages

Detailed in next section - Reducing the indentation by two levels.

## Packages

Is the root folder for all HDVPSS Drivers, the following sections expand on contents of sub-folders.

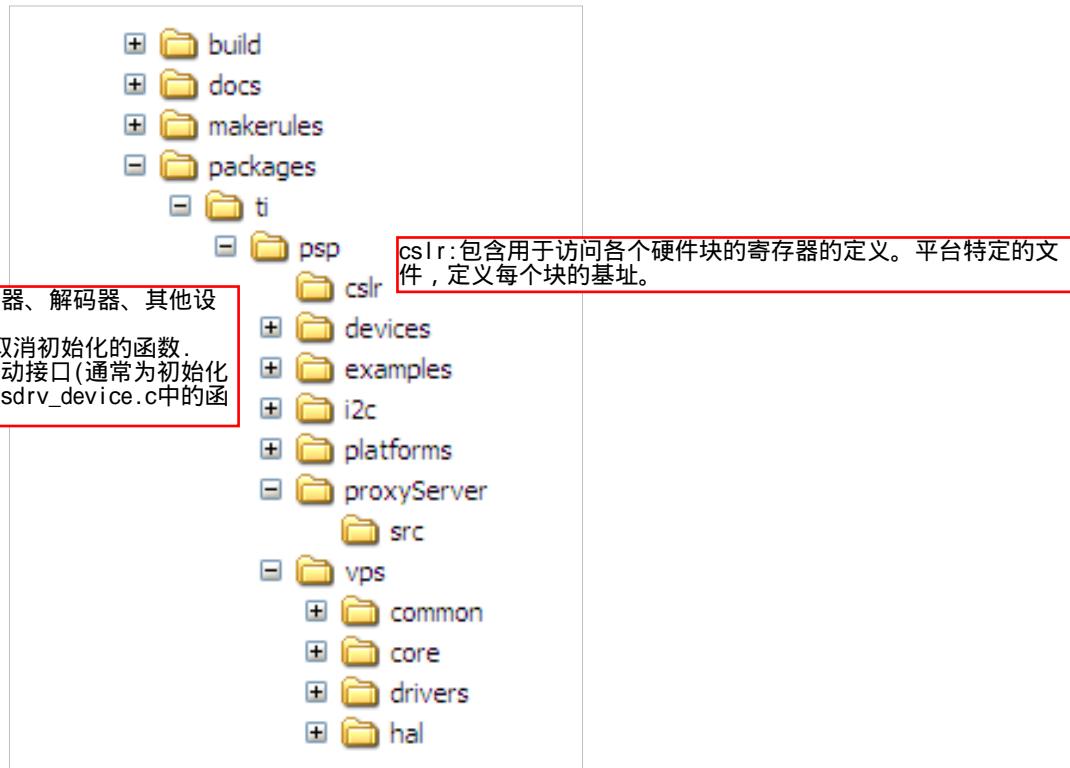

## CSLR

包含用于访问各个硬件块的寄存器的定义。平台特定的文件，定义每个块的基址。

Contains defines that would be used to access registers of the individual hardware blocks. The platform specific file, defines the base address of each of the blocks.

Devices: 包含驱动/功能实现，以控制机载编码器、解码器、其他设备，如tvp 7002、tvp 5158等。

src: 包含初始化受支持的板上设备驱动程序和取消初始化的函数。

Devices设备名文件夹：定义了设备的驱动.h定义了驱动接口(通常为初始化函数和反初始化函数)，统一被devices\src\vpsdrv\_device.c中的函数调用

Contains driver / function implementation to control on-board encoders, decoders, other devices such as TVP7002, TVP5158, etc...

Folder devices/src – Contains functions that initialize the supported on-board devices drivers and de-initialize the same. Folder <device name> e.g. TVP7002 – Interface file vpsdrv\_tvp7002.h at \packages\ti\psp\devices\tvp7002 - Defines the interface exposed by the TVP7002 decoder driver, typically initialization and de-initialization function called by device initialization. \devices\src\vpsdrv\_device.c Encoder / decoder device driver implementation could be found at - \packages\ti\psp\devices\tvp7002\src

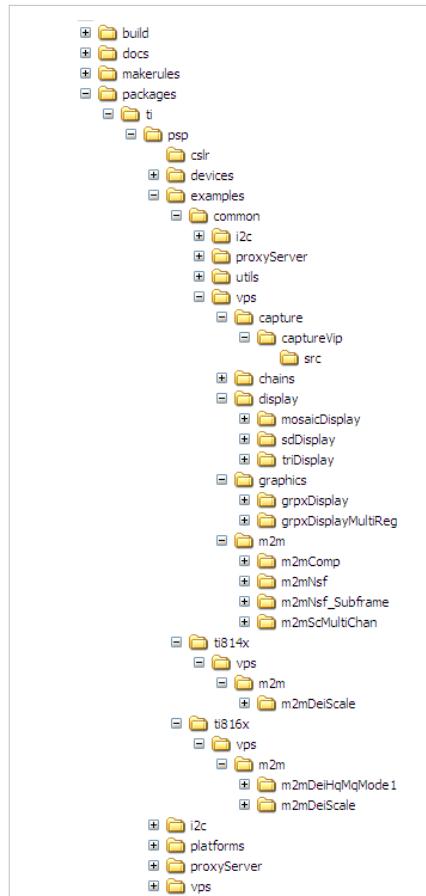

## Examples

The examples folder is the root folder for all the examples provided in standard HDVPSS release. The examples could be broadly classified into platform specific examples and examples that are common for all supported platforms.

示例文件夹是标准hdvpss发布中提供的所有示例的根文件夹。这些示例可以广泛地分为平台特定示例和所有支持的平台中常见的示例。

## Common

IIC: 实现基于命令行的i2c应用程序，该应用程序可用于读取/写入任何视频上的设备，如sii 9022a、tvp 7002、io扩展器。

Proxy Server : 实现代理服务器的主机应用程序。proxyserverhost\_main.c在上为每个受支持的平台实现主机，内存映射可能不同，配置文件proxyserverhost\_t\_i181xx.cfg在proxyserverhost\proxyserverhostvsm3ti1814x上指定给定平台的内存映射。

Utils : 实现支持的通用实用程序应用程序，用于调试辅助

printDesc文件夹 : 实现一个可以用于打印任何vpdma描述符的简单应用程序。这通常用作调试辅助，以识别损坏/不正确的vpdma描述符。

vpdmaListDump : 实现一个应用程序，可以转储列表管理器的当前配置。这是另一个调试辅助。

通用实用程序函数(如堆内存、t1ler内存管理等)

代理服务器实现

vps\_proxyServer.h 代理服务器接口

VPS: 是包含所有驱动程序示例应用程序实现的根文件夹。这些示例的组织都是相似的。如果驱动程序有多个示例应用程序，则会有多个文件夹，每个文件夹都包含一个示例应用程序。例如，显示应用程序有3个不同的示例应用程序供显示，所有这些示例应用程序都位于显示文件夹下的单独文件夹中。

所有的HDVPSS驱动：整个驱动程序和fvid 2接口所需的接口文件都位于该文件夹。任何需要使用hdvpss驱动程序服务的应用程序都必须包含一个或多个接口文件。

platforms: 平台特定的操作，如确定平台类型、板版本、硅版本等，都是通过本文件夹下的文件/函数实现的。作为hdvpss初始化的一部分，平台功能将被初始化。

**I2C**

实现基于命令行的i2c应用程序，该应用程序可用于读取/写入任何视频上的设备，如sii 9022a、tvp 7002、io扩展器。

Implements the command line based I2C application, that could be used to read / write into any of the video on-board devices such as sii9022a, TVP7002, IO Expanders.

**Proxy Server** 实现代理服务器的主机应用程序。proxyserverhost\_main.c在上为每个受支持的平台实现主机，内存映射可能不同，配置文件proxyserverhost\_ti81xx.cfg在proxyserverhostproxyservervsm3ti814x上指定给定平台的内存映射。

Implements host application for the proxy server. The file ProxyServerHost\_main.c implements host at \proxyServer\hostProxyServerVpsM3\src For each of the supported platform, the memory map could be different, the config file proxyServerHost\_ti81xx.cfg at \proxyServer\hostProxyServerVpsM3\ti814x\ specifies the memory map for a given platform.

**Utils** **Utils** : 实现支持的通用实用程序应用程序，用于调试辅助

**printDesc**文件夹 : 实现一个可以用于打印任何vpdma描述符的简单应用程序。这通常用作调试辅助，以识别损坏/不正确的vpdma描述符。

**vpdmaListDump** : 实现一个应用程序，可以转储列表管理器的当前配置。这是另一个调试辅助。

Implements generic utility applications that are supported.

- Utils\printDesc folder – Implements a simple application that could be used to print any VPDMA descriptors. This is typically used as debug aid to identify corrupted / incorrect VPDMA descriptors.

- Utils\vpdmaListDump – Implements a application that could dump the current configuration of the List Manager.

This is another debug aid.

**VPS** : 是包含所有驱动程序示例应用程序实现的根文件夹。这些示例的组织都是相似的。如果驱动程序有多个示例应用程序，则会有多个文件夹，每个文件夹都包含一个示例应用程序。例如，显示应用程序有3个不同的示例应用程序供显示，所有这些示例应用程序都位于显示文件夹下的单独文件夹中。

Is the root folder that contains all the driver sample application implementations. The organization of these examples are similar for all examples. The following paragraph expands on one of the example, same could be extended to others

In case a driver has multiple sample applications, there would be multiple folders, each holding a sample application. E.g. Display application, there are 3 different sample application for display, all these sample applications are in separate folders under display folder.

是make文件和捕获应用程序配置文件的位置持有人。下面的src文件夹保存捕获示例应用程序的源代码。有关捕获示例应用程序的详细信息，请参阅捕获的用户指南。

### **captureVip**

Is the place holder for the make file and captures applications configuration file. The src folder under this holds the source code for the captures sample application. Please refer the user guide of capture for details on the capture sample application. 有关捕获示例应用程序的详细信息，请参阅捕获用户指南。

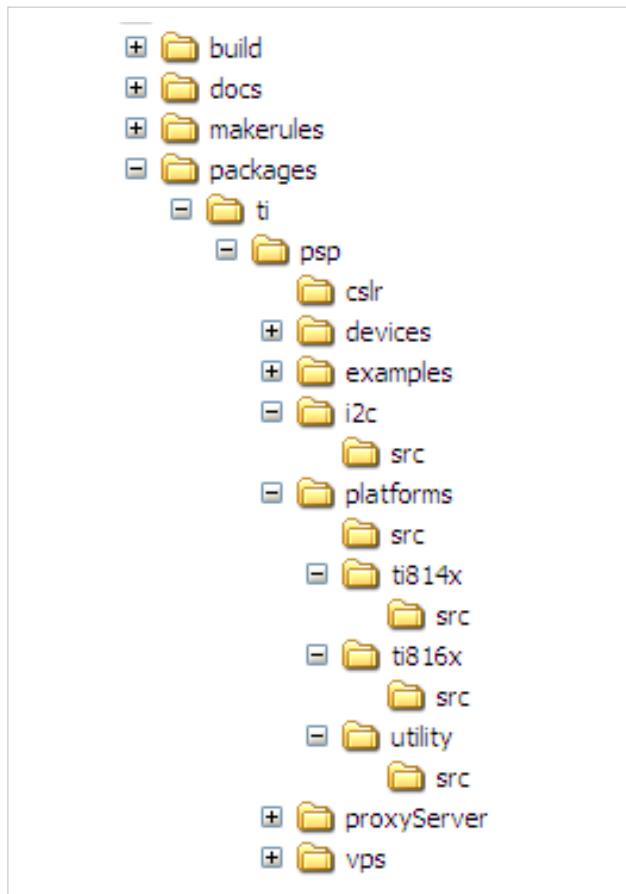

### **I2C**

The folder is the place holder for I2C driver implementation. The interface exposed by I2C driver is available at \packages\ti\psp\i2c\psp\_i2c.h. The source I2C driver is available at \packages\ti\psp\i2c\src\

平台特定的操作，如确定平台类型、板版本、硅版本等，都是通过本文件夹下的文件/函数实现的。作为UserGuideHdvpssFolhdvpss初始化的一部分，平台功能将被初始化。

## Platform

The platform specific operations such as determining the platform type, board versions, silicon versions, etc... is implemented by files / functions under this folder. As part of HDVPSS initialization, the platform functionality would be initialized

## Utility 通用实用程序函数(如堆内存、tiler内存管理等)

Is the place holder for all generic utility functions (such heap memory, Tiler memory management, etc... )

## Proxy Server 代理服务器实现 vps\_proxyServer.h 代理服务器接口

Is the place holder for proxy server implementation. The interface exposed by proxy server is at \packages\ti\psp\proxyServer\vps\_proxyServer.h, along with make file to build proxy server. The folder \packages\ti\psp\proxyServer\src\ contains the source files for proxy server.

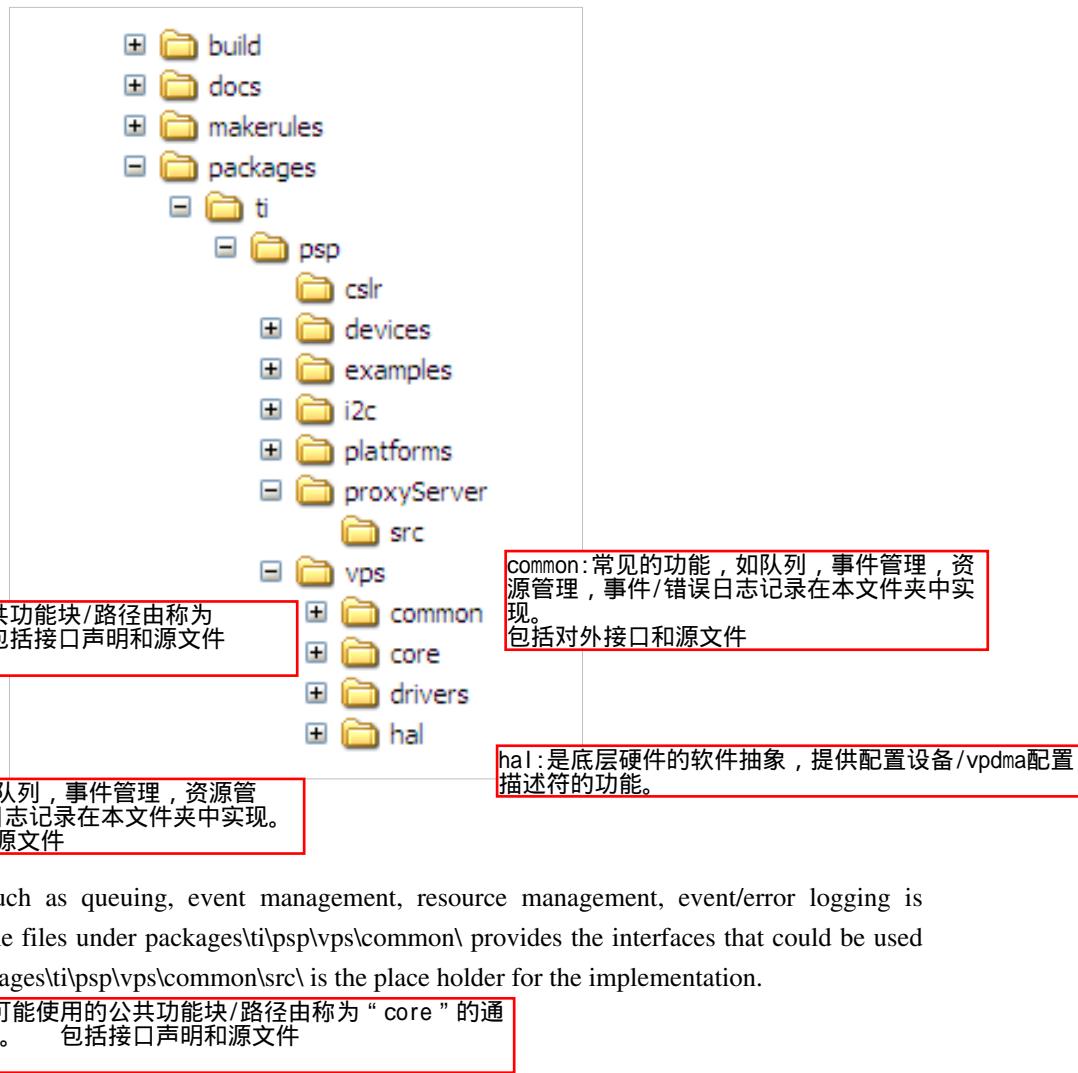

## VPS 所有的HDVPSS驱动：整个驱动程序和fvid 2接口所需的 接口文件都位于该文件夹。任何需要使用hdvpss驱动程 序服务的应用程序都必须包含一个或多个接口文件。

Is the master folder for all HDVPSS drivers. The interface files required for the entire driver and the FVID 2 interface is available at \packages\ti\psp\vps\. Any application that requires using the services of HDVPSS driver will have to include one or more of the interface files.

The common functionality such as queuing, event management, resource management, event/error logging is implemented in this folder. The files under packages\ti\psp\vps\common\ provides the interfaces that could be used by the drivers. The folder packages\ti\psp\vps\common\src\ is the place holder for the implementation.

Core

一个或多个驱动程序可能使用的公共功能块/路径由称为“core”的通用软件实体配置/管理。包括接口声明和源文件

The common functional block / paths that could potentially be used by one or more drivers, is configured / managed by common software entity called “core”. The implementation of this core is at \packages\ti\psp\vps\core\src\ and the interface files of core is at \packages\ti\psp\vps\core

是底层硬件的软件抽象，提供配置设备/vpdma配置描述符的功能

## HAL

Is a software abstraction of the underlying hardware, provides function to configure the devices / VPDMA configuration descriptors.

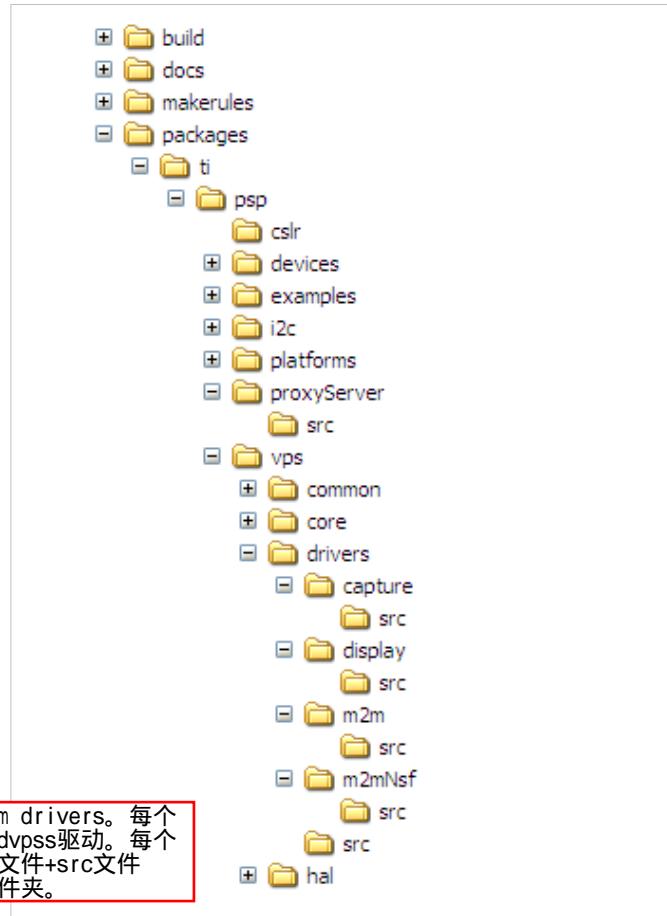

## Driver

HDVPSS驱动分为capture, display and m2m drivers。每个子文件夹下的驱动文件夹实现一个或多个hdvpss驱动。每个子文件夹都有一致的子文件夹目录结构(头文件+src文件夹)，作为一个例子，让我们考虑捕获子文件夹。

驱动程序公开的应用程序接口位于

\\packages\\ti\\psp\\vps\\

FVID2 manager的驱动程序接口位于

于./drivers\\capture\\

The HDVPSS drivers are segregated into capture, display and m2m drivers. Each of the sub-folder under driver folder implements one or more HDVPSS drivers. Each of the sub-folder have consistent sub-folder directory structure, as an example, lets consider Capture sub-folder

The application interface exposed by the drivers is available at \\packages\\ti\\psp\\vps\\ and the driver interface (to FVID2 Manager) is defined at \\packages\\ti\\psp\\vps\\drivers\\capture\\

The makefile to build the driver is also contained here.

The source folder "src" under the driver folder is the place holder for the driver implementation. Note that there could be multiple drivers, as in case of the m2m driver. The driver instances defined in the application interface at \\packages\\ti\\psp\\vps\\ is expected to be used to differentiate the drivers.

驱动文件夹下的源文件夹“SRC”是驱动程序实现的文件夹。请注意，可能有多个驱动程序，如在M2M驱动程序的情况下。在\\packages\\ti\\psp\\vps\\的应用程序接口中定义的驱动程序实例预计将用于区分驱动程序。

# UserGuideFVID2

## FVID2

fvid 2是用于BIOS操作系统之上的视频捕获、视频显示和视频处理(内存到内存驱动程序)应用程序的接口API。它为流操作提供接口，例如把缓冲区数据与硬件的数据交换。还为视频编码器和视频解码器等设备提供控制接口，它们实际上不是数据路径设备。为不同的SoC视频应用程序提供相同的外观和感觉。

### Introduction

FVID2 are the interface APIs for the video capture, video display and video processing (Memory to Memory drivers)applications on top of BIOS operating system. Provides the interfaces for the streaming operations like queuing of buffers to the hardware and getting is back from the hardware. Also provides the control interface for the devices like video encoders and video decoders which are actually not the data path devices. Gives same look and feel for the video applications across different SoCs.

#### Following are the features of the FVID2 APIs.

独立于平台的API和与CPU无关的API

- Platform independent and CPU independent APIs. 适用于客户端-服务器模型等多处理器通信环境。

- Suitable for multiprocessor communication environment like client-server model.

- Supports blocking as well as non-blocking APIs. 支持阻塞和非阻塞API。

- Supports streaming class of devices like video capture and video display. 支持流类设备，如视频捕获和视频显示。

- Supports non-streaming class of devices like video encoders and video decoders. 支持非蒸汽类设备，如视频编码器和视频解码器。

- Supports sliced based operations like sliced based capture and slice based memory to memory drivers.

- Support for the multiple buffers representing a single frame. 支持表示单个帧的多个缓冲区。

- Support for configuring the hardware on per frame basis in synchronous with the frames submitted. AKA Runtime parameters change. 支持在每个帧的基础上配置硬件，并与帧同步。也就是运行时参数更改。

- Interface supports multiple handle and multiple channel operation. Explained in detail in coming sections.

- Support for adding the custom controls specific to the device. 接口支持多句柄和多通道操作。在接下来的章节中详细解释。

#### Warning

Underlying drivers catering to FVID2 interfaces may decide to expose the sub-set of features supported by FVID2.

Please refer to the individual driver userGuide for the features exposed by drivers.

满足fvid 2接口的底层驱动程序可能决定公开fvid 2支持的特性子集。请参阅驱动程序公开的特性的单个驱动程序用户指南。

### FVID2 enumerations

枚举数据类型

#### FVID2\_DataFormat 数据格式

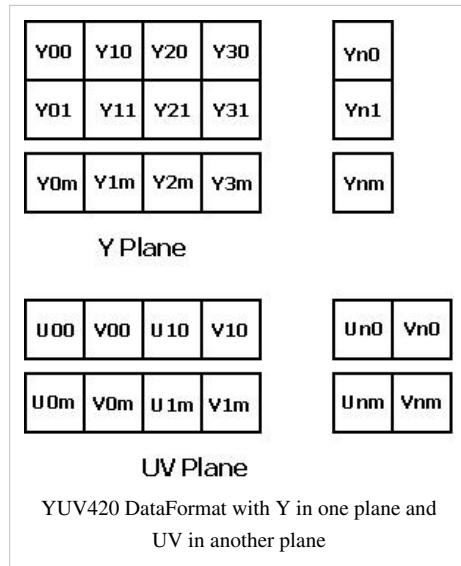

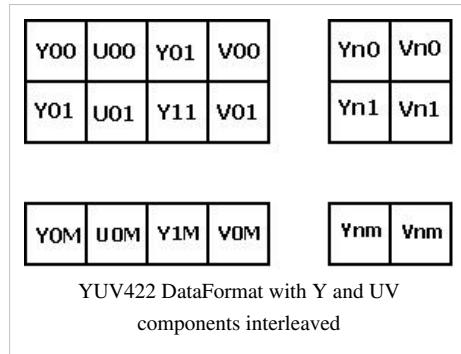

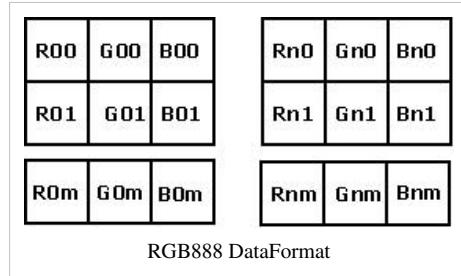

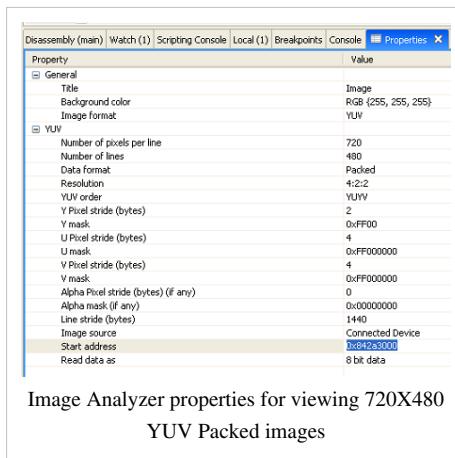

FVID2\_DataFormat represents the arrangement of the different components forming the pixel. These components can be in YUV color space or the RGB color space or any other color space. Below figure shows the commonly used data formats. FVID2 supports many more data formats. Specific driver may expose subset of the data formats from the mentioned below based on the hardware capability.

#### YUV420 Semiplanar Format

fvid 2\_datamat表示构成像素的不同组件的排列。这些组件可以在yuv颜色空间或RGB颜色空间或任何其他颜色空间中。下图显示了常用的数据格式。fvid 2支持更多的数据格式。特定驱动程序可能会根据硬件功能从下面提到的数据格式中公开子集。

FVID2\_DataFormat

FVID2\_ScanFormat

FVID2\_Field ID

Bits per Pixel

### YUV422 Interleaved Format

### RGB888 Packed Format

```

typedef enum

{

FVID2_DF_YUV422I_UYVY = 0x0000,

/**< YUV 422 Interleaved format - UYVY. */

FVID2_DF_YUV422I_YUYV,

/**< YUV 422 Interleaved format - YUYV. */

FVID2_DF_YUV422I_YVYU,

/**< YUV 422 Interleaved format - YVYU. */

FVID2_DF_YUV422I_VYUY,

/**< YUV 422 Interleaved format - VYUY. */

FVID2_DF_YUV422SP_UV,

/**< YUV 422 Semi-Planar - Y separate, UV interleaved. */

}

```

```

FVID2_DF_YUV422SP_VU,

/**< YUV 422 Semi-Planar - Y separate, VU interleaved. */

FVID2_DF_YUV422P,

/**< YUV 422 Planar - Y, U and V separate. */

FVID2_DF_YUV420SP_UV,

/**< YUV 420 Semi-Planar - Y separate, UV interleaved. */

FVID2_DF_YUV420SP_VU,

/**< YUV 420 Semi-Planar - Y separate, VU interleaved. */

FVID2_DF_YUV420P,

/**< YUV 420 Planar - Y, U and V separate. */

FVID2_DF_YUV444P,

/**< YUV 444 Planar - Y, U and V separate. */

FVID2_DF_YUV444I,

/**< YUV 444 interleaved - YUVYUV... */

FVID2_DF_RGB16_565 = 0x1000,

/**< RGB565 16-bit - 5-bits R, 6-bits G, 5-bits B. */

FVID2_DF_ARGB16_1555,

/**< ARGB1555 16-bit - 5-bits R, 5-bits G, 5-bits B, 1-bit

Alpha (MSB). */

FVID2_DF_RGBA16_5551,

/**< RGBA5551 16-bit - 5-bits R, 5-bits G, 5-bits B, 1-bit

Alpha (LSB). */

FVID2_DF_ARGB16_4444,

/**< ARGB4444 16-bit - 4-bits R, 4-bits G, 4-bits B, 4-bit

Alpha (MSB). */

FVID2_DF_RGBA16_4444,

/**< RGBA4444 16-bit - 4-bits R, 4-bits G, 4-bits B, 4-bit

Alpha (LSB). */

FVID2_DF_ARGB24_6666,

/**< ARGB4444 24-bit - 6-bits R, 6-bits G, 6-bits B, 6-bit

Alpha (MSB). */

FVID2_DF_RGBA24_6666,

/**< RGBA4444 24-bit - 6-bits R, 6-bits G, 6-bits B, 6-bit

Alpha (LSB). */

FVID2_DF_RGB24_888,

/**< RGB24 24-bit - 8-bits R, 8-bits G, 8-bits B. */

FVID2_DF_ARGB32_8888,

/**< ARGB32 32-bit - 8-bits R, 8-bits G, 8-bits B, 8-bit

Alpha (MSB). */

FVID2_DF_RGBA32_8888,

/**< RGBA32 32-bit - 8-bits R, 8-bits G, 8-bits B, 8-bit

Alpha (LSB). */

FVID2_DF_BITMAP8 = 0x2000,

/**< BITMAP 8bpp. */

FVID2_DF_BITMAP4_LOWER,

/**< BITMAP 4bpp lower address in CLUT. */

FVID2_DF_BITMAP4_UPPER,

```

```

/**< BITMAP 4bpp upper address in CLUT. */

FVID2_DF_BITMAP2_OFFSET0,

/**< BITMAP 2bpp offset 0 in CLUT. */

FVID2_DF_BITMAP2_OFFSET1,

/**< BITMAP 2bpp offset 1 in CLUT. */

FVID2_DF_BITMAP2_OFFSET2,

/**< BITMAP 2bpp offset 2 in CLUT. */

FVID2_DF_BITMAP2_OFFSET3,

/**< BITMAP 2bpp offset 3 in CLUT. */

FVID2_DF_BITMAP1_OFFSET0,

/**< BITMAP 1bpp offset 0 in CLUT. */

FVID2_DF_BITMAP1_OFFSET1,

/**< BITMAP 1bpp offset 1 in CLUT. */

FVID2_DF_BITMAP1_OFFSET2,

/**< BITMAP 1bpp offset 2 in CLUT. */

FVID2_DF_BITMAP1_OFFSET3,

/**< BITMAP 1bpp offset 3 in CLUT. */

FVID2_DF_BITMAP1_OFFSET4,

/**< BITMAP 1bpp offset 4 in CLUT. */

FVID2_DF_BITMAP1_OFFSET5,

/**< BITMAP 1bpp offset 5 in CLUT. */

FVID2_DF_BITMAP1_OFFSET6,

/**< BITMAP 1bpp offset 6 in CLUT. */

FVID2_DF_BITMAP1_OFFSET7,

/**< BITMAP 1bpp offset 7 in CLUT. */

FVID2_DF_BAYER_RAW = 0x3000,

/**< Bayer pattern. */

FVID2_DF_RAW_VBI,

/**< Raw VBI data. */

FVID2_DF_RAW,

/**< Raw data - Format not interpreted. */

FVID2_DF_MISC,

/**< For future purpose. */

FVID2_DF_INVALID,

/**< Invalid data format. Could be used to initialize

variables. */

FVID2_DF_MAX

/**< Should be the last value of this enumeration.

Will be used by driver for validating the input parameters. */

} FVID2_DataFormat;

```

## FVID2 ScanFormat

fvid 2扫描格式：逐行

隔行

Strucutre represents the scanning format.

```

typedef enum

{

FVID2_SF_INTERLACED = 0,

/**< Interlaced mode. */

FVID2_SF_PROGRESSIVE,

/**< Progressive mode. */

FVID2_SF_MAX

/**< Should be the last value of this enumeration.

Will be used by driver for validating the input parameters. */

} FVID2_ScanFormat;

```

表示缓冲区的字段id。对于隔行缓冲区，字段id可以是0或1，这取决于奇偶字段缓冲区包含。对于逐行扫描显示，所有帧的字段ID是相同的。

## FVID2 Field ID

Represents field ID of the buffer. For interlaced buffers field ID could be 0 or 1 depending upon the even and odd field buffer contains. For progressive displays field ID is same for all the frames.

```

typedef enum

{

FVID2_FID_TOP = 0,

/**< Top field. */

FVID2_FID_BOTTOM,

/**< Bottom field. */

FVID2_FID_FRAME,

/**< Frame mode - Contains both the fields or a progressive

frame. */

FVID2_FID_MAX

/**< Should be the last value of this enumeration.

Will be used by driver for validating the input parameters. */

} FVID2_Fid;

```

## Bits per Pixel

表示缓冲器的每像素所占的位数。例如，对于yuv 422，每像素交错格式比特为16，而yuv 444为24，yuv 420为12。

Represents bits per pixel for buffer. For example for YUV422 interlaced format bit per pixel will be 16 and for YUV444 it will be 24 and YUV420 it will be 12.

```

typedef enum

{

FVID2_BPP_BITS1 = 0,

/**< 1 Bits per Pixel. */

FVID2_BPP_BITS2,

/**< 2 Bits per Pixel. */

FVID2_BPP_BITS4,

/**< 4 Bits per Pixel. */

FVID2_BPP_BITS8,

/**< 8 Bits per Pixel. */

FVID2_BPP_BITS12,

/**< 12 Bits per Pixel - used for YUV420 format. */

}

```

```

FVID2_BPP_BITS16,

/**< 16 Bits per Pixel. */

FVID2_BPP_BITS24,

/**< 24 Bits per Pixel. */

FVID2_BPP_BITS32,

/**< 32 Bits per Pixel. */

FVID2_BPP_MAX

/**< Should be the last value of this enumeration.

Will be used by driver for validating the input parameters. */

} FVID2_BitsPerPixel;

```

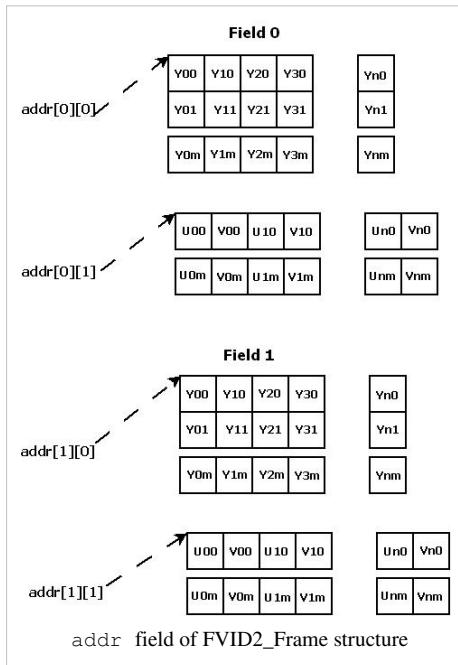

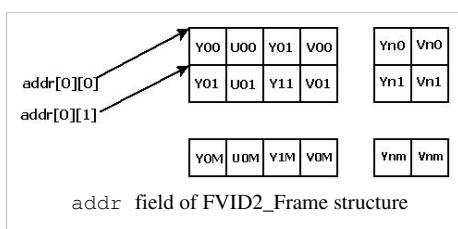

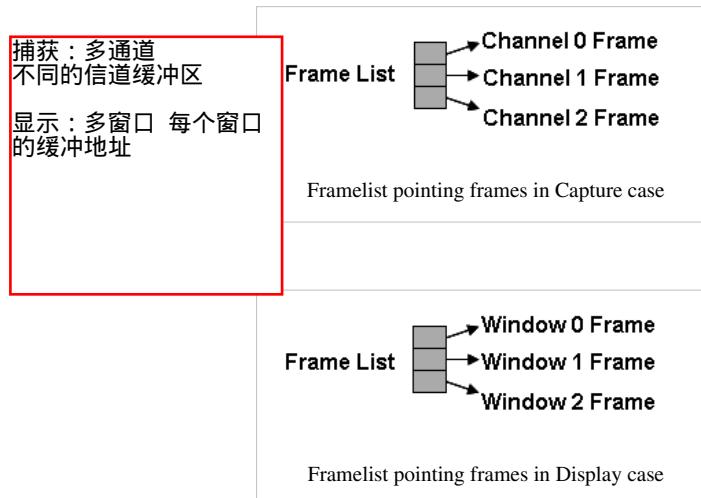

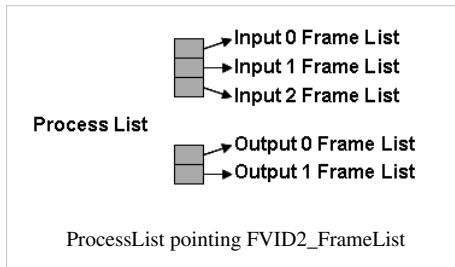

## FVID2 Structures

数据结构

FVID2 CallBack Parameters

fvid 2支持驱动程序回调。驱动程序在特定事件上调用应用程序，如完成缓冲区捕获、显示或处理。或者在出现错误时，应用程序需要采取一些操作。下面是fvid 2 API为应用程序传递将由驱动程序调用的回调函数而定义的结构。

### FVID2 CallBack Parameters

FVID2 supports the driver call back. Driver call the application on specific events like, completion of buffer capture, displayed or process. Or in case of error where application needs to take some action. Following is the structure defined by the FVID2 API for the application to pass the callback functions to be invoked by the driver.

```

typedef struct

{

FVID2_CbFxn            cbFxn;           驱动程序用来通知操作已经完成或未完成的回调函数。这是一个可选的参数，如果应用程序决定使用轮询方法，因此可以设置为NULL

/**< Application callback function used by the driver to

intimate any

operation has completed or not. This is an optional

parameter

in case application decides to use polling method and so

could be

set to NULL. */

FVID2_ErrCbFxn         errCbFxn;

/**< Application error callback function used by the driver

to intimate

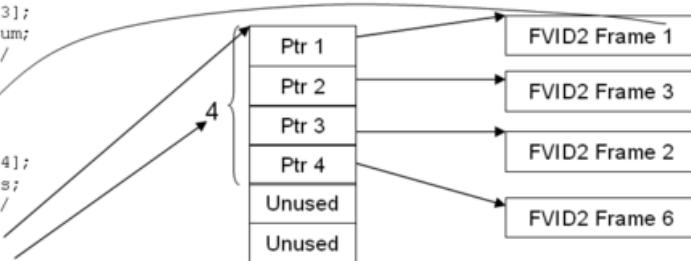

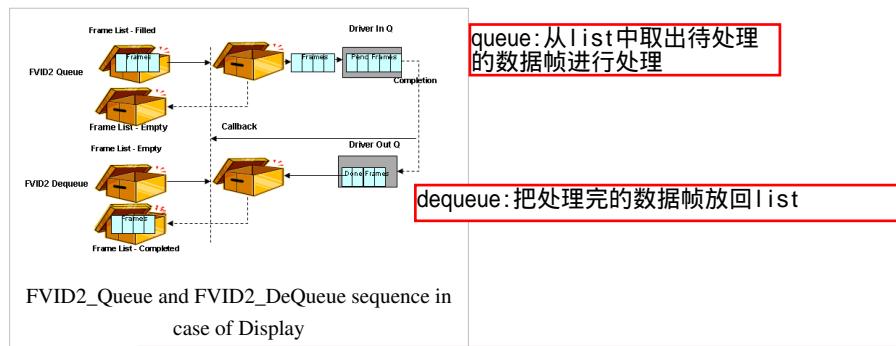

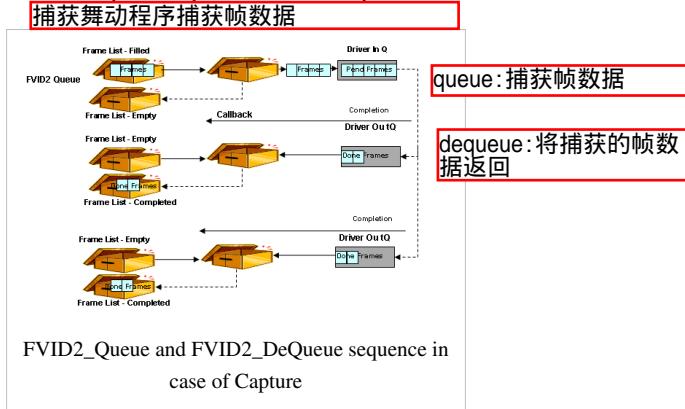

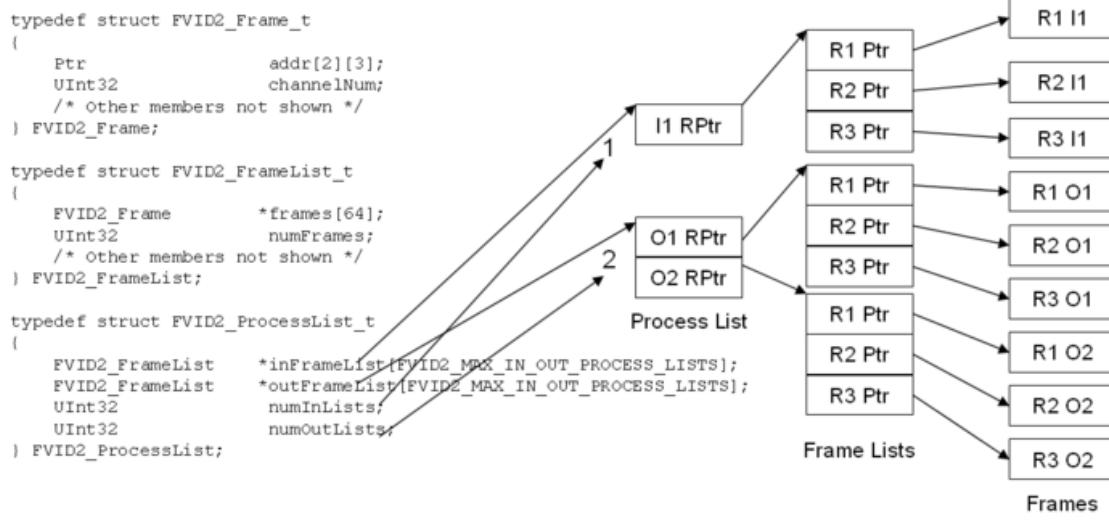

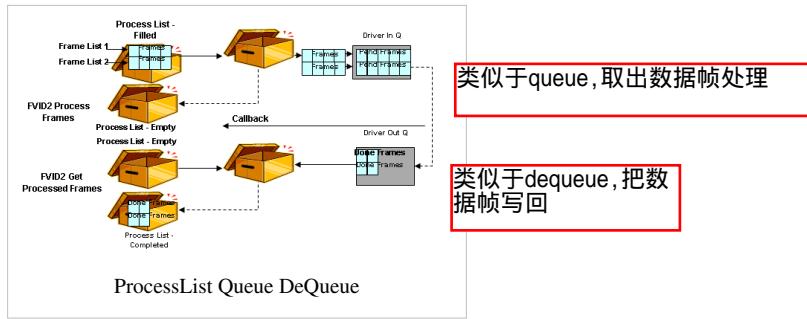

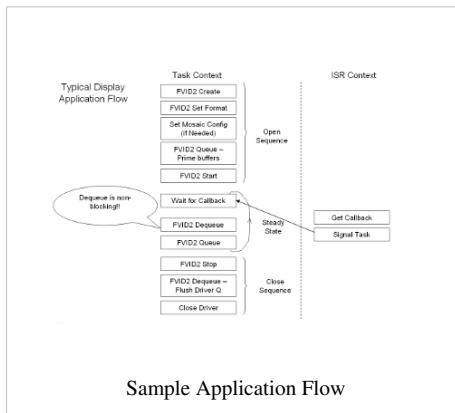

any error occurs at the time of streaming. This is an