## TL5728F-EVM 开发板硬件说明书

## RevisionHistory

| DraftDate  | Revision No. | Description |

|------------|--------------|-------------|

| 2018/06/10 | V1.0         | 1. 初始版本.    |

创龙

## 目 录

|                       |    |

|-----------------------|----|

| 1 处理器                 | 4  |

| 2 FLASH               | 5  |

| 3 RAM                 | 6  |

| 4 QSPI Flash          | 6  |

| 5 硬件加密芯片              | 7  |

| 6 电源接口和拨码开关           | 8  |

| 7 JTAG 仿真器接口          | 8  |

| 8 Xilinx FPGA 下载器接口   | 9  |

| 9 FPGA XACD 接口        | 10 |

| 10 FPGA POMD 接口       | 11 |

| 11 FPGA EXPORT 拓展口    | 11 |

| 12 SFP 接口             | 12 |

| 13 FMC 接口             | 13 |

| 14 BANK 电压配置接口        | 14 |

| 15 LCD 触摸屏接口          | 15 |

| 16 LED 指示灯            | 16 |

| 17 按键                 | 18 |

| 18 串口                 | 20 |

| 19 BOOT SET 启动选择开关    | 22 |

| 20 Micro SD 接口        | 24 |

| 21 拓展 IO 信号           | 25 |

| 22 底板 B2B 连接器         | 27 |

| 23 RTC 座              | 27 |

| 24 USB OTG/USB HUB 接口 | 28 |

| 25 RGMII 千兆以太网口       | 30 |

| 26 HDMI OUT 接口        | 30 |

| 27 CAN 总线接口           | 32 |

| 28 SATA 接口            | 33 |

| 29 散热风扇接口             | 33 |

|                           |    |

|---------------------------|----|

| 30 视频输入拓展口 (V-PORT) ..... | 34 |

| 更多帮助 .....                | 37 |

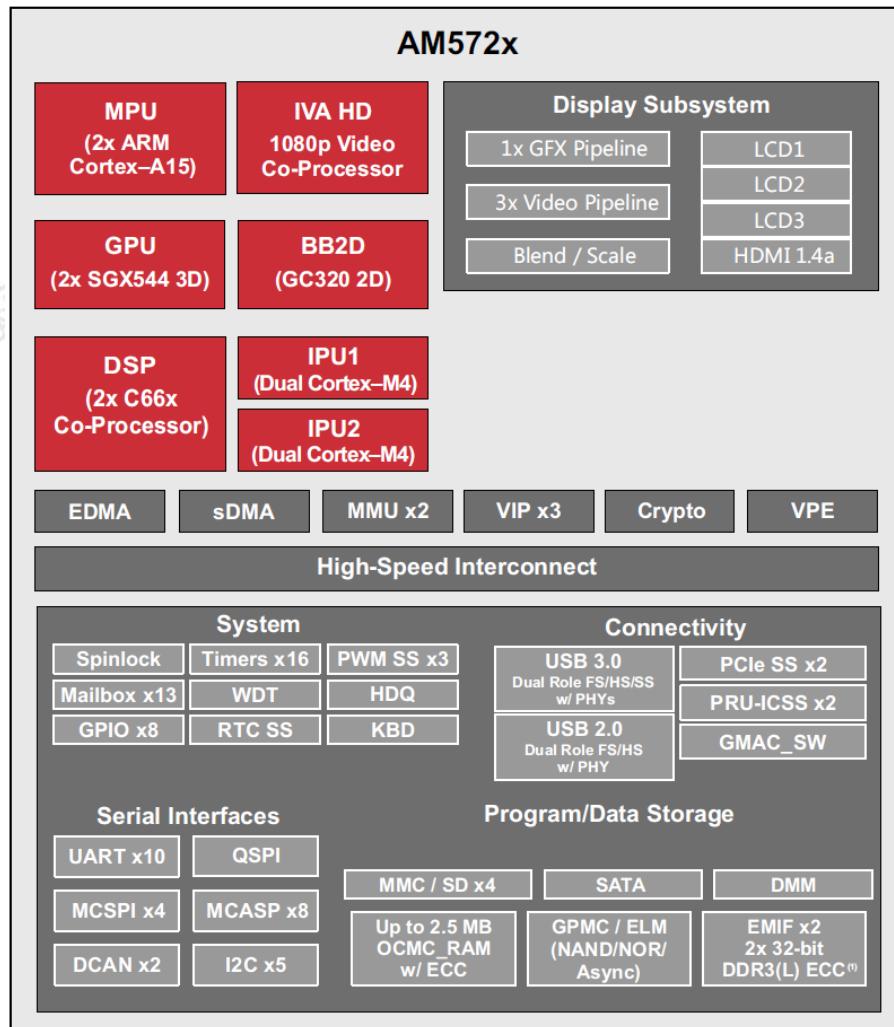

## 1 处理器

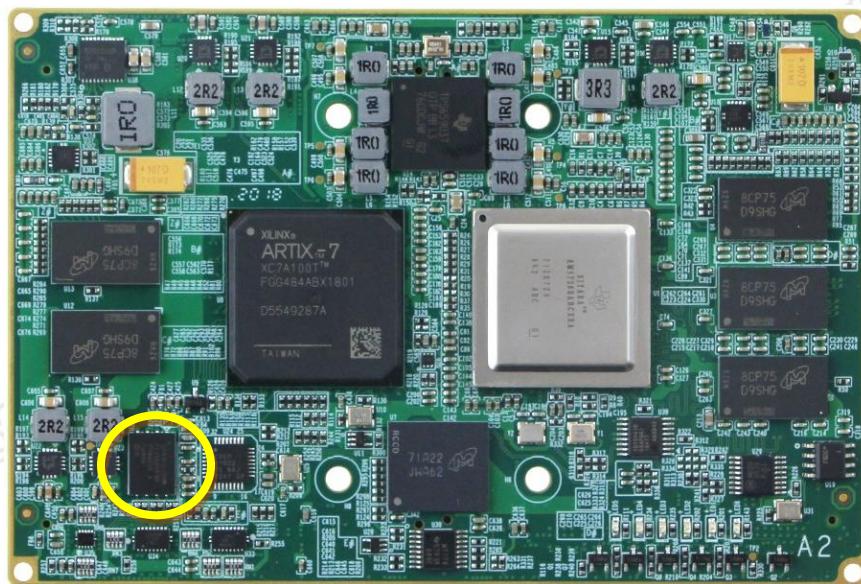

基于 TI Sitara AM5728 (浮点双 DSPC66x+双 ARM Cortex-A15) +Xilinx Artix-7FPGA 工业控制及高性能音视频处理器。拥有多种工业接口资源，资源框图如下所示：

图 1

## Artix-7 FPGAs

| Artix®-7 FPGAs                                                                               |                                                     |                 |                                                              |             |             |             |             |             |             |

|----------------------------------------------------------------------------------------------|-----------------------------------------------------|-----------------|--------------------------------------------------------------|-------------|-------------|-------------|-------------|-------------|-------------|

| Transceiver Optimization at the Lowest Cost and Highest DSP Bandwidth<br>(1.0V, 0.95V, 0.9V) |                                                     |                 |                                                              |             |             |             |             |             |             |

|                                                                                              | Part Number                                         | XC7A12T         | XC7A15T                                                      | XC7A25T     | XC7A35T     | XC7A50T     | XC7A75T     | XC7A100T    | XC7A200T    |

| Logic Resources                                                                              | Logic Cells                                         | 12,800          | 16,640                                                       | 23,360      | 33,280      | 52,160      | 75,520      | 101,440     | 215,360     |

|                                                                                              | Slices                                              | 2,000           | 2,600                                                        | 3,650       | 5,200       | 8,150       | 11,800      | 15,850      | 33,650      |

|                                                                                              | CLB Flip-Flops                                      | 16,000          | 20,800                                                       | 29,200      | 41,600      | 65,200      | 94,400      | 126,800     | 269,200     |

| Memory Resources                                                                             | Maximum Distributed RAM (Kb)                        | 171             | 200                                                          | 313         | 400         | 600         | 892         | 1,188       | 2,888       |

|                                                                                              | Block RAM/FIFO w/ ECC (36 Kb each)                  | 20              | 25                                                           | 45          | 50          | 75          | 105         | 135         | 365         |

| Clock Resources                                                                              | Total Block RAM (Kb)                                | 720             | 900                                                          | 1,620       | 1,800       | 2,700       | 3,780       | 4,860       | 13,140      |

|                                                                                              | CMTs (1 MMCM + 1 PLL)                               | 3               | 5                                                            | 3           | 5           | 5           | 6           | 6           | 10          |

| I/O Resources                                                                                | Maximum Single-Ended I/O                            | 150             | 250                                                          | 150         | 250         | 250         | 300         | 300         | 500         |

|                                                                                              | Maximum Differential I/O Pairs                      | 72              | 120                                                          | 72          | 120         | 120         | 144         | 144         | 240         |

| Embedded Hard IP Resources                                                                   | DSP Slices                                          | 40              | 45                                                           | 80          | 90          | 120         | 180         | 240         | 740         |

|                                                                                              | PCIe® Gen2 <sup>(1)</sup>                           | 1               | 1                                                            | 1           | 1           | 1           | 1           | 1           | 1           |

|                                                                                              | Analog Mixed Signal (AMS) / XADC                    | 1               | 1                                                            | 1           | 1           | 1           | 1           | 1           | 1           |

|                                                                                              | Configuration AES / HMAC Blocks                     | 1               | 1                                                            | 1           | 1           | 1           | 1           | 1           | 1           |

| Speed Grades                                                                                 | GTP Transceivers (6.6 Gb/s Max Rate) <sup>(2)</sup> | 2               | 4                                                            | 4           | 4           | 4           | 8           | 8           | 16          |

|                                                                                              | Commercial                                          | -1, -2          | -1, -2                                                       | -1, -2      | -1, -2      | -1, -2      | -1, -2      | -1, -2      | -1, -2      |

|                                                                                              | Extended                                            | -2L, -3         | -2L, -3                                                      | -2L, -3     | -2L, -3     | -2L, -3     | -2L, -3     | -2L, -3     | -2L, -3     |

|                                                                                              | Industrial                                          | -1, -2, -1L     | -1, -2, -1L                                                  | -1, -2, -1L | -1, -2, -1L | -1, -2, -1L | -1, -2, -1L | -1, -2, -1L | -1, -2, -1L |

|                                                                                              | Dimensions (mm)                                     | Ball Pitch (mm) | Available User I/O: 3.3V SelectIO™ HR I/O (GTP Transceivers) |             |             |             |             |             |             |

| CPG236                                                                                       | 10 x 10                                             | 0.5             | 106 (2)                                                      | 106 (2)     | 106 (4)     | 106 (2)     | 106 (2)     |             |             |

| CSG324                                                                                       | 15 x 15                                             | 0.8             |                                                              | 210 (0)     |             | 210 (0)     | 210 (0)     | 210 (0)     | 210 (0)     |

| CSG325                                                                                       | 15 x 15                                             | 0.8             | 150 (2)                                                      |             | 150 (4)     | 150 (4)     | 150 (4)     |             |             |

| FTG256                                                                                       | 17 x 17                                             | 1.0             |                                                              |             | 170 (0)     |             | 170 (0)     | 170 (0)     | 170 (0)     |

| SBG484 / SBV484                                                                              | 19 x 19                                             | 0.8             |                                                              |             |             |             |             |             | 285 (4)     |

| Footprint Compatible                                                                         | FGG484                                              | 23 x 23         | 1.0                                                          | 250 (4)     |             | 250 (4)     | 250 (4)     | 285 (4)     | 285 (4)     |

|                                                                                              | FBG484 / FBV484                                     | 23 x 23         | 1.0                                                          |             |             |             |             |             | 285 (4)     |

图 2Xilinx Artix-7 FPGA 硬件资源

## 2 FLASH

核心板上采用工业级 eMMC, 4/8GByte 可选, 硬件如下图:

图 3

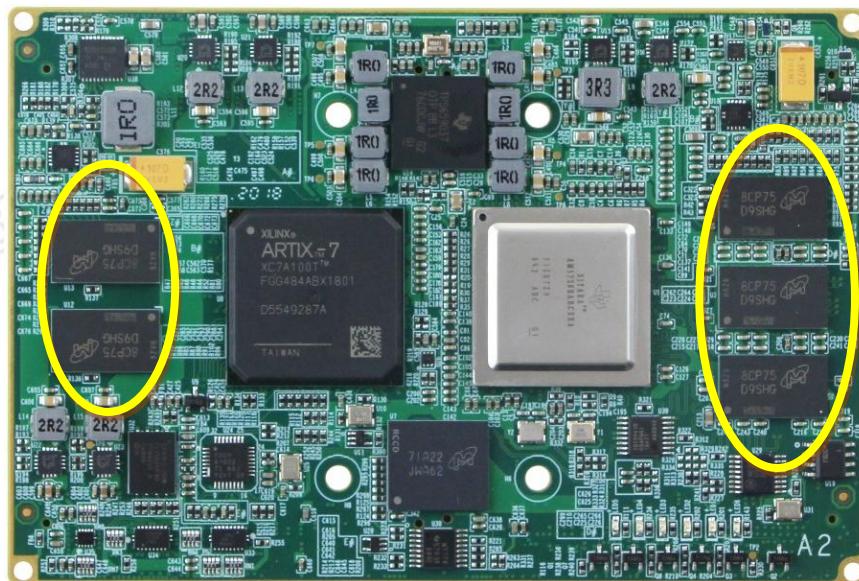

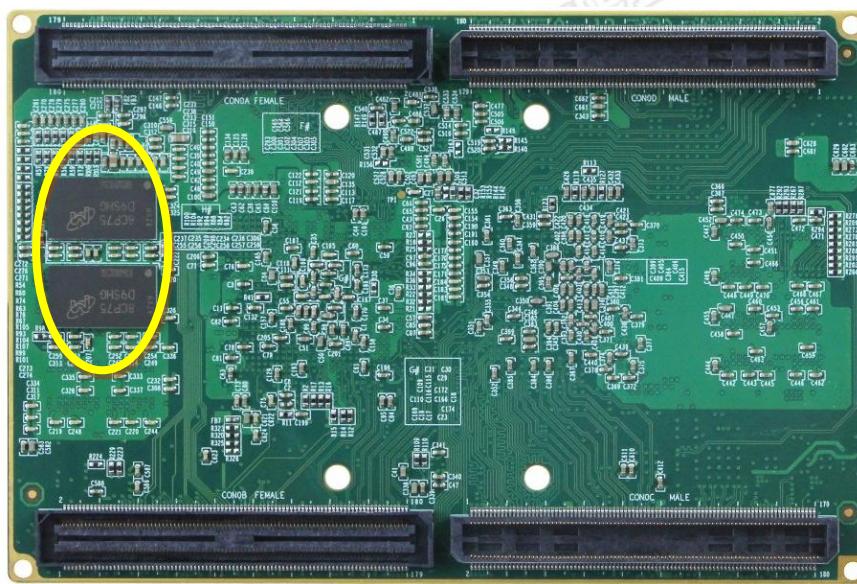

### 3 RAM

核心板 ARM 端和 FPGA 端 RAM 均采用工业级低功耗 DDR3，存储大小 1/2GByte、512MByte/1GByte 可选；FPGA 端包含 2 片 DDR3，ARM 端总共包含 5 片 DDR3（正面三片，背面两片），其中一片专门用于做 ECC 校验作用，不计入内存大小；硬件如下图：

图 4

图 5

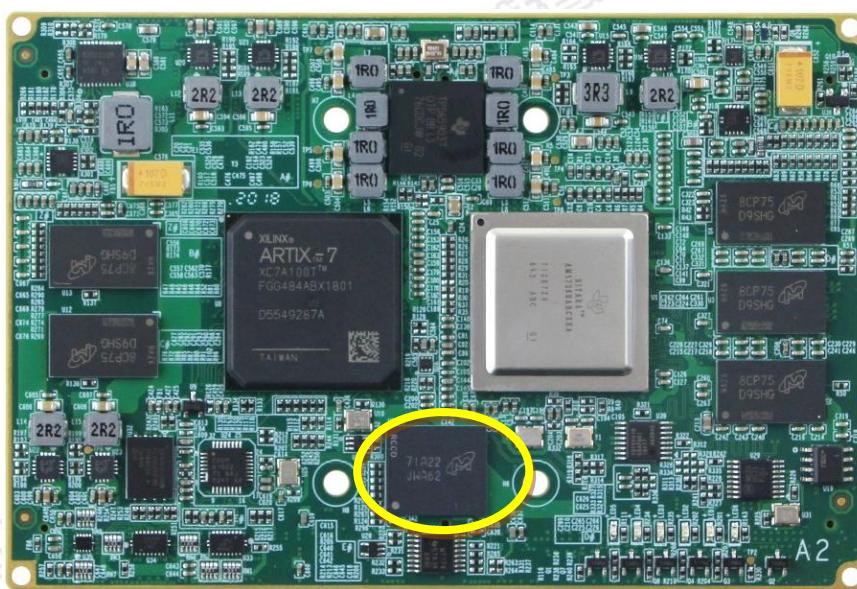

### 4 QSPI Flash

创龙

核心板 FPGA 端采用存取速度更快的 QSPI Flash, 内存大小为 32MByte, 硬件如下图:

图 6

## 5 硬件加密芯片

核心板采用高安全性的加密芯片 ATAES132A, 为串行电子可擦写和可编程只读存储器 (EEPROM) 提供了验证和机密的非易失性存储性能。

图 7

## 6 电源接口和拨码开关

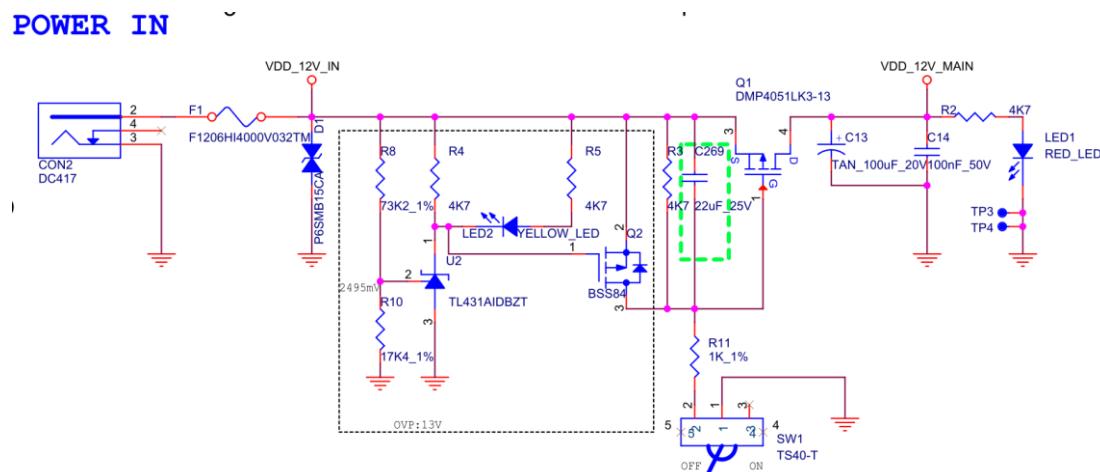

采用 12V 3A 直流电源供电, CON2 为电源接口, SW1 为电源拨码开关, 硬件及原理图如下所示:

冬 8

冬 9

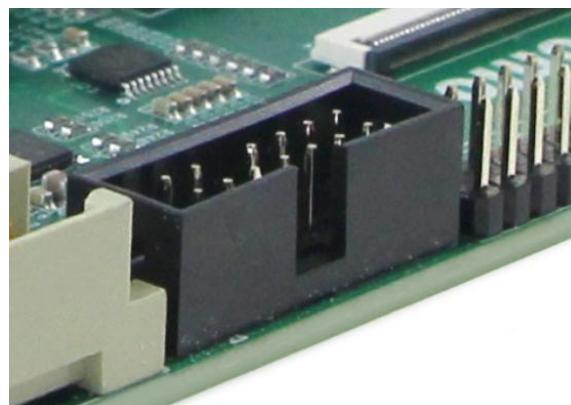

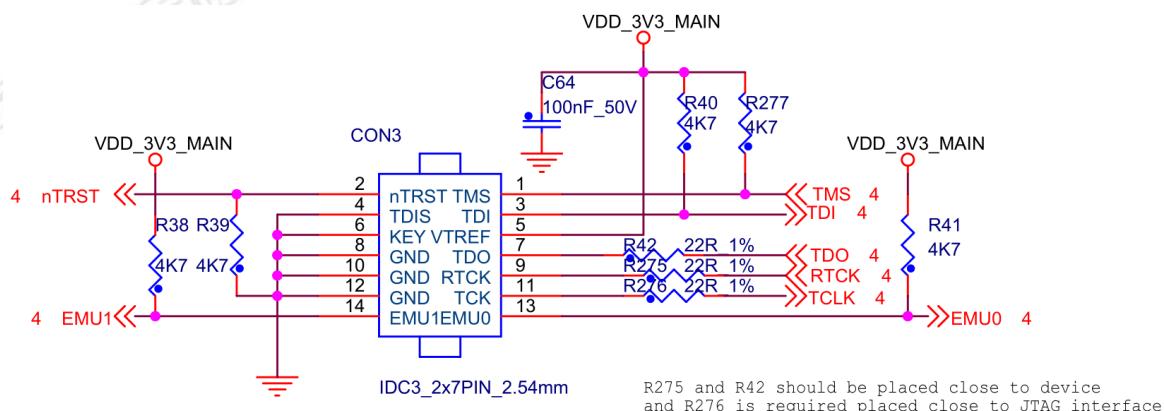

## 7 JTAG 仿真器接口

可以通过 JTAG 接口 (CON3) 烧写 Bootloader 和进行软件调试，各引脚定义如下图：

图 10

图 11

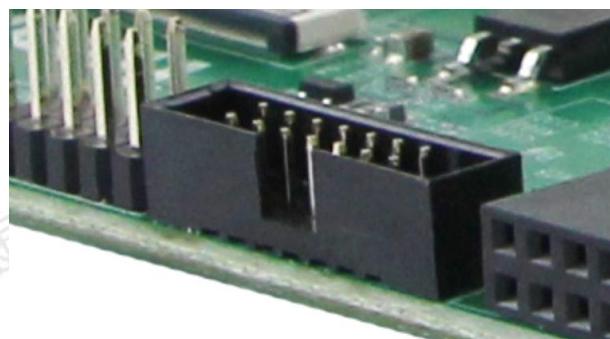

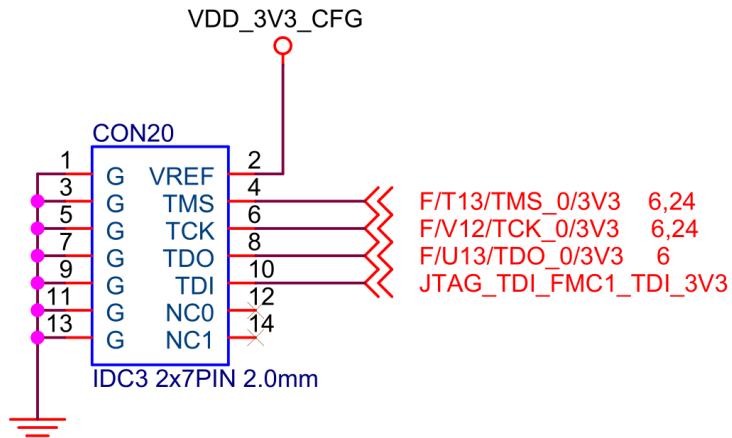

## 8 Xilinx FPGA 下载器接口

Xilinx FPGA 下载器接口 (CON20) 共 14pin, 2.0mm 间距, 硬件及各引脚定义如下图:

图 12

# FPGA JTAG

图 13

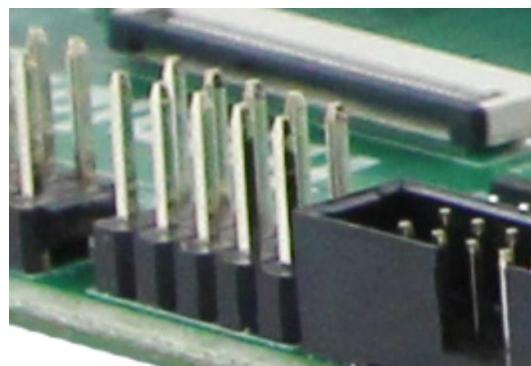

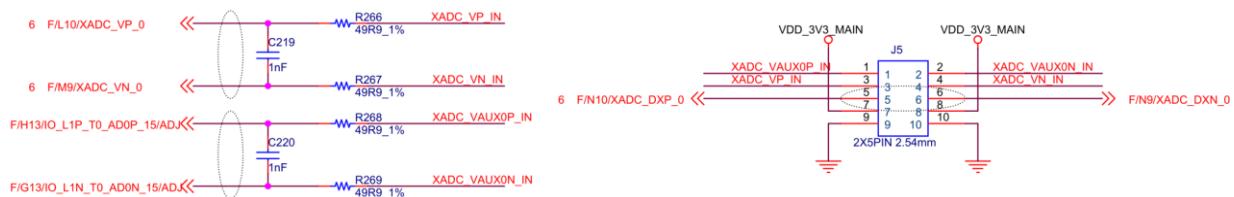

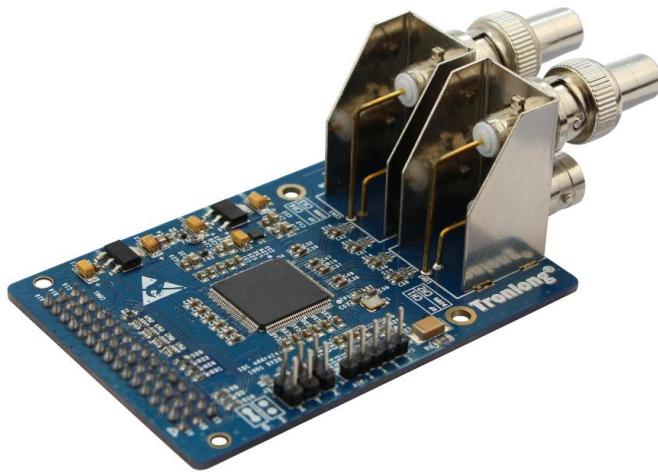

9 FPGA XADC 接口

开发板引出 FPGA 端 XADC 接口, 12bit 双通道模拟输入接口和 1 个温度传感器输入接口, 量程 1.0Vp-p, 支持 1MHz 带宽, 硬件及各引脚定义如下图:

图 14

图 15

## 10 FPGA PMOD 接口

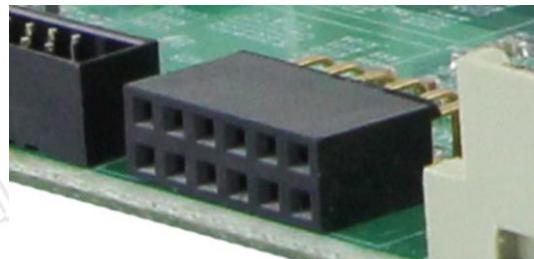

开发板 FPGA 端引出 PMOD 接口，支持 PMOD 类型的扩展模块，硬件及各引脚定义如下图：

图 16

图 17

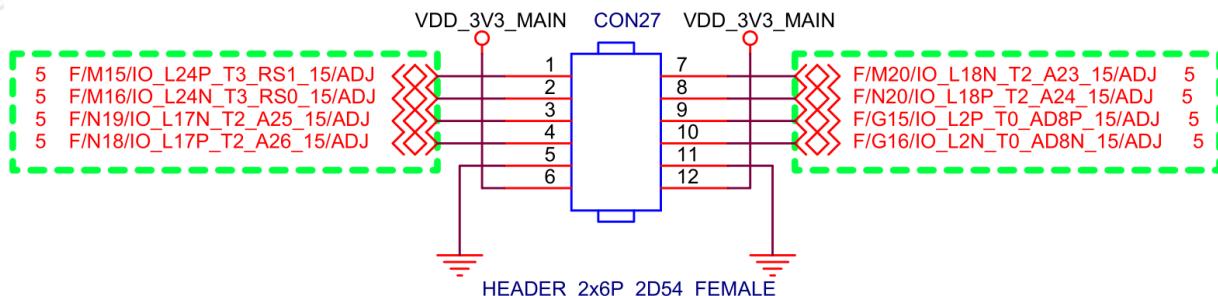

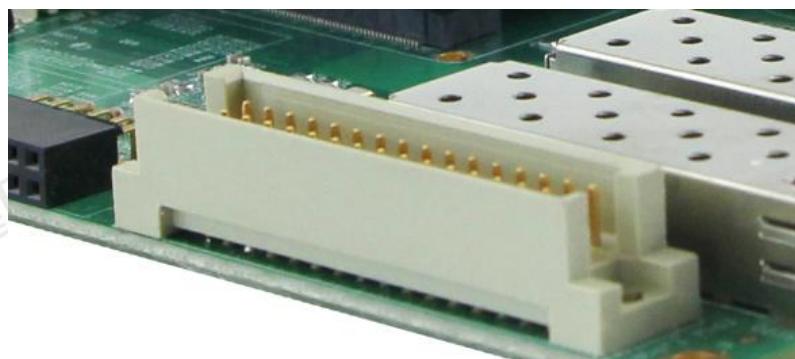

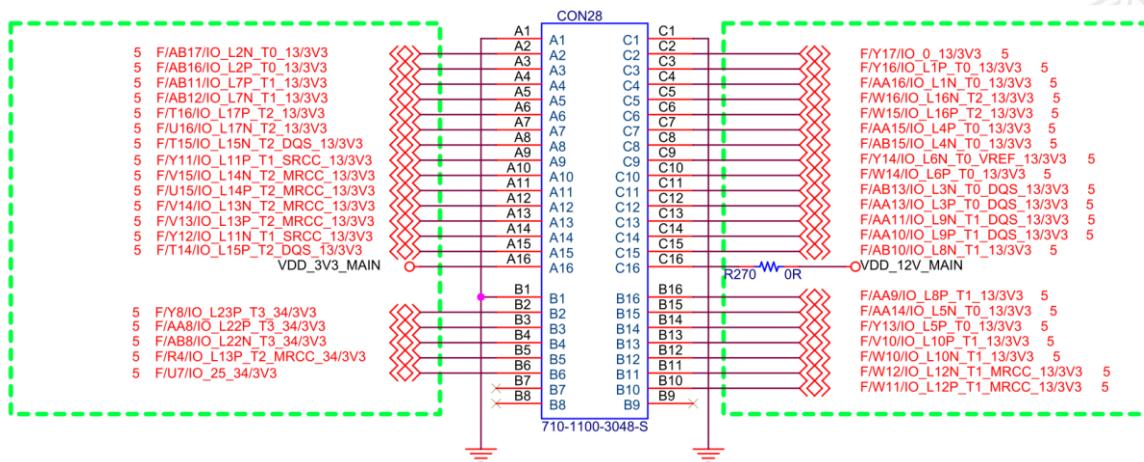

## 11 FPGA ExPORT 拓展口

开发板 CON28 口为 FPGA ExPORT 拓展口，以 48 pin 的欧式端子公座连接器引出 FPGA 相关引脚信号，支持广州创龙 TL287P, TL288AP, TL7123P 模块，硬件及引脚定义如下图：

图 18

图 19

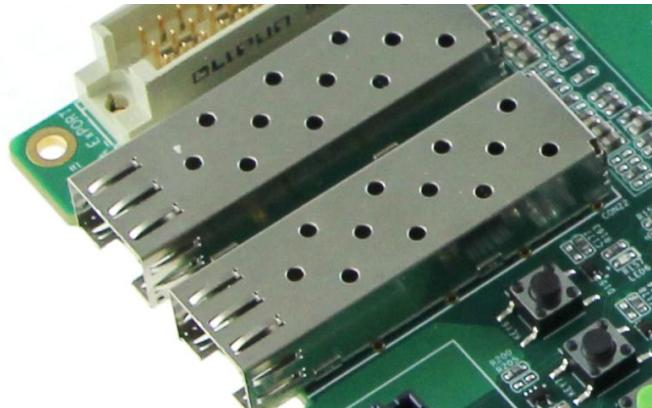

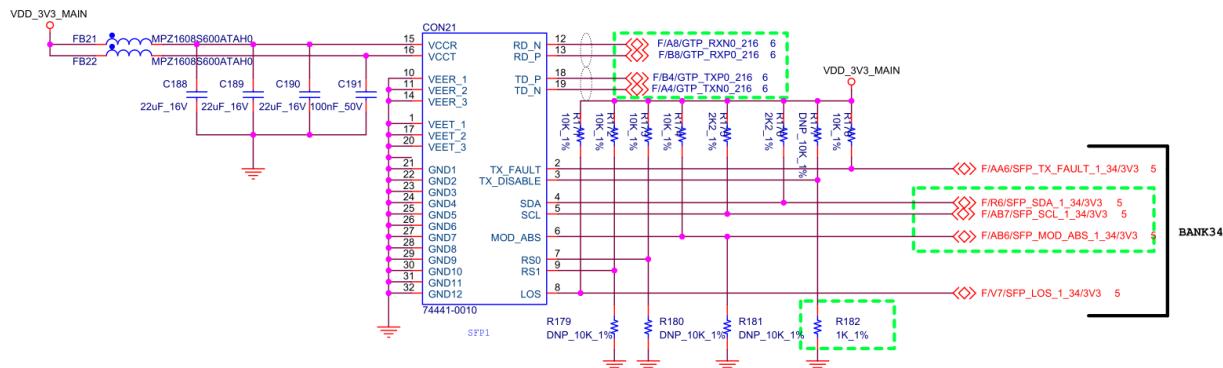

## 12 SFP 接口

开发板引出 CON21、CON22 两路 SFP 接口，传输速率可高达 5Gbit/s，可接 SFP 光口模块或 SFP 电口模块。硬件及引脚定义如下图：

图 20

图 21

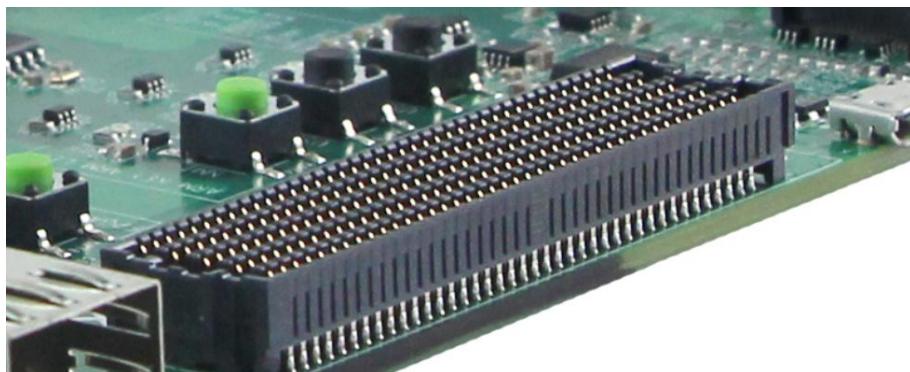

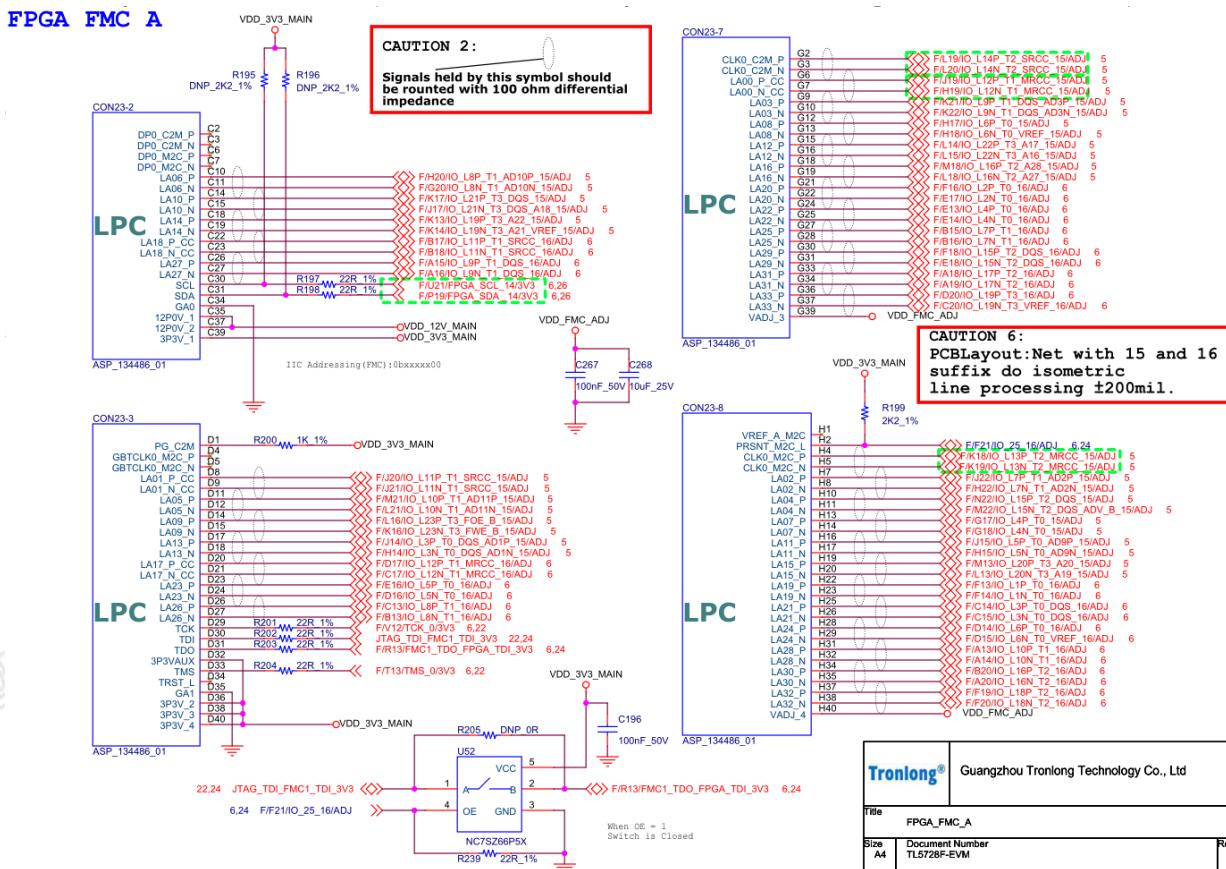

### 13 FMC 接口

开发板上引出了 1 个工业级 FMC 连接器，支持高速 ADC、DAC 和视频输入输出等 FMC-LPC 标准模块，硬件及引脚定义如下图：

图 22

图 23

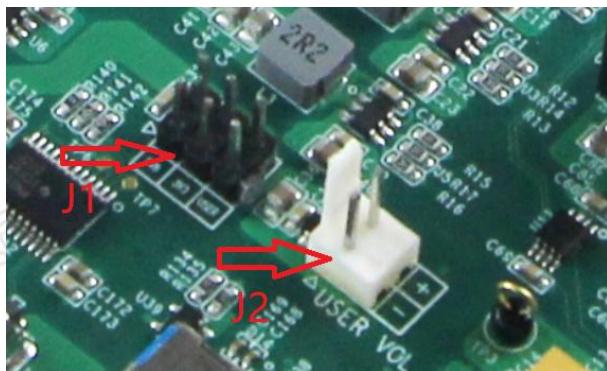

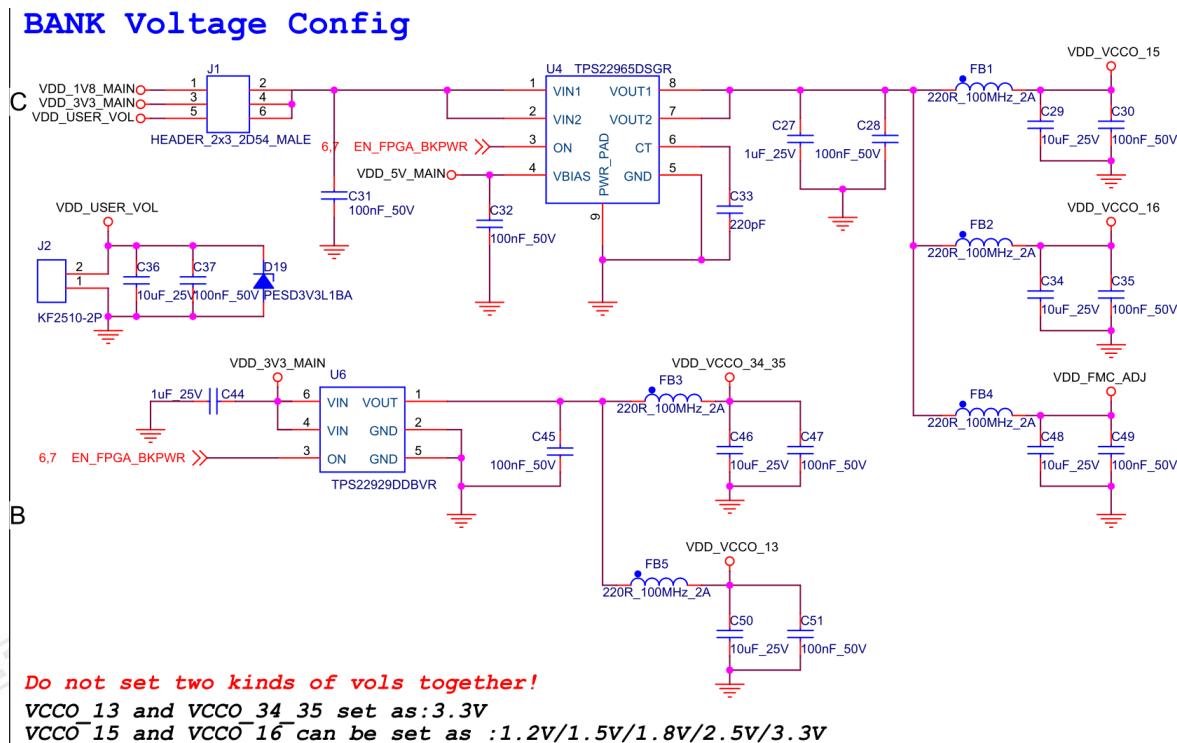

## 14 BANK 电压配置接口

开发板上引出两个 BANK 电压配置接口 J1 和 J2, J1 接口通过跳线帽可选模式为 1.8V、3.3V 和 USER\_VOL 三种, J2 为 FPGA BANK15/16 和 FMC 的电压选择跟外部用户电压输入脚, 外部用户电压输入不能超过 3.3V, 硬件及引脚定义如下图:

图 24

图 25

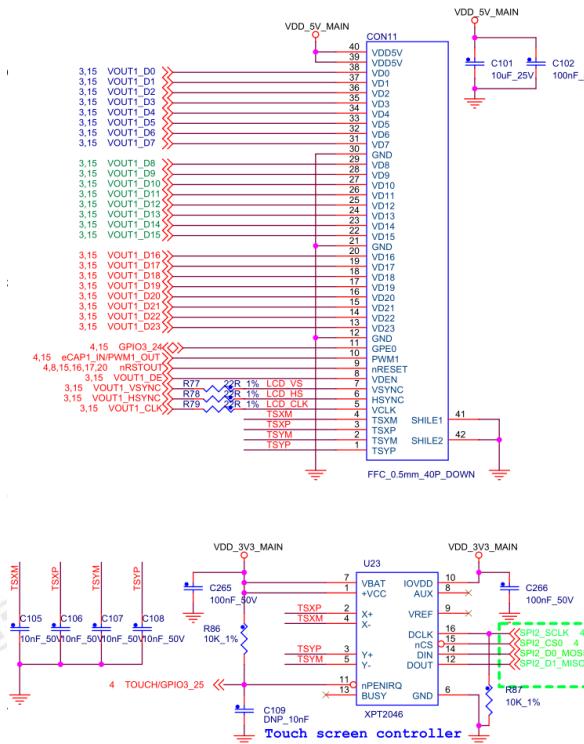

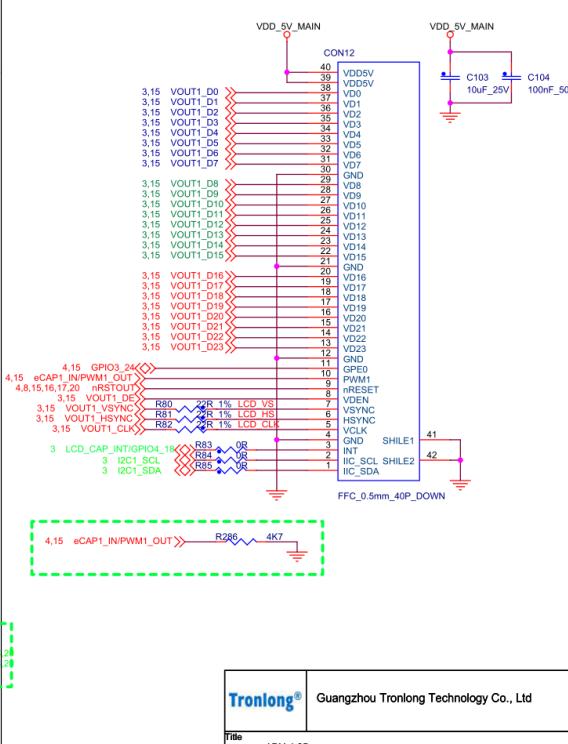

## 15 LCD 触摸屏接口

开发板总共引出两路触摸屏接口，40pin、0.5mm 间距，使用 FFC 排线座。其中 CON11 为 LCD 电阻触摸屏接口，CON12 为 LCD 电容触摸屏接口。LCD 接口包含了常见 LCD 所用全部控制信号（行场扫描、时钟和使能等），接口定义如下图所示：

图 26

## ARM LCD RES

## ARM LCD CAP

图 27

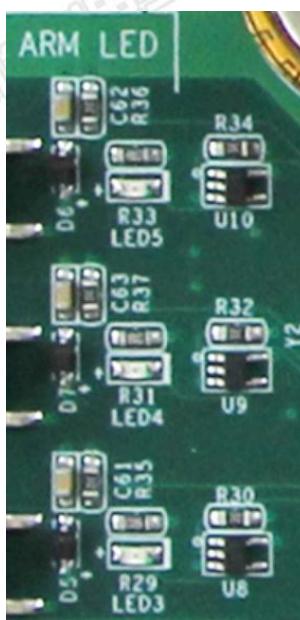

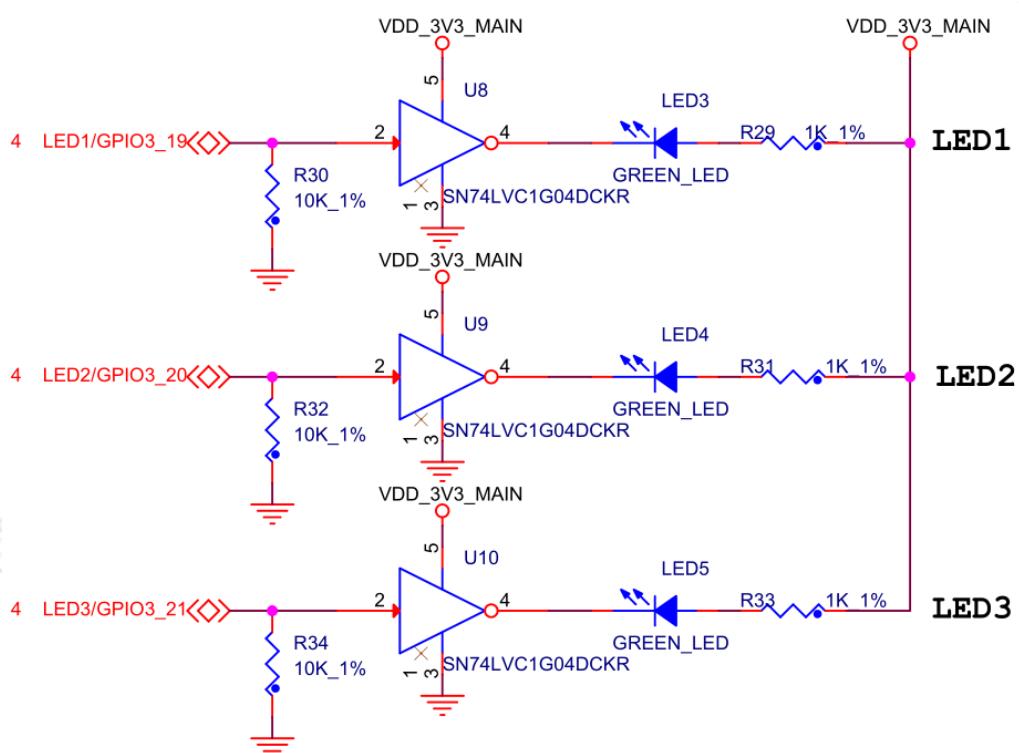

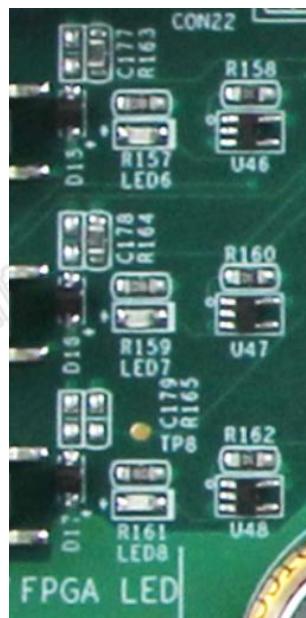

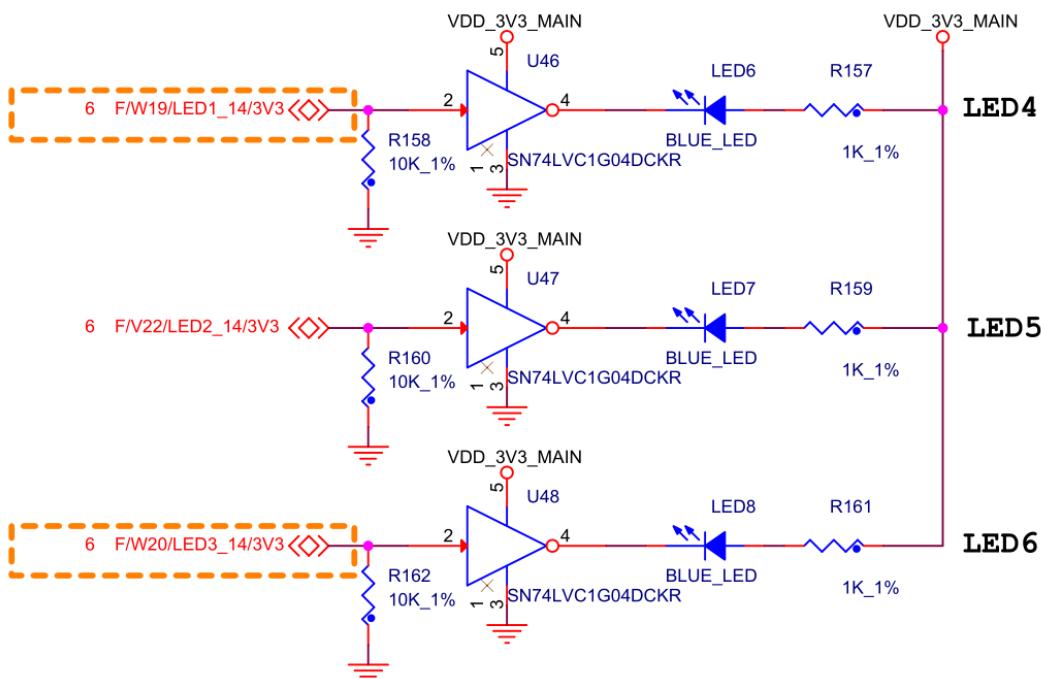

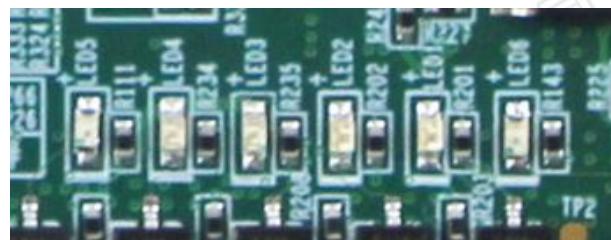

## 16 LED 指示灯

开发板底板具有 3 个 ARM 端用户可编程指示灯 LED3、LED4、LED5 和 3 个 FPGA 端用户可编程指示灯 LED6、LED7、LED8，原理图如下：

图 28 ARM LED

创龙

图 29

图 30 FPGA LED

图 31

核心板共设有 6 个 LED 灯：1 个电源指示灯（LED6）、1 个 FPGA DONE 灯（LED5）、2 个 ARM 用户指示灯（LED1、LED2）、2 个 FPGA 用户指示灯（LED3、LED4）。

图 32

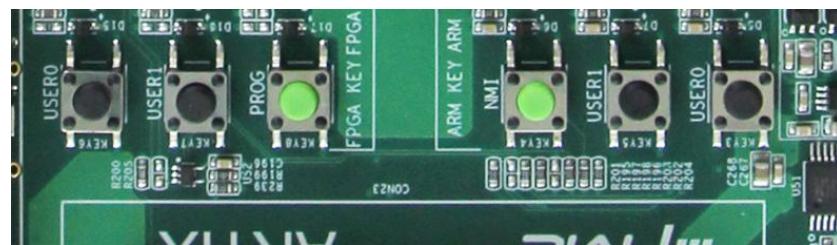

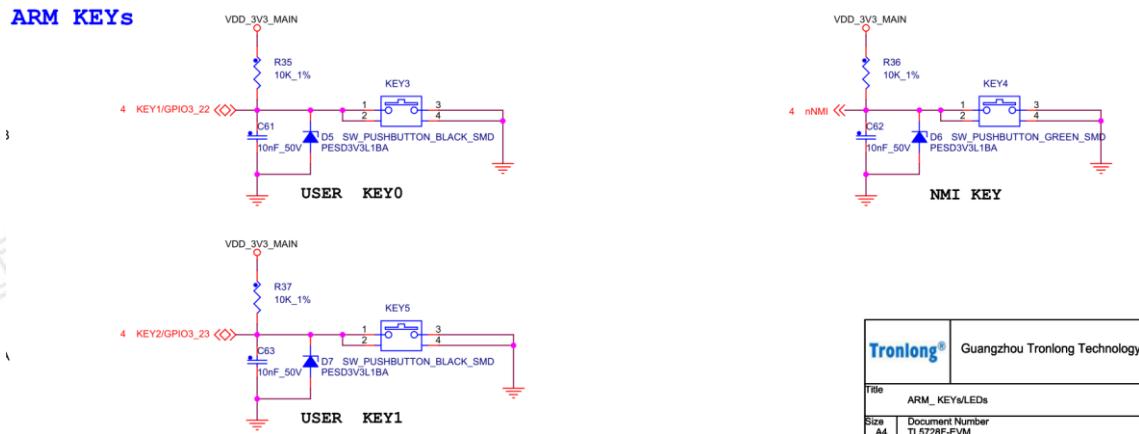

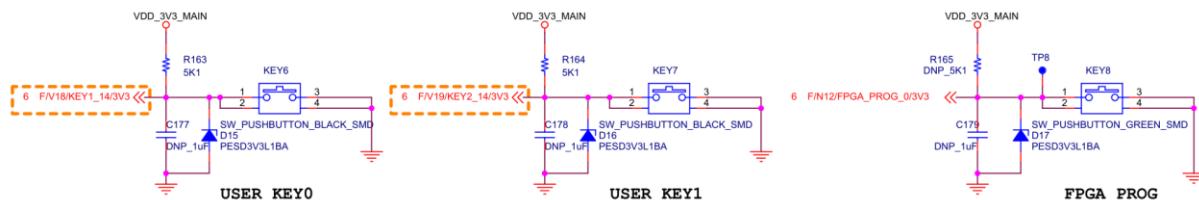

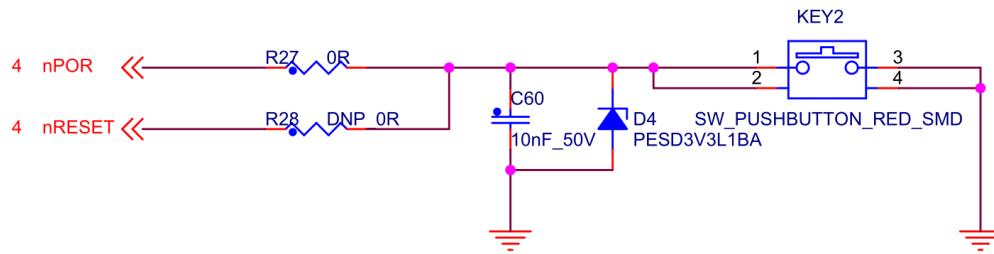

## 17 按键

本开发板总共有 1 个热复位按键 KEY2, 3 个 ARM 端用户按键 KEY3、KEY4(NMI)、KEY5, 3 个 FPGA 端用户按键 KEY6、KEY7、KEY8(PROG), 如下图所示：

图 33 用户按键

图 34

## FPGA USER KEYS

图 35

图 36 热复位按键 KEY2

## WARM RESET

图 37

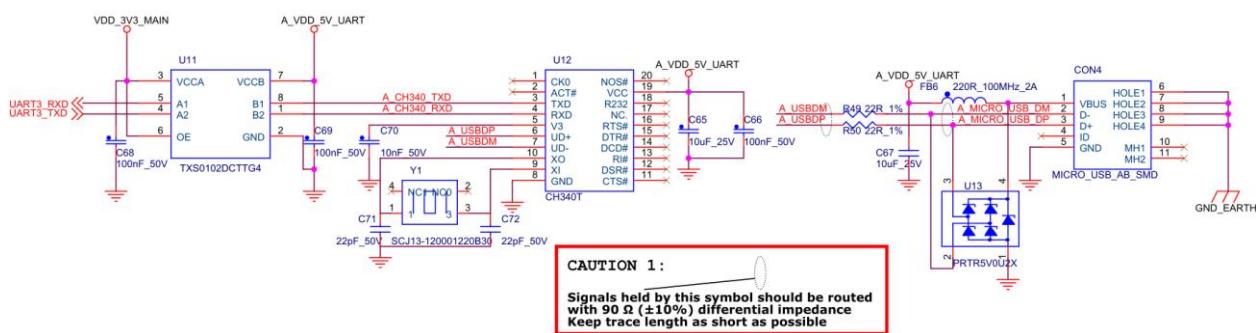

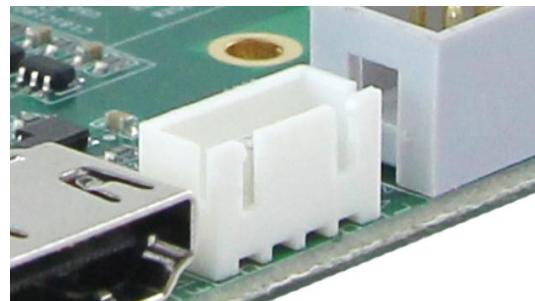

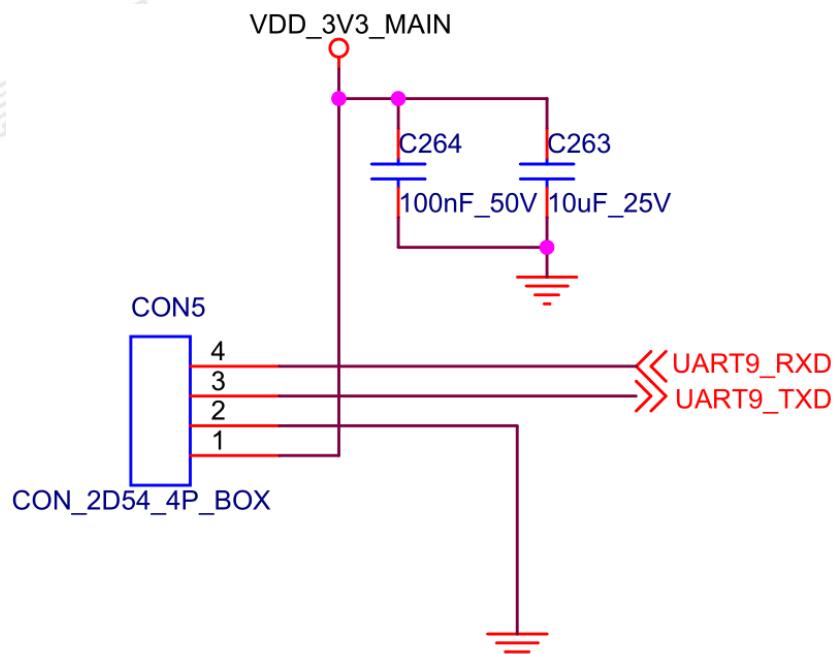

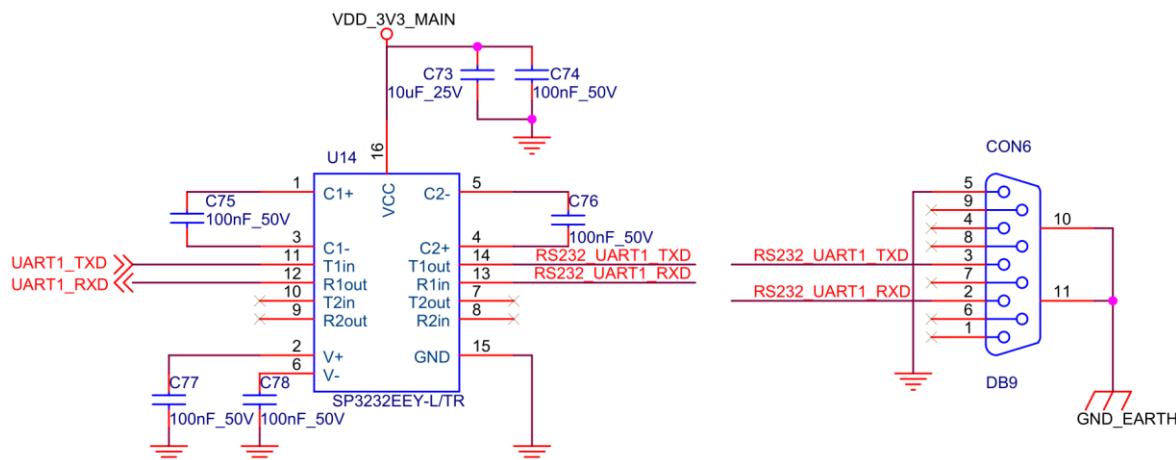

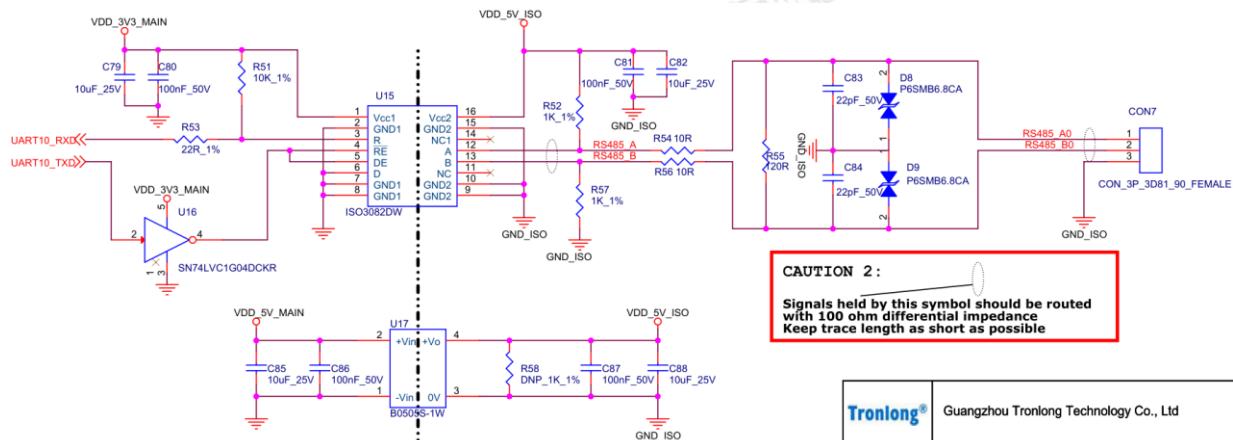

## 18 串口

开发板上共引出了 5 路串口，分别为 CON4、CON5、CON6、CON7、CON19。其中 CON4 由 UART3 通过 CH340T 芯片转成 Micro USB 接口；CON5 由 UART9 通过白色排针端子引出 LVCMOS 电平串口；CON6 由 UART1 通过 SP3232EEY-L/TR 串口电平转换芯片转换为 RS232 串口，使用 9 针 DB9 接口；CON7 由 UART10 转换成 RS485 串口，使用 3 位接线端子；FPGA 端 CON19 由 UART3 通过 CH340T 芯片转成 Micro USB 接口；

图 38 USB to UART3

图 39

图 40 LVC MOS UART9

图 41

图 42 RS232

图 43

图 44RS485

图 45

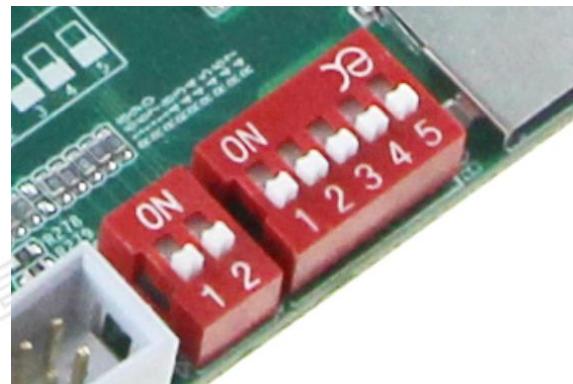

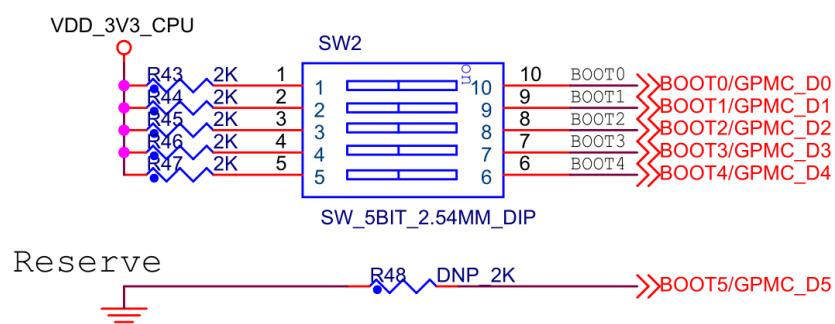

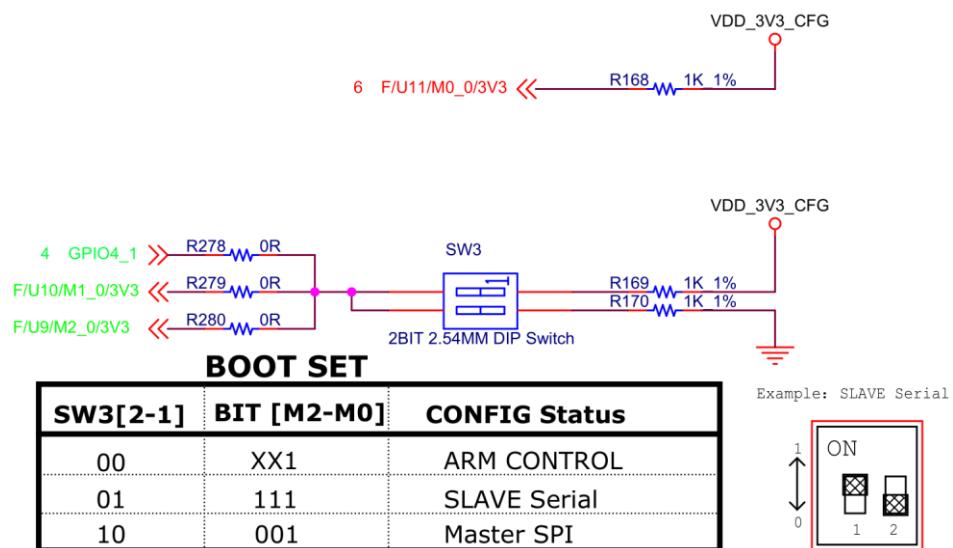

## 19 BOOTSET 启动选择开关

开发板引出 SW2、SW3 拨码开关，ON 为 1，相反为 0。其中 SW2 为 ARM 端 5 位启动选择开关，SW3 为 FPGA 端 2 位启动选择开关，详情如下图所示：

图 46

| BOOT DEVICE FIRSTST | BTMODE [4 : 0] |

|---------------------|----------------|

| eMMC                | 00000          |

| SD                  | 00010          |

| QSPI_1              | 00110          |

| SATA                | 00011          |

| USB                 | 00001          |

| UART                | 00100          |

图 47 ARM BOOTMODE

图 48 FPGA BOOTMODE

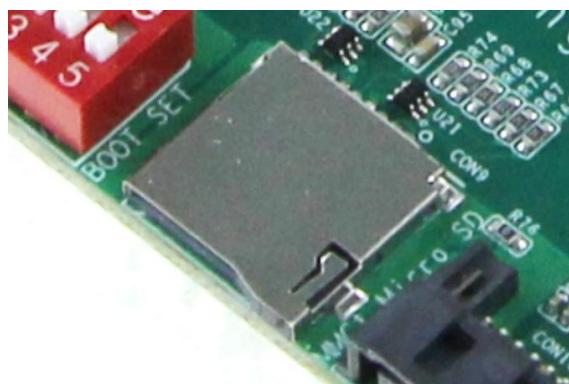

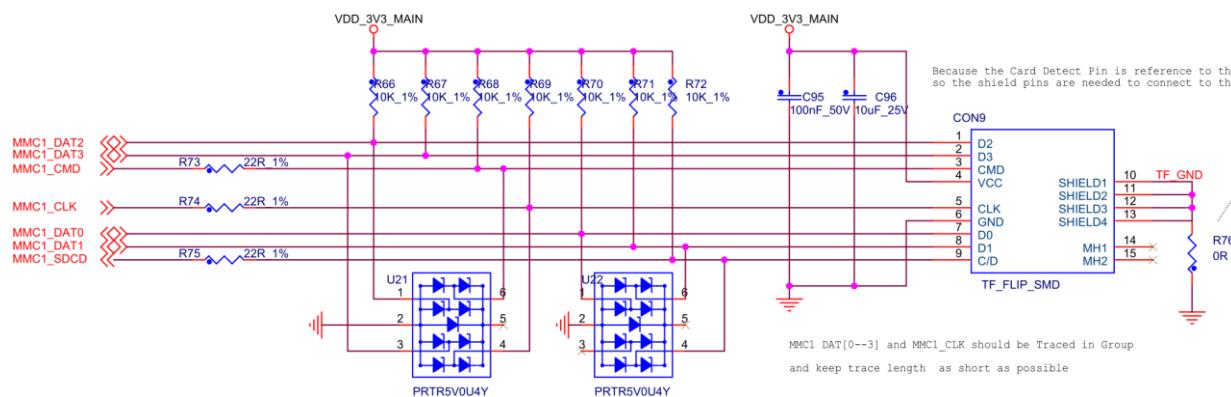

## 20 MicroSD 接口

CON9 是 MicroSD 卡接口, 主要用于外接大容量数据存储, 具体接口定义如下图所示:

图 49

图 50

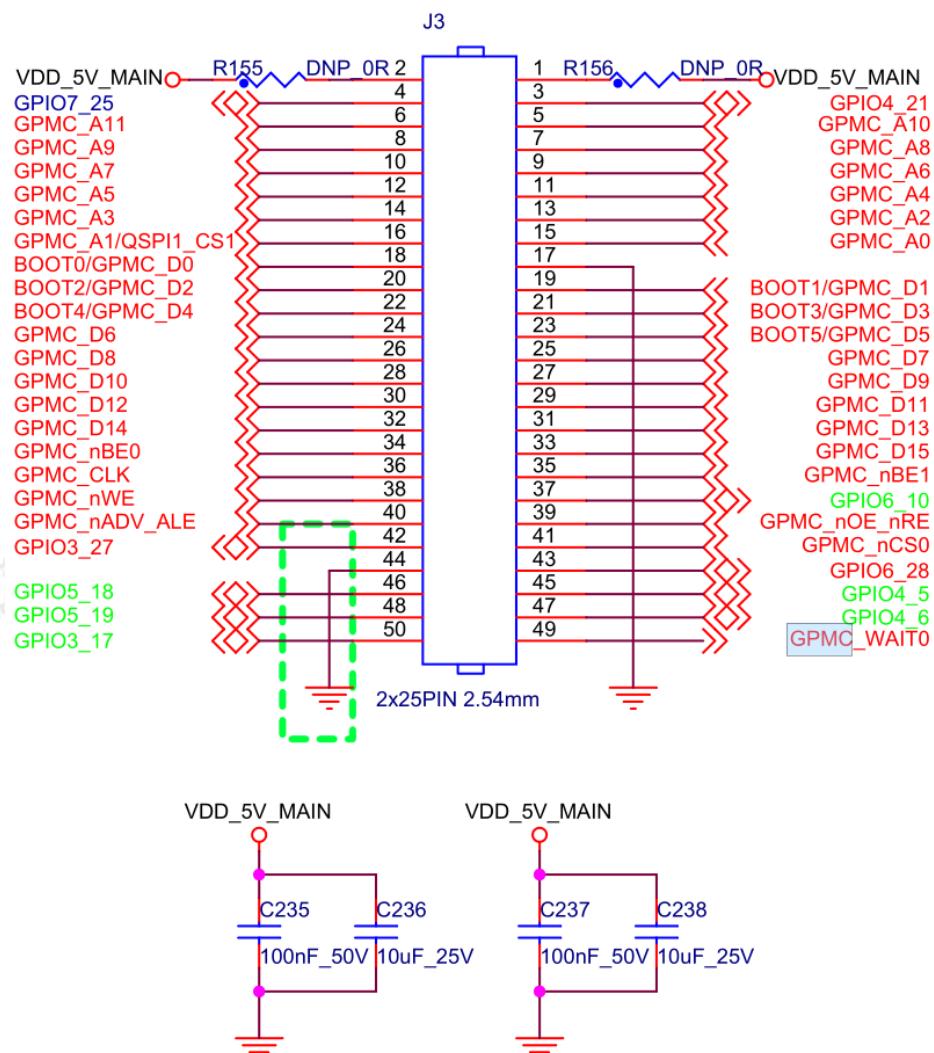

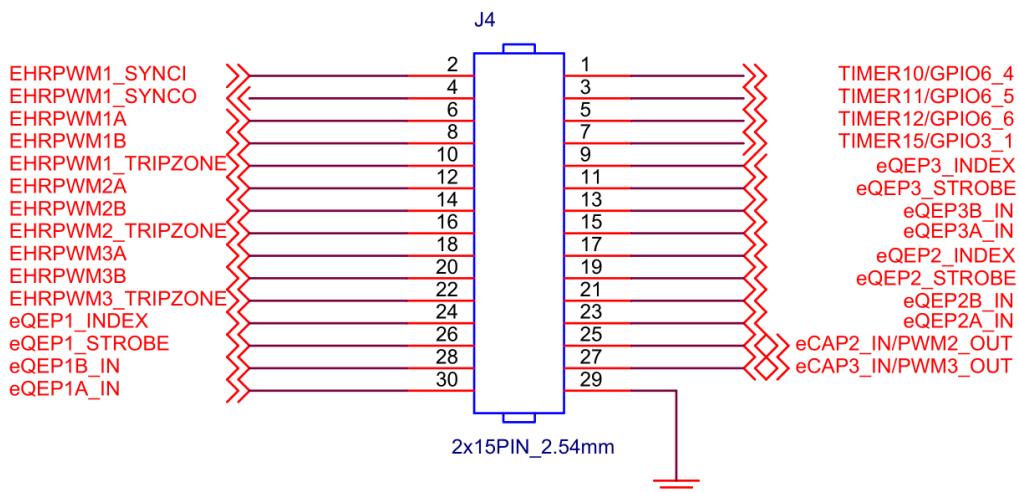

## 21 拓展 IO 信号

开发板 J3 端口引出了 GPMC/QSPI 拓展信号, J4 引出了 eHRPWM/eQEP/TIMER/eCAP 拓展信号。其硬件图及引脚定义如下:

图 51 GPMC/QSPI 拓展信号 (J3)

图 52

图 53 eHRPWM/eQEP/TIMER/eCAP 拓展信号 (J4)

图 54

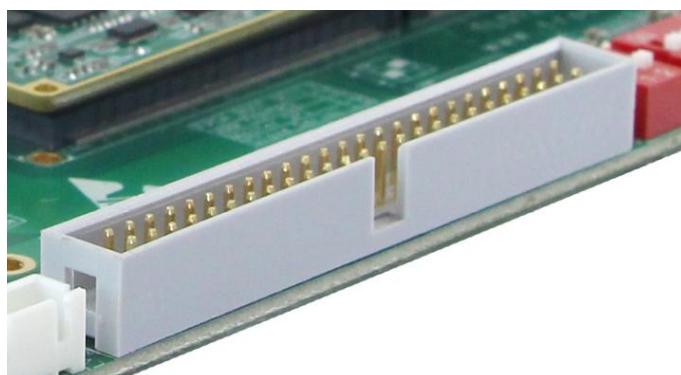

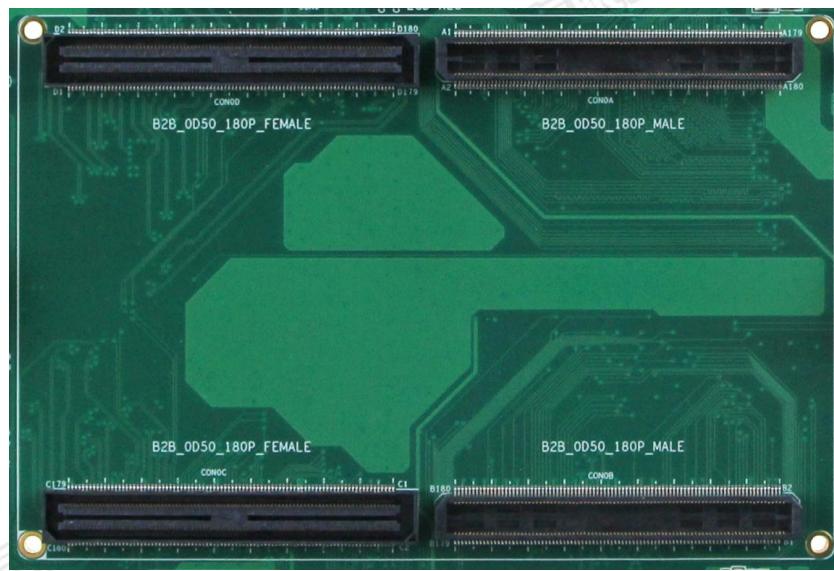

## 22 底板 B2B 连接器

开发板使用底板+核心板设计模式，通过 2x 180pin 高速 B2B 公座连接器，2x 180pin 高速 B2B 母座连接器，间距 0.5mm，合高 5mm，共 720pin，其中底板 CON0C 和 CON0D 为母座，CON0A 和 CON0B 为公座，下图为底板各个 B2B 的实物图，引脚定义详见光盘中的底板原理图：

图 55

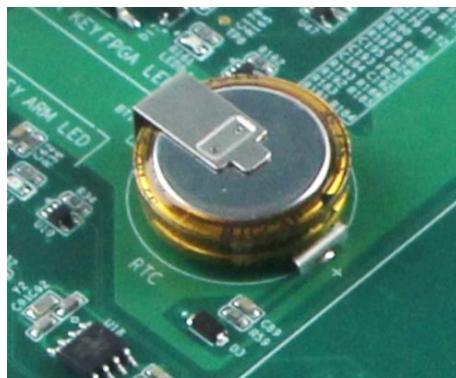

## 23 RTC 座

# 创龙

开发板通过外部扩展 RTC 时钟控制器，接 1.5F 法拉电容。引脚定义如下图：

图 56

图 57

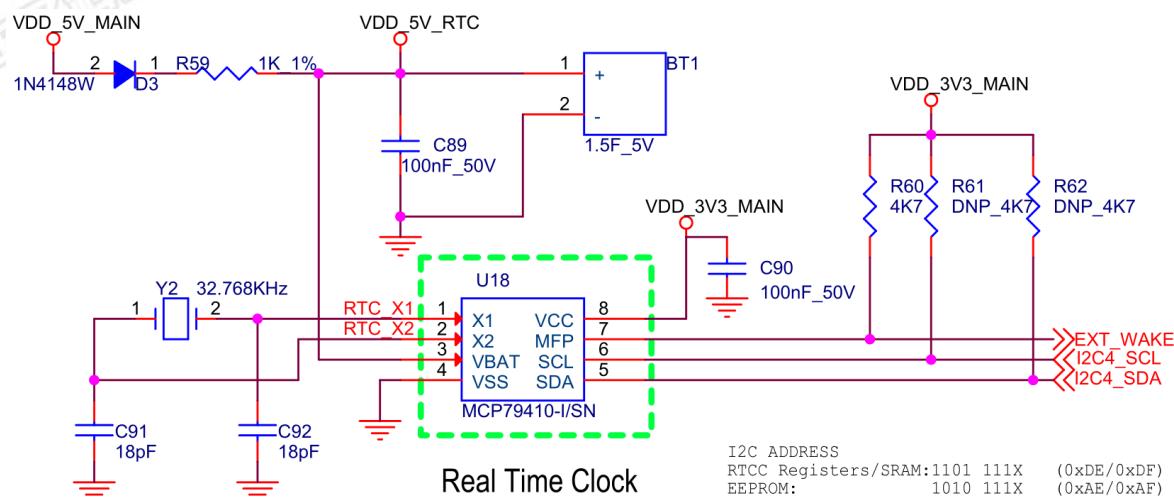

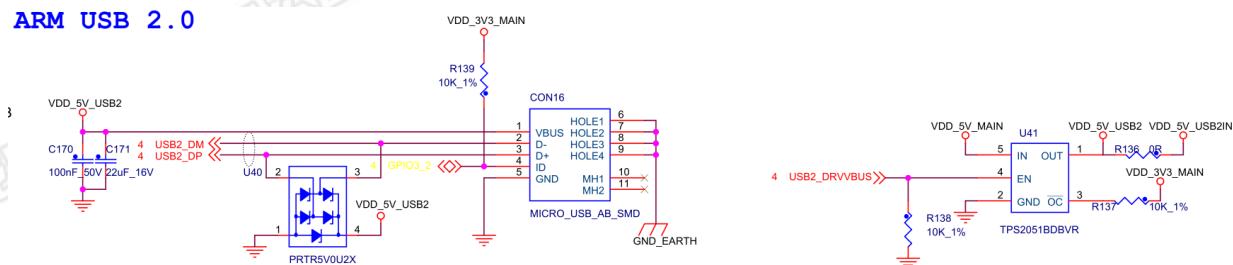

## 24 USB 接口

CON4 为 MicroUSB 2.0 接口，应用于各种不同的移动设备间的连接，进行数据交换，传输速度高达 480Mbps。CON15 是 USB 3.0 接口，理论速度 5.0Gbps，可以接 USB 摄像头、USB 键盘、USB 鼠标、U 盘等常见的 USB 外设。对应引脚定义如下图：

图 58USB 3.0 接口

ARM USB 2.0

图 59

图 60MicroUSB 2.0 接口

图 61

## 25 RGMII 千兆以太网口

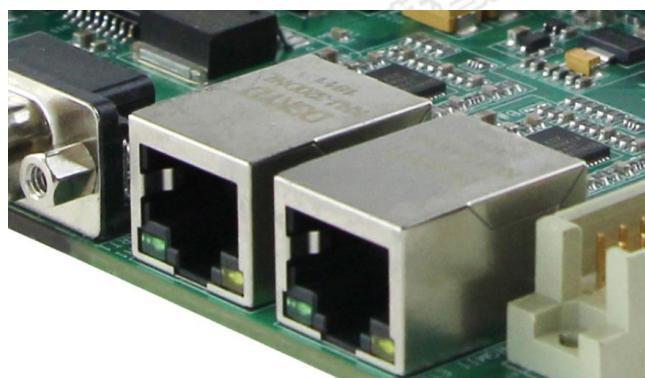

开发板配备了两个 RGMII 千兆以太网口 CON13 和 CON14，采用了 KSZ9031RNXIA 网络芯片，可自适应 10/100/1000M 网络，RJ45 连接头内部已经包含了耦合线圈，因此不必另接网络变压器，使用普通的直连网线即可连接本开发板至路由器或者交换机。引脚定义详见光盘中的底板原理图：

图 62

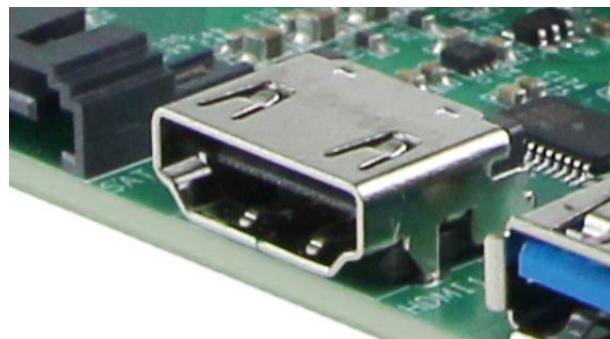

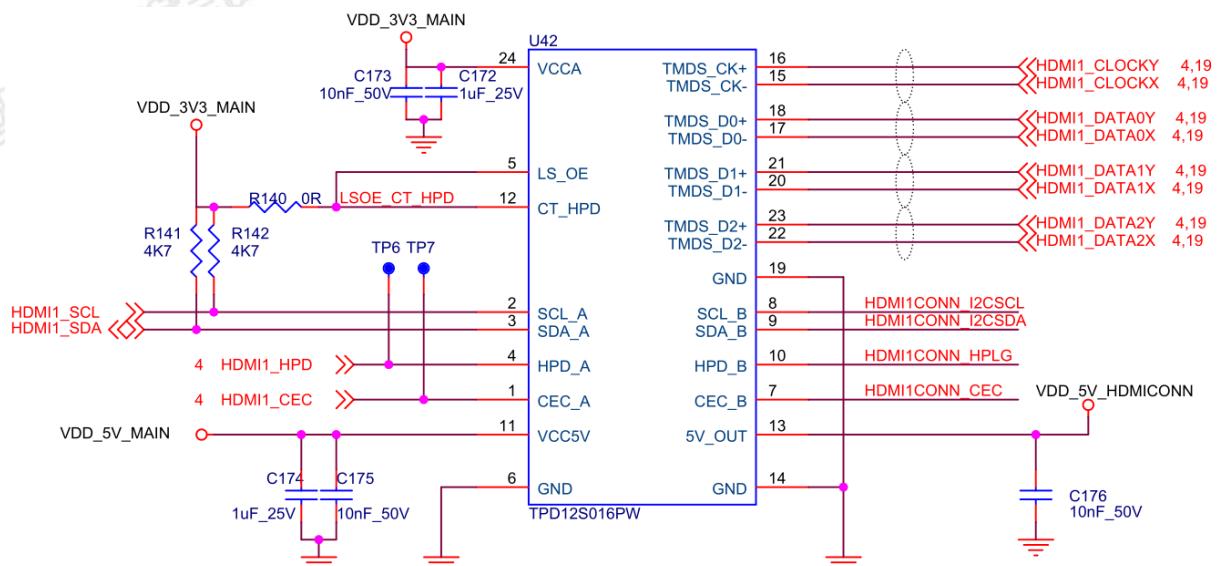

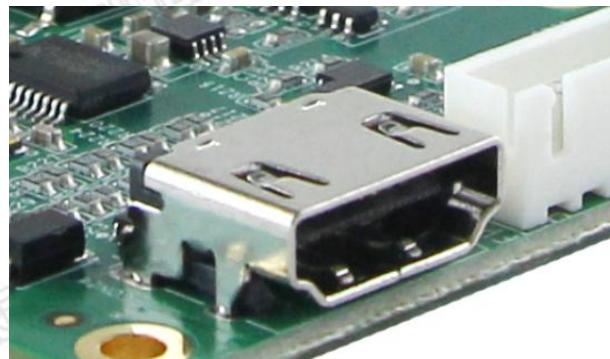

## 26 HDMI OUT 接口

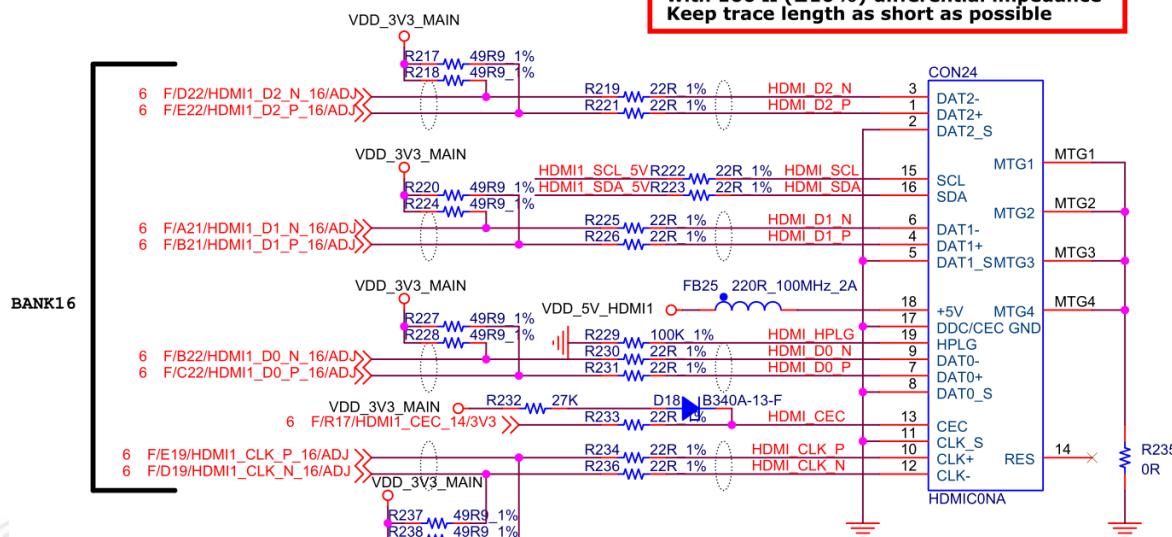

开发板配有 2 路高清晰度 HDMI 输出接口，包括 ARM 端的 HDMI OUT (CON17) 和 FPGA 端的 HDMI (CON24)，支持 1080p 高清视频，引脚定义如下图：

图 63HDMI OUT

图 64

图 65FPGA HDMI

劍龍

### Before using HDMI1,VCCO\_16 set as 3V3

**CAUTION 2:**

**Signals held by this symbol should be routed with  $100\ \Omega$  ( $\pm 10\%$ ) differential impedance

Keep trace length as short as possible**

图 66

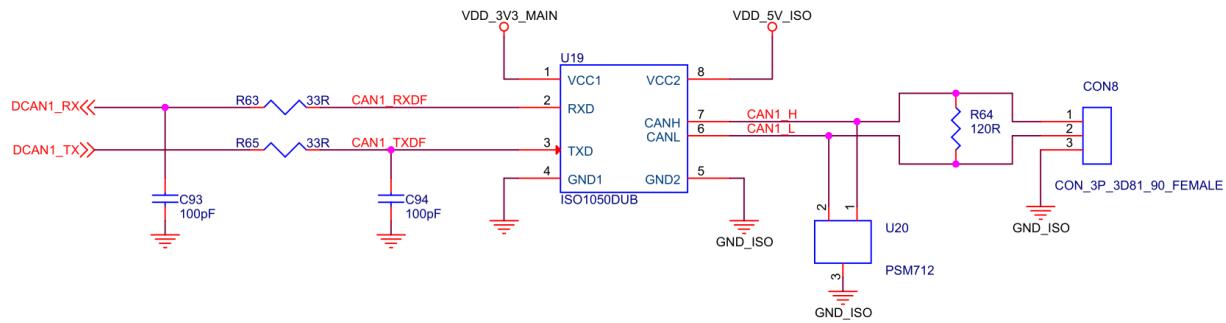

27 CAN 总线接口

开发板搭载有一个 CAN 总线接口 CAN1。CON8 为对应接线端子，使用隔离式芯片 ISO1050 作为 CAN 收发器，接口定义如下图：

图 67

图 68

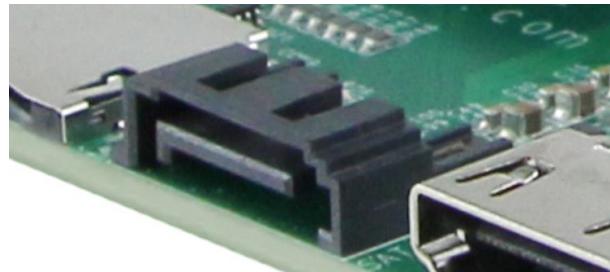

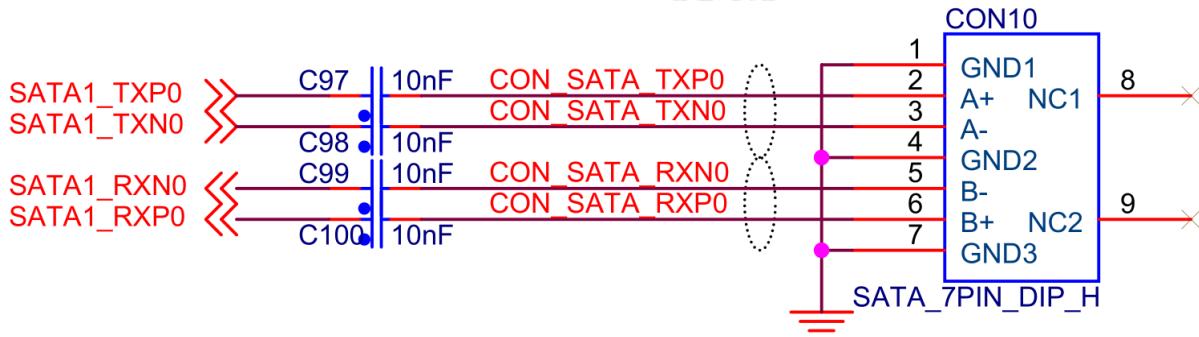

## 28 SATA 接口

开发板引出了一个 SATA 硬盘接口，接口为 CON10，硬件及引脚如图：

图 69

图 70

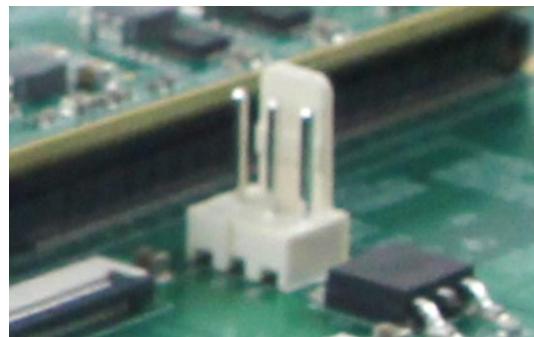

## 29 散热风扇接口

J6 为开发板散热风扇接口，采用 3pin，间距 2.54mm，供电电压为 12V。

图 71

图 72

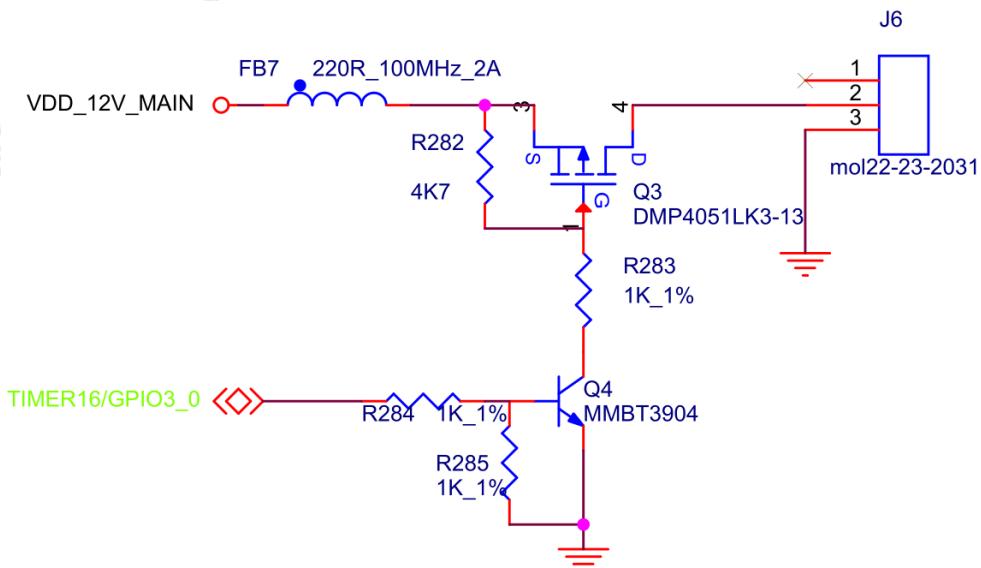

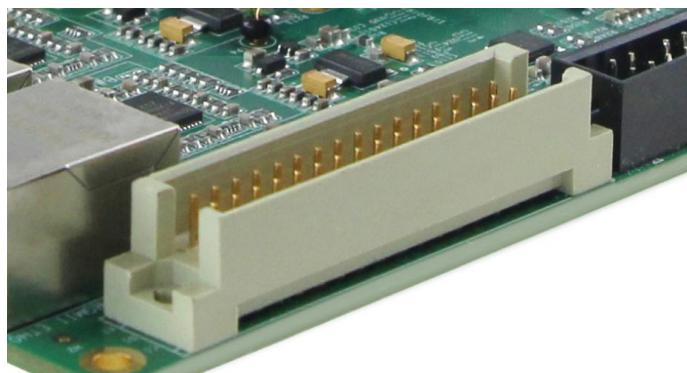

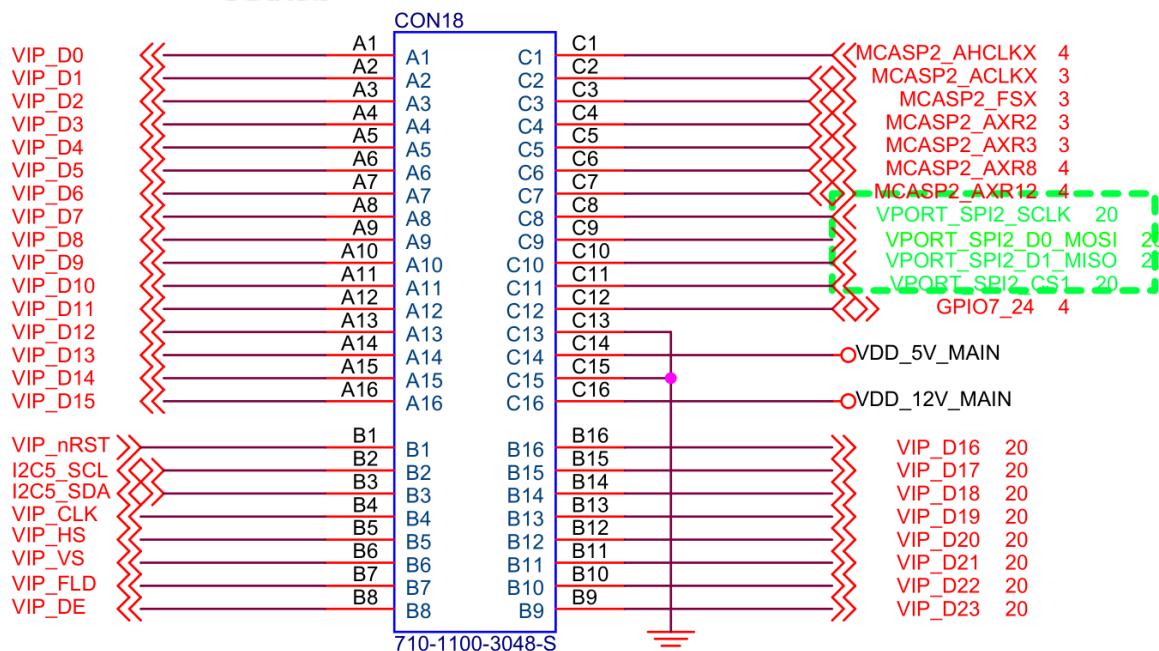

### 30 视频输入拓展口 (V-PORT)

开发板 CON18 接口为视频输入拓展口，以 48 pin 的欧式端子公座连接器引出了 CPU 视频输入通道的 VIN4 和 McASP2、SPI2、I2C5。可以配套广州创龙视频输入拓展模块使用，如：TVP5158 四路 D1 视频采集模块，GV7601 HD-SDI 视频采集模块等。

图 73

图 74

图 75 TVP5158D1 视频采集模块

图 76 GV7601 HD-SDI 视频采集模块

## 更多帮助

销售邮箱: [sales@tronlong.com](mailto:sales@tronlong.com)

技术邮箱: [support@tronlong.com](mailto:support@tronlong.com)

创龙总机: 020-8998-6280

技术热线: 020-3893-9734

创龙官网: [www.tronlong.com](http://www.tronlong.com)

技术论坛: [www.51ele.net](http://www.51ele.net)

线上商城: <https://tronlong.taobao.com>