# Throughput Performance Guide for C66x KeyStone Devices

High-Performance and Multicore Processors

#### **Abstract**

This document analyzes various performance measurements of the KeyStone Architecture C66x device. It provides a throughput analysis of the various DSP support peripherals as well as EDMA transfer times to different end-points and memory access.

| 1  | Introduction                                                             | 5  |

|----|--------------------------------------------------------------------------|----|

| 2  | KeyStone Device Overview                                                 | 5  |

|    | 2.1 C66x CorePac Overview                                                | 6  |

|    | 2.2 TeraNet Overview                                                     | 7  |

|    | 2.3 Memory Access System Overview                                        | 8  |

| 3  | Memory Access Throughput Performance                                     | 8  |

|    | 3.1 Memory Read Performance                                              | 9  |

|    | 3.2 Memory Write Performance                                             |    |

| 4  | DDR3 Throughput                                                          | 11 |

|    | 4.1 DDR3 Command Interleaving Latency                                    |    |

|    | 4.2 DDR3 Class Of Service Throughput                                     | 12 |

| 5  | EDMA3 Complex Throughput                                                 | 14 |

|    | 5.1 Scenario 1: EDMA Transfer Between CorePac0 L2 and CorePac1 L2        |    |

|    | 5.2 Scenario 2: EDMA Transfer Between Different CorePac L2 and MSMC SRAM | 15 |

|    | 5.3 Scenario 3: EDMA Transfer From MSMC SRAM to MSMC SRAM                | 16 |

|    | 5.4 Scenario 4: EDMA Transfer From MSMC SRAM to DDR3                     | 16 |

|    | 5.5 Scenario 5: EDMA Transfer From DDR3 to DDR3                          | 17 |

|    | 5.6 Scenario 6: EDMA Transfer From Different CorePac L2 to DDR3          | 17 |

| 6  | BCP Throughput                                                           | 18 |

| 7  | FFTC Throughput                                                          | 19 |

| 8  | Gigabit Ethernet Switch Subsystem                                        | 22 |

|    | 8.1 SGMII-SerDes Clocking Considerations                                 | 22 |

|    | 8.2 Transmit Throughput Performance                                      | 23 |

|    | 8.3 Receive Throughput Performance                                       |    |

| 9  | Inter-integrated Circuit (I <sup>2</sup> C)                              | 24 |

|    | 9.1 Theoretical Throughput Performance                                   | 24 |

|    | 9.2 Measured Throughput Performance                                      | 26 |

| 10 | Multicore Navigator Throughput                                           | 27 |

|    | 10.1 Navigator PUSH Latency                                              | 27 |

|    | 10.2 Navigator POP Latency                                               | 28 |

|    | 10.3 Queue Access Through Different Access Regions                       | 29 |

|    | 10.4 Navigator Linking RAM Performance                                   | 30 |

|    | 10.5 Infrastructure PKTDMA Performance                                   |    |

|    | 10.6 Accumulator Interrupt Latency                                       | 32 |

|    | 10.7 Other Performance Considerations for Queue Operation                | 33 |

|    | 10.7.1 Monolithic Descriptors vs. Host Descriptors                       |    |

|    |                                                                          |    |

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this document.

|                                        | 10.7.2 Descriptors in Cacheable Memory vs. Non-Cacheable Memory                                                                                                                                                                                                                                              |                |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

|                                        | 10.8 PKTDMA Bandwidth                                                                                                                                                                                                                                                                                        |                |

|                                        | 10.8.1 PKTDMA Transfer Overhead                                                                                                                                                                                                                                                                              |                |

|                                        | 10.8.2 PKTDMA Bandwidth                                                                                                                                                                                                                                                                                      |                |

| 11                                     | Packet Accelerator (PA)                                                                                                                                                                                                                                                                                      | 35             |

| 12                                     | 2 PCle                                                                                                                                                                                                                                                                                                       |                |

|                                        | 12.1 Main Factors Affecting PCle Throughput Performance                                                                                                                                                                                                                                                      |                |

|                                        | 12.1.1 Overhead Considerations                                                                                                                                                                                                                                                                               |                |

|                                        | 12.1.2 Packet Size Considerations                                                                                                                                                                                                                                                                            | 37             |

|                                        | 12.1.3 EDMA Considerations                                                                                                                                                                                                                                                                                   | 37             |

|                                        | 12.2 How to Achieve Maximum Throughput with the PCle Peripheral                                                                                                                                                                                                                                              |                |

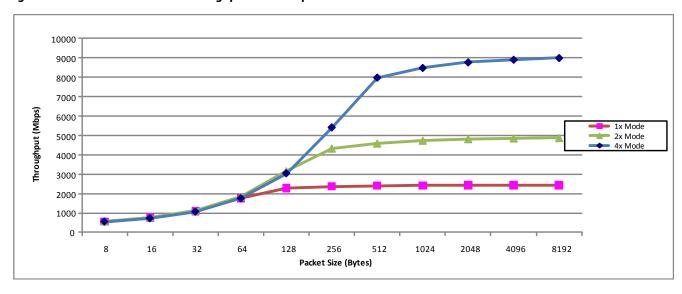

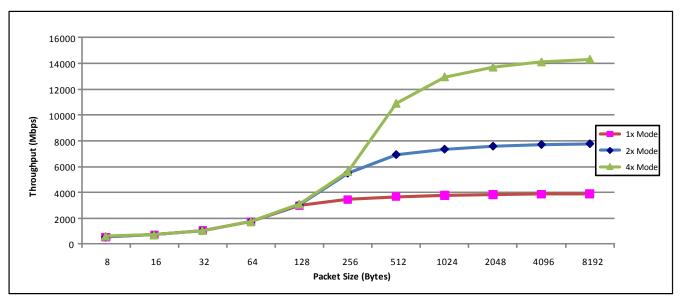

|                                        | 12.3 Measured Throughput Performance                                                                                                                                                                                                                                                                         | 38             |

|                                        | 12.3.1 Read Throughput Performance                                                                                                                                                                                                                                                                           | 38             |

|                                        | 12.3.2 Write Throughput Performance                                                                                                                                                                                                                                                                          |                |

| 13                                     | RAC Throughput                                                                                                                                                                                                                                                                                               | 40             |

| 14                                     | 4 SPI                                                                                                                                                                                                                                                                                                        | 41             |

|                                        | 14.1 Theoretical Throughput Performance                                                                                                                                                                                                                                                                      | 41             |

|                                        | 14.2 Measured Throughput Performance                                                                                                                                                                                                                                                                         | 41             |

| 15                                     | 5 SRIO Throughput                                                                                                                                                                                                                                                                                            | 41             |

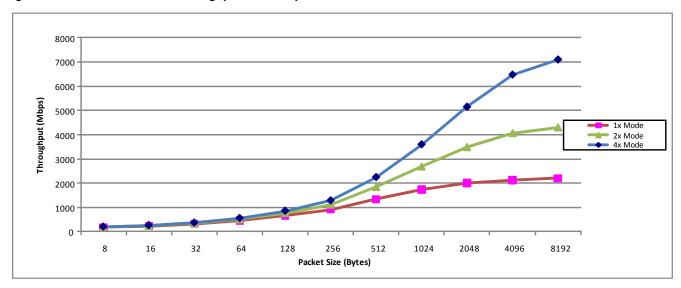

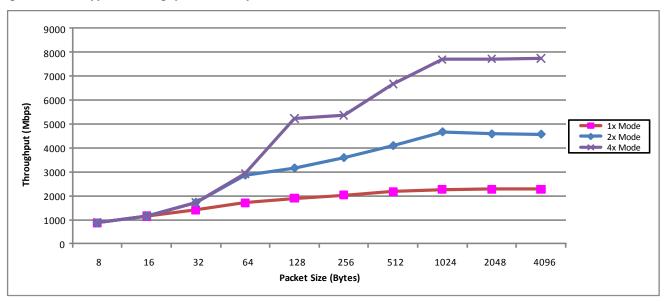

|                                        | 15.1 DirectlO (LSU) Operation:                                                                                                                                                                                                                                                                               | 42             |

|                                        | 15.2 Message Passing Throughput                                                                                                                                                                                                                                                                              |                |

|                                        | 15.2.1 Type 11 Throughput                                                                                                                                                                                                                                                                                    |                |

|                                        | 15.2.2 Type 9 Throughput                                                                                                                                                                                                                                                                                     |                |

| 16                                     |                                                                                                                                                                                                                                                                                                              |                |

| 17                                     |                                                                                                                                                                                                                                                                                                              |                |

|                                        | 17.1 TCP3d Processing Modes                                                                                                                                                                                                                                                                                  |                |

|                                        | 17.1.1 LTE Throughput                                                                                                                                                                                                                                                                                        |                |

|                                        | 17.1.2 WCDMA/HSPA Throughput                                                                                                                                                                                                                                                                                 |                |

|                                        | 17.1.3 WiMAX Throughput                                                                                                                                                                                                                                                                                      |                |

| 18                                     | 3 TCP3e Throughput                                                                                                                                                                                                                                                                                           |                |

|                                        | 18.1 LTE Mode Throughput                                                                                                                                                                                                                                                                                     |                |

|                                        | 18.2 WCDMA/HSPA Mode Throughput                                                                                                                                                                                                                                                                              |                |

|                                        | 18.3 WiMAX Mode Throughput                                                                                                                                                                                                                                                                                   |                |

| 19                                     | - ·                                                                                                                                                                                                                                                                                                          |                |

|                                        | 19.1 Theoretical Throughput Performance                                                                                                                                                                                                                                                                      |                |

|                                        | 19.2 Measured Throughput Performance                                                                                                                                                                                                                                                                         |                |

| 20                                     | VCP2 Throughput                                                                                                                                                                                                                                                                                              |                |

| 21                                     | <b>5</b> .                                                                                                                                                                                                                                                                                                   |                |

|                                        |                                                                                                                                                                                                                                                                                                              |                |

|                                        |                                                                                                                                                                                                                                                                                                              |                |

| Tala                                   | hla 1 - Davimhavala Curanavataal hu Davit Numbay                                                                                                                                                                                                                                                             | _              |

|                                        | ble 1 Peripherals Supported by Part Number                                                                                                                                                                                                                                                                   | 5              |

|                                        | ble 2 Theoretical Bandwidth of Core, IDMA and EDMA                                                                                                                                                                                                                                                           |                |

|                                        | ble 3 Theoretical Bandwidth of Different Memories                                                                                                                                                                                                                                                            |                |

|                                        | ble 4 Memory Read Performance                                                                                                                                                                                                                                                                                |                |

|                                        | ble 5 Memory Write Performance                                                                                                                                                                                                                                                                               |                |

|                                        | ble 6 DDR3 READ Command Interleave Cycle Counts                                                                                                                                                                                                                                                              |                |

|                                        | ble 7 DDR3 WRITE Command Interleave Cycle Counts                                                                                                                                                                                                                                                             |                |

|                                        | ble 8 DDR3 READ Command Priority Throughput                                                                                                                                                                                                                                                                  |                |

| Tab                                    | ble 9 DDR3 WRITE Command Priority Throughput                                                                                                                                                                                                                                                                 |                |

| <b>T</b> .                             | II 40 FDMATI I (D. C. D. C.C. IC. D. 415 T. I.                                                                                                                                                                                                                                                               |                |

|                                        | ble 10 EDMA Throughput Between CorePac0 L2 and CorePac1 L2 Endpoints.                                                                                                                                                                                                                                        |                |

| Tab                                    | ble 11 EDMA transfer between different CorePac L2 and MSMC SRAM                                                                                                                                                                                                                                              | 15             |

| Tab<br>Tab                             | ble 11 EDMA transfer between different CorePac L2 and MSMC SRAMble 12 EDMA Throughput Between MSMC SRAM and MSMC SRAM                                                                                                                                                                                        | 15<br>16       |

| Tab<br>Tab<br>Tab                      | ble 11 EDMA transfer between different CorePac L2 and MSMC SRAM                                                                                                                                                                                                                                              | 15<br>16<br>16 |

| Tab<br>Tab<br>Tab<br>Tab               | ble 11 EDMA transfer between different CorePac L2 and MSMC SRAM                                                                                                                                                                                                                                              |                |

| Tab<br>Tab<br>Tab<br>Tab<br>Tab        | ble 11 EDMA transfer between different CorePac L2 and MSMC SRAM ble 12 EDMA Throughput Between MSMC SRAM and MSMC SRAM ble 13 EDMA Throughput Between MSMC SRAM and DDR3 ble 14 EDMA Throughput Between DDR3 and DDR3 ble 15 EDMA Throughput Between Different CorePac L2s to DDR3                           |                |

| Tab<br>Tab<br>Tab<br>Tab<br>Tab<br>Tab | ble 11 EDMA transfer between different CorePac L2 and MSMC SRAM ble 12 EDMA Throughput Between MSMC SRAM and MSMC SRAM ble 13 EDMA Throughput Between MSMC SRAM and DDR3 ble 14 EDMA Throughput Between DDR3 and DDR3 ble 15 EDMA Throughput Between Different CorePac L2s to DDR3 ble 16 BCP LTE Throughput |                |

| Tab<br>Tab<br>Tab<br>Tab<br>Tab<br>Tab | ble 11 EDMA transfer between different CorePac L2 and MSMC SRAM ble 12 EDMA Throughput Between MSMC SRAM and MSMC SRAM ble 13 EDMA Throughput Between MSMC SRAM and DDR3 ble 14 EDMA Throughput Between DDR3 and DDR3 ble 15 EDMA Throughput Between Different CorePac L2s to DDR3                           |                |

**List of Tables**

| Table 19  | 1 <sup>2</sup> C Theoretical Throughput                                | 25 |

|-----------|------------------------------------------------------------------------|----|

| Table 20  | I <sup>2</sup> C Measured Throughput Performance                       | 27 |

| Table 21  | Multicore Navigator PUSH Latency                                       | 28 |

| Table 22  | Multicore Navigator POP Latency                                        | 29 |

| Table 23  | Multicore Navigator PUSH/POP Latency with Linking RAM                  | 31 |

| Table 24  | Infrastructure PKTDMA Receive Throughput                               | 31 |

| Table 25  | Multicore Navigator Accumulator Latency                                |    |

| Table 26  | Measured PCIe Read Throughput Performance                              |    |

| Table 27  | Measured PCIe Write Throughput Performance                             | 40 |

| Table 28  | DirectlO Write Throughput with 3.125 Gbps PHY                          |    |

| Table 29  | DirectIO Read Throughput with 3.125 Gbps PHY                           | 43 |

| Table 30  | DirectIO Write Throughput with 5 Gbps PHY                              | 43 |

| Table 31  | DirectIO Read Throughput with 5 Gbps PHY                               | 44 |

| Table 32  | Type 11 Message Passing Throughput with 3.125 Gbps PHY                 | 47 |

| Table 33  | Type 11 Message Passing Throughput with 5 Gbps PHY                     | 48 |

| Table 34  | Type 9 Message Passing Throughput with 3.125 Gbps PHY                  |    |

| Table 35  | Type 9 Message Passing Throughput with 5 Gbps PHY                      | 50 |

| Table 36  | TAC Complex Throughput                                                 | 51 |

| Table 37  | TCP3d Throughput In LTE Mode                                           | 52 |

| Table 38  | TCP3d Throughput In WCDMA/HSPA Mode                                    |    |

| Table 39  | TCP3d Throughput In WiMAX Mode                                         | 53 |

| Table 40  | TCP3e Throughput For LTE                                               |    |

| Table 41  | TCP3e Throughput For WCDMA/HSPA                                        | 54 |

| Table 42  | TCP3e Throughput For WiMAX                                             |    |

| Table 43  | UART Theoretical Throughput Performance                                | 57 |

| Table 44  | UART Measured Throughput Performance                                   |    |

| Table 45  | VCP2 Hard Decisions Throughput                                         |    |

| Table 46  | VCP2 Soft Decisions Throughput                                         | 59 |

| Table 47  | Document Revision History                                              | 59 |

|           |                                                                        |    |

| Figure 1  | TeraNet and Memory Access Diagram                                      |    |

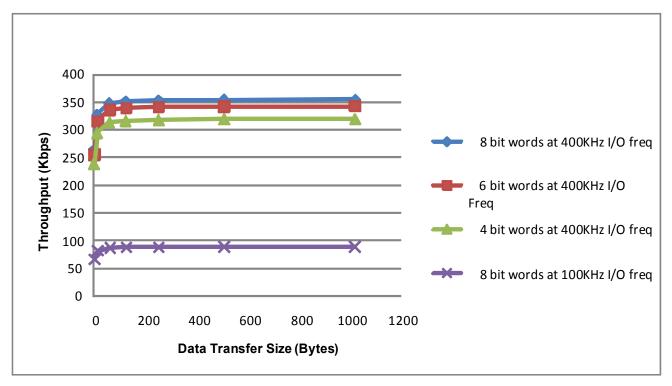

| Figure 2  | I <sup>2</sup> C Theoretical Throughput                                |    |

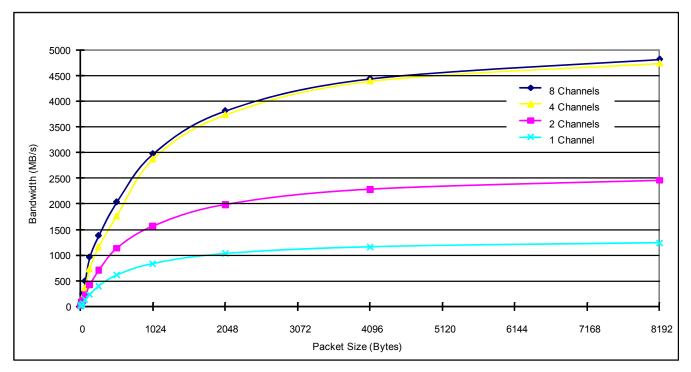

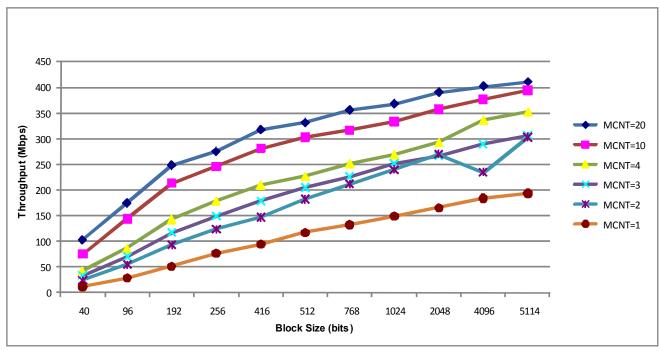

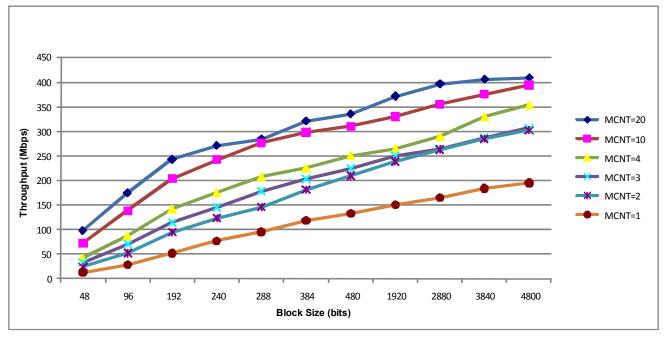

| Figure 3  | QMSS PKTDMA Total Throughput with Multiple Channels LL2-to-LL2         |    |

| Figure 4  | DirectIO NWRITE Throughput with 3 Gbps PHY with Overhead               |    |

| Figure 5  | DirectIO NWRITE Throughput with 5 Gbps PHY with Overhead               |    |

| Figure 6  | DirectIO NREAD Throughput with 3 Gbps PHY with Overhead                | 45 |

| Figure 7  | DirectIO NREAD Throughput with 5Gbps PHY with Overhead                 |    |

| Figure 8  | Type 11 Throughput with 3 Gbps PHY with Overhead                       | 47 |

| Figure 9  | Type 11 Throughput with 5 Gbps PHY with Overhead                       |    |

| Figure 10 | Type 9 Throughput with 3 Gbps PHY with Overhead                        |    |

| Figure 11 | Type 9 Throughput with 5 Gbps PHY with Overhead                        |    |

| Figure 12 | TCP3e Throughput for LTE vs. Block Size (DSP @ 1GHz) (Data in L2RAM)   | 54 |

| Figure 13 | TCP3e Throughput for WCDMA vs. Block Size (DSP @ 1GHz) (Data in L2RAM) |    |

# **Terminology Used In This Document**

| Term | Definition                                                          |

|------|---------------------------------------------------------------------|

| AIF  | Antenna Interface                                                   |

| ВСР  | Bit Coprocessor                                                     |

| CFG  | Configuration                                                       |

| СРРІ | Communications Port Programming Interface (now Multicore Navigator) |

| DSP  | Digital Signal Processor                                            |

| DDR  | Dual Data Rate                                                      |

Figure 14 TCP3e Throughput for WiMAX vs. Block Size (DSP @ 1GHz) (Data in L2RAM) ......56

**List of Figures**

| Term     | Definition                                 |  |  |  |

|----------|--------------------------------------------|--|--|--|

| EMIF     | External Memory Interface Controller       |  |  |  |

| EDMA3    | Enhanced Direct Memory Access v3.0         |  |  |  |

| FFTC     | Fast Fourier Transform Coprocessor         |  |  |  |

| GPIO     | General Purpose Input/Output               |  |  |  |

| I2C      | Inter Integrated Circuit                   |  |  |  |

| IDMA     | Internal Direct Memory Access              |  |  |  |

| LSU      | Load Store Unit                            |  |  |  |

| MSMC     | Multicore Shared Memory Controller         |  |  |  |

| MPU      | Memory Protection Unit                     |  |  |  |

| NETCP    | Network Coprocessor                        |  |  |  |

| PA       | Packet Accelerator                         |  |  |  |

| PCIe     | Peripheral Component Interconnect Express  |  |  |  |

| PDSP     | Packet Data Structure Processor            |  |  |  |

| PLL      | Phase Locked Loop                          |  |  |  |

| PKTDMA   | Packet DMA                                 |  |  |  |

| QM, QMSS | Queue Manager, Queue Manager Sub-System    |  |  |  |

| RAC      | Receive Accelerator Coprocessor            |  |  |  |

| RSA      | Rake Search Accelerator                    |  |  |  |

| SA       | Security Accelerator                       |  |  |  |

| SDMA     | Slave Direct Memory Access                 |  |  |  |

| SDRAM    | Synchronous Dynamic Random Access Memory   |  |  |  |

| SGMII    | Serial Gigabit Media Independent Interface |  |  |  |

| SPI      | Serial Peripheral Interface                |  |  |  |

| SRIO     | Serial Rapid Input Output                  |  |  |  |

| TAC      | Transmit Accelerator Coprocessor           |  |  |  |

| TCP3d    | Turbo Decode Coprocessor                   |  |  |  |

| TCP3e    | Turbo Encode Coprocessor                   |  |  |  |

| TPDMA    | Third Party DMA Engine                     |  |  |  |

| TPCC     | TPDMA Channel Controller                   |  |  |  |

| ТРТС     | TPDMA Transfer Controller                  |  |  |  |

| UART     | Universal Asynchronous Receive/Transmit    |  |  |  |

| VCP2     | Viterbi Decode Coprocessor                 |  |  |  |

| хмс      | Extended Memory Controller                 |  |  |  |

www.ti.com 1 Introduction

#### 1 Introduction

The purpose of this document is to provide throughput performance data for Keystone Architecture C66x devices. This document provides theoretical and measured throughput performance for Keystone memories and peripherals. The peripherals presented in this document are shown in the table below. Please note that not all peripherals are supported by all devices. Please refer to the table or the device-specific data manual to determine which peripherals are supported for a particular device.

In addition to throughput performance data, this document also provides an overview of the TeraNet switch fabric implemented on Keystone C66x devices. Lastly, this document provides a basis for estimating memory access performance and presents theoretical and measured performance data achieved under various operating conditions. Some factors affecting memory access performance also are detailed.

Table 1 Peripherals Supported by Part Number

|                                                          | TMS320 |                                  |  |

|----------------------------------------------------------|--------|----------------------------------|--|

|                                                          | C6670  | C6671<br>C6672<br>C6674<br>C6678 |  |

| "DDR3 Throughput" on page 11                             | x      | Х                                |  |

| "EDMA3 Complex Throughput" on page 14                    | х      | Х                                |  |

| "BCP Throughput" on page 18                              | х      |                                  |  |

| "FFTC Throughput" on page 19                             | х      |                                  |  |

| "Gigabit Ethernet Switch Subsystem" on page 22           | х      | Х                                |  |

| "Inter-integrated Circuit (I <sup>2</sup> C)" on page 24 | x      | x                                |  |

| "Multicore Navigator Throughput" on page 27              | x      | x                                |  |

| "Packet Accelerator (PA)" on page 35                     | х      | Х                                |  |

| "PCle" on page 36                                        | x      | Х                                |  |

| "RAC Throughput" on page 40                              | x      |                                  |  |

| "SPI" on page 41                                         | x      | x                                |  |

| "SRIO Throughput" on page 41                             | х      | Х                                |  |

| "TAC Throughput" on page 51                              | х      |                                  |  |

| "TCP3d Throughput" on page 52                            | х      |                                  |  |

| "TCP3e Throughput" on page 53                            | х      |                                  |  |

| "UART" on page 57                                        | х      | Х                                |  |

| "VCP2 Throughput" on page 58                             | х      |                                  |  |

| End of Table 1                                           |        |                                  |  |

# 2 KeyStone Device Overview

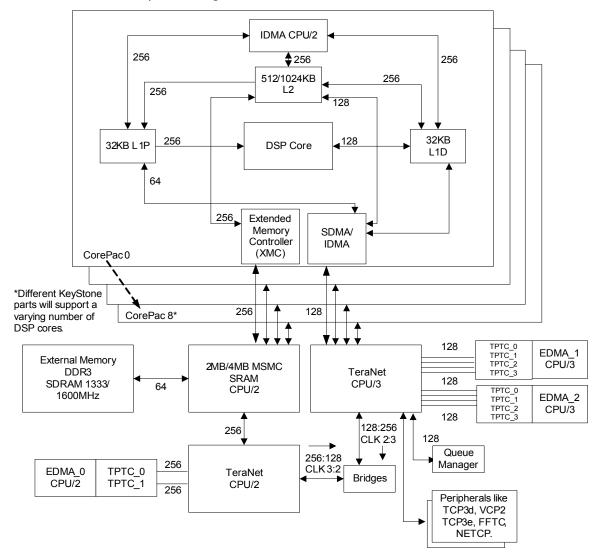

This section focuses on the TeraNet switch fabric that provides the interconnect between C66x DSP cores, peripherals, and memories. The high-level details provided in this section are required to understand the throughput performance of the C66x DSP, because the bus widths and the operating frequencies of each part of the TeraNet directly impact the throughput performance of the connected peripherals or memories. The C66x DSP architecture is shown in Figure 1 and shows the basic connectivity of the CorePac with the TeraNet and the various EDMA transfer controllers.

Figure 1 TeraNet and Memory Access Diagram

#### 2.1 C66x CorePac Overview

This section provides the fundamental details of the C66x CorePac. Additional details about the C66x CorePac can be found in the C66x CorePac User Guide. The C66x CorePac consists of several components including:

- C66x DSP core

- L1 and L2 memories

- external memory controller

- extended memory controller (XMC)

- interrupt controller

- power/sleep controller

- embedded trace buffer

- data trace formatter

- RSA accelerator (core 1 and 2 only)

Each CorePac has the ability to sustain up to 128 bits of load/store operations per cycle to L1D memory and is capable of handling up to 16 GB/second. When accessing data in the L2 memory or external memory, the access rate depends on the memory access pattern and the cache.

Within each CorePac, there is an internal DMA (IDMA) engine that can move data at the frequency rate of DSP/2 with a data width of 256 bits. The IDMA operates in the background of the DSP core activity (i.e., data can be brought into buffer A while the DSP core is accessing buffer B). The IDMA can transfer data only between the L1 and L2 memories and peripheral configuration ports; it cannot access external memory.

#### 2.2 TeraNet Overview

The TeraNet switch fabric provides interconnection between the C66x cores (and their local memories), external memory, the enhanced DMA v3 (EDMA3) controllers, Multicore Navigator, on-chip coprocessors, and high-speed IO. The TeraNet switch fabric allows each of these to operate at maximum efficiency with no blocking or stalling. It allows for concurrent transfers between non-conflicting master/slave pairs and can support a very high total data rate across any endpoint. If transfers line up such that the source or destination memory is the same, then collisions occur and certain transactions will be blocked.

The TeraNet consists of data switch fabric and configuration switch fabric:

- **Data Switch Fabric:** The data switch fabric mainly moves data across the system and is further subdivided into two smaller switch fabrics. One connects high speed masters to slaves via 256-bit data buses running at the DSP/2 frequency. The second data switch fabric connects high-speed masters to slaves via 128-bit data buses running at a DSP/3 frequency.

- Configuration Switch Fabric: This switch fabric is mainly used to access peripheral registers. It connects the C66x CorePac and masters on the data switch fabric to slaves via 32-bit configuration buses running at either DSP/3 or DSP/6 frequency.

C66x devices contain three EDMA Channel Controllers: TPCC0, TPCC1, and, TPCC2. Each TPCC can be programmed to move data concurrently in the background without the expense of any DSP cycles. These TPCCs can move data between on-chip L1 and L2 memory, MSMC SRAM, external memory, and the peripherals on the device that support EDMA-based transfer.

The TeraNet also provides connection to the Multicore Navigator which uses a Queue Manager Subsystem (QMSS) and a Packet DMA (PKTDMA) to control and implement high-speed data packet movement within the device. Frequent tasks are commonly offloaded from the host processor to peripheral hardware to increase system performance.

The TeraNet also provides a 64-bit DDR3 interface to support access to external memories that can be used for either data or program memory.

## 2.3 Memory Access System Overview

This section discusses the C66x memory system. Memory access is critical for applications running on the DSP. Some memories are internal to the CorePac, while other system memories are external to the CorePac. The memory system also provides a 64-bit DDR3 interface for accessing off-chip memory. Internal to each CorePac are the following memories:

- L1D SRAM that can be used as either data memory or data cache or both.

- L1P SRAM that can be used as either program memory or cache or both.

- Local L2 SRAM that can be used as either unified SRAM or unified cache or both.

L1D SRAM, L1P SRAM, L2 SRAM, MSMC SRAM, and DDR3 memories are accessible by all the cores and multiple DMA masters on the device.

External to the CorePac, the C66x DSPs have multicore shared memory (MSMC) SRAM, which is shared between the cores. The MSMC memory can be configured in two ways:

- **SL2 mode**: Shared L2 SRAM mode: L1P/L1D memory will cache MSMC, whereas L2 will not cache requests to MSMC SRAM.

- SL3 mode: Level 3 SRAM mode: Both L1P/L1D and L2 memories will cache the MSMC SRAM if it is remapped to an external address using the address extension unit. (For more information on this, see the Multicore Shared Memory Controller (MSMC) for KeyStone Devices User Guide.

A 64-bit EMIF interface is provided for accessing off-chip DDR3 SDRAM, which can be used as data or program memory. Although this interface supports a 64-bit data bus, it can also be configured to operate using a 32-bit or 16-bit data bus.

# **3 Memory Access Throughput Performance**

This section discusses the memory access throughput performance of C66x devices. The bandwidth of a memory copy is determined by the lowest of these three factors:

- Bus bandwidth

- Source throughput

- Destination throughput

Table 2 summarizes the maximum theoretical bandwidth of the C66x core, IDMA, and the EDMA when the device is operating at 1 GHz.

Table 2 Theoretical Bandwidth of Core, IDMA and EDMA

| Master           | Maximum Bandwidth MB/s | Comments                                  |

|------------------|------------------------|-------------------------------------------|

| C66x Core        | 16000                  | (128bits)/(8bit/byte)*(1000M)=16000MB/s   |

| IDMA             | 16000                  | (256bits)/(8bit/byte)*(1000M/2)=16000MB/s |

| EDMA0(Single TC) | 16000                  | (256bits)/(8bit/byte)*(1000M/2)=16000MB/s |

| EDMA1(Single TC) | 5333                   | (128bits)/(8bit/byte)*(1000M/3)=5333MB/s  |

| EDMA2(Single TC) | 5333                   | (128bits)/(8bit/byte)*(1000M/3)=5333MB/s  |

Table 3 summarizes the maximum theoretical throughput of different memories when the C66x device is operating at 1 GHz. The DDR3 performance assumes that a 64-bit bus width is used and that the external memory is operating at 1333 MHz.

Table 3 Theoretical Bandwidth of Different Memories

| Master    | Maximum Bandwidth MB/s | Comments                                    |  |  |

|-----------|------------------------|---------------------------------------------|--|--|

| L1D 32000 |                        | (256bits)/(8bit/byte)*(1000M)=32000MB/s     |  |  |

| L1P 32000 |                        | (256bits)/(8bit/byte)*(1000M)=32000MB/s     |  |  |

| L2        | 16000                  | (256bits)/(8bit/byte)*(1000M/2)=16000MB/s   |  |  |

| MSMC RAM  | 64000                  | 4*(256bits)/(8bit/byte)*(1000M/2)=64000MB/s |  |  |

| DDR3 RAM  | 10664                  | (64bits)/(8bit/byte)*(666.5M)*2=10664MB/s   |  |  |

When the C66x core tries to read from or write to different memory endpoints, it consumes some DSP cycles to access the memory region depending on various factors such as prefetching, caching, victim buffer hits, and so on. Section 3.1 and Section 3.2 estimate the number of DSP stalls for accessing different memory endpoints.

Note that MSMC SRAM has 4 memory banks of 256 bits. As mentioned previously, MSMC can be configured in either shared L2 (SL2) mode or shared L3 (SL3) mode.

## 3.1 Memory Read Performance

The C66x core has an improved pipeline between L1D/L1P and L2 memory controller and this significantly reduces the stall cycles for L1D/L1P cache misses.

Table 4 shows the DSP stalls for accessing different memories when the core tries to read from memory.

Table 4 Memory Read Performance

|                |          |          |          | DSP Stalls (in Cycles) |        |           |        |

|----------------|----------|----------|----------|------------------------|--------|-----------|--------|

|                |          |          |          | Single                 | Read   | Burst     | Read   |

| Source         | L1 Cache | L2 Cache | Prefetch | No Victim              | Victim | No Victim | Victim |

| ALL            | Hit      | NA       | NA       | 0                      | NA     | 0         | NA     |

| Local L2 SRAM  | Miss     | NA       | NA       | 7                      | 7      | 3.5       | 10     |

| MSMC RAM (SL2) | Miss     | NA       | Hit      | 7.5                    | 7.5    | 7.4       | 11     |

| MSMC RAM (SL2) | Miss     | NA       | Miss     | 19.8                   | 20.1   | 9.5       | 11.6   |

| MSMC RAM (SL3) | Miss     | Hit      | NA       | 9                      | 9      | 4.5       | 4.5    |

| MSMC RAM (SL3) | Miss     | Miss     | Hit      | 10.6                   | 15.6   | 9.7       | 129.6  |

| MSMC RAM (SL3) | Miss     | Miss     | Miss     | 22                     | 28.1   | 11        | 129.7  |

| DDR RAM (SL2)  | Miss     | NA       | Hit      | 9                      | 9      | 23.2      | 59.8   |

| DDR RAM (SL2)  | Miss     | NA       | Miss     | 84                     | 113.6  | 41.5      | 113    |

| DDR RAM (SL3)  | Miss     | Hit      | NA       | 9                      | 9      | 4.5       | 4.5    |

| DDR RAM (SL3)  | Miss     | Miss     | Hit      | 12.3                   | 59.8   | 30.7      | 287    |

| DDR RAM (SL3)  | Miss     | Miss     | Miss     | 89                     | 123.8  | 43.2      | 183    |

| End of Table 4 |          | •        |          |                        |        |           |        |

For example, when there is a L1 cache miss, it takes seven DSP cycles for the core to access its local L2 SRAM. Similarly, where there is a L1 cache miss and when the MSMC is configured as SL2/SL3, the DSP stalls depend on whether there is a Hit/Miss in the prefetch buffer. Prefetching reduces the latency gap between local memory and shared (internal/external) memories. Prefetching in the extended memory controller (XMC) helps reduce stall cycles for read accesses to the MSMC and the DDR3 EMIF.

The performance is affected when both L1 and L2 caches contain victims. So, when the MSMC or DDR3 is configured as SL3 memory, it can have a potential double victim performance impact where the victim cache lines have to be evicted from both L1 and L2 caches. When victims are in the cache, burst reads are slower than single reads because reads have to wait for victim write-backs to complete.

The numbers show that MSMC access is slower when it is configured as SL3 instead of SL2. There is a potential double victim involved. This holds true for DDR3 as well.

If DDR3 does not have large cacheable data, it is recommended that it be configured as SL2.

## 3.2 Memory Write Performance

The C66x CorePac has improved write merging and optimized burst sizes that reduce the stalls to external memory.

The L1D memory controller merges writes, not only to L2 SRAM, but to any address that is allowed to be cached (MAR.PC==1).

Table 5 shows the DSP stalls for accessing different memories when the core tries to write to memory. There are no stalls when the DSP does a single write operation.

Table 5 Memory Write Performance

|                |                |          |          | DSP Stalls (in Cycles) |        |           |        |

|----------------|----------------|----------|----------|------------------------|--------|-----------|--------|

|                |                |          |          | Single                 | Write  | Burst     | Write  |

| Source         | L1 Cache       | L2 Cache | Prefetch | No Victim              | Victim | No Victim | Victim |

| ALL            | Hit            | NA       | NA       | 0                      | NA     | 0         | NA     |

| Local L2 SRAM  | Miss           | NA       | NA       | 0                      | 0      | 1         | 1      |

| MSMC RAM (SL2) | Miss           | NA       | Hit      | 0                      | 0      | 2         | 2      |

| MSMC RAM (SL2) | Miss           | NA       | Miss     | 0                      | 0      | 2         | 2      |

| MSMC RAM (SL3) | Miss           | Hit      | NA       | 0                      | 0      | 3         | 3      |

| MSMC RAM (SL3) | Miss           | Miss     | Hit      | 0                      | 0      | 6.7       | 14.6   |

| MSMC RAM (SL3) | Miss           | Miss     | Miss     | 0                      | 0      | 6.7       | 16.7   |

| DDR RAM (SL2)  | Miss           | NA       | Hit      | 0                      | 0      | 4.7       | 4.7    |

| DDR RAM (SL2)  | Miss           | NA       | Miss     | 0                      | 0      | 5         | 5      |

| DDR RAM (SL3)  | Miss           | Hit      | NA       | 0                      | 0      | 3         | 3      |

| DDR RAM (SL3)  | Miss           | Miss     | Hit      | 0                      | 0      | 16        | 114.3  |

| DDR RAM (SL3)  | Miss           | Miss     | Miss     | 0                      | 0      | 18.2      | 115.5  |

| End of Table 5 | End of Table 5 |          |          |                        |        |           |        |

www.ti.com 4 DDR3 Throughput

## 4 DDR3 Throughput

Applies to

All KeyStone Devices

The DDR3 module in the C66x DSP is accessible across all cores and other system masters. The DDR3 controller interfaces with most standard DDR3 SDRAM devices. There are two clock domains in the controller. The Command FIFO, Read FIFO and Write FIFO are all on the DSP/2 clock domain. The Memory Mapped Registers (MMR), state machine, and interface to the DDR PHY are all driven by the DDR3 memory clock. The DDR3 controller is interfaced to the MSMC controller and any access made via any of the EDMAs are handled by MSMC which serves as the common management path.

## 4.1 DDR3 Command Interleaving Latency

The DDR3 controller supports interleaving of commands for maximum efficiency, i.e., the controller will partially execute one command and switch to executing another high priority command before finishing the first command. The READ latencies from DDR3 to L2 and WRITE latencies from L2 to DDR3 are independently run and tested.

The test case details are as follows:

- Testing is done on a 1 GHz TMS320C6670 DSP with DDR3 frequency at 1600 MHz.

- The EDMA configuration used across the tests is an array of contiguous sequences of memory of size 1K bytes.

- Test runs from CorePac0 with L2 memory as one endpoint and DDR3 as the other.

- Data page size is 1KB for different DDR3 modes of operation.

- 2 buffers are set up and populated in DDR3 such that they lie in the same page.

- 2 buffers are set up and populated in DDR3 such that they lie in a different page but in the same bank.

The test process includes the following steps:

- 1. Wait for the completion of the refresh interval for about 1 ms in a tight loop.

- 2. Configure two channels (four for 64-bit) on different TCs such that they perform READ/WRITE transaction from the allocated buffers.

- 3. Trigger channels simultaneously and wait for the completion of both.

- 4. Aggregate throughput for the transfers is measured.

Table 6 shows the latencies for DDR3 in different modes for a READ command interleave.

Table 6 DDR3 READ Command Interleave Cycle Counts

|                          | Same Page EDMA0<br>(TC0 and TC1) | Different Page EDMA0<br>(TC0 and TC1) | Same Page EDMA1<br>(TC2 and TC3) | Different Page EDMA1<br>(TC2 and TC3) |

|--------------------------|----------------------------------|---------------------------------------|----------------------------------|---------------------------------------|

| CPU Cycle Count (64 bit) | 1170                             | 1172                                  | 1114                             | 1173                                  |

| CPU Cycle Count (32 bit) | 920                              | 1001                                  | 774                              | 768                                   |

| CPU Cycle Count (16 bit) | 1424                             | 1505                                  | 981                              | 1043                                  |

4 DDR3 Throughput www.ti.com

Table 7 shows the latencies for DDR3 in different modes for interleaved WRITE command.

Table 7 DDR3 WRITE Command Interleave Cycle Counts

|                          | Same Page EDMA0<br>(TC0 and TC1) | Different Page EDMA0<br>(TC0 and TC1) | Same Page EDMA1<br>(TC2 and TC3) | Different Page EDMA1<br>(TC2 and TC3) |

|--------------------------|----------------------------------|---------------------------------------|----------------------------------|---------------------------------------|

| CPU Cycle Count (64 bit) | 1338                             | 1422                                  | 1121                             | 1121                                  |

| CPU Cycle Count (32 bit) | 835                              | 1000                                  | 705                              | 768                                   |

| CPU Cycle Count (16 bit) | 1340                             | 1504                                  | 981                              | 1043                                  |

## 4.2 DDR3 Class Of Service Throughput

The commands in the Command FIFO can be mapped to two classes of service (CoS), namely 1 and 2. The mapping based on priority can be done by setting the appropriate values in the Priority to Class of Service Mapping register. By default, all commands will be mapped to Class of Service 2.

The tests were measured on a TMS320C6670 DSP operating at 1 GHz. The scenario details to test the effect of Class of Service assignment to commands for EDMA based transfers are listed below:

- TMS320C6670 DDR3 frequency at 1600 MHz.

- The EDMA configuration used across the tests is an array of contiguous sequences of memory of size 1K bytes.

- Test runs from CorePac0 with L2 memory as one endpoint and DDR3 as the other.

- Data page size is 1KB for different DDR3 modes of operation.

- Two buffers are set up and populated in DDR3 such that they lie in the same page.

- Wait for the completion of the refresh interval for about 1 ms in a tight loop.

The test process includes the following steps:

- 1. Configure two channels (four for 64-bit) on different TCs such that they perform READ/WRITE transaction from the allocated buffers.

- 2. Trigger channels simultaneously and wait for the completion of TC1.

- 3. TC1 throughput for the transfers is measured.

- 4. The test is run for 3 different CoS settings and the results are compared against each other: Default, TC1 at minimum latency, and TC0 and minimum latency.

Table 8 shows the aggregate throughput for DDR3 in different modes for a READ command priority.

Table 8 DDR3 READ Command Priority Throughput

|                                 | Default CoS Settings | TC0 Maximum Latency<br>TC1 Minimum Latency | TC0 Minimum Latency<br>TC1 Maximum Latency |

|---------------------------------|----------------------|--------------------------------------------|--------------------------------------------|

| TC1 Throughput in Mbps (64 bit) | 2311.5               | 2348.6                                     | 1965.5                                     |

| TC1 Throughput in Mbps (32 bit) | 1943.1               | 2354                                       | 1000                                       |

| TC1 Throughput in Mbps (16 bit) | 1475.5               | 2354                                       | 604.1                                      |

www.ti.com 4 DDR3 Throughput

Table 9 shows the aggregate throughput for DDR3 in different modes for a WRITE command priority.

#### Table 9 DDR3 WRITE Command Priority Throughput

|                                 | Default CoS Settings | TC0 Maximum Latency<br>TC1 Minimum Latency | TC0 Minimum Latency<br>TC1 Maximum Latency |

|---------------------------------|----------------------|--------------------------------------------|--------------------------------------------|

| TC1 Throughput in Mbps (64 bit) | 1946.8               | 1969.2                                     | 1973                                       |

| TC1 Throughput in Mbps (32 bit) | 1950.5               | 1969.2                                     | 1692.6                                     |

| TC1 Throughput in Mbps (16 bit) | 1477.6               | 1692.6                                     | 603.4                                      |

## **5 EDMA3 Complex Throughput**

Applies to All KeyStone Devices

Various complex throughput tests were performed for measuring the EDMA throughput under different conditions. The following tests calculate the EDMA throughput without any background traffic in the CorePac.

The test process includes the following steps:

- 1. Get the transfer time for a payload of 32KB/channel (includes overhead).

- 2. Get the transfer time for 0 bytes this is called a dummy transfer and closely approximates the overhead.

- 3. Subtract 2 from 1 to get the transfer time with overhead removed t3.

- 4. Throughput = [(32KB \* number of channels)/t3] \* 1GHz

The basis of these tests is to set up and trigger parallel read and write data transfers bidirectionally for different combinations of TCs of the EDMA. The channel controller is programmed such that each TC performs one read and one write transfer between the TC endpoints bidirectionally on two different logical channels. Once TCs are triggered, wait (poll) for the completion of all transfers and capture the throughput values.

The EDMA configuration uses A-synchronized transfers across all tests and TC combinations with ACNT = 32KB and BCNT = CCNT = 1 per logical channel.

Note that each of the TCs have bidirectional transfers —from endpoint A to endpoint B and the other from endpoint B to endpoint A on two different logical channels. For example, for the TC0 and TC1 testcase, there are a total of four transfers on four different logical channels.

The test case descriptions are as follows:

- **TC0 and TC1 test case:** Trigger TC0 and TC1 in parallel. After the completion of the TC0 and TC1 transfers in both directions, the steady state throughput is calculated

- TC2 and TC6 test case: Trigger TC2 first and after a delta lag TC6 is triggered. After the completion of TC2 and TC6 transfers in both directions, the steady state throughput is calculated.

- TC3 and TC7 test case: Trigger TC3 first and after a delta lag TC7 is triggered. After the completion of TC3 and TC7 transfers in both directions, the steady state throughput is calculated.

- TC3, TC5, TC7, and TC8 test case: First, TC3 and TC5 are triggered in parallel. After a delta lag, TC7 and TC8 are triggered in parallel. After the completion of all TC transfers in both directions, the steady state throughput is calculated.

Please note that TC0 through TC8 in this document correlate to the Data Manual nomenclature in the following way:

ICS = EDIMAT IC

#### 5.1 Scenario 1: EDMA Transfer Between CorePac0 L2 and CorePac1 L2

As mentioned above, the throughput is limited by the lowest of the bus bandwidth, source throughput, and destination throughput.

The TeraNet allows for concurrent transfers between non-conflicting master/slave pairs and can support a very high total data rate across any endpoint. If transfers line up such that the source or destination memory is the same, then collisions occur and certain transactions will be blocked.

In this scenario, the endpoints used are CorePac0 L2 SRAM and CorePac1 L2 SRAM memory. There is contention among TCs as the same endpoint is used by both TCs for each of the bidirectional transfers. The TCs have to use the same SDMA/IDMA port of the same CorePac and the second transaction will have to wait until the first is complete.

So only one TC transfer is done at a time and the theoretical throughput is equivalent to (128bits)/(8bit/byte)×(1000M/3)=5333MB/s. Note that EDMA0 will access the CorePac0 using the DSP/3 128-bit TeraNet switch fabric similar to EDMA1 and EDMA2.

Table 10 shows the measured aggregate throughput of the TCs for this scenario.

Table 10 EDMA Throughput Between CorePac0 L2 and CorePac1 L2 Endpoints

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 | TC3 and TC7 | TC3, TC5, TC7, and TC8 |

|--------------------------------------------------------|-------------|-------------|-------------|------------------------|

| Wait for completion of                                 | Both        | Both        | Both        | All                    |

| Theoretical Max throughput between TC endpoints (MBPS) | 5333.3      | 5333.3      | 5333.3      | 5333.3                 |

| Aggregate throughput of TCs fired (MBPS)               | 5201.3      | 5276.6      | 5283.5      | 5322.5                 |

The testcase setup details are as follows:

Every TC sets up bidirectional data transfer between the same CorePac0 L2 and CorePac1 L2.

#### 5.2 Scenario 2: EDMA Transfer Between Different CorePac L2 and MSMC SRAM

In this scenario, each TC uses a different CorePac source address and there is no contention between TCs. For example TC0 reads from CorePac0 L2, whereas TC1 reads from CorePac1 L2. So the total throughput for any two TCs would be  $2 \times [(128 \text{bits})/(8 \text{bit/byte}) \times (1000 \text{M/3})] = 10666.66 \text{MB/s}$ .

**Note**—For TC3, TC5, TC7, and TC8 it cannot be  $4 \times [(128 \text{bits})/(8 \text{bit/byte}) \times (1000 \text{M/3})]$  because it is limited by the MSMC maximum throughput, which is 16000MB/s.

Table 11 shows the measured aggregate throughput of the TCs for this scenario.

Table 11 EDMA transfer between different CorePac L2 and MSMC SRAM

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 | TC3 and TC7 | TC3, TC5, TC7, and TC8 |

|--------------------------------------------------------|-------------|-------------|-------------|------------------------|

| Wait for completion of                                 | Both        | Both        | Both        | All                    |

| Theoretical Max throughput between TC endpoints (MBPS) | 10667       | 10667       | 10667       | 16000                  |

| Aggregate throughput of TCs fired (MBPS)               | 10472.4     | 10437.3     | 10553.3     | 15896.2                |

The testcase setup details are as follows:

• TC0 and TC1: TC0 has bidirectional data transferred between CorePac0 L2 and MSMC. TC1 has bidirectional data transferred between CorePac1 L2 and MSMC.

- TC2 and TC6: TC2 has bidirectional data transferred between CorePac0 L2 and MSMC. TC6 has bidirectional data transferred between CorePac1 L2 and MSMC.

- TC3 and TC7: TC3 has bidirectional data transferred between CorePac0 L2 and MSMC. TC7 has bidirectional data transferred between CorePac1 L2 and MSMC.

- TC3, TC5, TC7, and TC8: Each TC uses a different CorePac to transfer bidirectional data between MSMC and CorePac For example, TC3 uses CorePac0, TC5 uses CorePac1, TC7 uses CorePac2, and TC8 uses CorePac3.

#### 5.3 Scenario 3: EDMA Transfer From MSMC SRAM to MSMC SRAM

In this scenario there is contention between TCs because the source/destination are the same for different TCs, so there is only one transfer happening at a time. Even though the theoretical throughput for MSMC is  $(256bits)/(8bit/byte)\times(1000M/2)=16000MB/s$ , it cannot do both reads and writes at the same time. It has to wait for the previous read from MSMC to complete and then do the write operation to the MSMC. Therefore, the throughput will be effectively halved and is 16000/2 = 8000MB/s.

Table 12 shows the measured aggregate throughput of the TCs for this scenario.

Table 12 EDMA Throughput Between MSMC SRAM and MSMC SRAM

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 | TC3 and TC7 | TC3, TC5, TC7, and TC8 |

|--------------------------------------------------------|-------------|-------------|-------------|------------------------|

| Wait for completion of                                 | Both        | Both        | Both        | All                    |

| Theoretical Max throughput between TC endpoints (MBPS) | 8000        | 8000        | 8000        | 8000                   |

| Aggregate throughput of TCs fired (MBPS)               | 7961.6      | 7882.1      | 7981.5      | 7981.5                 |

The testcase setup details are as follows:

Every TC sets up bidirectional data transfer between MSMC and MSMC SRAM.

#### 5.4 Scenario 4: EDMA Transfer From MSMC SRAM to DDR3

There is no contention between TCs, but the throughput is limited by the maximum DDR3 bandwidth, which is  $(64bits)/(8bit/byte) \times (666.5M) \times 2 = 10664MB/s$ . Table 13 shows the measured aggregate throughput of the TCs for this scenario.

Table 13 EDMA Throughput Between MSMC SRAM and DDR3

| Transaction on TCs                                     | TC0 and TC1 | TC2 andTC6 | TC3 and TC7 | TC3, TC5, TC7, and TC8 |

|--------------------------------------------------------|-------------|------------|-------------|------------------------|

| Wait for completion of                                 | Both        | Both       | Both        | All                    |

| Theoretical Max throughput between TC endpoints (MBPS) | 10664       | 10664      | 10664       | 10664                  |

| Aggregate throughput of TCs fired (MBPS)               | 10132.3     | 10104.2    | 10193.8     | 10152.7                |

The testcase setup details are as follows:

Every TC sets up bidirectional data transfer between the MSMC and DDR3 SRAM.

#### 5.5 Scenario 5: EDMA Transfer From DDR3 to DDR3

There is no contention between TCs, but because the DDR3 EMIF cannot do a read from DDR3 and a write to DDR3 in parallel, the EDMA needs to wait until the previous operation is completed. The DDR3 throughput of 10664MB/s will be halved and will be equivalent to 5332 MB/s. The reason for the low throughput in this case is due to read-write turnaround and page switch overheads. Table 14 shows the measured aggregate throughput of the TCs for this scenario.

Table 14 EDMA Throughput Between DDR3 and DDR3

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 | TC3 and TC7 | TC3, TC5, TC7, and TC8 |

|--------------------------------------------------------|-------------|-------------|-------------|------------------------|

| Wait for completion of                                 | Both        | Both        | Both        | All                    |

| Theoretical Max throughput between TC endpoints (MBPS) | 5332        | 5332        | 5332        | 5332                   |

| Aggregate throughput of TCs fired (MBPS)               | 3960.5      | 4138.5      | 3472.7      | 4351.9                 |

The testcase setup details are as follows:

Every TC sets up bidirectional data transfer between DDR3 and DDR3 SRAM.

#### 5.6 Scenario 6: EDMA Transfer From Different CorePac L2 to DDR3

In this scenario, each TC uses a different CorePac source address and there is no contention between TCs. However, the throughput is limited by the DDR3 maximum throughput, which is 10664MB/s. Table 15 shows the measured aggregate throughput of the TCs for this scenario.

Table 15 EDMA Throughput Between Different CorePac L2s to DDR3

| Transaction on TCs                                     | TC0 and TC1 | TC2 and TC6 | TC3 and TC7 | TC3, TC5, TC7, and TC8 |

|--------------------------------------------------------|-------------|-------------|-------------|------------------------|

| Wait for completion of                                 | Both        | Both        | Both        | All                    |

| Theoretical Max throughput between TC endpoints (MBPS) | 10664       | 10664       | 10664       | 10664                  |

| Aggregate throughput of TCs fired (MBPS)               | 10132.3     | 10158.3     | 10222.4     | 10158.3                |

The testcase setup details are as follows:

- TC0 and TC1: TC0 has bidirectional data transferred between CorePac0 L2 and DDR3. TC1 has bidirectional data transferred between CorePac1 L2 and DDR3.

- TC2 and TC6: TC2 has bidirectional data transferred between CorePac0 L2 and DDR3. TC6 has bidirectional data transferred between CorePac1 L2 and DDR3.

- TC3 and TC7: TC3 has bidirectional data transferred between CorePac0 L2 and DDR3. TC7 has bidirectional data transferred between CorePac1 L2 and DDR3.

- TC3, TC5, TC7, and TC8: Each TC uses a different CorePac to transfer bidirectional data between DDR3 and CorePac. i.e., TC3 uses CorePac0, TC5 uses CorePac1, TC7 uses CorePac2, and TC8 uses CorePac3.

6 BCP Throughput www.ti.com

## **6 BCP Throughput**

#### Applies to

C6670

The Bit Rate Coprocessor (BCP) is a programmable peripheral for baseband bit processing. It supports FDD LTE, TDD LTE, WCDMA, TD-SCDMA, HSPA, HSPA+, WiMAX 802.16e, and monitoring/planning for LTE-A. The BCP accelerates the Layer1 Downlink processing from transport blocks down to OFDM symbols (LTE, WiMAX) or physical channel data (WCDMA, TD-SCDMA, HSPA/+). It also accelerates Layer1 uplink processing from OFDM symbols to transport blocks for LTE/WiMAX (with the help of Turbo and Convolutional Decoder Accelerators) or the physical channel data to the output of rate dematching or LLR combining for WCDMA, TD-SCDMA, or HSPA/+.

The BCP has three VBUSM master ports for data movement. One is a 128-bit Navigator interface and there are two 128-bit direct I/O interfaces. The BCP runs at DSP/3 clock frequency.

The testcase details for measuring the throughput are as follows:

- Testing is done on a 1GHz TMS320C6670 DSP with DDR3, MSMC SRAM and L2 SRAM as memory endpoints for both input and output data.

- Downlink and Uplink throughput tests are run independently of each other.

- All the packets are enqueued by setting up the descriptors (Host descriptors used for the tests). After enqueing, the logical transmit channel is enabled to initiate transfer.

- Steady-state throughput measurement is performed to remove software overhead by enqueuing 20 input blocks at a time. Once the transmit channel is enabled, the average time taken to process an input block is calculated by averaging the total time taken to process the 20 input blocks.

- Throughput is calculated by dividing the average block processing time by the input blocks size.

BCP LTE Uplink Throughput

Table 16 through Table 17 show the BCP LTE (PUSCH and PDSCH) and WCDMA (HSUPA and HSDPA) throughputs for minimum and maximum transport block sizes, different modulation schemes, and different memory endpoints.

Table 16 BCP LTE Throughput (Part 1 of 2)

| Channel | PKTDMA Memory | HARQ Memory | TB Size | Modulation<br>Scheme | Throughput<br>(Mbps) |

|---------|---------------|-------------|---------|----------------------|----------------------|

|         | L2 SRAM       | MSMC        | 136     | QPSK                 | 241                  |

|         | L2 SRAM       | DDR3        | 136     | QPSK                 | 241                  |

| PUSCH   | DDR3          | DDR3        | 136     | QPSK                 | 231                  |

|         | L2 SRAM       | MSMC        | 75376   | 64-QAM               | 846                  |

|         | L2 SRAM       | DDR3        | 75376   | 64-QAM               | 498                  |

|         | DDR3          | DDR3        | 75376   | 64-QAM               | 455                  |

www.ti.com 7 FFTC Throughput

Table 16 BCP LTE Throughput (Part 2 of 2)

| Channel         | PKTDMA Memory | HARQ Memory | TB Size | Modulation<br>Scheme | Throughput<br>(Mbps) |

|-----------------|---------------|-------------|---------|----------------------|----------------------|

|                 | L2 SRAM       | N/A         | 136     | QPSK                 | 278                  |

|                 | MSMC          | N/A         | 136     | QPSK                 | 276                  |

| PDSCH           | DDR3          | N/A         | 136     | QPSK                 | 288                  |

|                 | L2 SRAM       | N/A         | 440     | 64-QAM               | 1272                 |

|                 | MSMC          | N/A         | 503     | 64-QAM               | 1272                 |

|                 | DDR3          | N/A         | 500     | 64-QAM               | 1272                 |

| End of Table 16 |               |             |         |                      |                      |

Table 17 BCP WCDMA Throughput

| AM DE | DR3 DR3 DR3 DR3 DR3 DR3 DR3 | 18<br>18<br>18<br>22996<br>22996<br>22996 | BPSK BPSK BPSK 4-PAM 4-PAM 4-PAM | 21<br>21<br>21<br>332<br>332<br>332 |

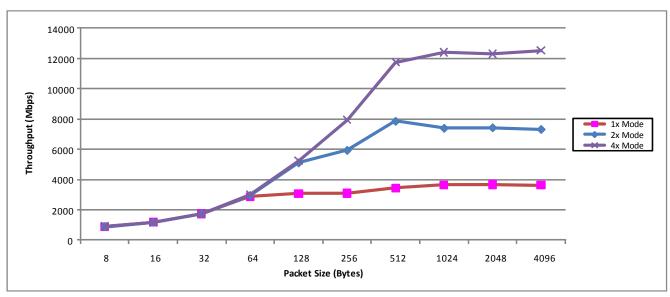

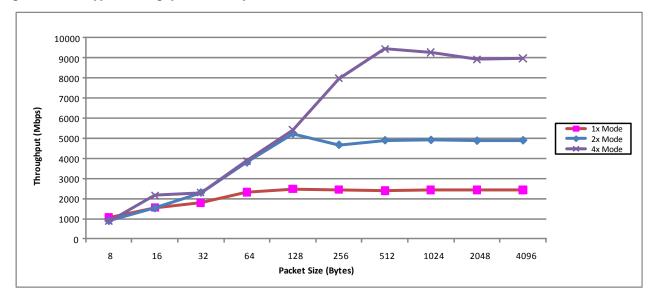

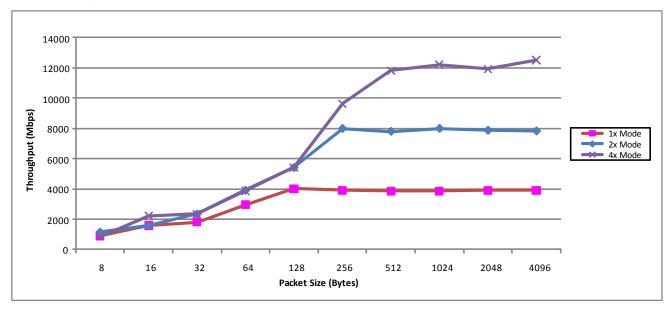

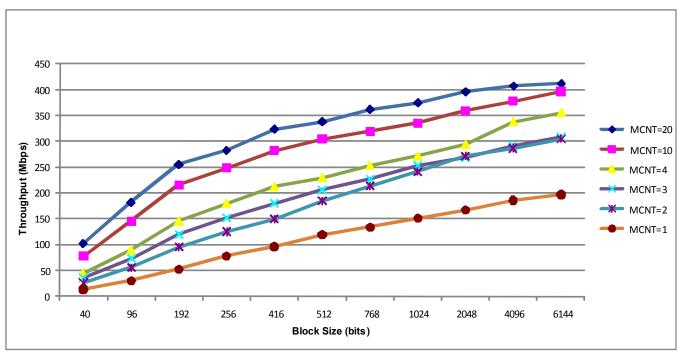

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-------------------------------------------|----------------------------------|-------------------------------------|