## **BQ25756 Schematic Checklist**

|                                   |                     |                   |            |       |                |      | INPUT POWER- DESIGN CHECKLIST                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|---------------------|-------------------|------------|-------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NAME                          |                     | REQUIREMENTS      | Component  | MIN   | TYP            | MAX  | DESCRIPTION                                                                                                                                                                                                                                             | COMMENTS AND RELEVANT EQUATIONS                                                                                                                                                                                                                                                                                   |

| ACP-ACN, ILIM_HIZ                 | 30,29,10            | Optional          | R2(RAC)    | 0mΩ   |                | 5mΩ  | Differential input current sensing and current limit se<br>Input current sensing resistor. This is used for both input<br>current limit regulation and for inductor current sensing of the<br>average current mode control architecture of the charger. | R2(RAC) is not required if input current limit functionality is not needed. Short ACP and ACN to VAC if R2(RAC) is not being used. Refer to section 8.2.2.7 Sense Resistor (RAC_SNS and RBAT_SNS) and Current Programming for choosing the correct resistor value if input current limit functionality is needed. |

|                                   |                     | Optional          | R5,R6      |       | 10Ω            |      | Input current sense switching noise and common mode                                                                                                                                                                                                     | Can be removed if R2(RAC) is not going to be used.                                                                                                                                                                                                                                                                |

|                                   |                     |                   | C10,C11    |       | 100nF          |      | and noise filtering                                                                                                                                                                                                                                     | Can be removed if R2(RAC) is not going to be used.                                                                                                                                                                                                                                                                |

|                                   |                     | Optional Optional | C34<br>R66 | 0kΩ   | 470nF<br>2.5kΩ | 50kΩ | Differential mode noise filtering  Resistor to PGND                                                                                                                                                                                                     | Can be removed if R2(RAC) is not going to be used.  Refer to section 7.3.5.1.1.1 ILIM_HIZ Pin of the datasheet for choosing the correct resistor values.                                                                                                                                                          |

|                                   |                     |                   |            |       |                |      | Internal LDO output                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                   |

| REGN                              | 24                  | Required          | C22        | 4.7μF | 4.7μF          |      | Internal LDO output stabilizing capacitor                                                                                                                                                                                                               | Placed close to the IC REGN pin.                                                                                                                                                                                                                                                                                  |

| HIDRV1                            | 27                  | Required          | Q1         |       |                |      | Converter (Forward Buck Mode) High-Side N-Channel MOSFE<br>Converter (forward buck mode) active High-Side N-Channel<br>MOSFET                                                                                                                           | This is also the reverse boost mode synchronous High-Side MOSFET.                                                                                                                                                                                                                                                 |

|                                   | 21                  | Recommended       | RHIDRV1    | 0Ω    |                |      | Q1 High-Side MOSFET gate drive strength limiting resistor                                                                                                                                                                                               | For non-ideal layouts with EMI contraints, add an experimentally derived resistance to slow down the Q1 turn-on and turn-off. Don't add a gate to source pull down resistor to Q1.                                                                                                                                |

|                                   |                     |                   |            |       |                |      | Converter (Forward Buck Mode) Low-Side N-Channel MOSFE                                                                                                                                                                                                  | T gate driver                                                                                                                                                                                                                                                                                                     |

| LODRV1                            | 25                  | Required          | Q2         |       |                |      | Converter (forward buck mode) active Low-Side N-Channel MOSFET                                                                                                                                                                                          | This is also the reverse boost mode synchronous Low-Side MOSFET.                                                                                                                                                                                                                                                  |

|                                   |                     | Recommended       | RLORV1     | 0Ω    |                |      | Q2 Low-Side MOSFET gate drive strength limiting resistor                                                                                                                                                                                                | For non-ideal layouts with EMI contraints, add an experimentally derived resistance to slow down the Q2 turn-on and turn-off.                                                                                                                                                                                     |

|                                   |                     |                   |            |       |                |      | Buck-boost switching nodes and High-Side MOSFET bootstr                                                                                                                                                                                                 | ap network                                                                                                                                                                                                                                                                                                        |

|                                   | 28-18,<br>26,20, 23 | Required          | L1         | 2.2μΗ | 10μΗ           | 15μΗ | Converter inductor                                                                                                                                                                                                                                      | SW1 and SW2 should be connected to minimize the inductive path from the IC pin to the Inductor                                                                                                                                                                                                                    |

|                                   |                     | Required          | D2,D3      |       | -              |      | BTST1/BTST2 Diode-OR                                                                                                                                                                                                                                    | BTST diodes should use a Schottky diode to minimize reverse recovery loss                                                                                                                                                                                                                                         |

|                                   |                     | Required          | C26        |       | 4.7μF          |      | Connected between DRV-SUP and PGND                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                   |

| SW1-SW2, BTST1,<br>BTST2, DRV-SUP |                     | Required          | C12        |       | 100nF          |      | Converter bootstrap capacitor for Q1 High-Side N Channel MOSFET gate driver                                                                                                                                                                             | Capacitor needs to be placed close to the IC.                                                                                                                                                                                                                                                                     |

| B1312, DRV-30F                    |                     | Recommended       | R13        |       | Ω0             |      | Bootstrap capacitor discharge current limiting resistor                                                                                                                                                                                                 | For non-ideal layouts with EMI contraints, add an experimentally derived resistance to slow down the Q1 turn-on.                                                                                                                                                                                                  |

|                                   |                     | Required          | C18        |       | 100nF          |      | Converter bootstrap capacitor for Q4 High-Side N Channel<br>MOSFET gate driver                                                                                                                                                                          | Capacitor needs to be placed close to the IC.                                                                                                                                                                                                                                                                     |

|                                   |                     | Recommended       | R23        |       | 0Ω             |      | Bootstrap capacitor discharge current limiting resistor F                                                                                                                                                                                               | For non-ideal layouts with EMI contraints, add an experimentally derived resistance to slow down the Q4 turn-on.                                                                                                                                                                                                  |

|                                   |                     |                   |            |       |                |      | Converter (Forward Boost Mode) High-Side N-Channel MOSF                                                                                                                                                                                                 | T gate driver                                                                                                                                                                                                                                                                                                     |

| HIDRV2                            | 19                  | Required          | Q3         |       |                |      | Converter (forward boost mode) active High-Side N-Channel MOSFET                                                                                                                                                                                        | This is also the reverse buck mode synchronous High-Side MOSFET.                                                                                                                                                                                                                                                  |

| HIDKV2                            |                     | Recommended       | RHIDRV2    | 0Ω    |                |      | Q3 High-Side MOSFEt gate drive strength limiting resistor                                                                                                                                                                                               | For non-ideal layouts with EMI contraints, add an experimentally derived resistance to slow down the Q3 turn-on and turn-off. Don't add a gate to source pull down resistor to Q3.                                                                                                                                |

| LODRV2                            | 25                  |                   |            |       |                |      | Converter (Forward Boost Mode) Low-Side N-Channel MOSFE                                                                                                                                                                                                 | T gate driver                                                                                                                                                                                                                                                                                                     |

|                                   |                     | Required          | Q4         |       |                |      | Converter (forward boost mode) active Low-Side N-Channel MOSFET                                                                                                                                                                                         | This is also the reverse buck mode synchronous Low-Side MOSFET.                                                                                                                                                                                                                                                   |

|                                   |                     | Recommended       | RLORV2     | 0Ω    |                |      | Q4 Low-Side MOSFET gate drive strength limiting resistor                                                                                                                                                                                                | For non-ideal layouts with EMI contraints, add an experimentally derived resistance to slow down the Q4 turn-on and turn-off.                                                                                                                                                                                     |

|                                   |                     |                   |            |       |                |      | Converter (Forward Boost Mode) Low-Side N-Channel MOSF                                                                                                                                                                                                  | T gate driver                                                                                                                                                                                                                                                                                                     |

| ACUV, ACOV                        | 34, 35              | Optional          | R21        |       | *Ω             |      | Resistor divider from VAC to PGND to program the                                                                                                                                                                                                        | Refer to section 8.2.2.1 ACUV/ACOV Input Voltage Operating Window                                                                                                                                                                                                                                                 |

| .==.,==.                          |                     | Optional          | R27        |       | *Ω             |      | undervoltage and overvoltage protection.                                                                                                                                                                                                                | <b>Programming</b> of the datasheet for choosing the correct resistor values. Tie ACOV                                                                                                                                                                                                                            |

|                                   |                     | Optional          | R30        |       | *Ω             |      |                                                                                                                                                                                                                                                         | to GND and ACUV to VAC to set the widest operating window                                                                                                                                                                                                                                                         |

| VAC                               | 33,32               | Required          | C16        |       | 1μF            |      | Input Voltage Detection and Power Input voltage noise decoupling capacitor                                                                                                                                                                              | Place close to the VAC Pin. Short pin 33 and 32 together.                                                                                                                                                                                                                                                         |

| OUTPUT POWER- DESIGN CHECKLIST |        |              |           |     |         |       |                                                                                                                                                                                              |                                                                                                                                                                                                |

|--------------------------------|--------|--------------|-----------|-----|---------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NAME                       |        | REQUIREMENTS | Component | MIN | TYP MAX |       | DESCRIPTION                                                                                                                                                                                  | COMMENTS AND RELEVANT EQUATIONS                                                                                                                                                                |

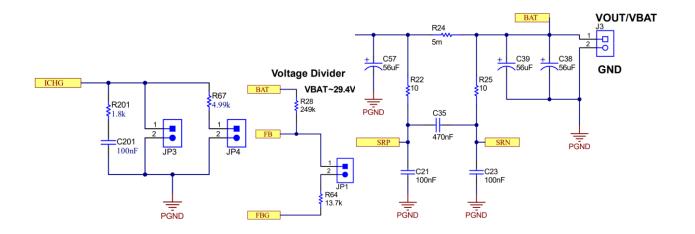

|                                |        |              |           |     |         |       | Differential charge current sensing                                                                                                                                                          |                                                                                                                                                                                                |

| SRP,SRN                        | 14,13  | Required     | R24       | =   | 5mΩ     | -     | Input current sensing resistor. This is used for both input<br>current limit regulation and for inductor current sensing of the<br>average current mode control architecutre of the charger. | The battery sense resistor between SRP and SRN is fixed at $5m\Omega$ . Using a differential value is not recommend.                                                                           |

|                                |        | Required     | R22,R25   |     | 10Ω     |       | Input current sense switching noise and common mode and                                                                                                                                      |                                                                                                                                                                                                |

|                                |        | Required     | C21,C23   |     | 100nF   |       | noise filtering                                                                                                                                                                              |                                                                                                                                                                                                |

|                                |        | Required     | C35       |     | 470nF   |       | Differential mode noise filtering                                                                                                                                                            |                                                                                                                                                                                                |

| ICHG                           |        |              |           |     |         |       | Charge Current Limit setting                                                                                                                                                                 |                                                                                                                                                                                                |

|                                | 9      | Optional     | R67       | 0kΩ | 5kΩ     | 100kΩ | Resistor to PGND                                                                                                                                                                             | Refer to section <b>7.3.4.1.1 Charge Current Programming (ICHG pin and ICHG_REG)</b> of<br>the datasheet for choosing the correct resistor values. This pin can be tied to GND<br>if not used. |

|                                |        |              |           |     |         |       | Charge voltage                                                                                                                                                                               |                                                                                                                                                                                                |

| FB. FBG                        | 12, 11 | Required     | R28       |     | 249kΩ   |       | Voltage divider used to adjust output battery regulation                                                                                                                                     | $R64 = \frac{(R28*VFB\_REG)}{(Voods_{1}VFB\_REG)}$                                                                                                                                             |

| 16,160                         | 12, 11 | Required     | R64       |     | *kΩ     |       | voltage. R28 needs to be 249kΩ                                                                                                                                                               | $R64 = {(Vout - VFB\_REG)}$                                                                                                                                                                    |

|           |       |                                               |           |      |               |                                                          | TION AND MISC INPUT/OUTPUT SIGNAL- DESIGN CHECKLIST                                                                 |                                                                                     |

|-----------|-------|-----------------------------------------------|-----------|------|---------------|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| PIN NAME  |       | REQUIREMENTS                                  | Component | MIN  | TYP           | MAX                                                      | DESCRIPTION                                                                                                         | COMMENTS AND RELEVANT EQUATIONS                                                     |

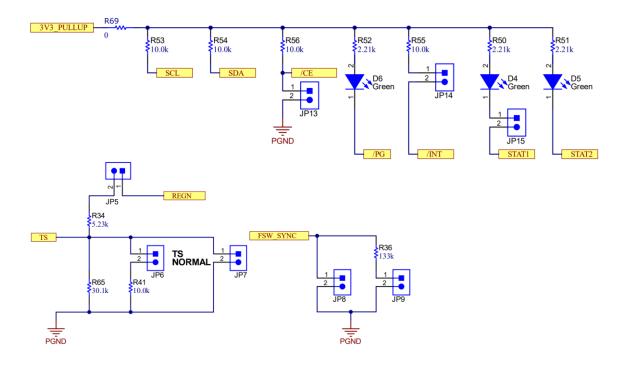

|           |       | 12C Open-drain communication input and output |           |      |               |                                                          |                                                                                                                     |                                                                                     |

| SCL,SDA   | 1,2   |                                               |           |      |               |                                                          | Pullup resistors for the open-drain I2C clock and data                                                              | The BQ25756 can operate in standalone by setting the charge current and voltage     |

|           | 1,2   | Optional                                      | R53,R54   | ļ.   | 10kΩ          | ĺ                                                        | communication bus. The pull up voltage can be between 1.8V                                                          | through external resistor on ICHG and FB, FBG pin. The 10kohm resistor is required  |

|           |       |                                               |           |      |               |                                                          | to 5V                                                                                                               | if host control configuration is desired                                            |

|           | 4     |                                               |           |      |               |                                                          | Open Drain Charge Status 1 Output                                                                                   |                                                                                     |

| STAT1     |       | Optional                                      | R50       |      | 2.21ΚΩ        |                                                          | STAT1 pull up resistor to 3.3V                                                                                      | This pin can be left floating if not used                                           |

|           |       | Орцина                                        | D4        |      | -             |                                                          | STAT1 LED Indicator Inis pin can be left floating if not used                                                       |                                                                                     |

|           |       | Open Drain Charge Status 2 Output             |           |      |               |                                                          |                                                                                                                     |                                                                                     |

| STAT2     | 5     | Optional                                      | R51       |      | 2.21ΚΩ        |                                                          | STAT2 pull up resistor to 3.3V  This pin can be left floating if not used                                           |                                                                                     |

|           |       | Ориона                                        | D5        |      | -             |                                                          | STAT2 LED Indicator                                                                                                 | This pin can be left floating if flot used                                          |

| /nc       | 6     |                                               |           |      |               |                                                          | Open Drain Active Low Power Good Indicator                                                                          |                                                                                     |

| /PG       |       | Optional                                      | R52       |      | 2.21ΚΩ        |                                                          | /PG pull up resistor to 3.3V                                                                                        | This air see he left flooring if not used                                           |

|           |       |                                               | D6        |      | -             |                                                          | /PG LED Indicator                                                                                                   | This pin can be left floating if not used                                           |

| 105       | _     |                                               |           |      |               |                                                          | Charge Enable pin                                                                                                   |                                                                                     |

| /CE       | 7     | Required                                      | R56       |      | 10kΩ          |                                                          | /CE pull up resistor to 3.3V                                                                                        | /CE must be pulled High or Low, do not leave floating.                              |

|           | 8     |                                               |           |      |               |                                                          | Battery temperature qualification voltage input                                                                     |                                                                                     |

|           |       | Optional                                      | R34       |      | *Ω            |                                                          | Refer to section <b>7.3.4.7.1 JEITA Guideline Compliance in</b> datasheet for choosing the correct resistor values. | Refer to section 7.3.4.7.1 JEITA Guideline Compliance in Charge Mode in the         |

|           |       |                                               | N34       |      | -Ω            |                                                          |                                                                                                                     | datasheet for choosing the correct resistor values.                                 |

| TS        |       | Optional                                      | R65       |      | *Ω            |                                                          | Resistor divider from REGN to TS to PGND                                                                            |                                                                                     |

|           |       |                                               |           |      | +             |                                                          |                                                                                                                     | TS pin function can be disabled with EN TS register bit. In this case, the resistor |

|           |       | Optional                                      | R41       |      | 103AT-2 10 kΩ |                                                          |                                                                                                                     | network does not need to be populated                                               |

|           | 3     | Open Drain Interrupt Output                   |           |      |               |                                                          |                                                                                                                     |                                                                                     |

| /INT      |       | Optional                                      | R55       |      | 10kΩ          |                                                          | /INT pull up resistor to 3.3V                                                                                       | This pin can be left floating if not used                                           |

|           |       |                                               |           |      |               |                                                          | Switching Frequency and Synchronization Input                                                                       |                                                                                     |

|           | 36    | Required                                      |           |      | 40kΩ -        |                                                          |                                                                                                                     | A clock can be provided on this pin in the range of 200 – 600kHz for switching      |

| FSW SYNC  |       |                                               |           |      |               | $200k\Omega$ Used to set the nominal switching frequency |                                                                                                                     | frequency synchronization. R36 can also be calculated with the following formula    |

| F3W_3TINC |       |                                               | R36       | 40kΩ |               |                                                          |                                                                                                                     | 1 ' ' '                                                                             |

|           |       |                                               |           |      |               |                                                          | $R_{FSW} = \frac{1}{10 \times (f_{SW} \times 5 \times 10^{-12} - 500 \times 10^{-9})}$                              |                                                                                     |

|           |       |                                               |           |      |               |                                                          |                                                                                                                     | 10 × () SW × 3 × 10 300 × 10 )                                                      |

| PGND      | 17    |                                               |           |      |               |                                                          | GND                                                                                                                 |                                                                                     |

| 1 0140    |       | Required                                      | -         |      | -             |                                                          | Tie this pin to PGND                                                                                                | Tie this pin to PGND                                                                |

| PGND      | 37&22 |                                               |           |      |               |                                                          | Power Ground Return                                                                                                 |                                                                                     |

|           |       | Required                                      | -         |      | -             |                                                          | IC Ground Return                                                                                                    |                                                                                     |

|           | 31    |                                               |           |      |               |                                                          | NC PINS                                                                                                             |                                                                                     |

| NC PINS   |       | Required                                      | -         |      | -             |                                                          | Leave this pin NC, do not tie to ground                                                                             |                                                                                     |

| NC PINS   | 15    | Required                                      | -         |      | -             |                                                          | Leave this pin NC, do not tie to ground                                                                             |                                                                                     |

|           | 16    | Required                                      | -         |      | -             |                                                          | Leave this pin NC, do not tie to ground                                                                             |                                                                                     |

## **BQ25756 Layout Guidelines**

Proper layout of the components to minimize high frequency current path loops is important to prevent electrical and magnetic field radiation and high frequency resonant problems. Here is a PCB layout priority list for proper layout.

| Components                                                       | Function                 | Impact                                                                 | Guidelines                                                                                                                                                                                                                                                                                                                    |

|------------------------------------------------------------------|--------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Buck high side FET,<br>Buck low side FET,<br>input capacitors    | Buck input loop          | High frequency<br>noise, ripple,<br>efficiency                         | This path forms a high frequency switching loop due to the pulsating current at the input of the buck. Place components on the same side of the board. Minimize loop area to reduce parasitic inductance. Maximize trace width to reduce parasitic resistance. Place input ceramic capacitors close to the switching FETs.    |

| Boost low side FET,<br>boost high side FET,<br>output capacitors | Boost output loop        | High frequency<br>noise, ripple,<br>efficiency                         | This path forms a high frequency switching loop due to the pulsating current at the output of the boost. Place components on the same side of the board. Minimize loop area to reduce parasitic inductance. Maximize trace width to reduce parasitic resistance. Place output ceramic capacitors close to the switching FETs. |

| Sense resistors,<br>Switching FETS,<br>inductor                  | Current path             | Efficiency                                                             | The current path from input to output through the power stage and sense resistors have low impedance. Pay attention to via resistance if they are not on the same side. The number of vias can be estimated as 1 to 2-A per via for a 10-mil via with 1oz. copper thickness.                                                  |

| Switching FETs, inductor                                         | Power stage              | Thermal,<br>efficiency                                                 | The switching FETs and inductor are the components with highest power loss. Allow enough copper area for heat dissipation.  Multiple thermal vias can be used to connect more copper layers together and dissipate more heat.                                                                                                 |

| DRV_SUP, BTST1,<br>BTST2, capacitors                             | Switching FET gate drive | High frequency<br>noise, parasitic<br>ringing, gate<br>drive integrity | The DRV_SUP capacitors are used to supply the power to drive the low side FETs. The BTST capacitors are used to drive the high side FETs. It is recommended to place the capacitors as close as possible to the IC                                                                                                            |

| LODRV1, LODRV2                                                   | Low side gate drive      | High frequency<br>noise, parasitic<br>ringing, gate<br>drive integrity | LODRV1 and LODRV2 supplies the gate drive current to turn on the low side FETs. The return of LODRV1 and LODRV2 is PGND. As current take the path of least impedance, a ground plane close to the low side gate drive traces is recommended. Minimize gate drive length and aim for at least 20 mil gate drive trace width.   |

| HIDRV1, HIDRV2, SW1<br>(pin trace), SW2 (pin<br>trace)     | High side gate drive            | High frequency<br>noise, parasitic<br>ringing, gate<br>drive integrity | HIDRV1 and HIDRV2 supplies the gate drive current to turn on the high side FETs. The return of HIDRV1 and HIDRV2 are SW1 and SW2, respectively. Route HIDRV1/SW1 and HIDRV2/SW2 pair next to each other to reduce gate drive parasitic inductance. Minimize gate drive length and aim for at least 20 mil gate drive trace width. |

|------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Current limit resistors, FSW_SYNC resistor                 | IC programmable settings        | Regulation<br>accuracy,<br>Switching integrity                         | Pin voltage determines the setting for input current limit, output current limit and switching frequency. Ground noise on these could lead to inaccuracy. Minimize ground return from these resistors to the IC ground pin.                                                                                                       |

| Input (ACP, CAN) and<br>output (SRP, SRN)<br>current sense | Current regulation              | Regulation<br>accuracy                                                 | Use Kelvin-sensing technique for input and output current sense resistors. Connect the current sense traces to the center of the pads, and run current sense traces as differential pairs, away from switching nodes.                                                                                                             |

| Input (ACUV), and output (FB, VO_SNS) voltage sensing      | Voltage sense and<br>Regulation | Regulation<br>accuracy                                                 | ACUV divider sets internal input voltage regulation in forward mode (V <sub>ACUV_DPM</sub> ). FB divider sets battery voltage regulation in forward mode (V <sub>FB_ACC</sub> ). Route the top of the divider point to the target regulation location Avoid routing close to high power switching nodes.                          |

| Bypass capacitors                                          | Noise filter                    | Noise immunity                                                         | Place lowest value cap+B7:D12acitors closest to the IC                                                                                                                                                                                                                                                                            |

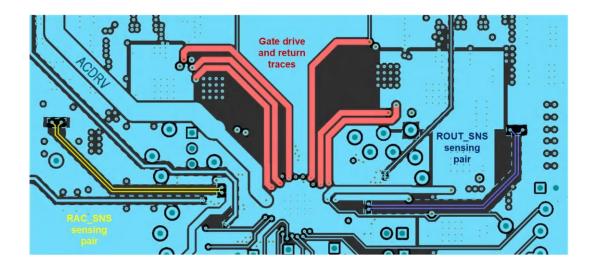

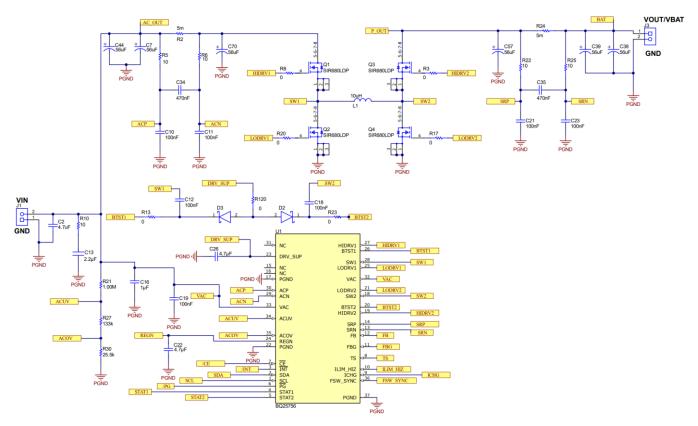

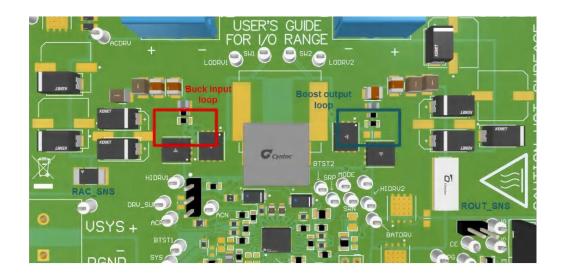

## Layout Example:

Based on the above layout guidelines, the buck-boost PCB layout example top view is shown below including all the key power components.

For both input and output current sensing resistors, differential sensing and routing method are suggested and highlighted in the Image below. Use wide trace for gate drive traces, minimum 20 mil trace width. Connect all analog grounds to a dedicated low-impedance copper plane, which is tied to the power ground underneath the IC exposed pad.