# D-CAP<sup>™</sup> Mode With All-Ceramic Output Capacitor Application

Nancy Zhang, Wenkai Wu, Weidong Zhu

DCS Computing Power Management

### ABSTRACT

The TI D-CAP<sup>™</sup> Mode controller is widely used in computing power management. D-CAP<sup>™</sup> Mode requires an appropriate amount of equivalent series resistance (ESR) on output capacitors to ensure the loop stability. However, many customers prefer to use a low-ESR capacitor such as a ceramic output capacitor. Sufficient output ripple, however, may not be available in this case to ensure the system stability. This application report introduces an implementation of D-CAP<sup>™</sup> Mode with all-ceramic capacitor application using a ripple injection approach. First, the basic D-CAP<sup>™</sup> Mode operation is described. Then, the ripple injection approach is introduced to ensure system stability. Last, the step-by-step components selection procedure is provided. The performance of TPS53219EVM with all-ceramic output capacitor using ripple injection approach is demonstrated. This ripple injection approach can be applied to TPS51116, TPS51117, TPS51315, TPS51218, TPS53219, and other single D-CAP<sup>™</sup> Mode controllers with low- output voltage application. Texas Instruments does not recommend using the ripple injection on the dual D-CAP<sup>™</sup> Mode controllers because it might cause channel-to-channel interference issues

### 1 Introduction

The D-CAP<sup>™</sup> abbreviation stands for "Direct connection to the output CAPacitor." D-CAP<sup>™</sup> Mode control provides many attractive features:

- Ease of use with no loop compensation

- Minimum external components

- · Fast transient response which reduces output capacitance, saving board space and cost

- High efficiency for both heavy and light load

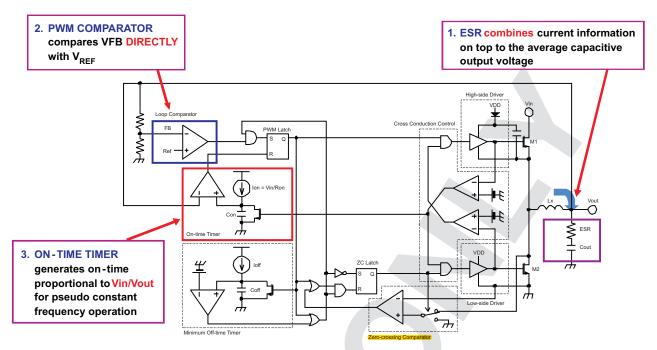

Figure 1 is basic block diagram of D-CAP<sup>™</sup> mode control with adaptive on-time modulator. D-CAP<sup>™</sup> Mode actually has three fundamental components listed as follows.

- 1. The output capacitor with ESR.

- 2. PWM comparator compares VFB with VREF directly.

- 3. On-time timer to generate pseudo constant frequency.

D-CAP, Eco-mode are trademarks of Texas Instruments.

Introduction

Figure 1. D-CAP<sup>™</sup> Mode With Adaptive On-Time Modulator Block Diagram

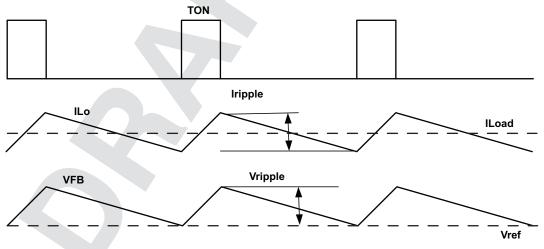

Figure 2 illustrates the operation of D-CAP<sup>™</sup> Mode with adaptive on-time control. At the beginning of each cycle, the high-side MOSFET M1 is turned on. M1 is turned off after the internal one-shot timer expires. The on-time is determined by feed forwarding Vin and Vout to keep frequency fairly constant over input voltage range. Hence, it is called adaptive on-time control. M1 is turned on again when the feedback voltage declines to Vref which indicates insufficient output voltage. Repeating the operation in this manner, the controller regulates the output voltage. The rectifying MOSFET M2 is turned on in each OFF state to keep the conduction loss at minimum. M2 is turned off when the inductor current reaches zero. This enables a seamless transition to the reduced frequency at light-load condition so that high efficiency is achieved from full load to light load.

Figure 2. D-CAP<sup>™</sup> Mode With Adaptive On-Time Operation

In D-CAP<sup>™</sup> Mode, the output voltage is directly compared by the PWM comparator. Theoretically, the gain and bandwidth of a comparator are infinite. So, the loop gain from the output node becomes infinite. This means that the loop transfer function which uses the output node voltage as a state variable is not

www.ti.com

derivable and not measurable as well. As for the stability analysis, a loop transfer function that uses an intrinsic capacitance node voltage as a state variable is derivable. The loop stability of D-CAP<sup>™</sup> Mode is determined by certain ESR of the output capacitor. The proper ESR of the output capacitor keeps the loop stable and results in less PWM jitter. The loop stability criteria and jitter requirement are demonstrated as follows.

1. Loop stability criteria:

$$f_0 = \frac{1}{2\pi \times \text{ESR} \times \text{Co}} < \frac{f_{\text{sw}}}{3}$$

2. Jitter Performance: Required 10-mV to 15-mV ripple at VFB pin; usually, choose 12 mV (for higher output voltage, higher injected ripple may be needed).

$$\mathsf{ESR} \geq \frac{\mathsf{V}_{\mathsf{out}} \times \mathsf{12} \ \mathsf{mV}}{\mathsf{V}_{\mathsf{ref}} \times \mathsf{I}_{\mathsf{Ripple}}}$$

(2)

(3)

(4)

(1)

For application with all-ceramic output capacitors, the ESR is usually too small to meet the preceding criteria. Double pulse or more jitter might be shown on the PWM waveforms. In this case, the ripple injection approach can be used for injecting a small virtual ripple into the VFB pin to make the D-CAP<sup>™</sup> Mode stable. This application report shows how to implement a ripple injection network and what the performance looks like.

### 2 **Ripple Injection Approach**

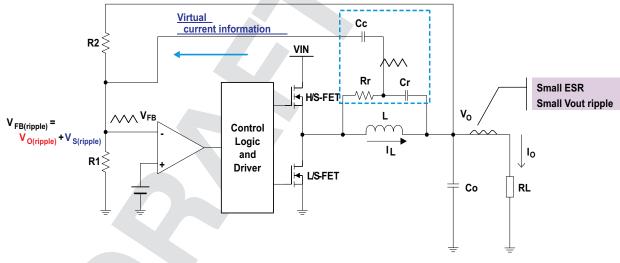

Figure 3 shows the ripple injection network. This approach is simple and only composed of two capacitors and one resistor. Rr and Cr across inductor generates the ripple by using DCR of the inductor. This ripple voltage is analogous to ripple voltage generated across the ESR of a standard capacitor. The ripple voltage is then coupled into the feedback VFB pin through Cc. Cc is used to isolate the dc voltage because only a small ac ripple voltage is needed.

### Figure 3. D-CAP<sup>™</sup> Mode With Ripple Injection Approach

New loop stability criteria for D-CAP<sup>™</sup> Mode with ripple injection approach:

$$\frac{L \times Co}{R_r \times C_r} > \frac{Ton}{2}$$

$$C_r > C_c > \frac{1}{2\pi \times f_{sw} \times \left(\frac{R1 \times R2}{R1 + R2}\right)}$$

SLVA453–January 2011 Submit Documentation Feedback

## 3 Rr, Cr, and Cc Selection Procedure

The following step-by-step design procedure shows how to choose this ripple injection network Rr, Cr, and Cc. TPS53219EVM is used as an example.

Vin: 12 V Vout: 1.1 V Iout: 0 A - 25 A Inductor L: 0.44  $\mu$ H, DCR: 0.32 m $\Omega$ Switching frequency f<sub>sw</sub>: 300 kHz Output capacitor Co: 5 x 100  $\mu$ F = 500  $\mu$ F ceramic capacitors, ESR: 0.4 m $\Omega$ R1: 10 k $\Omega$ , R2: 8.25 k $\Omega$ Ton: PWM on time

- 1. Select RrCr: Inject at approximately 12-mV virtual ripple at VFB pin.

- (a) RrCr = L/DCR, means you extract the same ripple from the DCR of the inductor to VFB pin.

- (b) RrCr > L/DCR, means you extract the smaller ripple from the DCR of the inductor to VFB pin; the transient may be good but may have heavier PWM jitter.

- (c) RrCr < L/DCR, means you extract the larger ripple from the DCR of the inductor to VFB pin; the transient may be sacrificed a little for less PWM jitter.

$$\begin{split} & I_{\text{Ripple}} = \frac{(V_{\text{in}} - V_{\text{out}}) \times V_{\text{out}}}{L \times f_{\text{sw}} \times V_{\text{in}}} & I_{\text{Ripple}} = 7.57 \text{ A} \\ & V_{\text{Ind}\_\text{DCR}\_\text{Ripple}} = I_{\text{Ripple}} \times \text{DC} & V_{\text{Ind}\_\text{DCR}\_\text{Ripple}} = 2.422 \text{ mV} \\ & V_{\text{CO}\_\text{Ripple}} = \frac{I_{\text{Ripple}}}{8 \times \text{Co} \times f_{\text{sw}}} & V_{\text{CO}\_\text{Ripple}} = 6.31 \text{ mV} \\ & V_{\text{INJ}\_\text{Ripple}} = \max(V_{\text{CO}\_\text{Ripple}}, 12 \text{ mV}) & V_{\text{INJ}\_\text{Ripple}} = 12 \text{ mV} \\ & k = \frac{V_{\text{INJ}\_\text{Ripple}}}{V_{\text{INJ}\_\text{DCR}\_\text{Ripple}}} & k = 4.955 \text{ k} \text{ Ripple injection ratio} \\ & R_r \times C_r = \frac{L}{k \times \text{DCR}} & R_r \times C_r = 0.000277 \end{split}$$

2. Ensure that RrCr satisfies the loop stability:

$$\frac{L \times Co}{R_r \times C_r} > \frac{Ton}{2}$$

$$\frac{L \times Co}{R_r \times C_r} = 0.794 \times 10^{-6} > \frac{Ton}{2} = 0.153 \times 10^{-6}$$

- 3. Set Rr =10 k $\Omega$ , then calculate Cr = 0.027  $\mu$ F or set Cr, then calculate Rr.

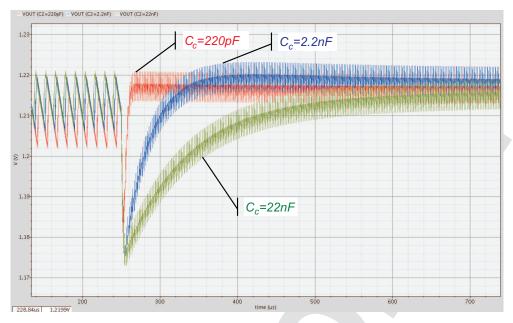

- 4. Cc selection:

4

Cc is used to isolate dc voltage. If Cc is large, the transient is slower. If the Cc is small, the transient is faster. So, Cc=1000 pF is recommended. This value is good for most applications. Figure 4 shows the Cc value impact on the transient response.

TEXAS INSTRUMENTS

www.ti.com

(5)

(6)

(7)

(8)

(9)

5

#### www.ti.com

5. Ensure that Cr, Cc meet the new loop stability:

$$C_{\rm r} > C_{\rm c} > \frac{1}{2\pi \times f_{\rm sw} \times \left(\frac{{\rm R1} * {\rm R2}}{{\rm R1} + {\rm R2}}\right)}$$

$$\frac{1}{2\pi \times f_{\rm sw} \times \left(\frac{{\rm R1} \times {\rm R2}}{{\rm R1} + {\rm R2}}\right)} = 117 \, \rm pF$$

$$C_{\rm r} = 0.027 \, \mu \rm F$$

$$C_{\rm c} = 1000 \, \rm pF$$

6. Check the output dc voltage accuracy.

ESR = 0.4 mΩ  $V_{\text{ESR Ripple}}$  = ESR × I<sub>Ripple</sub>

V<sub>ESR Ripple</sub> = 3.028 mV

So, total approximate average ripple voltage at feedback VFB pin is:

$$V_{FB\_Ripple} = V_{ESR\_Ripple} + V_{CO\_Ripple} + 12mV$$

$$V_{FB\_Ripple} = 21.338 mV$$

$$V_{ref} = 0.6 V$$

$$V_{FB} = V_{ref} + \frac{V_{FB\_Ripple}}{2}$$

$$V_{FB} = 0.6107 V$$

$$V_{out} = \left(\frac{R1 + R2}{R1}\right) \times V_{FB}$$

$$V_{out} = 1.115 V$$

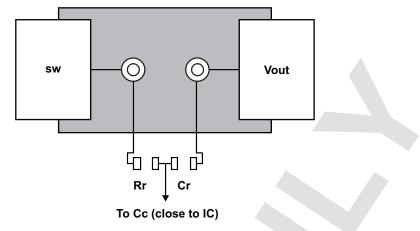

7. Ripple injection parts layout consideration: Rr and Cr must be placed close to the inductor and Cc must be close to the IC as shown in Figure 5.

Figure 5. Ripple Injection Network Layout Consideration

### 4 The Performance of TPS53219EVM With All-Ceramic Output Capacitor

The TPS53219 is a D-CAP<sup>™</sup> Mode with adaptive on-time controller. Usually, the TPS53219 needs an output capacitor with certain ESR for proper operation. However, equivalent or superior performance can be obtained by using an all-ceramic output capacitor and ripple injection approach.

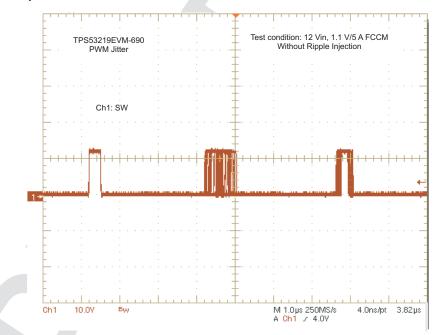

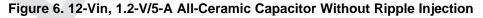

Based on the design procedure described in this application report, the following values were derived: Rr = 10 k $\Omega$ , Cr = 0.027  $\mu$ F, Cc = 1000 pF. Figure 6 shows the PWM waveform that has double pulse and heavy jitter without ripple injection. Figure 7 shows the waveform that has no double pulse and less jitter with the ripple injection.

www.ti.com

Figure 7. 12-Vin, 1.2-V/5-A All-Ceramic Capacitor With Ripple Injection

The bode plot is not measurable for the D-CAP<sup>™</sup> Mode with an adaptive on-time modulator. However, a bode plot for D-CAP<sup>™</sup> Mode with ripple injection can be measured, and it can provide a rough idea about loop stability. (It is worthwhile to mention that the measured bandwidth is not related to the real transient performance because a small-signal model is not applicable to the large-signal controller, i.e., D-CAP<sup>™</sup> Mode control).

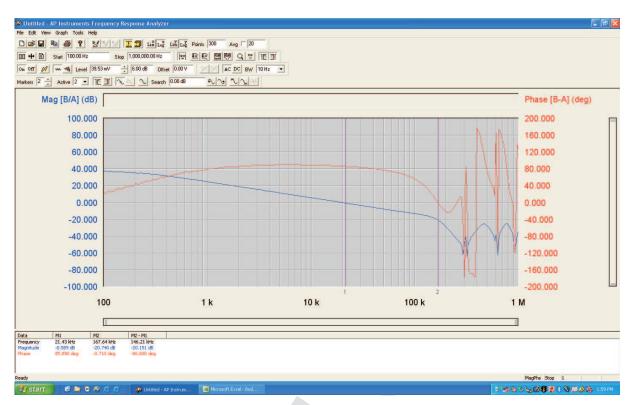

Figure 8 is the bode plot for TPS53219EVM with all-ceramic capacitor application. Test condition: 12 Vin, 1.1 V/25 A, crossover frequency: 21.43 kHz, phase margin: 85.50 degrees, gain margin: -21.58 dB.

www.ti.com

Figure 8. Bode Plot for TPS53219EVM With All-Ceramic Capacitor Application

### 5 Conclusions

The D-CAP<sup>™</sup> Mode control was introduced to satisfy the market requirement of low-cost, high-performance, dc-dc converters. The ripple injection approach overcomes the limitation of the original D-CAP<sup>™</sup> Mode control. The D-CAP<sup>™</sup> Mode with all-ceramic output capacitor and ripple injection approach shows superior performance and ease of use.

### 6 References

- 1. Tetsuo Tateishi, *The D-CAP™ Mode operation and an implementation of the OOA™ skip mode*, TI's Integrated Power Conference 2005

- 2. Adaptive Constant On-Time (D-CAP<sup>™</sup>) Control Study In Notebook Applications application report (SLVA281)

- 3. Wenkai Wu, The D-CAP™ Mode with all ceramic output design procedure, Presentation, 2010

- 4. TPS53219, Wide Input Voltage, Eco-mode<sup>™</sup>, Single Synchronous Step-Down Controller data sheet (SLUSAA8)

- 5. Using the TPS53219EVM-690 Wide-Input Voltage, Eco-mode<sup>™</sup>, Single, Synchronous, Step-Down Controller user's guide (<u>SLVU431</u>)