# Single Cell Battery Fuel Gauge with Integrated Protector

## FEATURES

- Highly Integrated Battery Fuel Gauge and Protector for 1-Series Li-Ion Applications

- Fully Integrated 262.144 kHz Low frequency Oscillator

- Fully Integrated 50.33 MHz High Frequency Oscillator

- Integrated High Side NMOS Protection FET Drive

- Integrated Charge Pump

- CHG/DSG FET drivers

- Linear Charge Control

- Minimum System Voltage Regulation

- 32-bit RISC ARM Cortex-M0+ CPU

- Single-cycle 32-bit multiplier

- 24-bit SysTick timer

- Nested Vector Interrupt Controller (NVIC)

- 2-wire serial debug (SWD)

- 192Kbytes of Flash memory with ECC

- 24Kbytes of RAM

- 32Kbytes of ROM

- Host Communication Support

- I2C (100 and 400kHz)

- High Accuracy Analog Front End with Three Independent ADC's

- 18 bit High Resolution Delta-Sigma ADC for continuous current measurement

- 16 bit High Resolution Delta-Sigma ADC for voltage/temperature measurement

- 16 (including sign) bit High Resolution Delta-Sigma ADC for high frequency current sample measurement

- Synchronous Measurement of Voltage/Current

- Programmable Current Protection

- Overcurrent in Discharge

- Overcurrent in Charge

- Supports up to Two External Thermistor measurements and an internal temperature sensor

- Peripherals

- Two 24-bit General Purpose Timers

- General Purpose I/O's

- CRC generator

- True Random Number Generator

## DESCRIPTION

The bq7037 is a highly integrated system on chip for battery management and gas-gauge applications.

In a single CMOS Integrated Circuit, the bq7037 combines high-accuracy analog measurement capabilities with a low-power high-speed ARM Cortex M0+ processor, integrated flash memory, integrated LDO for core voltage operation and an array of peripheral features and communication ports. The program flash allows fast development of custom implementations, and the low-power analog peripherals improve accuracy beyond discrete implementations. The integrated battery charge and discharge protection feature eliminates the need for an external protection device.

## Device Information

| Part Number  | Package | Body Size (Nom)             |

|--------------|---------|-----------------------------|

| SN7037B0YFDR | YFD-32  | 1610 $\mu$ m x 3410 $\mu$ m |

| SN7037B0YFDT |         |                             |

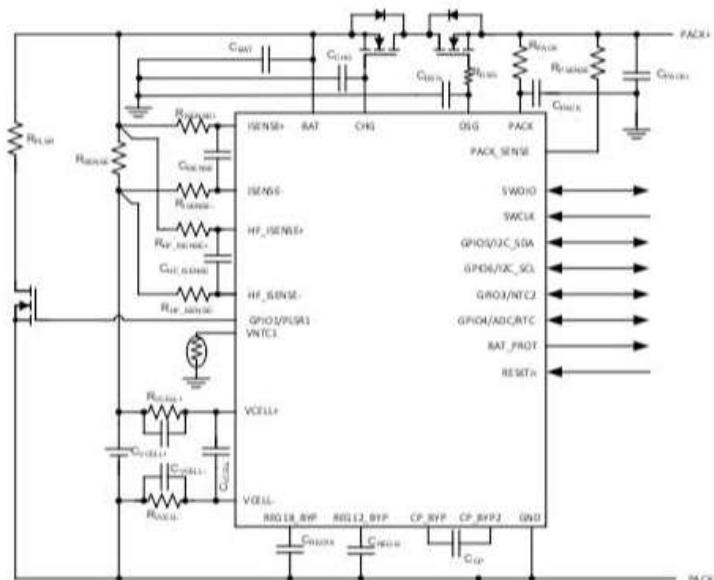

## Simplified Schematic

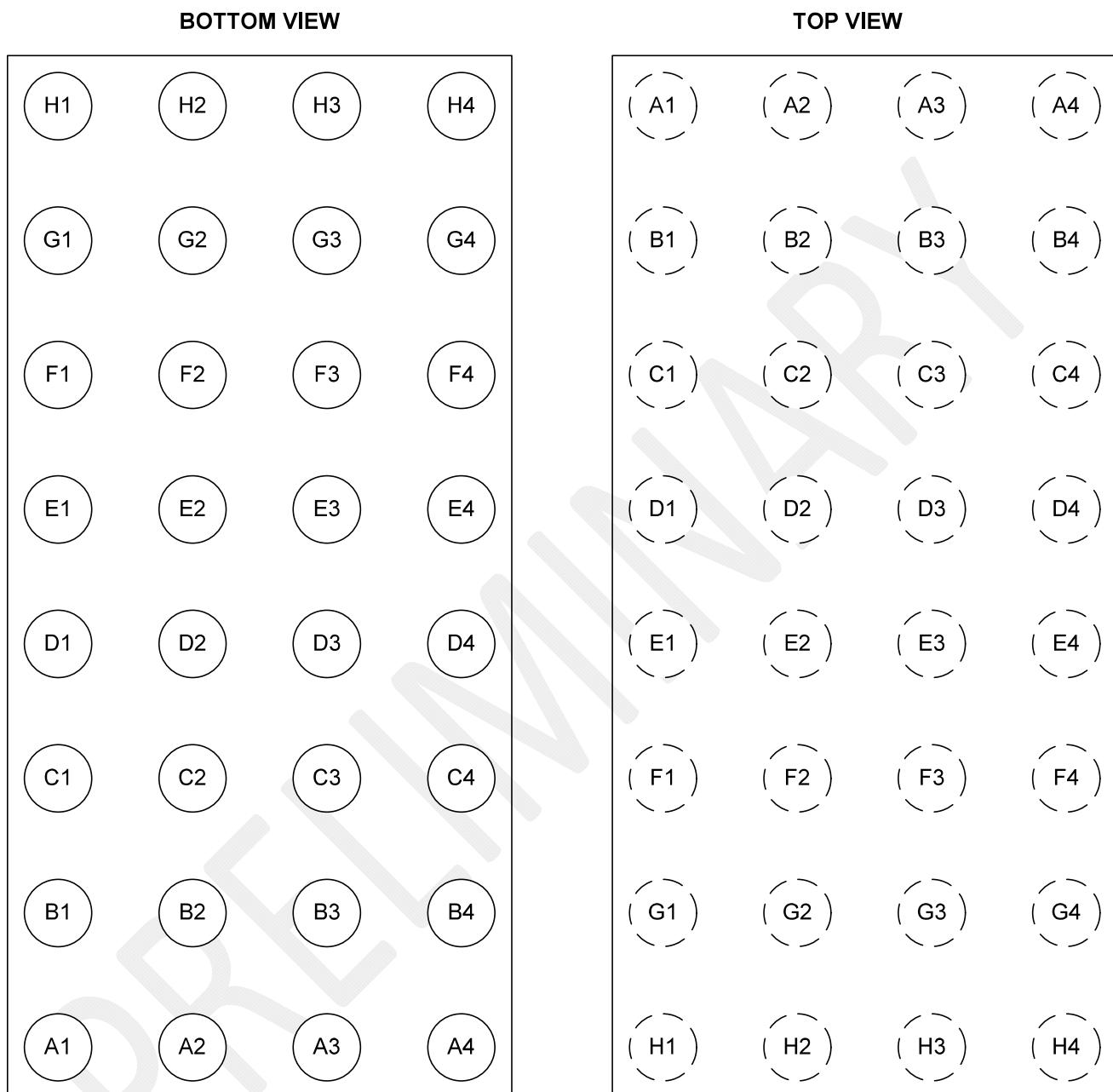

## 1 Pin Configurations and Functions

Figure 1 Pin Configuration

Table 1-1 Pin Functions

| TERMINAL          |     | I/O | DESCRIPTION                                                                                                                       |

|-------------------|-----|-----|-----------------------------------------------------------------------------------------------------------------------------------|

| NAME              | PIN |     |                                                                                                                                   |

| PACK              | E2  | P   | Device power from system when charger connected                                                                                   |

| PACK_SENSE        | E1  | I   | Measurement of the PACK voltage used for linear control of the charge FET and A/D input                                           |

| BAT               | F3  | P   | Device power from cell                                                                                                            |

| BAT_PROT          | G1  | O   | High impedance output pin with the same voltage as the BAT pin                                                                    |

| RESETn            | B4  | I   | Active Low Reset input with internal pull up.                                                                                     |

| CHG               | A3  | O   | External high side N-channel Charge FET driver                                                                                    |

| DSG               | A2  | O   | External high side N-channel Discharge FET driver                                                                                 |

| ISENSE+           | H2  | I   | Pack side of the current sense resistor for the continuous current A/D converter                                                  |

| ISENSE-           | H1  | I   | Cell side of the current sense resistor for the continuous current A/D converter                                                  |

| SWCLK             | B3  | I   | Serial Wire Debug Clock                                                                                                           |

| SWDIO             | C3  | I/O | Serial Wire Debug Data In/Out                                                                                                     |

| HF_ISENSE+        | H4  | I   | Pack side of the current sense resistor for the High Frequency Current A/D                                                        |

| HF_ISENSE-        | H3  | I   | Cell side of the current sense resistor for the High Frequency Current A/D                                                        |

| VCELL+            | G3  | I   | Positive terminal of the cell                                                                                                     |

| VCELL-            | G2  | I   | Negative terminal of the cell                                                                                                     |

| VNTC1             | C4  | I   | A/D input designed to measure an external NTC thermistor                                                                          |

| GPIO1/PLSR1       | F1  | I/O | Pin configurable as a general purpose input/output or as a pulser FET gate driver synchronized to the high frequency A/D sampling |

| GPIO2/PLSR2       | F2  | I/O | Pin configurable as a general purpose input/output, or as a driver for a second pulser FET                                        |

| GPIO3/VNTC2       | B2  | I/O | Pin configurable as a general purpose input/output or as an A/D input designed to measure an external NTC thermistor              |

| GPIO4/ADC/RTC     | C2  | I/O | Pin configurable as a general purpose input/output as an A/D input, or as a real time clock for an external precision clock input |

| GPIO5/I2C_SDA/HDQ | C1  | I/O | Pin configurable as a general purpose input/output, the I2C bi-directional data line, or the bi-directional HDQ line              |

| GPIO6/I2C_SCL     | B1  | I/O | General purpose input/output or the I2C clock line                                                                                |

| REG18_BYP         | G4  | O   | Internal linear regulator(1.8V) supply connection to an external bypass capacitor                                                 |

|                   | E3  | O   | Internal linear regulator(1.8V) supply connection to an external bypass capacitor                                                 |

| CP_BYP            | A1  | O   | Internal charge pump connection to an external bypass capacitor                                                                   |

| GND               | F4  | P   | Device Ground                                                                                                                     |

|                   | D1  | P   | Device Ground                                                                                                                     |

|                   | D4  | P   | Device Ground                                                                                                                     |

|                   | A4  | P   | Device Ground                                                                                                                     |

| REG12_BYP         | D2  | O   | Internal linear regualtor (1.2V) supply connection to an external bypass capacitor                                                |

|                   | D3  | O   | Internal linear regualtor (1.2V) supply connection to an external bypass capacitor                                                |

|                   | E4  | O   | Internal linear regualtor (1.2V) supply connection to an external bypass capacitor                                                |

\*KEY: I =Input, O = Output, NC = No Connect, P = Power

Table 1-2 Pin Functions Ball Grids

**Top View**

|   |                   |               |            |            |

|---|-------------------|---------------|------------|------------|

| A | CP_BYP            | DSG           | CHG        | GND        |

| B | GPIO6/I2C_SCL     | GPIO3/VNTC2   | SWCLK      | RESETn     |

| C | GPIO5/I2C_SDA/HDQ | GPIO4/ADC/RTC | SWDIO      | VNTC1      |

| D | GND               | REG12_BYP     | REG12_BYP  | GND        |

| E | PACK_SENSE        | PACK          | REG18_BYP  | REG12_BYP  |

| F | GPIO1/PLSR1       | GPIO2/PLSR2   | BAT        | GND        |

| G | BAT_PROT          | VCELL-        | VCELL+     | REG18_BYP  |

| H | ISENSE-           | ISENSE+       | HF_ISENSE- | HF_ISENSE+ |

1

2

3

4

**Bottom View**

|   |                   |               |            |            |

|---|-------------------|---------------|------------|------------|

| H | ISENSE-           | ISENSE+       | HF_ISENSE- | HF_ISENSE+ |

| G | BAT_PROT          | VCELL-        | VCELL+     | REG18_BYP  |

| F | GPIO1/PLSR1       | GPIO2/PLSR2   | BAT        | GND        |

| E | PACK_SENSE        | PACK          | REG18_BYP  | REG12_BYP  |

| D | GND               | REG12_BYP     | REG12_BYP  | GND        |

| C | GPIO5/I2C_SDA/HDQ | GPIO4/ADC/RTC | SWDIO      | VNTC1      |

| B | GPIO6/I2C_SCL     | GPIO3/VNTC2   | SWCLK      | RESETn     |

| A | CP_BYP            | DSG           | CHG        | GND        |

1

2

3

4

## 2 Specifications

### 2.1 Absolute Maximum Ratings

| SYMBOL           | PARAMETER                                                                                                  | VALUE        | UNITS |

|------------------|------------------------------------------------------------------------------------------------------------|--------------|-------|

| $V_{PWR}$        | BAT, VCELL+, VCELL-, BAT_PROT                                                                              | -0.3 to 6    | V     |

| $V_{PACK}$       | PACK, PACK_SENSE                                                                                           | -0.3 to 6.5  | V     |

| $V_{SR}$         | ISENSE+, ISENSE--, HF_ISENSE+, HF_ISENSE-                                                                  | -0.3 to 6    | V     |

| $V_{GPIOA}$      | RESETn, SWDIO, SWCLK, VNTC1, GPIO3/VNTC2, GPIO4/ADC/RTC, GPIO5/I2C_SDA/HDQ, GPIO6/I2C_SCL, GND, GND(TEST1) | -0.3 to 2.1  | V     |

| $V_{GPIOB}$      | GPIO1/PLSR1, GPIO2/PLSR2                                                                                   | -0.3 to 6    | V     |

| $V_{OUT}$        | CHG, DSG, CP_BYP                                                                                           | -0.3 to 8.5  | V     |

| $V_{REG12\_BYP}$ | REG12_BYP                                                                                                  | -0.3 to 1.40 | V     |

| $V_{REG18\_BYP}$ | REG18_BYP                                                                                                  | -0.3 to 2.1  | V     |

| $T_A$            | Operating Ambient Temperature                                                                              | -40 to 85    | °C    |

| $T_{STORAGE}$    | Storage Temperature Range                                                                                  | -65 to 150   | °C    |

† Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 2.2 ESD Ratings

| SYMBOL   |                         | VALUE                                                            | UNITS   |

|----------|-------------------------|------------------------------------------------------------------|---------|

| $V(ESD)$ | Electrostatic Discharge | Human Body Model (HBM), per JEDEC specification JESD22-A114      | +/-1500 |

|          |                         | Charged-device model (CDM), per JEDEC specification JESD22-C101F | +/-500  |

## 2.3 Recommended Operating Conditions

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| SYMBOL              | DESCRIPTION                         | CONDITIONS                                                                                      | MIN  | TYP <sup>(1)</sup> | MAX  | UNITS            |

|---------------------|-------------------------------------|-------------------------------------------------------------------------------------------------|------|--------------------|------|------------------|

| $V_{\text{BAT}}$    | Battery Input Voltage               |                                                                                                 | 2.0  |                    | 5.0  | V                |

| $V_{\text{PACK}}$   | Pack Input Voltage                  |                                                                                                 | 2.0  |                    | 5.0  | V                |

| $V_{\text{FWRITE}}$ | $V_{\text{IN}}^{(2)}$ Input Voltage | Flash Erase and Write allowed                                                                   | 2.4  |                    | 5.0  | V                |

| $C_{\text{BAT}}$    | Battery Input Capacitor             |                                                                                                 | 0.08 | 0.1                | 0.12 | $\mu\text{F}$    |

| $C_{\text{REG18}}$  | 1.8V LDO Bypass Capacitor           |                                                                                                 | 0.8  | 1                  | 1.2  | $\mu\text{F}$    |

| $C_{\text{CP}}$     | CP Bypass Capacitor                 |                                                                                                 | 0.2  | 1                  | 1.2  | $\mu\text{F}$    |

| $C_{\text{CHGIN}}$  | CHG FET ripple Capacitor            | Required if CHG FET $C_{\text{GS}} < 10\text{nF}$<br>$3\text{V} < V_{\text{CHG}} < 8.1\text{V}$ | 4.32 | 4.7                | 10   | $\text{nF}$      |

| $C_{\text{REG12}}$  | 1.2V LDO Bypass Capacitor           |                                                                                                 | 0.8  | 1                  | 1.2  | $\mu\text{F}$    |

| $C_{\text{PACK}}$   | PACK Capacitor                      |                                                                                                 | 0.8  | 1                  | 1.2  | $\mu\text{F}$    |

| $R_{\text{PACK}}$   | PACK Series Resistor                |                                                                                                 | 180  | 200                | 220  | $\Omega$         |

| $R_{\text{PSENSE}}$ | PACK Sense Series Resistor          |                                                                                                 | 9    | 10                 | 11   | $\text{k}\Omega$ |

(1) Production test uses typical values

(2) If ( $\text{BAT} > 2\text{V}$ ),  $V_{\text{IN}} = \text{BAT}$ , else  $V_{\text{IN}} = \text{PACK}$

## 2.4 Thermal Information

| SYMBOL                  | PARAMETER <sup>(1)</sup>                                    | VALUE | UNITS              |

|-------------------------|-------------------------------------------------------------|-------|--------------------|

| $\Theta_{\text{JA}}$    | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 78.1  | $^\circ\text{C/W}$ |

| $\Theta_{\text{JC}}$    | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 0.3   |                    |

| $\Theta_{\text{JB}}$    | Junction-to-board thermal resistance <sup>(4)</sup>         | 15.9  |                    |

| $\Psi_{\text{JT}}$      | Junction-to-top characterization parameter <sup>(5)</sup>   | 0.2   |                    |

| $\Psi_{\text{JB}}$      | Junction-to-board characterization parameter <sup>(6)</sup> | 15.7  |                    |

| $\Theta_{\text{JCBOT}}$ | Junction-to-case(bottom) thermal resistance <sup>(7)</sup>  | NA    |                    |

1. For more information about traditional and new thermal metrics, see the device Package Thermal Metrics application report, SPRA953.

2. The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

3. The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

4. The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

5. The junction-to-top characterization parameter,  $\Psi_{\text{JT}}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\Theta_{\text{JA}}$ , using a procedure described in JESD51-2a (sections 6 and 7).

6. The junction-to-board characterization parameter,  $\Psi_{\text{JB}}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\Theta_{\text{JA}}$ , using a procedure described in JESD51-2a (sections 6 and 7).

7. The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

## 2.5 Supply Current

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -25^\circ\text{C}$  to  $65^\circ\text{C}$  unless otherwise noted.

| PARAMETER        | TEST CONDITIONS                                                 | MIN | TYP | MAX | UNITS |

|------------------|-----------------------------------------------------------------|-----|-----|-----|-------|

| AWAKE Mode       | All Subsystems Enabled, Erasing Flash <sup>1</sup>              |     | 15  |     | mA    |

|                  | All Subsystems Enabled, No Flash Erase <sup>1</sup>             |     | 1.7 |     | mA    |

| Sleep Mode       | SLEEP1 - See Table 4-1 for blocks enabled/disabled <sup>1</sup> |     | 135 |     | µA    |

|                  | SLEEP2 - See Table 4-1 for blocks enabled/disabled <sup>1</sup> |     | 134 |     | µA    |

|                  | SLEEP3 - See Table 4-1 for blocks enabled/disabled              |     | 102 |     | µA    |

|                  | SLEEP4 - See Table 4-1 for blocks enabled/disabled              |     | 47  |     | µA    |

| Test_Mode        | See Table 4-1 for blocks enabled/disabled                       |     | 15  |     | mA    |

| Test_Init Mode   | See Table 4-1 for blocks enabled/disabled                       |     | 600 |     | µA    |

| Reset Mode       | See Table 4-1 for blocks enabled/disabled                       |     | 35  |     | µA    |

| Flash_Init Mode  | See Table 4-1 for blocks enabled/disabled                       |     | 53  |     | µA    |

| Power_Ready Mode | See Table 4-1 for blocks enabled/disabled                       |     | 49  |     | µA    |

| Power_Off Mode   | See Table 4-1 for blocks enabled/disabled                       |     | 3.5 |     | µA    |

1. Both HF\_I\_ADC/HF\_VT\_ADC are assumed to be running with a Output Sample Rate of 256 Hz

## 2.6 Voltage References

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER              | TEST CONDITIONS                                                      | MIN                                                                                                                                                                | TYP   | MAX   | UNITS |        |

|------------------------|----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|--------|

| $V_{CC\_REF}$          | Coulomb Counter Reference Voltage                                    | $T_A = 25^\circ\text{C}$                                                                                                                                           | 1.00  | 1.16  | 1.34  | V      |

| $V_{REF1p0}$           | Internal System Reference Voltage                                    | $T_A = 25^\circ\text{C}$                                                                                                                                           | 0.999 | 1.000 | 1.001 | V      |

| $V_{CCREF\_DRIFT}$     | CC_REF Reference Voltage Drift                                       | $T_A = -25^\circ\text{C}$ to $65^\circ\text{C}$                                                                                                                    |       |       | ±56   | PPM/°C |

| $PSRR_{CC\_REF}^{(1)}$ | Power Supply Rejection Ratio ( $\Delta V_{BAT}/\Delta V_{CC\_REF}$ ) | $I_{REG18} = 10\text{mA}$ , $V_{BAT} > 2.5\text{V}$ , $V_{BATAC} \pm 100\text{mV}$<br>$f = 0$ to $20\text{kHz}$<br>$T_A = -25^\circ\text{C}$ to $65^\circ\text{C}$ | 40    | 50    | 60    | dB     |

| $I_{CC\_REF}$          |                                                                      |                                                                                                                                                                    |       | 10    |       | µA     |

| $V_{HF\_REF}$          | HF_ADC Reference Voltage                                             | $T_A = 25^\circ\text{C}$                                                                                                                                           | 1.00  | 1.21  | 1.36  | V      |

| $V_{HF\_REF\_DRIFT}$   | HF_ADC Reference Voltage Drift                                       | $T_A = -25^\circ\text{C}$ to $65^\circ\text{C}$                                                                                                                    |       |       | ±56   | PPM/°C |

| $PSRR_{HF\_REF}^{(1)}$ | Power Supply Rejection Ratio ( $\Delta V_{BAT}/\Delta V_{HF\_REF}$ ) | $I_{REG18} = 10\text{mA}$ , $V_{BAT} > 2.5\text{V}$ , $V_{BATAC} \pm 100\text{mV}$<br>$f = 0$ to $20\text{kHz}$<br>$T_A = -25^\circ\text{C}$ to $65^\circ\text{C}$ | 40    | 50    | 60    | dB     |

| $I_{HF\_REF}$          | Current Consumption                                                  | $HF\_ADC$ Mod $F_s = 512\text{k}$                                                                                                                                  |       | 35    |       | µA     |

(1) Specified by design. Not production tested

## 2.7 1.8V LDO Regulator (REG18)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER                          |                                                                                           | TEST CONDITIONS                                                                                                                                                                    | MIN  | TYP  | MAX  | UNITS         |

|------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|---------------|

| $V_{\text{REG18}}$                 | Regulator output voltage                                                                  | $2 \text{ V} < \text{VIN}^1 < 5 \text{ V}$ , $I_{\text{REG18}} = 0$ to $12 \text{ mA}$<br>$2.4 \text{ V} < \text{VIN}^1 < 5 \text{ V}$ , $I_{\text{REG18}} = 0$ to $22 \text{ mA}$ | 1.75 | 1.8  | 1.85 | V             |

|                                    |                                                                                           | After trim is loaded                                                                                                                                                               | -3   |      | +3   | %             |

| $\Delta V_{\text{REG18TEMP}}$      | Regulator output change with temperature ( $\Delta V_{\text{REG18}} / V_{\text{REG18}}$ ) | $I_{\text{REG18}} = 1 \text{ mA}$                                                                                                                                                  | -1   |      | 1    | %             |

| $\Delta V_{\text{REG18LINE}}$      | Line regulation ( $\Delta V_{\text{REG18}} / \Delta V_{\text{BAT}}$ )                     | $I_{\text{REG18}} = 22 \text{ mA}$<br>$V_{\text{BAT}} = 2$ to $5\text{V}$                                                                                                          | -2   |      | 2    | %             |

| $\Delta V_{\text{REG18LOAD}}$      | Load regulation ( $\Delta V_{\text{REG18}} / \Delta I_{\text{REG18}}$ )                   | $I_{\text{REG18}} = 0$ to $22 \text{ mA}$                                                                                                                                          | -2   |      | 2    | %             |

| $\Delta V_{\text{TRANSIENT}}$      | Transient response load step                                                              | $I_{\text{REG18}} = 0$ to $10 \text{ mA}$                                                                                                                                          | -55  |      | 45   | mV            |

| $I_{\text{REG18\_EXT}}$            | External load capability                                                                  | $V_{\text{BAT}} = 2$ to $5\text{V}$                                                                                                                                                |      |      | 1    | mA            |

| $I_{\text{REG18\_SHORT}}$          | Short Circuit Current Limit                                                               | $V_{\text{REG18}} = 0 \text{ V}$                                                                                                                                                   | 20   | 38   | 85   | mA            |

|                                    |                                                                                           | $V_{\text{REG18}} = 0 \text{ V}$ , After trim is loaded                                                                                                                            | 26   | 38   | 72   | mA            |

| $\text{PSRR}_{\text{REG18}}^{(2)}$ | Power Supply Rejection Ratio ( $\Delta V_{\text{BAT}} / \Delta V_{\text{REG18}}$ )        | $I_{\text{REG18}} = 10 \text{ mA}$ , $V_{\text{BAT}} > 2.5 \text{ V}$ , $f = 1 \text{ Hz}$ to $20 \text{ kHz}$ , $\text{VIN}^{(1)}$ Ripple = $\pm 100 \text{ mV}$                  | 30   | 40   | 50   | dB            |

| $V_{\text{REG18TH+}}$              | REG18 Good Threshold Rising                                                               | $\text{POR} = V_{\text{REG18TH+}} + V_{\text{REG18HYS}}$                                                                                                                           |      | 1.73 |      | V             |

| $V_{\text{REG18TH-}}$              | REG18 Good Threshold Falling                                                              |                                                                                                                                                                                    | 1.63 | 1.7  | 1.77 | V             |

| $V_{\text{REG18HYS}}$              | REG18 Good Hysteresis                                                                     |                                                                                                                                                                                    | 10   | 30   | 50   | mV            |

| $I_{\text{REG18}}$                 | Current Consumption                                                                       |                                                                                                                                                                                    |      | 6    |      | $\mu\text{A}$ |

(1) If ( $\text{BAT} > 2\text{V}$ ),  $\text{VIN} = \text{BAT}$ , else  $\text{VIN} = \text{PACK}$

(2) Specified by design. Not production tested.

## 2.8 1.2V LDO Regulator (REG12)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER                          |                                                                                         | TEST CONDITIONS                                                                                                                                           | MIN  | TYP  | MAX  | UNITS         |

|------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|---------------|

| $V_{\text{REG12}}$                 | Regulator output voltage                                                                | $2 \text{ V} < \text{VIN}^1 < 5 \text{ V}$ , $I_{\text{REG12}} = 0$ to $10 \text{ mA}$                                                                    | 1.15 | 1.2  | 1.25 | V             |

|                                    |                                                                                         | After trim is loaded                                                                                                                                      | -3   |      | +3   | %             |

| $\Delta V_{\text{REG12TEMP}}$      | Regulator output change with temperature ( $\Delta V_{\text{REG12}}/V_{\text{REG12}}$ ) | $I_{\text{REG12}} = 1 \text{ mA}$                                                                                                                         | -1   |      | 1    | %             |

| $\Delta V_{\text{REG12LINE}}$      | Line regulation ( $\Delta V_{\text{REG12}}/\Delta V_{\text{BAT}}$ )                     | $I_{\text{REG12}} = 10 \text{ mA}$<br>$V_{\text{BAT}} = 2$ to $5\text{V}$                                                                                 | -1   |      | 1    | %             |

| $\Delta V_{\text{REG12LOAD}}$      | Load regulation ( $\Delta V_{\text{REG12}}/\Delta I_{\text{REG12}}$ )                   | $I_{\text{REG12}} = 0$ to $10 \text{ mA}$                                                                                                                 | -1   |      | 1    | %             |

| $\Delta V_{\text{TRANSIENT}}$      | Transient response load step                                                            | $I_{\text{REG12}} = 0$ to $10 \text{ mA}$                                                                                                                 | -55  |      | 45   | mV            |

| $I_{\text{REG12\_SHORT}}$          | Short Circuit Current Limit                                                             | $V_{\text{REG12}} = 0 \text{ V}$                                                                                                                          | 12   | 20   | 35   | mA            |

| $\text{PSRR}_{\text{REG12}}^{(2)}$ | Power Supply Rejection Ratio ( $\Delta V_{\text{BAT}}/\Delta V_{\text{REG12}}$ )        | $I_{\text{REG12}} = 10 \text{ mA}$ , $V_{\text{BAT}} > 2.5 \text{ V}$ , $f = 1 \text{ Hz}$ to $20 \text{ kHz}$ , $\text{VIN Ripple} = \pm 100 \text{ mV}$ | 30   | 50   | 130  | dB            |

| $V_{\text{REG12TH+}}$              | REG12 Good Threshold Rising                                                             | $\text{POR} = V_{\text{REG12TH-+}} V_{\text{REG12HYS}}$                                                                                                   |      | 1.03 |      | V             |

| $V_{\text{REG12TH-}}$              | REG12 Good Threshold Falling                                                            |                                                                                                                                                           | 0.95 | 1    | 1.05 | V             |

| $V_{\text{REG12HYS}}$              | REG12 Good Hysteresis                                                                   |                                                                                                                                                           | 10   | 30   | 50   | mV            |

| $I_{\text{REG12}}$                 | Current Consumption                                                                     | $I_{\text{REG12}} = 0 \text{ mA}$                                                                                                                         |      | 3.5  |      | $\mu\text{A}$ |

(1) If ( $\text{BAT} > 2\text{V}$ ),  $\text{VIN} = \text{BAT}$ , else  $\text{VIN} = \text{PACK}$

(2) Specified by design. Not production tested.

## 2.9 Under Voltage Lock Out (UVLO)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER             |                                                     | TEST CONDITIONS                                                  | MIN | TYP  | MAX | UNITS         |

|-----------------------|-----------------------------------------------------|------------------------------------------------------------------|-----|------|-----|---------------|

| $V_{\text{UVLOTHR+}}$ | UVLO Detection Voltage Rising Threshold             | $V_{\text{BAT}}$ or $V_{\text{PACK+}}$                           | 2.1 | 2.35 | 2.6 | V             |

| $V_{\text{UVLOTHR-}}$ | UVLO Detection Voltage Falling Threshold, Post Trim | $V_{\text{BAT}}$ or $V_{\text{PACK+}}$<br>$\text{SCOMP\_EN} = 1$ | 2.0 | 2.05 | 2.1 | V             |

| $I_{\text{UVLO}}$     | Current Consumption                                 |                                                                  |     | 2    |     | $\mu\text{A}$ |

## 2.10 Pack Overvoltage Protection (OVP)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER            |                                        | TEST CONDITIONS                          | MIN  | TYP | MAX  | UNITS         |

|----------------------|----------------------------------------|------------------------------------------|------|-----|------|---------------|

| $V_{\text{OVP\_TH}}$ | OVP Detection Voltage Rising Threshold | With respect to $V_{\text{PACK\_SENSE}}$ | 4.95 | 5.0 | 5.05 | V             |

| $t_{\text{OVP}}$     | OVP Detection Time                     | $\text{XYZ\_FAST\_EN} = 3\text{b}100$    |      | 180 | 250  | $\mu\text{s}$ |

| $I_{\text{OVP}}$     | Current Consumption                    |                                          |      | 3   |      | $\mu\text{A}$ |

## 2.11 Fast Reaction Current Safety Discharge (DSG\_SFTY)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER                |                                                  | TEST CONDITIONS                                           | MIN  | TYP | MAX   | UNITS         |

|--------------------------|--------------------------------------------------|-----------------------------------------------------------|------|-----|-------|---------------|

| $V_{OCD\_TH1}$           | DSG_SFTY 1 Detection Voltage Threshold           | $V_{ISENSE+} - V_{ISENSE-}$ ,<br>DSG_SFTY_LVL1 = 1 to 127 | -0.5 |     | -62.5 | mV            |

| $V_{OCD\_TH1ST}$         | DSG_SFTY 1 Detection Voltage Threshold step size |                                                           | 250  | 500 | 750   | $\mu\text{V}$ |

| $V_{OCD\_TH2}$           | DSG_SFTY 2 Detection Voltage Threshold           | $V_{ISENSE+} - V_{ISENSE-}$ ,<br>DSG_SFTY_LVL2 = 1 to 127 | -0.5 |     | -62.5 | mV            |

| $V_{OCD\_TH2ST}$         | DSG_SFTY 2 Detection Voltage Threshold step size |                                                           | 250  | 500 | 750   | $\mu\text{V}$ |

| $V_{OCD\_TH3}$           | DSG_SFTY 3 Detection Voltage Threshold           | $V_{ISENSE+} - V_{ISENSE-}$ ,<br>DSG_SFTY_LVL3 = 1 to 127 | -0.5 |     | -62.5 | mV            |

| $V_{OCD\_TH3ST}$         | DSG_SFTY 3 Detection Voltage Threshold step size |                                                           | 250  | 500 | 750   | $\mu\text{V}$ |

| $V_{OCD\_TH4}$           | DSG_SFTY 4 Detection Voltage Threshold           | $V_{ISENSE+} - V_{ISENSE-}$ ,<br>DSG_SFTY_LVL4 = 1 to 127 | -0.5 |     | -62.5 | mV            |

| $V_{OCD\_TH4ST}$         | DSG_SFTY 4 Detection Voltage Threshold step size |                                                           | 250  | 500 | 750   | $\mu\text{V}$ |

| $V_{OCD\_SCALEERR}$      | DSG_SFTY Detection Scale Error                   |                                                           |      | 5   |       | %             |

| $I_{OCD}$                | Current Consumption                              |                                                           |      | 1   |       | $\mu\text{A}$ |

| $t_{OCD\_DLY1}$          | DSG Safety Time1                                 | DSG_SFTY_TIME1 = 0 to 255                                 | 61   |     | 15600 | $\mu\text{s}$ |

| $t_{OCD\_DLY1\_ACC}$     | DSG Safety Time1 Accuracy                        | DSG_SFTY_TIME1 = 0 to 255                                 | -15  |     | 15    | $\mu\text{s}$ |

| $t_{OCD\_DLY2}$          | DSG Safety Time2                                 | DSG_SFTY_TIME2 = 0 to 255                                 | 0.98 |     | 250   | ms            |

| $t_{OCD\_DLY3}$          | DSG Safety Time3                                 | DSG_SFTY_TIME3 = 0 to 255                                 | 15.6 |     | 4000  | ms            |

| $t_{OCD\_DLY4}$          | DSG Safety Time4                                 | DSG_SFTY_TIME4 = 0 to 255                                 | 15.6 |     | 4000  | ms            |

| $t_{OCD\_DLY2,3,4\_ACC}$ | DSG Safety Time2,3,4 Accuracy                    | DSG_SFTY_TIME2,3,4 = 0 to 255                             | -100 |     | 100   | $\mu\text{s}$ |

## 2.12 Fast Reaction Current Safety Charge (CHG\_SFTY)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER           |                                                | TEST CONDITIONS                                          | MIN  | TYP | MAX  | UNITS         |

|---------------------|------------------------------------------------|----------------------------------------------------------|------|-----|------|---------------|

| $V_{OCC\_TH}$       | CHG_SFTY Detection Voltage Threshold           | $V_{ISENSE-} - V_{ISENSE+}$ ,<br>CHG_SFTY_LVL = 1 to 127 | 62.5 |     | 0.5  | mV            |

| $V_{OCC\_THST}$     | CHG_SFTY Detection Voltage Threshold step size |                                                          | 250  | 500 | 750  | $\mu\text{V}$ |

| $V_{OCC\_SCALEERR}$ | CHG_SFTY Detection Scale Error                 |                                                          |      | 5   |      | %             |

| $I_{OCC}$           | Current Consumption                            |                                                          |      | 1   |      | $\mu\text{A}$ |

| $t_{OCC\_DLY}$      | CHG Safety Time                                | CHG_SFTY_TIME = 0 to 255                                 | 15.6 |     | 4000 | ms            |

| $t_{OCC\_DLY\_ACC}$ | CHG Safety Time Accuracy                       | CHG_SFTY_TIME = 0 to 255                                 | -100 |     | 100  | $\mu\text{s}$ |

## 2.13 PTAT Good Comparator (PTATDET)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER       |                      | TEST CONDITIONS | MIN | TYP | MAX | UNITS |

|-----------------|----------------------|-----------------|-----|-----|-----|-------|

| $T_{PTAT\_TH}$  | PTAT Good Threshold  |                 | 110 | 120 | 130 | °C    |

| $T_{PTAT\_HYS}$ | PTAT Good Hysteresis |                 |     | 10  |     | °C    |

| $I_{PTAT}$      | Current Consumption  |                 |     | 0.8 |     | µA    |

## 2.14 Internal Temperature Sensor (INTTEMP)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER           |                                           | TEST CONDITIONS | MIN  | TYP  | MAX  | UNITS |

|---------------------|-------------------------------------------|-----------------|------|------|------|-------|

| $V_{INTTEMP}^{(1)}$ | Internal Temperature sensor voltage drift |                 | -1.5 | -1.9 | -2.3 | mV/°C |

| $V_{INTTEMP\_ERR}$  | Internal Temperature sensor Accuracy      |                 | -3   |      | +3   | °C    |

| $I_{INTTEMP}$       | Current Consumption                       |                 |      | 50   |      | µA    |

1) Data to calculate slope is stored in the device see section 7.1.4.14

## 2.15 Charger Detect (CD)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER      |                          | TEST CONDITIONS                                       | MIN   | TYP   | MAX   | UNITS                 |

|----------------|--------------------------|-------------------------------------------------------|-------|-------|-------|-----------------------|

| $V_{CD}$       | Charger Detect Threshold | $V_{PACK\_SENSE} - V_{BAT} \text{ CHGR\_DET\_EN} = 1$ | 1     |       | 50    | mV                    |

| $t_{debounce}$ | Charger Debounce Times   | CHGR_DET_DEBOUNCE = 0000                              | 2     | 2     | 3     | Clocks <sup>(1)</sup> |

|                |                          | CHGR_DET_DEBOUNCE = 0001                              | 4     | 4     | 5     |                       |

|                |                          | CHGR_DET_DEBOUNCE = 0010                              | 8     | 8     | 9     |                       |

|                |                          | CHGR_DET_DEBOUNCE = 0011                              | 16    | 16    | 17    |                       |

|                |                          | CHGR_DET_DEBOUNCE = 0100                              | 32    | 32    | 33    |                       |

|                |                          | CHGR_DET_DEBOUNCE = 0101                              | 64    | 64    | 65    |                       |

|                |                          | CHGR_DET_DEBOUNCE = 0110                              | 128   | 128   | 129   |                       |

|                |                          | CHGR_DET_DEBOUNCE = 0111                              | 256   | 256   | 257   |                       |

|                |                          | CHGR_DET_DEBOUNCE = 1000                              | 512   | 512   | 513   |                       |

|                |                          | CHGR_DET_DEBOUNCE = 1001                              | 1024  | 1024  | 1025  |                       |

|                |                          | CHGR_DET_DEBOUNCE = 1010                              | 2048  | 2048  | 2049  |                       |

|                |                          | CHGR_DET_DEBOUNCE = 1011                              | 4096  | 4096  | 4097  |                       |

|                |                          | CHGR_DET_DEBOUNCE = 1100                              | 8192  | 8192  | 8193  |                       |

|                |                          | CHGR_DET_DEBOUNCE = 1101                              | 16384 | 16384 | 16385 |                       |

|                |                          | CHGR_DET_DEBOUNCE = 1110                              | 32768 | 32768 | 32769 |                       |

|                |                          | CHGR_DET_DEBOUNCE = 1111                              | 65536 | 65536 | 65537 |                       |

| $I_{CD}$       | Current Consumption      | CHGR_DET_EN = 1                                       |       | 1     |       | µA                    |

(1) Clocks are those of the internal 32768 Hz clock derived from the Low Frequency Oscillator (LFO)

## 2.16 Protected Battery Output (BAT\_PROT)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER     |                                      | TEST CONDITIONS                                   | MIN | TYP | MAX  | UNITS         |

|---------------|--------------------------------------|---------------------------------------------------|-----|-----|------|---------------|

| $V_{PBOVIN}$  | Input Voltage Range                  | BAT_PROT_EN = 1                                   | 2.0 |     | 5    | V             |

| $R_{PBORon}$  | Resistance On                        | BAT_PROT_EN = 1                                   |     |     | 5000 | $\Omega$      |

| $I_{PBOIOUT}$ | Output Current Drive Capability      | BAT_PROT_EN = 1                                   |     |     | 100  | $\mu\text{A}$ |

| $I_{REVERSE}$ | Reverse Current from BAT_PROT to BAT | BAT_PROT_EN = 1                                   |     | -20 |      | $\mu\text{A}$ |

|               |                                      | BAT_PROT_EN = 0                                   |     | -1  |      | $\mu\text{A}$ |

| $t_{FLT_DET}$ | Fault detection time                 | BAT_PROT_EN = 1, $C_{BAT\_PROT} \leq 10\text{nF}$ |     |     | 200  | $\mu\text{s}$ |

| $I_{PBO}$     | Current Consumption                  | BAT_PROT_EN = 1                                   |     | 0.6 |      | $\mu\text{A}$ |

## 2.17 Secondary Wakeup (SEC\_WAKE)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER       |                                     | TEST CONDITIONS      | MIN | TYP | MAX | UNITS    |

|-----------------|-------------------------------------|----------------------|-----|-----|-----|----------|

| $R_{SEC\_WAKE}$ | Secondary Wake up Series Resistance | SCNDRY_WAKE_DATA = 1 | 400 | 550 | 800 | $\Omega$ |

| $t_{SEC\_WAKE}$ | Secondary Wake up Connection Time   |                      | 4.5 | 5   | 5.5 | ms       |

## 2.18 Pack Clamp (PACK\_CLAMP)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER                              |                                                  | TEST CONDITIONS                                                                             | MIN | TYP | MAX  | UNITS         |

|----------------------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------------|-----|-----|------|---------------|

| $V_{PACK\_CLAMP}$                      | Rising voltage on Pack when clamp is active      | $I_{PACK\_CLAMP} < 1\text{mA}$                                                              | 5.3 |     |      | V             |

|                                        |                                                  | $I_{PACK\_CLAMP} < 150\text{mA}$                                                            | 5.3 |     |      | V             |

| $P_{PACK\_CLAMP}$ <sup>(1) (2)</sup>   | Pack Clamp Power Dissipation                     | $V_{PACK} = V_{PACK\_SENSE} \leq V_{PACK\_CLAMP(MAX)}$                                      |     |     | 0.5  | W             |

|                                        |                                                  | $V_{PACK} = V_{PACK\_SENSE} \leq V_{PACK\_CLAMP(MAX)}, t = 10\text{ ms}$                    |     |     | 0.75 | W             |

| $I_{PACK\_CLAMP\_PEAK}$ <sup>(1)</sup> | Peak current consumption when clamp fully active | For a time $< 1\text{ms}$                                                                   |     |     | 150  | mA            |

| $I_{PACK\_CLAMP\_ON}$                  | Current consumption when clamp fully active      |                                                                                             |     |     | 100  | mA            |

| $t_{PACK\_CLAMP}$ <sup>(1)</sup>       | Clamp activation slew rate                       | $V_{PACK} = V_{PACK\_SENSE} \leq V_{PACK\_CLAMP(MAX)}$<br>$C_{PACK} = 1\text{ }\mu\text{F}$ | 50  | 100 |      | ns/V          |

| $I_{PACK\_CLAMP\_OFF}$                 | Current Consumption                              | Not Clamping                                                                                |     | 0.1 |      | $\mu\text{A}$ |

(1) Specified by design. Not production tested

(2) Simulated on a JEDEC-standard, high-K board, as specified in JESD51-7, in an environment described in JESD51-2a.

## 2.19 High Frequency Oscillator (HFO)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER                     |                                | TEST CONDITIONS                                                                                        | MIN   | TYP   | MAX  | UNITS         |

|-------------------------------|--------------------------------|--------------------------------------------------------------------------------------------------------|-------|-------|------|---------------|

| $F_{\text{Hosc}}$             | Operating Frequency            | After system calibration                                                                               | 48    | 50.33 | 51.5 | MHz           |

| $F_{\text{HOSCD}}^{(2)}$      | Frequency Drift <sup>(1)</sup> | After system calibration<br>$-25^\circ\text{C}$ to $65^\circ\text{C}$                                  | -1.5% |       | 2.5% |               |

|                               |                                | After system calibration<br>$-20^\circ\text{C}$ to $55^\circ\text{C}$<br>$\text{FLL\_TIGHT\_LOCK} = 1$ | -1%   |       | 1%   |               |

| $t_{\text{HFO\_START}}^{(2)}$ | HFO Start Up time              | Oscillator frequency within $\pm 3\%$ of nominal                                                       |       |       | 10   | $\mu\text{s}$ |

| $I_{\text{Hosc}}$             | Current Consumption            |                                                                                                        |       | 24    |      | $\mu\text{A}$ |

(1) The frequency drift is included and measured from the trimmed frequency at  $T_A = 25^\circ\text{C}$

(2) Specified by design. Not production tested

## 2.20 Low Frequency Oscillator (LFO)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -40^\circ\text{C}$  to  $85^\circ\text{C}$  unless otherwise noted.

| PARAMETER                     |                                  | TEST CONDITIONS                                                      | MIN    | TYP     | MAX   | UNITS         |

|-------------------------------|----------------------------------|----------------------------------------------------------------------|--------|---------|-------|---------------|

| $F_{\text{Losc}}$             | Operating Frequency <sup>1</sup> |                                                                      | 260.18 | 262.144 | 264.1 | kHz           |

|                               | Trim Accuracy                    | $T_A = 25^\circ\text{C}$                                             | -0.1%  |         | 0.1%  |               |

| $F_{\text{LOS_CD}}$           | Frequency Drift <sup>2</sup>     | $-25^\circ\text{C}$ to $65^\circ\text{C}$ (after system calibration) | -0.4%  |         | 0.4%  |               |

| $t_{\text{LFO\_START}}^{(3)}$ | LFO Start Up time                | Oscillator frequency within $\pm 3\%$ of nominal                     |        |         | 80    | $\mu\text{s}$ |

| $F_{\text{LFO\_WD}}^{(3)}$    | LFO Watchdog Fault Frequency     |                                                                      | 116    | 212     | 238   | kHz           |

| $I_{\text{Losc}}$             | Current Consumption              |                                                                      |        | 2.5     |       | $\mu\text{A}$ |

(1) The raw LFO frequency will be divided to generate all the clocks for internal modules

(2) The frequency drift is included and measured from the trimmed frequency at  $T_A = 25^\circ\text{C}$

(3) Specified by design. Not production tested

## 2.21 Continuous Current ADC (CC\_ADC)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -25^\circ\text{C}$  to  $65^\circ\text{C}$  unless otherwise noted.

| PARAMETER                           |                                               | TEST CONDITIONS                                                                                                  | MIN   | TYP       | MAX      | UNITS                  |

|-------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------|-----------|----------|------------------------|

| CC <sub>VIN</sub>                   | Input Voltage Range                           | $V_{\text{ISENSE+}} - V_{\text{ISENSE-}}$                                                                        | -62.5 |           | 62.5     | mV                     |

| CC <sub>C MODE</sub> <sup>(3)</sup> | Input Common Mode Range                       | $V_{\text{ISENSE-}} - \text{GND}$                                                                                | 0     |           | 5        | V                      |

| CC <sub>ER</sub>                    | Effective Resolution <sup>(1)(3)</sup>        | Post system calibration, CC_CAL_MUX = 2b00                                                                       | 18    |           |          | bits                   |

|                                     |                                               | Pre system calibration, CC_CAL_MUX = 2b00                                                                        | 16    |           |          | bits                   |

|                                     |                                               | Post system calibration, CC_CAL_MUX = 2b01 or 2b10                                                               | 16.5  |           |          | bits                   |

|                                     |                                               | Pre system calibration, CC_CAL_MUX = 2b01 or 2b10                                                                | 14.5  |           |          | bits                   |

| CC <sub>INL</sub>                   | Integral Non Linearity <sup>(2)(3)</sup>      |                                                                                                                  |       |           | $\pm 20$ | LSB                    |

| CC <sub>VOSER</sub>                 | Offset Error                                  | Post system calibration, CC_CAL_MUX = 2b00                                                                       |       | $\pm 2$   |          | LSB                    |

|                                     |                                               | Pre system calibration, CC_CAL_MUX = 2b00                                                                        |       | $\pm 3$   |          | LSB                    |

|                                     |                                               | Post system calibration, CC_CAL_MUX = 2b01 or 2b10                                                               |       | $\pm 3.5$ |          | LSB                    |

|                                     |                                               | Pre system calibration, CC_CAL_MUX = 2b01 or 2b10                                                                |       | $\pm 4.5$ |          | LSB                    |

| CC <sub>VOS_DR</sub>                | Offset Error Drift <sup>(3)</sup>             | $T_A = -25$ to $65^\circ\text{C}$ , post system calibration                                                      |       | $\pm 5$   |          | LSB                    |

|                                     |                                               | $T_A = -25$ to $65^\circ\text{C}$ , Pre system calibration                                                       |       | $\pm 6$   |          | LSB                    |

| CC <sub>VOS</sub>                   | Offset Error across full scale <sup>(3)</sup> | Post system calibration, CC_CAL_MUX = 2b00                                                                       |       | 0.0016    |          | %FSR                   |

|                                     |                                               | Pre system calibration, CC_CAL_MUX = 2b00                                                                        |       | 0.0023    |          | %FSR                   |

| CC <sub>NOISE</sub>                 | Noise Floor <sup>(2)(3)</sup>                 |                                                                                                                  |       | 700       |          | nV/ $\sqrt{\text{Hz}}$ |

| CC <sub>GAINER</sub>                | Gain Error <sup>(5)</sup>                     | $T_A = -25$ to $65^\circ\text{C}$ , $2\text{ V} \leq \text{VIN}^{(6)} \leq 5\text{ V}$ , Post system calibration |       | $\pm 16$  |          | LSB                    |

|                                     |                                               | $T_A = -25$ to $65^\circ\text{C}$ , $2\text{ V} \leq \text{VIN}^{(6)} \leq 5\text{ V}$ , Pre system calibration  |       | $\pm 18$  |          | LSB                    |

| CC <sub>GAINER_DR</sub>             | Gain Error Drift <sup>(3)(5)</sup>            | $T_A = -25$ to $65^\circ\text{C}$ , $2\text{ V} \leq \text{VIN}^{(6)} \leq 5\text{ V}$ , Post system calibration |       | 5         |          | LSB/ $^\circ\text{C}$  |

|                                     |                                               | $T_A = -25$ to $65^\circ\text{C}$ , $2\text{ V} \leq \text{VIN}^{(6)} \leq 5\text{ V}$ , Pre system calibration  |       | 6         |          | LSB/ $^\circ\text{C}$  |

| CC <sub>GAIN</sub>                  | Gain Error Across Full Scale <sup>(5)</sup>   | Post system calibration                                                                                          |       | 0.013     |          | %FSR                   |

|                                     |                                               | Pre system calibration                                                                                           |       | 0.014     |          | %FSR                   |

| CC <sub>DNL</sub>                   | Differential Non Linearity <sup>(3)(4)</sup>  | $T_A = -25$ to $65^\circ\text{C}$                                                                                | -1    |           | 1        | LSB                    |

| CC <sub>LKG</sub>                   | Input Leakage                                 |                                                                                                                  |       |           | 0.3      | $\mu\text{A}$          |

| I <sub>CC</sub>                     | Current Consumption <sup>(3)</sup>            |                                                                                                                  |       | 26.5      |          | $\mu\text{A}$          |

1. Input signal  $V_{\text{cell+}} = 4.35$ , DC =  $\pm 1\text{mV}$ , Harmonic Free Full Scale

2. First order curve fit from  $-FS$  to  $+FS$

3. Specified by design. Not production tested

4. Monotonic performance

5. Does not include CC Reference Gain Error

6. If (BAT > 2V), VIN = BAT, else VIN = PACK

## 2.22 High Frequency Current ADC (HF\_I\_ADC)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -25^\circ\text{C}$  to  $65^\circ\text{C}$  unless otherwise noted.

| PARAMETER                            |                                                                      | TEST CONDITIONS                                                        | MIN   | TYP   | MAX  | UNITS |

|--------------------------------------|----------------------------------------------------------------------|------------------------------------------------------------------------|-------|-------|------|-------|

| HFIADC <sub>IN</sub>                 | Input Voltage Range                                                  | $V_{HF\_ISENSE+} - V_{HF\_ISENSE-}$                                    | -62.5 |       | 62.5 | mV    |

| HFI <sub>C</sub> MODE <sup>(5)</sup> | Input Common Mode Range                                              | $V_{HF\_ISENSE-} - \text{GND}$                                         | 0     |       | 5    | V     |

| HFIADC <sub>RES256</sub>             | SNR and SFDR <sup>(1) (5)</sup><br>Sample Rate = 256 Hz              | Modulator Clock = 524.288 kHz<br>HF_FIR_SEL = 2b00                     | 15    |       |      | bits  |

| HFIADC <sub>RES1K</sub>              | SNR and SFDR <sup>(1) (5)</sup><br>Sample Rate = 1.024 kHz           | Modulator Clock = 2097.152 kHz<br>HF_FIR_SEL = 2b00                    |       | 15    |      | bits  |

| HFIADC <sub>RES2K</sub>              | SNR and SFDR <sup>(1) (5)</sup><br>Sample Rate = 2.048 kHz           | Modulator Clock = 4194.304 kHz<br>HF_FIR_SEL = 2b00                    |       | 15    |      | bits  |

| HFIADC <sub>RES4K</sub>              | SNR and SFDR <sup>(1) (5)</sup><br>Sample Rate = 4.096 kHz           | Modulator Clock = 8388.608 kHz<br>HF_FIR_SEL = 2b11                    |       | 14    |      | bits  |

| HFIADC <sub>RES8K</sub>              | SNR and SFDR <sup>(1) (5)</sup><br>Sample Rate = 8.192 kHz           | Modulator Clock = 8388.608 kHz<br>HF_FIR_SEL = 2b11                    |       | 14    |      | bits  |

| HFIADC <sub>RES16K</sub>             | SNR and SFDR <sup>(1) (5)</sup><br>Sample Rate = 16.384 kHz          | Modulator Clock = 8388.608 kHz<br>HF_FIR_SEL = 2b11                    |       | 13    |      | bits  |

| HFIADC <sub>RES32K</sub>             | SNR and SFDR <sup>(1) (5)</sup><br>Sample Rate = 32.768 kHz          | Modulator Clock = 8388.608 kHz<br>HF_FIR_SEL = 2b11                    |       | 13    |      | bits  |

| HFIADC <sub>RES64K</sub>             | SNR and SFDR <sup>(1) (5)</sup><br>Sample Rate = 65.535 kHz          | Modulator Clock = 8388.608 kHz<br>HF_FIR_SEL = 2b11                    | 12    |       |      | bits  |

| $t_{\text{hfriadcconv256}}$          | Conversion Time <sup>(5)</sup><br>Sample Rate = 256 Hz               | HF_FREQ = 3b000<br>HF_FIR_SEL = 2b00                                   |       | 3.90  |      | ms    |

| $t_{\text{hfriadcconv1K}}$           | Conversion Time <sup>(5)</sup><br>Sample Rate = 1.024 kHz            | HF_FREQ = 3b001<br>HF_FIR_SEL = 2b00                                   |       | 0.976 |      | ms    |

| $t_{\text{hfriadcconv2K}}$           | Conversion Time <sup>(5)</sup><br>Sample Rate = 2.048 kHz            | HF_FREQ = 3b010<br>HF_FIR_SEL = 2b00                                   |       | 0.488 |      | ms    |

| $t_{\text{hfriadcconv4K}}$           | Conversion Time <sup>(5)</sup><br>Sample Rate = 4.096 kHz            | HF_FREQ = 3b011<br>HF_FIR_SEL = 2b11                                   |       | 0.244 |      | ms    |

| $t_{\text{hfriadcconv8K}}$           | Conversion Time <sup>(5)</sup><br>Sample Rate = 8.192 kHz            | HF_FREQ = 3b100<br>HF_FIR_SEL = 2b11                                   |       | 122   |      | μs    |

| $t_{\text{hfriadcconv16K}}$          | Conversion Time <sup>(5)</sup><br>Sample Rate = 16.384 kHz           | HF_FREQ = 3b101<br>HF_FIR_SEL = 2b11                                   |       | 61    |      | μs    |

| $t_{\text{hfriadcconv32K}}$          | Conversion Time <sup>(5)</sup><br>Sample Rate = 32.768 kHz           | HF_FREQ = 3b110<br>HF_FIR_SEL = 2b11                                   |       | 31    |      | μs    |

| $t_{\text{hfriadcconv64K}}$          | Conversion Time <sup>(5)</sup><br>Sample Rate = 65.535 kHz           | HF_FREQ = 3b111<br>HF_FIR_SEL = 2b11                                   |       | 15    |      | μs    |

| HFIADC <sub>INL256</sub>             | Integral Non Linearity <sup>(2) (5)</sup><br>Sample Rate = 256 Hz    | HF_FREQ = 3b000,<br>Modulator Clock = 524.288 kHz<br>HF_FIR_SEL = 2b00 | -4    |       | +4   | LSB   |

| HFIADC <sub>INL1K</sub>              | Integral Non Linearity <sup>(2) (5)</sup><br>Sample Rate = 1.024 kHz | HF_FREQ = 3b001<br>Modulator Clock = 2097.152 kHz<br>HF_FIR_SEL = 2b00 | -4    |       | +4   | LSB   |

| HFIADC <sub>INL2K</sub>              | Integral Non Linearity <sup>(2) (5)</sup><br>Sample Rate = 2.048 kHz | HF_FREQ = 3b010<br>Modulator Clock = 4194.304 kHz<br>HF_FIR_SEL = 2b00 | -4    |       | +4   | LSB   |

| PARAMETER                   |                                                                       | TEST CONDITIONS                                                                                                                          | MIN | TYP  | MAX | UNITS  |

|-----------------------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| HFIADC <sub>INL4K</sub>     | Integral Non Linearity <sup>(2) (5)</sup><br>Sample Rate = 4.096 kHz  | HF_FREQ = 3b011<br>Modulator Clock= 8388.608 kHz<br>HF_FIR_SEL = 2b11                                                                    | -4  |      | +4  | LSB    |

| HFIADC <sub>INL8K</sub>     | Integral Non Linearity <sup>(2) (5)</sup><br>Sample Rate = 8.192 kHz  | HF_FREQ = 3b100<br>Modulator Clock= 8388.608 kHz<br>HF_FIR_SEL = 2b11                                                                    | -4  |      | +4  | LSB    |

| HFIADC <sub>INL16K</sub>    | Integral Non Linearity <sup>(2) (5)</sup><br>Sample Rate = 16.384 kHz | HF_FREQ = 3b101<br>Modulator Clock= 8388.608 kHz<br>HF_FIR_SEL = 2b11                                                                    | -4  |      | +4  | LSB    |

| HFIADC <sub>INL32K</sub>    | Integral Non Linearity <sup>(2) (5)</sup><br>Sample Rate = 32.768 kHz | HF_FREQ = 3b110<br>Modulator Clock= 8388.608 kHz<br>HF_FIR_SEL = 2b11                                                                    | -4  |      | +4  | LSB    |

| HFIADC <sub>INL64K</sub>    | Integral Non Linearity <sup>(2) (5)</sup><br>Sample Rate = 65.535 kHz | HF_FREQ = 3b111<br>Modulator Clock= 8388.608 kHz<br>HF_FIR_SEL = 2b11                                                                    | -4  |      | +4  | LSB    |

| HFIADC <sub>VOSER</sub>     | Offset Error <sup>(6)</sup>                                           | Sample Rate =256 Hz, Modulator Clock= 524.288 kHz, T <sub>A</sub> = -25 to 65°C, 2 V ≤ VIN <sup>(8)</sup> ≤ 5 V, Post system calibration |     | ±2   |     | LSB    |

|                             |                                                                       | Sample Rate =256 Hz, Modulator Clock= 524.288 kHz, T <sub>A</sub> = -25 to 65°C, 2 V ≤ VIN <sup>(8)</sup> ≤ 5 V, Pre system calibration  |     | ±3   |     | LSB    |

| HFIADC <sub>VOSER_DR</sub>  | Offset Error Drift <sup>(5)</sup>                                     | T <sub>A</sub> = -25 to 65°C, 2 V ≤ VIN <sup>(7)</sup> ≤ 5 V, Post system calibration                                                    |     | ±5   |     | LSB    |

|                             |                                                                       | T <sub>A</sub> = -25 to 65°C, 2 V ≤ VIN <sup>(7)</sup> ≤ 5 V, Pre system calibration                                                     |     | ±6   |     | LSB    |

| HFIADC <sub>VOS</sub>       | Offset Error across full scale <sup>(5)</sup>                         | T <sub>A</sub> = -25 to 65°C, 2 V ≤ VIN <sup>(7)</sup> ≤ 5 V, Post system calibration                                                    |     | 0.03 |     | %FSR   |

|                             |                                                                       | T <sub>A</sub> = -25 to 65°C, 2 V ≤ VIN <sup>(7)</sup> ≤ 5 V, Pre system calibration                                                     |     | 0.04 |     | %FSR   |

| HFIADC <sub>NOISE</sub>     | Noise Floor <sup>(5)</sup>                                            | DC to Sample output rate /3                                                                                                              |     | 170  |     | nV/√Hz |

| HFIADC <sub>GAINER</sub>    | Gain Error <sup>(4)(5)</sup>                                          | T <sub>A</sub> = -25 to 65°C, 2 V ≤ VIN <sup>(7)</sup> ≤ 5 V, Post system calibration                                                    |     | ±16  |     | LSB    |

|                             |                                                                       | T <sub>A</sub> = -25 to 65°C, 2 V ≤ VIN <sup>(7)</sup> ≤ 5 V, Pre system calibration                                                     |     | ±18  |     | LSB    |

| HFIADC <sub>GAINER_DR</sub> | Gain Error Drift <sup>(4) (5)</sup>                                   | T <sub>A</sub> = -25 to 65°C, 2 V ≤ VIN <sup>(7)</sup> ≤ 5 V ,Post system calibration                                                    |     | 5    |     | LSB/°C |

|                             |                                                                       | T <sub>A</sub> = -25 to 65°C, 2 V ≤ VIN <sup>(7)</sup> ≤ 5 V, Pre system calibration                                                     |     | 7    |     | LSB/°C |

| HFIADC <sub>GAIN</sub>      | Gain Error across Full Scale Range <sup>(4) (5)</sup>                 | T <sub>A</sub> = -25 to 65°C, 2 V ≤ VIN <sup>(7)</sup> ≤ 5 V, With in system calibration                                                 |     | 0.25 |     | %FSR   |

|                             |                                                                       | T <sub>A</sub> = -25 to 65°C, 2 V ≤ VIN <sup>(7)</sup> ≤ 5 V, Pre system calibration                                                     |     | 0.5  |     | %FSR   |

| HFIADC <sub>DNL</sub>       | Differential Non Linearity <sup>(3) (5)</sup>                         | HF_FREQ = 3b000                                                                                                                          | -1  |      | +1  | LSB    |

| HFIADC <sub>ICC1</sub>      | Current Consumption <sup>(5)</sup>                                    | Sample Rate = 256 Hz,<br>Modulator Clock= 524.288 kHz<br>HF_FIR_SEL = 2b00                                                               |     | 157  |     | µA     |

| HFIADC <sub>ICC2</sub>      |                                                                       | Sample Rate= 1024 Hz,<br>Modulator Clock= 2097.152 kHz<br>HF_FIR_SEL = 2b00                                                              |     | 371  |     | µA     |

| PARAMETER              |  | TEST CONDITIONS                                                             | MIN | TYP  | MAX | UNITS |

|------------------------|--|-----------------------------------------------------------------------------|-----|------|-----|-------|

| HFIADC <sub>ICC3</sub> |  | Sample Rate= 2048 Hz,<br>Modulator Clock= 4194.304 kHz<br>HF_FIR_SEL = 2b00 |     | 721  |     | µA    |

| HFIADC <sub>ICC4</sub> |  | Sample Rate= 4096 Hz<br>Modulator Clock= 8388.608 kHz<br>HF_FIR_SEL = 2b11  |     | 1421 |     | µA    |

| HFIADC <sub>ICC5</sub> |  | Sample Rate= 8192 Hz, Modulator Clock= 8388.608 kHz<br>HF_FIR_SEL = 2b11    |     | 1421 |     | µA    |

| HFIADC <sub>ICC6</sub> |  | Sample Rate= 16384 Hz, Modulator Clock= 8388.608 kHz<br>HF_FIR_SEL = 2b11   |     | 1421 |     | µA    |

| HFIADC <sub>ICC7</sub> |  | Sample Rate= 32768 Hz, Modulator Clock= 8388.608 kHz<br>HF_FIR_SEL = 2b11   |     | 1421 |     | µA    |

| HFIADC <sub>ICC8</sub> |  | Sample Rate= 65536 Hz, Modulator Clock= 8388.608 kHz<br>HF_FIR_SEL = 2b11   |     | 1421 |     | µA    |

1) Input signal V<sub>cell+</sub> = 4.35, AC =±1mV, f = Sample Rate /4, Harmonic Free Full Scale

2) First order curve fit from -FS to + FS

3) Monotonic Performance

4) Does not include HF Reference Gain Error

5) Specified by design. Not production tested

6) Offset error is the standard deviation of the measured offset

7) If (BAT &gt; 2V), VIN = BAT, else VIN = PACK

## 2.23 High Frequency Voltage/Temp ADC (HF\_VT\_ADC)

Typical values stated where  $T_A = 25^\circ\text{C}$ , Min/Max values stated where  $T_A = -25^\circ\text{C}$  to  $65^\circ\text{C}$  unless otherwise noted.

| PARAMETER                   |                                                                 | TEST CONDITIONS                                     | MIN | TYP   | MAX | UNITS |

|-----------------------------|-----------------------------------------------------------------|-----------------------------------------------------|-----|-------|-----|-------|

| HFVTADC <sub>IN</sub>       | V <sub>CELL</sub> Range                                         | SAMPn_SEL = 4b0001                                  | 0   |       | 5   | V     |

|                             | V <sub>PACK_SENSE</sub> Range                                   | SAMPn_SEL = 4b0011                                  | 0   |       | 5   | V     |

|                             | V <sub>INTTEMP</sub> Range                                      | SAMPn_SEL = 4b0100                                  | 0   |       | 1.2 | V     |

|                             | V <sub>GPIO4</sub> Range                                        | SAMPn_SEL = 4b0101                                  | 0   |       | 1.8 | V     |

|                             | V <sub>NTC</sub> Range                                          | SAMPn_SEL = 4b0110 or 4b0111                        | 0   |       | 1.8 | V     |

|                             | V <sub>VDD_1P2</sub> Range                                      | SAMPn_SEL = 4b1000                                  | 0   |       | 1.8 | V     |

|                             | V <sub>VDD_1P8</sub> Range                                      | SAMPn_SEL = 4b1001                                  | 0   |       | 1.8 | V     |

|                             | V <sub>SCOMP</sub> Range                                        | SAMPn_SEL = 4b1010                                  | 0   |       | 1.8 | V     |

|                             | V <sub>HF_VREF</sub> Range                                      | SAMPn_SEL = 4b1011                                  | 0   |       | 1.8 | V     |

|                             | V <sub>CC_REF</sub> Range                                       | SAMPn_SEL = 4b1100                                  | 0   |       | 1.8 | V     |