# C2000™ Piccolo™ Workshop

Workshop Guide and Lab Manual

F28xPmdw Revision 2.1 December 2010

### **Important Notice**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgment, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

Customers are responsible for their applications using TI components.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 2009 – 2010 Texas Instruments Incorporated

#### **Revision History**

September 2009 – Revision 1.0 May 2010 – Revision 2.0

December 2010 – Revision 2.1

#### **Mailing Address**

Texas Instruments Training Technical Organization 7839 Churchill Way M/S 3984 Dallas, Texas 75251-1903

## C2000™ Piccolo™ Workshop

#### **Introductions**

### **Introductions**

- ◆ Name

- **◆** Company

- ◆ Project Responsibilities

- ◆ DSP / Microcontroller Experience

- **♦ TI Processor Experience**

- Hardware / Software Assembly / C

- ◆ Interests

### C2000™ Piccolo™ Workshop Outline

### **C2000™** Piccolo™ Workshop Outline

- 1. Architecture Overview

- 2. Programming Development Environment Lab: Linker command file

- 3. Peripheral Register Header Files

- 4. Reset and Interrupts

- **5. System Initialization** *Lab: Watchdog and interrupts*

- **6. Analog-to-Digital Converter** *Lab: Build a data acquisition system*

- 7. Control Peripherals

Lab: Generate and graph a PWM waveform

- 8. Numerical Concepts and IQ Math

Lab: Low-pass filter the PWM waveform

- 9. Control Law Accelerator (CLA)

Lab: Use CLA to filter PWM waveform

- **10. System Design**Lab: Run the code from flash memory

- 11. Communications

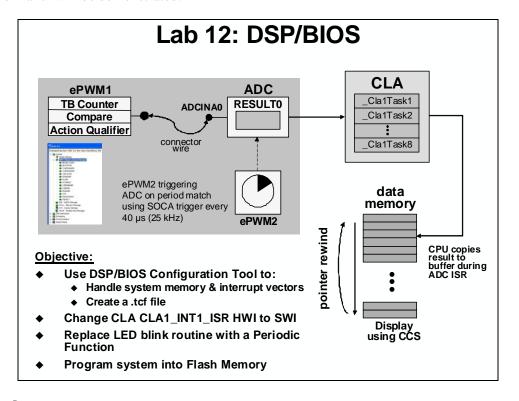

- 12. DSP/BIOS

Lab: Run DSP/BIOS code from flash memory

13. Support Resources

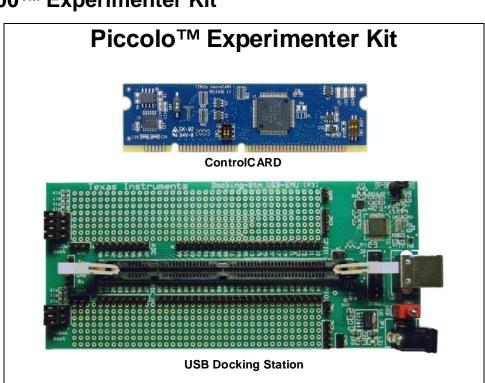

### C2000™ Experimenter Kit

### **Architecture Overview**

#### Introduction

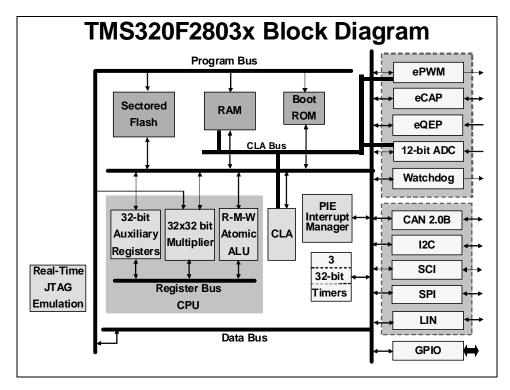

This architectural overview introduces the basic architecture of the C2000<sup>TM</sup> Piccolo<sup>TM</sup> series of microcontrollers from Texas Instruments. The Piccolo<sup>TM</sup> series adds a new level of general purpose processing ability unseen in any previous DSP/MCU chips. The C2000<sup>TM</sup> is ideal for applications combining digital signal processing, microcontroller processing, efficient C code execution, and operating system tasks.

Unless otherwise noted, the terms C28x, F28x and F2803x refer to TMS320F2803x devices throughout the remainder of these notes. For specific details and differences please refer to the device data sheet and user's guide.

### **Learning Objectives**

When this module is complete, you should have a basic understanding of the F28x architecture and how all of its components work together to create a high-end, uniprocessor control system.

### **Learning Objectives**

- Review the F28x block diagram and device features

- Describe the F28x bus structure and memory map

- ♦ Identify the various memory blocks on the F28x

- ♦ Identify the peripherals available on the F28x

# **Module Topics**

| Architecture Overview                                                              | 1-1  |

|------------------------------------------------------------------------------------|------|

| Module Topics                                                                      |      |

| What is the TMS320C2000 <sup>TM</sup> ? TMS320C2000 <sup>TM</sup> Internal Bussing |      |

| F28x CPUSpecial InstructionsPipeline Advantage                                     | 1-6  |

| Memory                                                                             |      |

| Fast Interrupt Response                                                            | 1-10 |

| F28x Mode                                                                          | 1-11 |

| Summary                                                                            | 1-12 |

#### What is the TMS320C2000 $^{TM}$ ?

The TMS320C2000™ is a 32-bit fixed point microcontroller that specializes in high performance control applications such as, robotics, industrial automation, mass storage devices, lighting, optical networking, power supplies, and other control applications needing a single processor to solve a high performance application.

The F2803x architecture can be divided into 3 functional blocks:

- CPU and busing

- Memory

- Peripherals

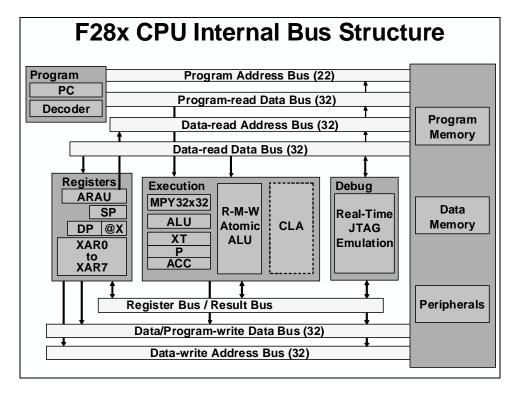

#### TMS320C2000™ Internal Bussing

As with many DSP-type devices, multiple busses are used to move data between the memories and peripherals and the CPU. The F28x memory bus architecture contains:

- A program read bus (22-bit address line and 32-bit data line)

- A data read bus (32-bit address line and 32-bit data line)

- A data write bus (32-bit address line and 32-bit data line)

The 32-bit-wide data busses enable single cycle 32-bit operations. This multiple bus architecture, known as a Harvard Bus Architecture enables the F28x to fetch an instruction, read a data value and write a data value in a single cycle. All peripherals and memories are attached to the memory bus and will prioritize memory accesses.

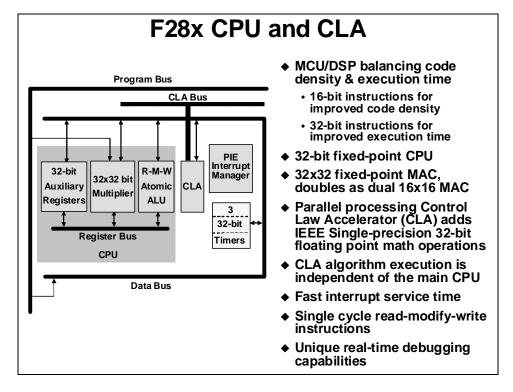

#### F28x CPU

The F28x is a highly integrated, high performance solution for demanding control applications. The F28x is a cross between a general purpose microcontroller and a digital signal processor, balancing the code density of a RISC processor and the execution speed of a DSP with the architecture, firmware, and development tools of a microcontroller.

The DSP features include a modified Harvard architecture and circular addressing. The RISC features are single-cycle instruction execution, register-to-register operations, and a modified Harvard architecture. The microcontroller features include ease of use through an intuitive instruction set, byte packing and unpacking, and bit manipulation.

The F28x design supports an efficient C engine with hardware that allows the C compiler to generate compact code. Multiple busses and an internal register bus allow an efficient and flexible way to operate on the data. The architecture is also supported by powerful addressing modes, which allow the compiler as well as the assembly programmer to generate compact code that is almost one to one corresponded to the C code.

The F28x is as efficient in DSP math tasks as it is in system control tasks. This efficiency removes the need for a second processor in many systems. The 32 x 32-bit MAC capabilities of the F28x and its 64-bit processing capabilities, enable the F28x to efficiently handle higher numerical resolution problems that would otherwise demand a more expensive solution. Along with this is the capability to perform two 16 x 16-bit multiply accumulate instructions simultaneously or Dual MACs (DMAC). Also, some devices feature a floating-point unit.

The, F28x is source code compatible with the 24x/240x devices and previously written code can be reassembled to run on a F28x device, allowing for migration of existing code onto the F28x.

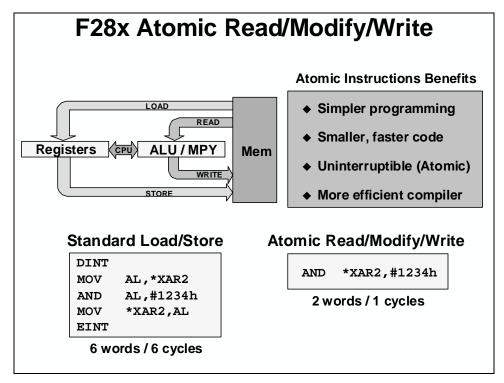

### **Special Instructions**

Atomics are small common instructions that are non-interuptable. The atomic ALU capability supports instructions and code that manages tasks and processes. These instructions usually execute several cycles faster than traditional coding.

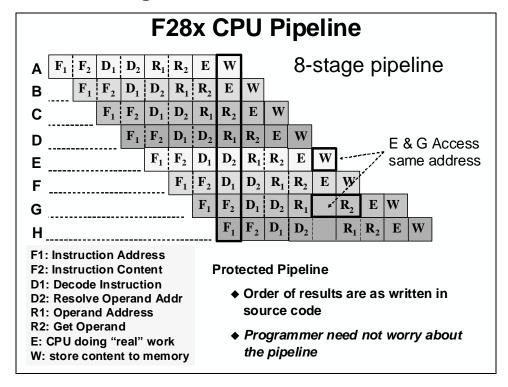

### **Pipeline Advantage**

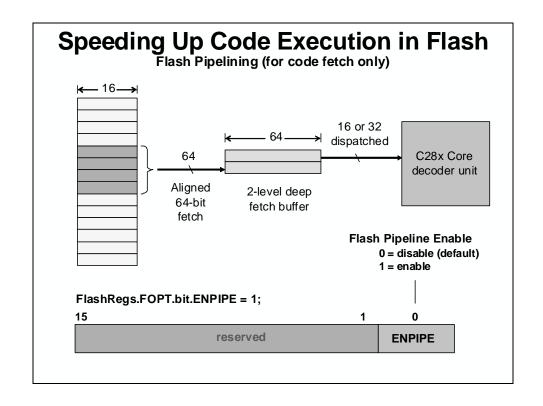

The F28x uses a special 8-stage protected pipeline to maximize the throughput. This protected pipeline prevents a write to and a read from the same location from occurring out of order.

This pipelining also enables the F28x to execute at high speeds without resorting to expensive high-speed memories. Special branch-look-ahead hardware minimizes the latency for conditional discontinuities. Special store conditional operations further improve performance.

### **Memory**

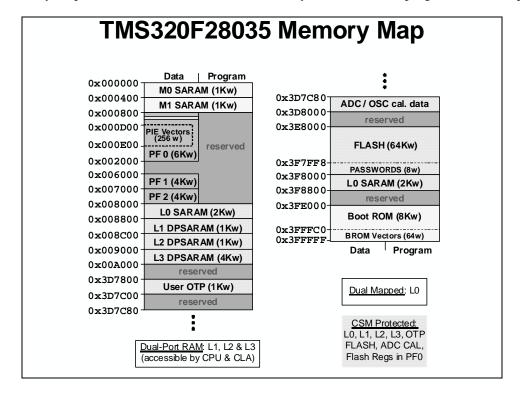

The memory space on the F28x is divided into program memory and data memory. There are several different types of memory available that can be used as both program memory and data memory. They include the flash memory, single access RAM (SARAM), OTP, and Boot ROM which is factory programmed with boot software routines or standard tables used in math related algorithms.

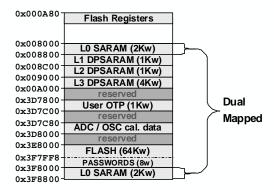

#### **Memory Map**

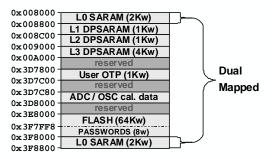

The F28x CPU contains no memory, but can access memory on chip. The F28x uses 32-bit data addresses and 22-bit program addresses. This allows for a total address reach of 4G words (1 word = 16-bits) in data memory and 4M words in program memory. Memory blocks on all F28x designs are uniformly mapped to both program and data space.

This memory map shows the different blocks of memory available to the program and data space.

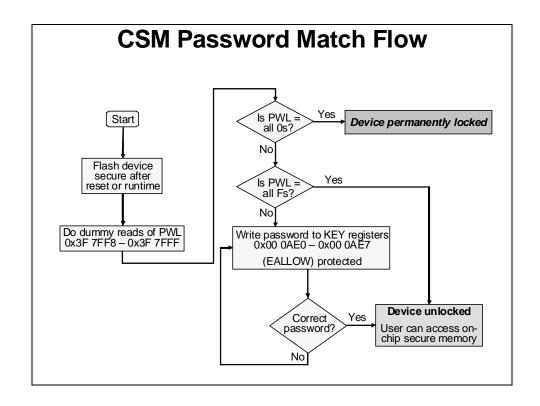

### **Code Security Module (CSM)**

## **Code Security Module**

Prevents reverse engineering and protects valuable intellectual property

- ◆ 128-bit user defined password is stored in Flash

- ♦ 128-bits = 2<sup>128</sup> = 3.4 x 10<sup>38</sup> possible passwords

- ◆ To try 1 password every 8 cycles at 60 MHz, it would take at least 1.4 x 10<sup>24</sup> years to try all possible combinations!

### **Peripherals**

The F28x comes with many built in peripherals optimized to support control applications. These peripherals vary depending on which F28x device you choose.

| • | ePWM | • | SPI |

|---|------|---|-----|

• CAP • SCI

• eQEP • I2C

Analog-to-Digital Converter

LIN

Watchdog Timer • CAN

CLA • GPIO

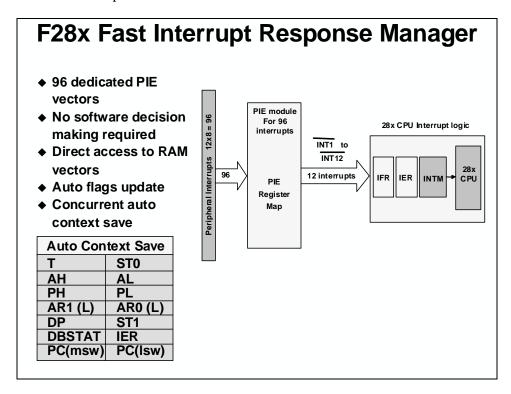

### **Fast Interrupt Response**

The fast interrupt response, with automatic context save of critical registers, resulting in a device that is capable of servicing many asynchronous events with minimal latency. F28x implements a zero cycle penalty to do 14 registers context saved and restored during an interrupt. This feature helps reduces the interrupt service routine overheads.

### F28x Mode

The F28x is one of several members of the TMS320 microcontroller family. The F28x is source code compatable with the 24x/240x devices and previously written code can be reassembled to run on a F28x device. This allows for migration of existing code onto the F28x.

## **F28x Operating Modes**

| Mode Type            | Mode Bits OBJMODE AMODE |   | Compiler Option |

|----------------------|-------------------------|---|-----------------|

| C28x Native Mode     | 1                       | 0 | -v28            |

| C24x Compatible Mode | 1                       | 1 | -v28 -m20       |

| Test Mode (default)  | 0                       | 0 |                 |

| Reserved             | 0                       | 1 |                 |

- ♦ Almost all users will run in C28x Native Mode

- ◆ The bootloader will automatically select C28x Native Mode after reset

- ◆ C24x compatible mode is mostly for backwards compatibility with an older processor family

### **Summary**

## **Summary**

- ♦ High performance 32-bit CPU

- ♦ 32x32 bit or dual 16x16 bit MAC

- **♦** Hardware Control Law Accelerator (CLA)

- **♦** Atomic read-modify-write instructions

- **♦** Fast interrupt response manager

- ♦ 64Kw on-chip flash memory

- ◆ Code security module (CSM)

- **♦** Control peripherals

- ♦ 12-bit ADC module

- **♦** Comparators

- ♦ Up to 44 shared GPIO pins

- **♦** Communications peripherals

## **Programming Development Environment**

#### Introduction

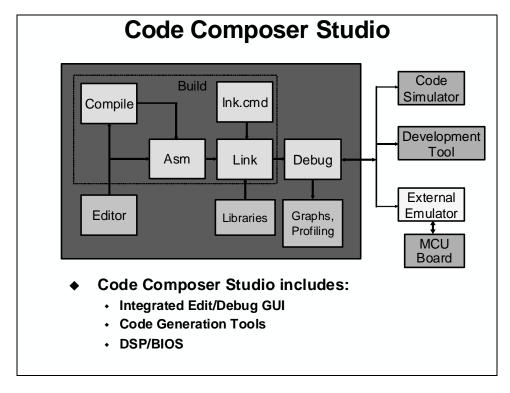

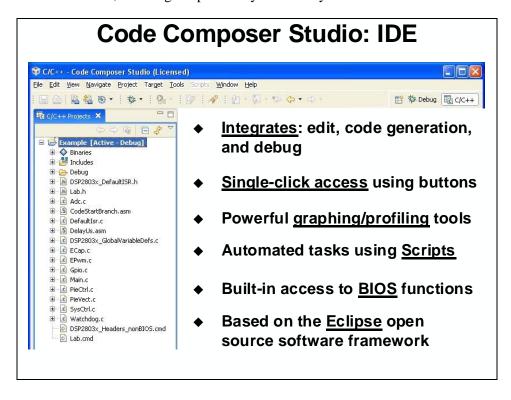

This module will explain how to use Code Composer Studio (CCS) integrated development environment (IDE) tools to develop a program. Creating projects and setting building options will be covered. Use and the purpose of the linker command file will be described.

### **Learning Objectives**

## **Learning Objectives**

- ◆ Use Code Composer Studio to:

- Create a Project

- · Set Build Options

- ♦ Create a *user* linker command file which:

- · Describes a system's available memory

- Indicates where sections will be placed in memory

# **Module Topics**

| Programming Development Environment     |      |

|-----------------------------------------|------|

| Module Topics                           | 2-2  |

| Code Composer Studio                    | 2-3  |

| Software Development and COFF Concepts  | 2-3  |

| C/C++ and Debug Perspective (CCSv4)     |      |

| CCSv4 Project                           |      |

| Creating a New CCSv4 Project            |      |

| CCSv4 Build Options – Compiler / Linker |      |

| Creating a Linker Command File          | 2-9  |

| Sections                                | 2-9  |

| Linker Command Files (.cmd)             |      |

| Memory-Map Description                  |      |

| Section Placement                       |      |

| Summary: Linker Command File            |      |

| Lab 2: Linker Command File              | 2-15 |

| Lab 2: Solution – lab2.cmd              | 2-22 |

## **Code Composer Studio**

#### **Software Development and COFF Concepts**

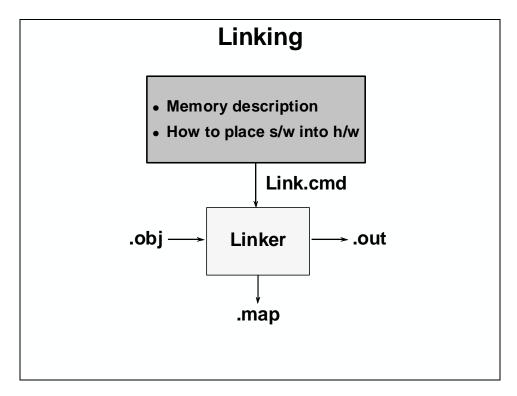

In an effort to standardize the software development process, TI uses the Common Object File Format (COFF). COFF has several features which make it a powerful software development system. It is most useful when the development task is split between several programmers.

Each file of code, called a *module*, may be written independently, including the specification of all resources necessary for the proper operation of the module. Modules can be written using Code Composer Studio (CCS) or any text editor capable of providing a simple ASCII file output. The expected extension of a source file is .ASM for *assembly* and .C for *C programs*.

Code Composer Studio includes a built-in editor, compiler, assembler, linker, and an automatic build process. Additionally, tools to connect file input and output, as well as built-in graph displays for output are available. Other features can be added using the plug-ins capability

Numerous modules are joined to form a complete program by using the *linker*. The linker efficiently allocates the resources available on the device to each module in the system. The linker uses a command (.CMD) file to identify the memory resources and placement of where the various sections within each module are to go. Outputs of the linking process includes the linked object file (.OUT), which runs on the device, and can include a .MAP file which identifies where each linked section is located.

The high level of modularity and portability resulting from this system simplifies the processes of verification, debug and maintenance. The process of COFF development is presented in greater detail in the following paragraphs.

The concept of COFF tools is to allow modular development of software independent of hardware concerns. An individual assembly language file is written to perform a single task and may be linked with several other tasks to achieve a more complex total system.

Writing code in modular form permits code to be developed by several people working in parallel so the development cycle is shortened. Debugging and upgrading code is faster, since components of the system, rather than the entire system, is being operated upon. Also, new systems may be developed more rapidly if previously developed modules can be used in them.

Code developed independently of hardware concerns increases the benefits of modularity by allowing the programmer to focus on the code and not waste time managing memory and moving code as other code components grow or shrink. A linker is invoked to allocate systems hardware to the modules desired to build a system. Changes in any or all modules, when re-linked, create a new hardware allocation, avoiding the possibility of memory resource conflicts.

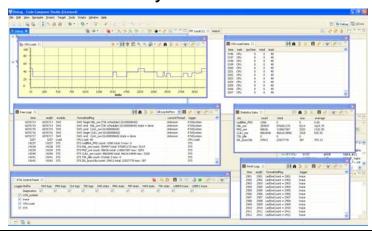

### C/C++ and Debug Perspective (CCSv4)

A perspective defines the initial layout views of the workbench windows, toolbars, and menus that are appropriate for a specific type of task, such as code development or debugging. This minimizes clutter to the user interface.

### C/C++ and Debug Perspective (CCSv4)

◆ Each perspective provides a set of functionality aimed at accomplishing a specific task

- ◆ C/C++ Perspective

- Displays views used during code development

- C/C++ project, editor, etc.

- ◆ Debug Perspective

- Displays views used for debugging

- Menus and toolbars associated with debugging, watch and memory windows, graphs, etc.

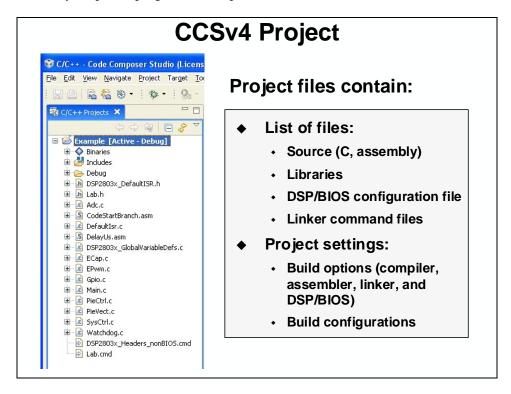

#### **CCSv4 Project**

Code Composer works with a *project* paradigm. Essentially, within CCS you create a project for each executable program you wish to create. Projects store all the information required to build the executable. For example, it lists things like: the source files, the header files, the target system's memory-map, and program build options.

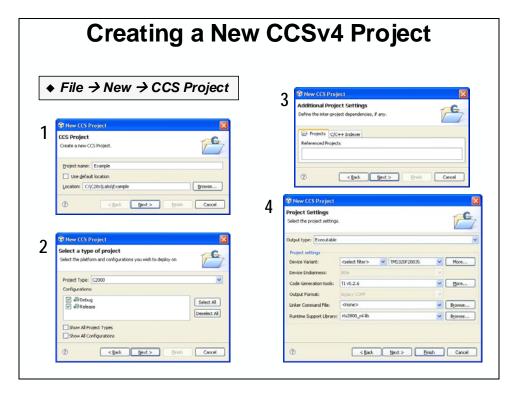

To create a new project, you need to select the following menu items:

File

$$\rightarrow$$

New  $\rightarrow$  CCS Project

Along with the main Project menu, you can also manage open projects using the right-click popup menu. Either of these menus allows you to modify a project, such as add files to a project, or open the properties of a project to set the build options.

### **Creating a New CCSv4 Project**

A graphical user interface (GUI) is used to assist in creating a new project. The four windows for the GUI are shown in the slide below.

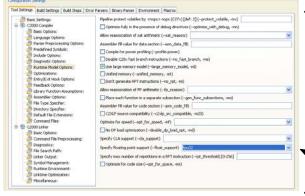

#### **CCSv4 Build Options – Compiler / Linker**

Project options direct the code generation tools (i.e. compiler, assembler, linker) to create code according to your system's needs. When you create a new project, CCS creates two sets of build options – called Configurations: one called *Debug*, the other *Release* (you might think of as Optimize).

To make it easier to choose build options, CCS provides a graphical user interface (GUI) for the various compiler and linker options. Here's a sample of the configuration options.

There is a one-to-one relationship between the items in the text box on the main page and the GUI check and drop-down box selections. Once you have mastered the various options, you can probably find yourself just typing in the options.

There are many linker options but these four handle all of the basic needs.

- -o <filename> specifies the output (executable) filename.

- -m <filename> creates a map file. This file reports the linker's results.

- -c tells the compiler to autoinitialize your global and static variables.

- -x tells the compiler to exhaustively read the libraries. Without this option libraries are searched only once, and therefore backwards references may not be resolved.

To help make sense of the many compiler options, TI provides two default sets of options (configurations) in each new project you create. The Release (optimized) configuration invokes the optimizer with -03 and disables source-level, symbolic debugging by omitting -g (which disables some optimizations to enable debug).

### **Creating a Linker Command File**

#### **Sections**

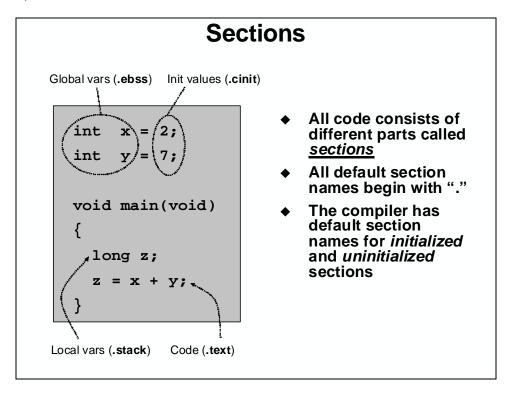

Looking at a C program, you'll notice it contains both code and different kinds of data (global, local, etc.).

In the TI code-generation tools (as with any toolset based on the COFF – Common Object File Format), these various parts of a program are called *Sections*. Breaking the program code and data into various sections provides flexibility since it allows you to place code sections in ROM and variables in RAM. The preceding diagram illustrated four sections:

- Global Variables

- Initial Values for global variables

- Local Variables (i.e. the stack)

- Code (the actual instructions)

Following is a list of the sections that are created by the compiler. Along with their description, we provide the Section Name defined by the compiler.

| Initialized Sections              |                                      |               |  |

|-----------------------------------|--------------------------------------|---------------|--|

| Name                              | Description Link Location            |               |  |

| .text                             | code                                 | FLASH         |  |

| .cinit                            | initialization values for            | FLASH         |  |

|                                   | global and static variables          |               |  |

| .econst                           | constants (e.g. const int k = 3;)    | FLASH         |  |

| .switch                           | tables for switch statements         | FLASH         |  |

| .pinit                            | tables for global constructors (C++) | FLASH         |  |

| Uninitialized Sections            |                                      |               |  |

| Name                              | Description                          | Link Location |  |

| .ebss global and static variables |                                      | RAM           |  |

| .stack space low 64Kw RA          |                                      | low 64Kw RAM  |  |

| .esysmem                          | memory for far malloc functions      | RAM           |  |

Sections of a C program must be located in different memories in your *target system*. This is the big advantage of creating the separate sections for code, constants, and variables. In this way, they can all be linked (located) into their proper memory locations in your target embedded system. Generally, they're located as follows:

#### Program Code (.text)

Program code consists of the sequence of instructions used to manipulate data, initialize system settings, etc. Program code must be defined upon system reset (power turn-on). Due to this basic system constraint it is usually necessary to place program code into non-volatile memory, such as FLASH or EPROM.

#### Constants (.cinit - initialized data)

Initialized data are those data memory locations defined at reset. It contains constants or initial values for variables. Similar to program code, constant data is expected to be valid upon reset of the system. It is often found in FLASH or EPROM (non-volatile memory).

#### Variables (.ebss – uninitialized data)

Uninitialized data memory locations can be changed and manipulated by the program code during runtime execution. Unlike program code or constants, uninitialized data or variables must reside in volatile memory, such as RAM. These memories can be modified and updated, supporting the way variables are used in math formulas, high-level languages, etc. Each variable must be declared with a directive to reserve memory to contain its value. By their nature, no value is assigned, instead they are loaded at runtime by the program.

Linking code is a three step process:

- 1. Defining the various regions of memory (on-chip SARAM vs. FLASH vs. External Memory).

- 2. Describing what sections go into which memory regions

- 3. Running the linker with "build" or "rebuild"

### Linker Command Files (.cmd)

The linker concatenates each section from all input files, allocating memory to each section based on its length and location as specified by the MEMORY and SECTIONS commands in the linker command file.

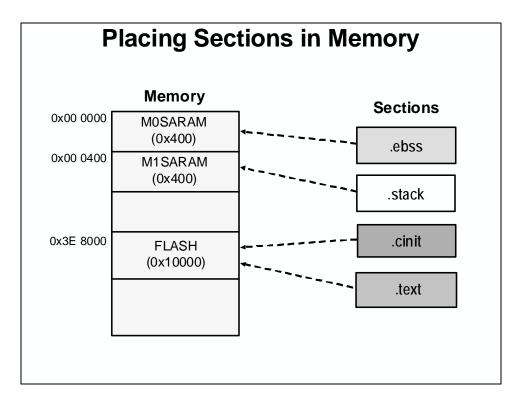

#### **Memory-Map Description**

The MEMORY section describes the memory configuration of the target system to the linker.

```

The format is: Name: origin = 0x????, length = 0x????

```

For example, if you placed a 64Kw FLASH starting at memory location 0x3E8000, it would read:

```

MEMORY

{

FLASH: origin = 0x3E8000 , length = 0x010000

}

```

Each memory segment is defined using the above format. If you added M0SARAM and M1SARAM, it would look like:

Remember that the DSP has two memory maps: *Program*, and *Data*. Therefore, the MEMORY description must describe each of these separately. The loader uses the following syntax to delineate each of these:

| Linker Page | TI Definition |

|-------------|---------------|

| Page 0      | Program       |

| Page 1      | Data          |

```

Linker Command File

MEMORY

/* Program Memory */

PAGE 0:

origin = 0x3E8000, length = 0x10000

FLASH:

/* Data Memory */

PAGE 1:

M0SARAM: origin = 0x000000, length = 0x400

M1SARAM: origin = 0x000400, length = 0x400

SECTIONS

.text:>

FLASH

PAGE = 0

.ebss:>

M0SARAM

PAGE = 1

.cinit:>

FLASH

PAGE = 0

.stack:>

M1SARAM

PAGE = 1

}

```

#### **Section Placement**

The SECTIONS section will specify how you want the sections to be distributed through memory. The following code is used to link the sections into the memory specified in the previous example:

The linker will gather all the code sections from all the files being linked together. Similarly, it will combine all 'like' sections.

Beginning with the first section listed, the linker will place it into the specified memory segment.

### **Summary: Linker Command File**

The linker command file (.cmd) contains the inputs — commands — for the linker. This information is summarized below:

## **Linker Command File Summary**

- ♦ Memory Map Description

- Name

- Location

- Size

- Sections Description

- Directs software sections into named memory regions

- Allows per-file discrimination

- Allows separate load/run locations

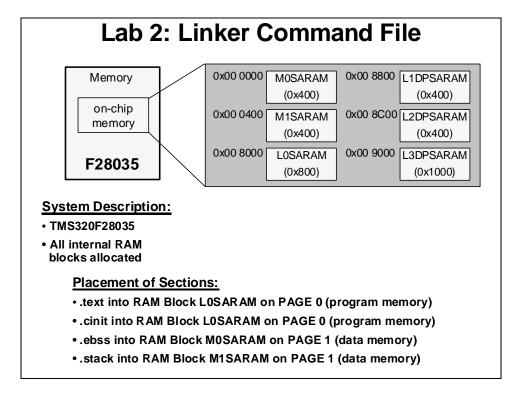

#### **Lab 2: Linker Command File**

#### Objective

Create a linker command file and link the C program file (Lab2.c) into the system described below.

#### **System Description**

- TMS320F28035

- All internal RAM blocks allocated

#### Placement of Sections:

- .text into RAM Block LOSARAM on PAGE 0 (program memory)

- .cinit into RAM Block LOSARAM on PAGE 0 (program memory)

- .ebss into RAM Block MOSARAM on PAGE 1 (data memory)

- .stack into RAM Block M1SARAM on PAGE 1 (data memory)

#### > Procedure

#### Start Code Composer Studio and Open a Workspace

1. Start Code Composer Studio (CCS) by double clicking the icon on the desktop or selecting it from the Windows Start menu. When CCS loads, a dialog box will prompt

you for the location of a workspace folder. Use the default location for the workspace and click OK.

This folder contains all CCS custom settings, which includes project settings and views when CCS is closed so that the same projects and settings will be available when CCS is opened again. The workspace is saved automatically when CCS is closed.

2. The first time CCS opens a "Welcome to Code Composer Studio v4" page appears. Close the page by clicking on the CCS icon in the upper right or by clicking the X on the "Welcome" tab. You should now have an empty workbench. The term workbench refers to the desktop development environment. Maximize CCS to fill your screen.

The workbench will open in the "C/C++ Perspective" view. Notice the C/C++ icon in the upper right-hand corner. A perspective defines the initial layout views of the workbench windows, toolbars, and menus which are appropriate for a specific type of task (i.e. code development or debugging). This minimizes clutter to the user interface. The "C/C++ Perspective" is used to create or build C/C++ projects. A "Debug Perspective" view will automatically be enabled when the debug session is started. This perspective is used for debugging C/C++ projects.

#### **Setup Target Configuration**

3. Open the emulator target configuration dialog box. On the menu bar click:

```

Target → New Target Configuration...

```

In the file name field type **F28035\_ExpKit.ccxml**. This is just a descriptive name since multiple target configuration files can be created. Leave the "Use shared location" box checked and select Finish.

- 4. In the next window that appears, select the emulator using the "Connection" pull-down list and choose "Texas Instruments XDS100v1 USB Emulator". In the box below, check the box to select "Experimenter's Kit Piccolo F28035". Click Save to save the configuration, then close the "Cheat Sheets" and "F28035\_ExpKit.ccxml" setup window by clicking the X on the tabs.

- 5. To view the target configurations, click:

```

View → Target Configurations

```

and click the plus sign (+) to the left of User Defined. Notice that the F28035\_ExpKit.ccxml file is listed and set as the default. If it is not set as the default, right-click on the .ccxml file and select "Set as Default". Close the Target Configurations window by clicking the X on the tab.

#### **Create a New Project**

6. A *project* contains all the files you will need to develop an executable output file (.out) which can be run on the MCU hardware. To create a new project click:

File  $\rightarrow$  New  $\rightarrow$  CCS Project

In the Project name field type **Lab2**. *Uncheck* the "Use default location" box. Click the Browse... button and navigate to:

C:\C28x\Labs\Lab2\Project

Click OK and then click Next.

- 7. The next window that appears selects the platform and configurations. Select the "Project Type" using the pull-down list and choose "C2000". In the "Configurations" box below, leave the "Debug" and "Release" boxes checked. This will create folders that will hold the output files. Click Next.

- 8. In the next window, inter-project dependencies (if any) are defined. Select Next.

- 9. In the last window, the CCS project settings are selected. Change the "Device Variant" using the pull-down list to "TMS320F28035". Next, using the pull-down list change the "Linker Command File" to "<none>". We will be using our own linker command file, rather than the one supplied by CCS. The "Runtime Support Library" will be automatically set to "rts2800\_ml.lib". This will select the large memory model runtime support library. Click Finish.

- 10. A new project has now been created. Notice the C/C++ Projects window contains Lab2. The project is set Active and the output files will be located in the Debug folder. At this point, the project does not include any source files. The next step is to add the source files to the project.

- 11. To add the source files to the project, right-click on Lab2 in the C/C++ Projects window and select:

```

Add Files to Project...

```

```

or click: Project → Add Files to Active Project...

```

and make sure you're looking in C:\C28x\Lab2\Files. With the "files of type" set to view all files (\*.\*) select Lab2.c and Lab2.cmd then click OPEN. This will add the files to the project.

12. In the C/C++ Projects window, click the plus sign (+) to the left of Lab2 and notice that the files are listed.

#### **Project Build Options**

13. There are numerous build options in the project. Most default option settings are sufficient for getting started. We will inspect a couple of the default options at this time. Right-click on Lab2 in the C/C++ Projects window and select Properties or click:

```

Project → Properties

```

14. A "Properties" window will open and in the section on the left be sure that "C/C++ Build" category is selected. In the "Configuration Settings" section make sure that the Tool Settings tab is selected. Next, under "C2000 Linker" select the "Basic Options". Notice that .out and .map files are being specified. The .out file is the

- executable code that will be loaded into the MCU. The .map file will contain a linker report showing memory usage and section addresses in memory.

- 15. Next in the "Basic Options" set the Stack Size to **0x200**.

- 16. Under "C2000 Compiler" select the "Runtime Model Options". Notice the "Use large memory model" and "Unified memory" boxes are checked. Select OK to save and close the Properties window.

#### Edit the Linker Command File - Lab2.cmd

- 17. To open and edit Lab2.cmd, double click on the filename in the C/C++ Projects window.

- 18. Edit the Memory { } declaration by describing the system memory shown on the "Lab2: Linker Command File" slide in the objective section of this lab exercise. Place the L0SARAM and L3DPSARAM memory blocks into program memory on page 0. Place the other memory blocks into data memory on page 1.

- 19. In the Sections { } area, notice that a section called .reset has already been allocated. The .reset section is part of the rts2800\_ml.lib, and is not needed. By putting the TYPE = DSECT modifier after its allocation, the linker will ignore this section and not allocate it.

- 20. Place the sections defined on the slide into the appropriate memories via the Sections { } area. Save your work and close the file.

#### **Build and Load the Project**

21. Three buttons on the horizontal toolbar control code generation. Hover your mouse over each button as you read the following descriptions:

| <b>Button</b> | Name    | <b>Description</b>                                       |

|---------------|---------|----------------------------------------------------------|

| 1             | Build   | Incremental build and link of only modified source files |

| 2             | Rebuild | Full build and link of all source files                  |

| 3             | Debug   | Automatically build, link, load and launch debug-session |

- 22. Click the "Build" button and watch the tools run in the Console window. Check for errors in the Problems window (we have deliberately put an error in Lab2.c). When you get an error, you will see the error message (in red) in the Problems window, and simply double-click the error message. The editor will automatically open to the source file containing the error, and position the mouse cursor at the correct code line.

- 23. Fix the error by adding a semicolon at the end of the "z = x + y" statement. For future knowledge, realize that a single code error can sometimes generate multiple error messages at build time. This was not the case here.

- 24. Build the project again. There should be no errors this time.

25. CCS can automatically save modified source files, build the program, open the debug perspective view, connect and download it to the target, and then run the program to the beginning of the main function.

Click on the "Debug" button (green bug) or click Target → Debug Active Project.

Notice the Debug icon in the upper right-hand corner indicating that we are now in the "Debug Perspective" view. The program ran through the C-environment initialization routine in the rts2800\_ml.lib and stopped at main() in Lab2.c.

#### **Debug Environment Windows**

It is standard debug practice to watch local and global variables while debugging code. There are various methods for doing this in Code Composer Studio. We will examine two of them here: memory windows, and watch windows.

26. Open a "Memory" window to view the global variable "z".

Click: View → Memory on the menu bar.

Type &z into the address field and select "Data" memory page. Note that you must use the ampersand (meaning "address of") when using a symbol in a memory window address box. Also note that Code Composer Studio is case sensitive.

Set the properties format to "Hex 16 Bit – TI Style Hex" in the window. This will give you more viewable data in the window. You can change the contents of any address in the memory window by double-clicking on its value. This is useful during debug.

27. Notice the "Local(1)" window automatically opened and the local variables x and y are present. The local window will always contain the local variables for the code function currently being executed.

(Note that local variables actually live on the stack. You can also view local variables in a memory window by setting the address to "SP" after the code function has been entered).

28. We can also add global variables to the watch window if desired. Let's add the global variable "z".

Click the "Watch (1)" tab at the top of the watch window. In the empty box in the "Name" column, type  $\mathbf{z}$  and then enter. An ampersand is not used here. The watch window knows you are specifying a symbol. (Note that the watch window can be manually opened by clicking: View  $\rightarrow$  Watch Window on the menu bar).

Check that the watch window and memory window both report the same value for "z". Trying changing the value in one window, and notice that the value also changes in the other window.

#### Single-stepping the Code

29. Click the "Local (1)" tab at the top of the watch window. Single-step through main() by using the <F5> key (or you can use the Step Into button on the horizontal toolbar). Check to see if the program is working as expected. What is the value for "z" when you get to the end of the program?

#### **Terminate Debug Session and Close Project**

30. The Terminate All button will terminate the active debug session, close the debugger and return CCS to the "C/C++ Perspective" view.

Click: Target → Terminate All or use the Terminate All icon:

Close the Terminate Debug Session "Cheat Sheet" by clicking on the X on the tab.

31. Next, close the project by right-clicking on Lab2 in the C/C++ Projects window and select Close Project.

#### **End of Exercise**

#### Lab 2: Solution - lab2.cmd

.stack:

.reset:

#### Lab 2: Solution - lab2.cmd MEMORY PAGE 0: /\* Program Memory \*/ LOSARAM: origin = 0x008000, length = 0x0800L3DPSARAM: origin = 0x009000, length = 0x1000/\* Data Memory \*/ PAGE 1: MOSARAM: origin = $0 \times 0000000$ , length = $0 \times 0400$ M1SARAM: origin = $0 \times 000400$ , length = $0 \times 0400$ L1DPSARAM: origin = 0x008800, length = 0x0400L2DPSARAM: origin = 0x008C00, length = 0x0400 } SECTIONS > LOSARAM PAGE = 0.text: > MOSARAM > LOSARAM > M1SARAM PAGE = 1.ebss: .cinit: PAGE = 0

> LOSARAM

PAGE = 1

PAGE = 0, TYPE = DSECT

## **Peripherial Registers Header Files**

#### Introduction

The purpose of the DSP2803x C-code header files is to simplify the programming of the many peripherals on the F28x device. Typically, to program a peripheral the programmer needs to write the appropriate values to the different fields within a control register. In its simplest form, the process consists of writing a hex value (or masking a bit field) to the correct address in memory. But, since this can be a burdensome and repetitive task, the C-code header files were created to make this a less complicated task.

The DSP2803x C-code header files are part of a library consisting of C functions, macros, peripheral structures, and variable definitions. Together, this set of files is known as the 'header files.'

Registers and the bit-fields are represented by structures. C functions and macros are used to initialize or modify the structures (registers).

In this module, you will learn how to use the header files and C programs to facilitate programming the peripherals.

#### **Learning Objectives**

# **Learning Objectives**

- Understand the usage of the F2803x

C-Code Header Files

- Be able to program peripheral registers

- Understand how the structures are mapped with the linker command file

# **Module Topics**

| Peripherial Registers Header Files             | 3-1  |

|------------------------------------------------|------|

| Module Topics                                  | 3-2  |

| Traditional and Structure Approach to C Coding | 3-3  |

| Naming Conventions                             | 3-6  |

| F2803x C-Code Header Files                     |      |

| Peripheral Structure .h File                   | 3-7  |

| Global Variable Definitions File               | 3-9  |

| Mapping Structures to Memory                   |      |

| Linker Command File                            | 3-10 |

| Peripheral Specific Routines                   | 3-11 |

| Summary                                        | 3-12 |

#### Traditional and Structure Approach to C Coding

## **Traditional Approach to C Coding**

```

#define ADCCTL1

(volatile unsigned int *)0x00007100

void main(void)

*ADCCTL1 = 0x1234;

//write entire register

*ADCCTL1 |= 0x4000;

//enable ADC module

```

#### **Advantages**

- Simple, fast and easy to type

- Variable names exactly match register names (easy to remember)

- Disadvantages Requires individual masks to be generated to manipulate individual bits

- Cannot easily display bit fields in debugger window

- Will generate less efficient code in many cases

#### Structure Approach to C Coding

```

void main(void)

AdcRegs.ADCCTL1.all = 0x1234;

//write entire register

AdcRegs.ADCCTL1.bit.ADCENABLE = 1; //enable ADC module

}

```

#### **Advantages**

- Easy to manipulate individual bits

- Watch window is amazing! (next slide)

- Generates most efficient code (on C28x)

#### **Disadvantages**

- Can be difficult to remember the structure names (Editor Auto Complete feature to the rescue!)

- More to type (again, Editor Auto Complete feature to the rescue)

#### Is the Structure Approach Efficient?

The structure approach enables efficient compiler use of DP addressing mode and C28x atomic operations

#### **C Source Code**

# // Stop CPU Timer0 CpuTimer0Regs.TCR.bit.TSS = 1; // Load new 32-bit period value CpuTimer0Regs.PRD.all = 0x00010000; // Start CPU Timer0 CpuTimer0Regs.TCR.bit.TSS = 0;

#### Generated Assembly Code\*

```

MOVW DP, #0030

OR @4, #0x0010

MOVL XAR4, #0x010000

MOVL @2, XAR4

AND @4, #0xFFEF

```

- Easy to read the code w/o comments

- Bit mask built-in to structure

5 words, 5 cycles

You could not have coded this example any more efficiently with hand assembly!

\* C28x Compiler v5.0.1 with -g and either -o1, -o2, or -o3 optimization level

## Compare with the #define Approach

The #define approach relies heavily on less-efficient pointers for random memory access, and often does not take advantage of C28x atomic operations

#### **C Source Code**

```

// Stop CPU Timer0

*TIMEROTCR |= 0x0010;

// Load new 32-bit period value

*TIMEROTPRD32 = 0x00010000;

// Start CPU Timer0

*TIMEROTCR &= 0xFFEF;

```

#### **Generated Assembly Code\***

```

MOV @AL,*(0:0x0C04)

ORB AL, #0x10

MOV *(0:0x0C04), @AL

MOVL XAR5, #0x010000

MOVL XAR4, #0x000C0A

MOVL *+XAR4[0], XAR5

MOV @AL, *(0:0x0C04)

AND @AL, #0xFFEF

MOV *(0:0x0C04), @AL

```

- Hard to read the code w/o comments

- 9 words, 9 cycles

- User had to determine the bit mask

- \* C28x Compiler v5.0.1 with -g and either -o1, -o2, or -o3 optimization level

### **Naming Conventions**

The header files use a familiar set of naming conventions. They are consistent with the Code Composer Studio configuration tool, and generated file naming conventions.

### **Structure Naming Conventions**

- The DSP2803x header files define:

- · All of the peripheral structures

- All of the register names

- All of the bit field names

- All of the register addresses

```

PeripheralName.RegisterName.half.LSW // Access low 16-bits of 32-bit register

PeripheralName.RegisterName.half.MSW // Access high 16-bits of 32-bit register

PeripheralName.RegisterName.half.MSW // Access high 16-bits of 32-bit register

PeripheralName.RegisterName.bit.FieldName // Access specified bit fields of register

Notes: [1] "PeripheralName" are assigned by TI and found in the DSP2803x header files.

They are a combination of capital and small letters (i.e. CpuTimer0Regs).

[2] "RegisterName" are the same names as used in the data sheet.

They are always in capital letters (i.e. TCR, TIM, TPR,...).

[3] "FieldName" are the same names as used in the data sheet.

They are always in capital letters (i.e. POL, TOG, TSS,...).

```

#### F2803x C-Code Header Files

The C-code header files consists of .h, c source files, linker command files, and other useful example programs, documentations and add-ins for Code Composer Studio.

# DSP2803x Header File Package (http://www.ti.com, literature # SPRC892)

- Contains everything needed to use the structure approach

- Defines all peripheral register bits and register addresses

- Header file package includes:

- DSP2803x headers\include → .h files

- \DSP2803x headers\cmd → linker .cmd files

- → .gel files for CCS \DSP2803x\_headers\gel

- \DSP2803x examples → CCS3 examples

- DSP2803x examples ccsv4 → CCS4 examples

- \doc → documentation

A peripheral is programmed by writing values to a set of registers. Sometimes, individual fields are written to as bits, or as bytes, or as entire words. Unions are used to overlap memory (register) so the contents can be accessed in different ways. The header files group all the registers belonging to a specific peripheral.

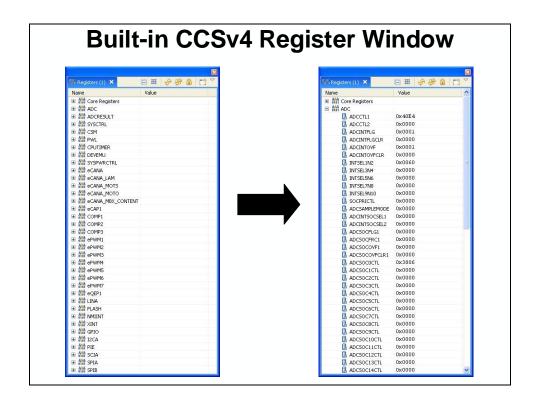

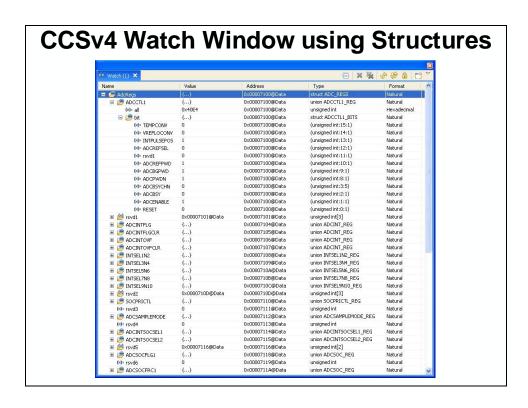

Peripheral data structures can be added to the watch window by right-clicking on the structure and selecting the option to add to watch window. This will allow viewing of the individual register fields.

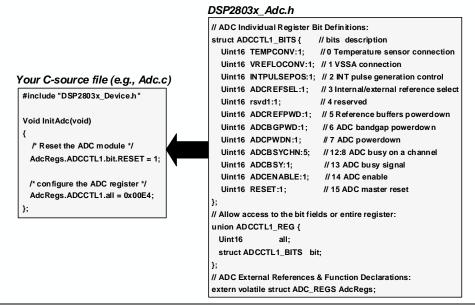

#### **Peripheral Structure .h File**

The DSP2803x\_Device.h header file is the main include file. By including this file in the .c source code, all of the peripheral specific h header files are automatically included. Of course, each specific .h header file can be included individually in an application that does not use all the header files, or you can comment out the ones you do not need. (Also includes typedef statements).

#### Peripheral Structure .h files (1 of 2)

♦ Contain bits field structure definitions for each peripheral register

### Peripheral Structure .h files (2 of 2)

◆ The header file package contains a .h file for each peripheral in the device

```

DSP2803x_BootVars.h

DSP2803x_Adc.h

DSP2803x_Cla.h

DSP2803x_Comp.h

DSP2803x_CpuTimers.h DSP2803x_DevEmu.h

DSP2803x_Device.h

DSP2803x_ECan.h

DSP2803x_ECap.h

DSP2803x_EPwm.h

DSP2803x_EQep.h

DSP2803x_Gpio.h

DSP2803x I2c.h

DSP2803x Lin.h

DSP2803x_NmiIntrupt.h

DSP2803x_PieCtrl.h

DSP2803x_PieVect.h

DSP2803x_Sci.h

DSP2803x_Spi.h

DSP2803x_SysCtrl.h

DSP2803x_XIntrupt.h

```

- ◆ DSP2803x Device.h

- Main include file

- · Will include all other .h files

- Include this file (directly or indirectly) in each source file:

#include "DSP2803x Device.h"

#### **Global Variable Definitions File**

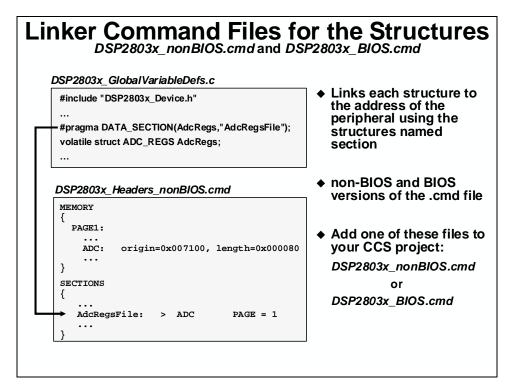

With DSP2803x\_GlobalVariableDefs.c included in the project all the needed variable definitions are globally defined.

# Global Variable Definitions File DSP2803x\_GlobalVariableDefs.c

- Declares a global instantiation of the structure for each peripheral

- Each structure is placed in its own section using a DATA\_SECTION pragma to allow linking to the correct memory (see next slide)

DSP2803x\_GlobalVariableDefs.c

#include "DSP2803x\_Device.h" #pragma DATA\_SECTION(AdcRegs,"AdcRegsFile"); volatile struct ADC\_REGS AdcRegs;

Add this file to your CCS project: DSP2803x\_GlobalVariableDefs.c

#### **Mapping Structures to Memory**

The data structures describe the register set in detail. And, each instance of the data type (i.e., register set) is unique. Each structure is associated with an address in memory. This is done by (1) creating a new section name via a DATA\_SECTION pragma, and (2) linking the new section name to a specific memory in the linker command file.

#### **Linker Command File**

When using the header files, the user adds the MEMORY regions that correspond to the CODE\_SECTION and DATA\_SECTION pragmas found in the .h and global-definitions.c file.

The user can modify their own linker command file, or use a pre-configured linker command file such as F28035.cmd. This file has the peripheral memory regions defined and tied to the individual peripheral.

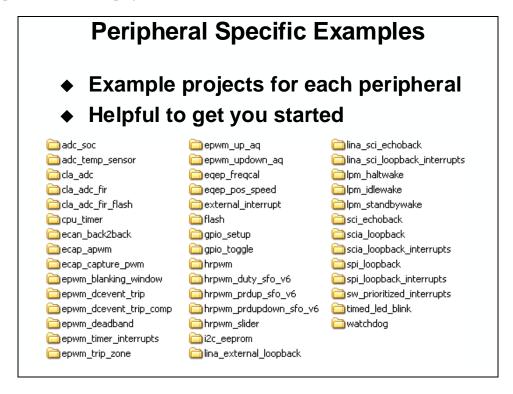

#### **Peripheral Specific Routines**

Peripheral Specific C functions are used to initialize the peripherals. They are used by adding the appropriate .c file to the project.

## **Summary**

# Peripheral Register Header Files Summary

- **♦** Easier code development

- Easy to use

- **♦** Generates most efficient code

- Increases effectiveness of CCS watch window

- TI has already done all the work!

- Use the correct header file package for your device:

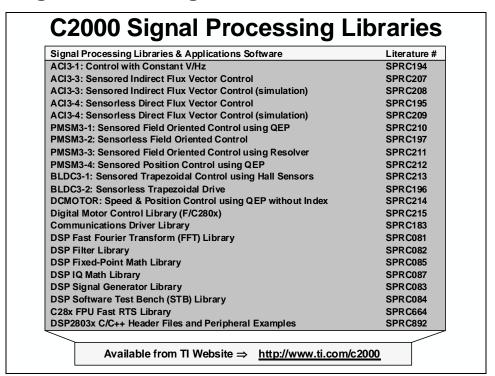

| • F2803x            | # SPRC892 |

|---------------------|-----------|

| • F2802x            | # SPRC832 |

| • F2833x and F2823x | # SPRC530 |

| • F280x and F2801x  | # SPRC191 |

| • F2804x            | # SPRC324 |

| • F281x             | # SPRC097 |

Go to http://www.ti.com and enter the literature number in the keyword search box

# **Reset and Interrupts**

#### Introduction

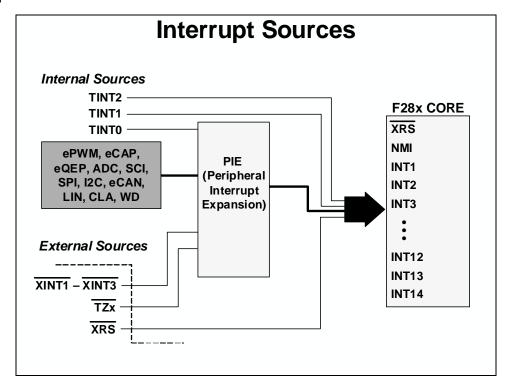

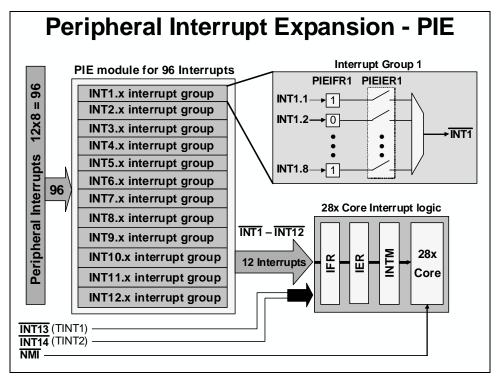

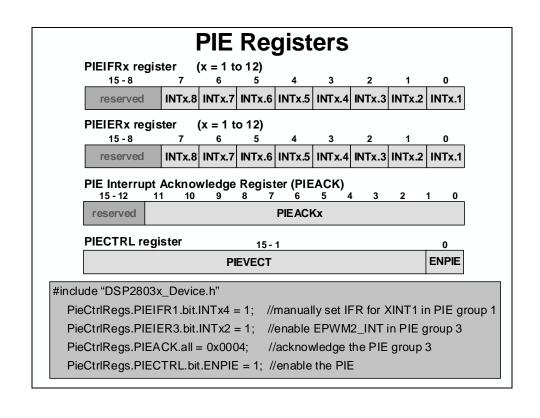

This module describes the interrupt process and explains how the Peripheral Interrupt Expansion (PIE) works.

## **Learning Objectives**

# **Learning Objectives**

- ◆ Describe the F28x reset process

- ◆ List the event sequence during an interrupt

- **♦** Describe the F28x interrupt structure

# **Module Topics**

| Reset and Interrupts                               | 4-1 |

|----------------------------------------------------|-----|

| Module Topics                                      | 4-2 |

| Reset                                              | 4-3 |

| Reset - Bootloader                                 | 4-3 |

| Emulation Boot Mode                                |     |

| Stand-Alone Boot Mode                              | 4-4 |

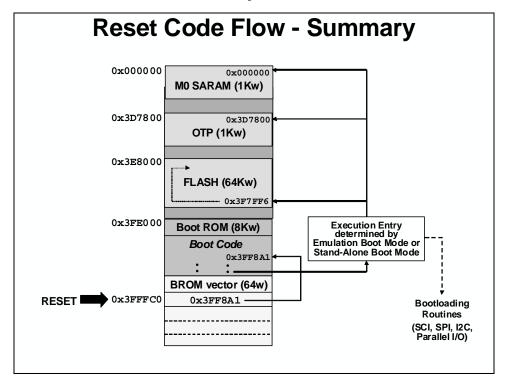

| Reset Code Flow – Summary                          |     |

| Emulation Boot Mode using Code Composer Studio GEL |     |

| Interrupts                                         | 4-6 |

| Interrupt Processing                               | 4-6 |

| Interrupt Flag Register (IFR)                      | 4-7 |

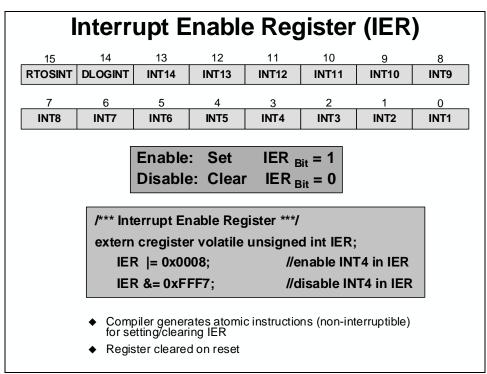

| Interrupt Enable Register (IER)                    |     |

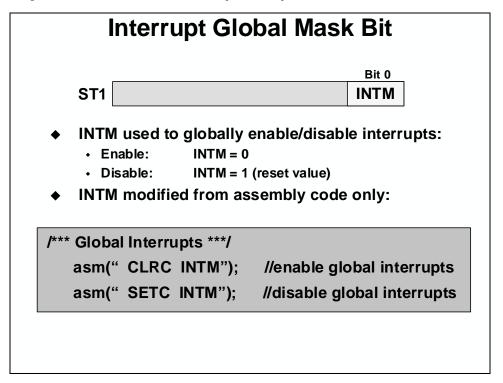

| Interrupt Global Mask Bit (INTM)                   |     |

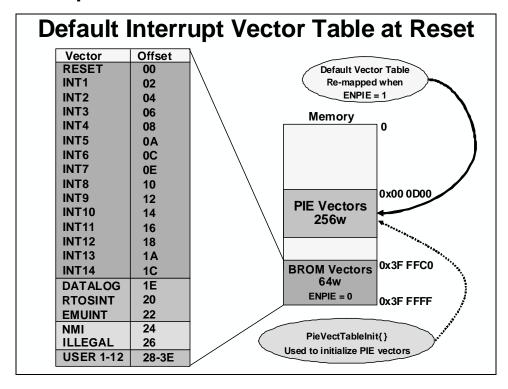

| Peripheral Interrupt Expansion (PIE)               |     |

| PIE Interrupt Vector Table                         |     |

| Interrupt Response and Latency                     |     |

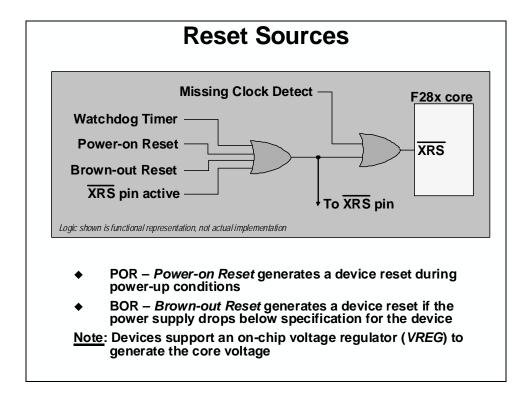

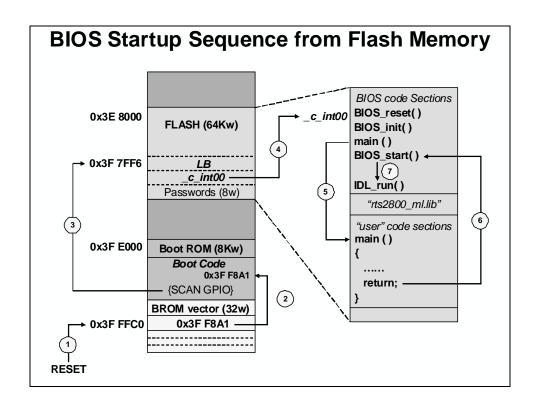

#### Reset

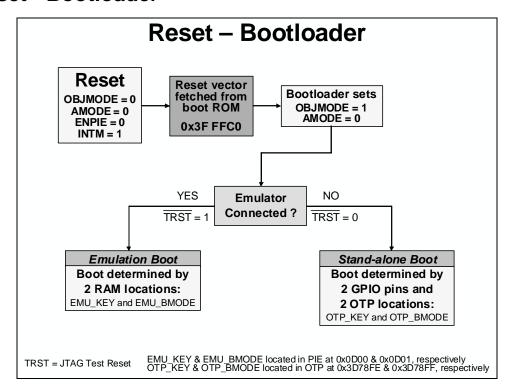

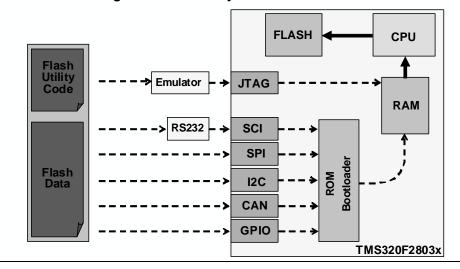

#### Reset - Bootloader

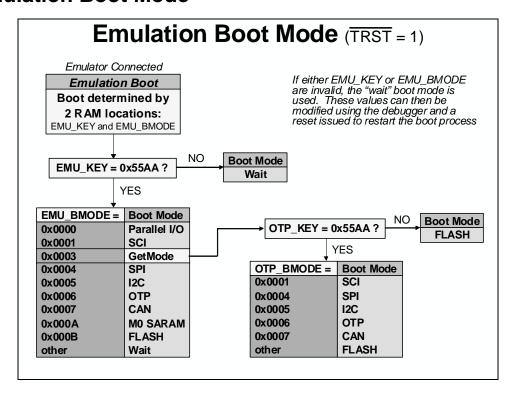

#### **Emulation Boot Mode**

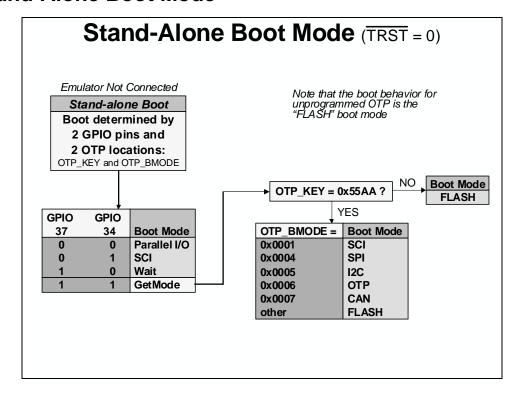

#### Stand-Alone Boot Mode

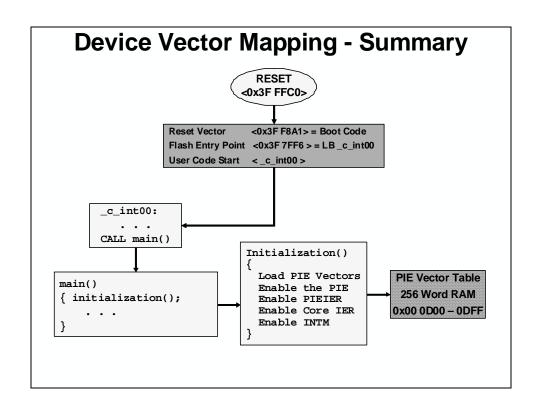

#### **Reset Code Flow – Summary**

#### **Emulation Boot Mode using Code Composer Studio GEL**

The CCS GEL file can be used to setup the boot mode for the device during debug. The "OnReset()" GEL function is called each time the device is reset. This function can be modified to include a call to set the device to "Boot to SARAM" emulation mode automatically, if desired.

```

OnReset(int nErrorCode)

{

C28x_Mode();

Unlock_CSM();

Device_Cal();

CLA_Clock_Enable();

/* Enable CLA clock */

/* Set EMU Boot Variables - Boot to SARAM */

// EMU_BOOT_SARAM();

EMU_BOOT_FLASH();

/* Set EMU Boot Variables - Boot to flash */

The GEL file also provides a function to set the device to "Boot to Flash":

/* EMU Boot Mode - Set Boot Mode During Debug

/****************************

menuitem "EMU Boot Mode Select"

hotmenu EMU_BOOT_SARAM()

*0xD00 = 0x55AA; /* EMU_KEY = 0x 55AA */

*0xD01 = 0x000A; /* Boot to SARAM */

hotmenu EMU_BOOT_FLASH()

*0xD00 = 0x55AA; /* EMU_KEY = 0x 55AA */

*0xD01 = 0x000B; /* Boot to FLASH

```

To access the GEL file use: Tools → Debugger Options → Generic Debugger Options

#### **Interrupts**

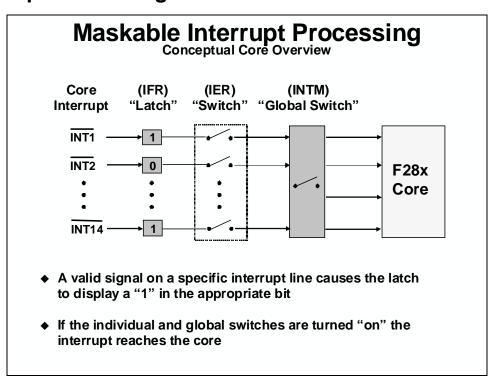

#### **Interrupt Processing**

#### **Interrupt Flag Register (IFR)**

#### **Interrupt Flag Register (IFR)** 14 12 15 13 11 10 8 **RTOSINT** DLOGINT INT14 INT13 INT12 INT11 INT<sub>10</sub> INT9 0 INT8 INT7 INT6 INT5 INT4 INT3 INT2 INT1 Pending: IFR $_{Bit} = 1$

Pending: IFR  $_{Bit} = 1$ Absent: IFR  $_{Bit} = 0$

/\*\*\* Manual setting/clearing IFR \*\*\*/

extern cregister volatile unsigned int IFR;

IFR |= 0x0008; //set INT4 in IFR IFR &= 0xFFF7; //clear INT4 in IFR

- ◆ Compiler generates atomic instructions (non-interruptible) for setting/clearing IFR

- ◆ If interrupt occurs when writing IFR, interrupt has priority

- ◆ IFR(bit) cleared when interrupt is acknowledged by CPU

- ◆ Register cleared on reset

#### Interrupt Enable Register (IER)

#### **Interrupt Global Mask Bit (INTM)**

#### **Peripheral Interrupt Expansion (PIE)**

| F28   | 03x I         | PIE li          | nterr           | upt A           | Assig           | jnme            | nt Ta           | able                |

|-------|---------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|---------------------|

|       | INTx.8        | INTx.7          | INTx.6          | INTx.5          | INTx.4          | INTx.3          | INTx.2          | INTx.1              |

| INT1  | WAKEINT       | TINT0           | ADCINT9         | XINT2           | XINT1           |                 | ADCINT2         | ADCINT <sup>2</sup> |

| INT2  |               | EPWM7<br>_TZINT | EPWM6<br>_TZINT | EPWM5<br>_TZINT | EPWM4<br>_TZINT | EPWM3<br>_TZINT | EPWM2<br>_TZINT | EPWM1<br>_TZINT     |

| INT3  |               | EPWM7<br>_INT   | EPWM6<br>_INT   | EPWM5<br>_INT   | EPWM4<br>_INT   | EPWM3<br>_INT   | EPWM2<br>_INT   | EPWM1<br>_INT       |

| INT4  |               |                 |                 |                 |                 |                 |                 | ECAP1<br>_INT       |

| INT5  |               |                 |                 |                 |                 |                 |                 | EQEP1<br>_INT       |

| INT6  |               |                 |                 |                 | SPITX<br>INTB   | SPIRX<br>INTB   | SPITX<br>INTA   | SPIRX<br>INTA       |

| INT7  |               |                 |                 |                 |                 |                 |                 |                     |

| INT8  |               |                 |                 |                 |                 |                 | I2CINT2A        | I2CINT1             |

| INT9  |               |                 | ECAN1<br>INTA   | ECAN0<br>INTA   | LIN1<br>INTA    | LIN0<br>INTA    | SCITX<br>INTA   | SCIRX<br>INTA       |

| INT10 | ADCINT8       | ADCINT7         | ADCINT6         | ADCINT5         | ADCINT4         | ADCINT3         | ADCINT2         | ADCINT1             |

| INT11 | CLA1<br>_INT8 | CLA1<br>_INT7   | CLA1<br>_INT6   | CLA1<br>_INT5   | CLA1<br>_INT4   | CLA1<br>_INT3   | CLA1<br>_INT2   | CLA1<br>_INT1       |

| INT12 | LUF           | LVF             |                 |                 |                 |                 |                 | XINT3               |

#### **PIE Interrupt Vector Table**

|                                                                                                                                                                                                            |     | PIE         | Vector      | Mapping (ENPIE = 1)                   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|-------------|---------------------------------------|

|                                                                                                                                                                                                            |     | Vector Name | PIE Address | PIE Vector Description                |

|                                                                                                                                                                                                            |     | Reset       | 0x00 0D00   | Reset fetched from Boot ROM 0x3F FFC0 |

|                                                                                                                                                                                                            |     | INT1        | 0x00 0D02   | INT1 remapped to PIE group below      |

| Г                                                                                                                                                                                                          |     |             |             | INTx remapped to PIE group below      |

|                                                                                                                                                                                                            |     | INT12       | 0x00 0D18   | INT12 remapped to PIE group below     |

|                                                                                                                                                                                                            | Ì   | INT13       | 0x00 0D1A   | CPU Timer 1                           |

|                                                                                                                                                                                                            |     | INT14       | 0x00 0D1C   | CPU Timer 2                           |

| Remapped                                                                                                                                                                                                   |     | DATALOG     | 0x00 0D1E   | CPU Data Logging Interrupt            |

| ар                                                                                                                                                                                                         |     |             |             |                                       |

| e l                                                                                                                                                                                                        |     | USER12      | 0x00 0D3E   | User Defined Trap                     |

| ~                                                                                                                                                                                                          |     | INT1.1      | 0x00 0D40   | PIE INT1.1 Interrupt Vector           |

|                                                                                                                                                                                                            |     |             |             |                                       |

|                                                                                                                                                                                                            |     | INT1.8      | 0x00 0D4E   | PIE INT1.8 Interrupt Vector           |

| L                                                                                                                                                                                                          | ► ( |             |             |                                       |

|                                                                                                                                                                                                            |     | INT12.1     | 0x00 0DF0   | PIE INT12.1 Interrupt Vector          |

|                                                                                                                                                                                                            |     |             |             |                                       |

|                                                                                                                                                                                                            |     | INT12.8     | 0x00 0DFE   | PIE INT12.8 Interrupt Vector          |

| <ul> <li>PIE vector location – 0x00 0D00 – 256 words in data memory</li> <li>RESET and INT1-INT12 vector locations are re-mapped</li> <li>CPU vectors are re-mapped to 0x00 0D00 in data memory</li> </ul> |     |             |             |                                       |

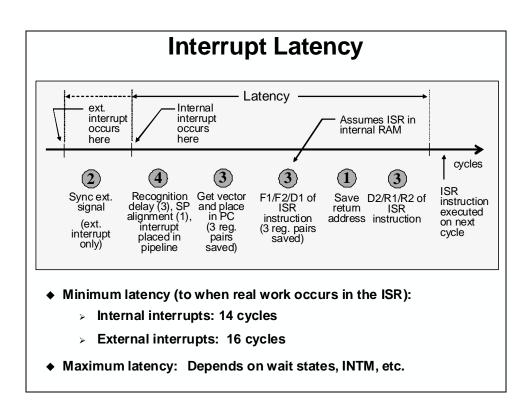

#### **Interrupt Response and Latency**

# **Interrupt Response - Hardware Sequence**

| CPU Action              | Description                      |

|-------------------------|----------------------------------|

| Registers → stack       | 14 Register words auto saved     |

| 0 → IFR (bit)           | Clear corresponding IFR bit      |

| 0 → IER (bit)           | Clear corresponding IER bit      |

| 1 → INTM/DBGM           | Disable global ints/debug events |

| Vector → PC             | Loads PC with int vector address |

| Clear other status bits | Clear LOOP, EALLOW, IDLESTAT     |

Note: some actions occur simultaneously, none are interruptible

| Т       | ST0     |

|---------|---------|

| AH      | AL      |

| PH      | PL      |

| AR1     | AR0     |

| DP      | ST1     |

| DBSTAT  | IER     |

| PC(msw) | PC(Isw) |

# **System Initialization**

#### Introduction

This module discusses the operation of the OSC/PLL-based clock module and watchdog timer. Also, the general-purpose digital I/O ports, external interrups, various low power modes and the EALLOW protected registers will be covered.

#### **Learning Objectives**

## **Learning Objectives**

- **◆ OSC/PLL Clock Module**

- Watchdog Timer

- ♦ General Purpose Digital I/O

- ◆ External Interrupts

- **◆ Low Power Modes**

- **♦** Register Protection

# **Module Topics**

| System Initialization        | 5-1  |

|------------------------------|------|

| Module Topics                | 5-2  |

| Oscillator/PLL Clock Module  | 5-3  |

| Watchdog Timer               | 5-6  |

| General-Purpose Digital I/O  | 5-10 |

| External Interrupts          | 5-13 |

| Low Power Modes              | 5-14 |

| Register Protection          | 5-16 |

| Lah 5: System Initialization | 5-18 |

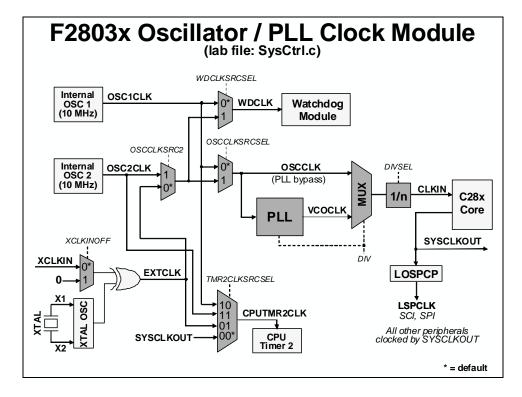

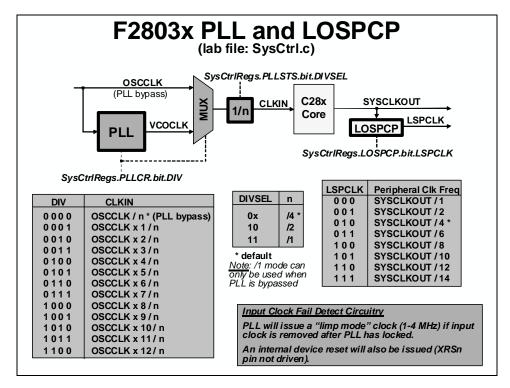

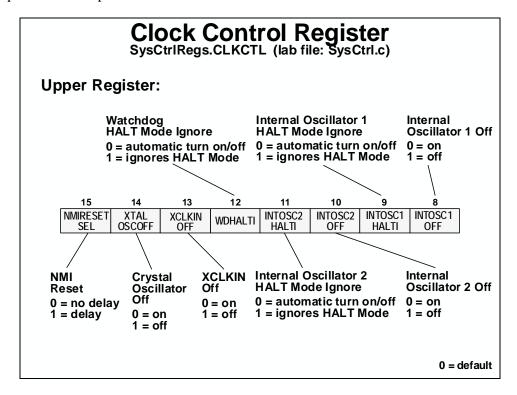

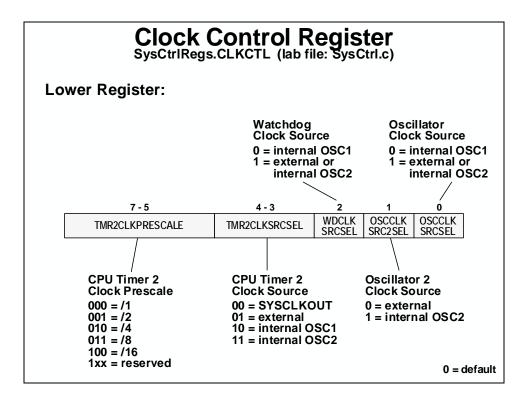

#### Oscillator/PLL Clock Module

The on-chip oscillator and phase-locked loop (PLL) block provide all the necessary clocking signals for the F2803x devices. The two internal oscillators (INTOSC1 and INTOSC2) need no external components.

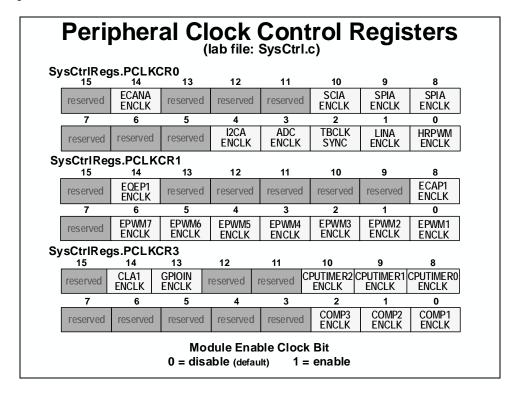

The PLL has a 4-bit ratio control to select different CPU clock rates. In addition to the on-chip oscillators, two external modes of operation are supported – crystal operation, and external clock source operation. Crystal operation allows the use of an external crystal/resonator to provide the time base to the device. External clock source operation allows the internal (crystal) oscillator to be bypassed, and the device clocks are generated from an external clock source input on the XCLKIN pin. The C28x core provides a SYSCLKOUT clock signal. This signal is prescaled to provide a clock source for some of the on-chip communication peripherals through the low-speed peripheral clock prescaler. Other peripherals are clocked by SYSCLKOUT and use their own clock prescalers for operation.

The peripheral clock control register allows individual peripheral clock signals to be enabled or disabled. If a peripheral is not being used, its clock signal could be disabled, thus reducing power consumption.

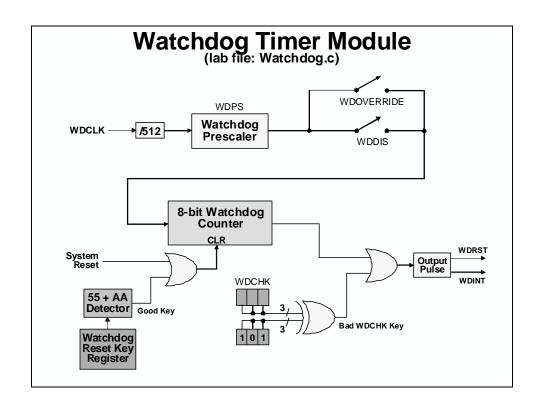

#### **Watchdog Timer**

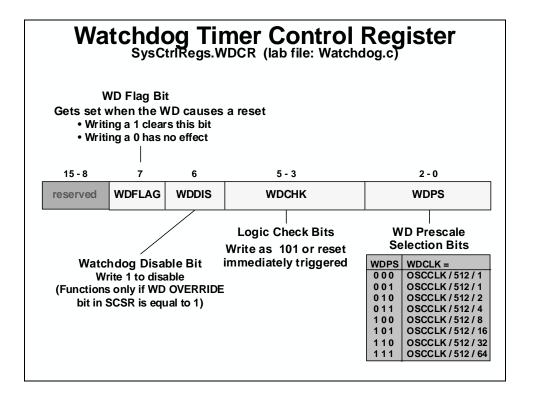

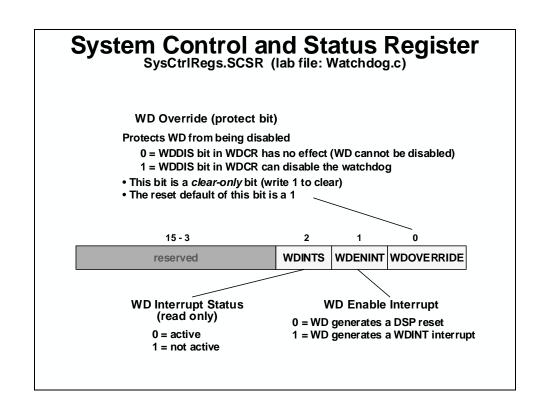

### **Watchdog Timer**

- Resets the C28x if the CPU crashes

- Watchdog counter runs independent of CPU

- If counter overflows, a reset or interrupt is triggered (user selectable)

- CPU must write correct data key sequence to reset the counter before overflow

- Watchdog must be serviced or disabled within 131,072 WDCLK cycles after reset

- ◆ This translates to 13.11 ms with a 10 MHz WDCLK

The watchdog timer provides a safeguard against CPU crashes by automatically initiating a reset if it is not serviced by the CPU at regular intervals. In motor control applications, this helps protect the motor and drive electronics when control is lost due to a CPU lockup. Any CPU reset will revert the PWM outputs to a high-impedance state, which should turn off the power converters in a properly designed system.

The watchdog timer is running immediately after system power-up/reset, and must be dealt with by software soon after. Specifically, you have 13.11 ms (for a 60 MHz device) after any reset before a watchdog initiated reset will occur. This translates into 131,072 WDCLK cycles, which is a seemingly tremendous amount! Indeed, this is plenty of time to get the watchdog configured as desired and serviced. A failure of your software to properly handle the watchdog after reset could cause an endless cycle of watchdog initiated resets to occur.

# **Watchdog Period Selection**

| WDPS<br>Bits                                 | FRC<br>rollover              | WD timeout period @ 10 MHz WDCLK                           |

|----------------------------------------------|------------------------------|------------------------------------------------------------|

| 00x:<br>010:<br>011:<br>100:<br>101:<br>110: | 1<br>2<br>4<br>8<br>16<br>32 | 13.11 ms * 26.22 ms 52.44 ms 104.88 ms 209.76 ms 419.52 ms |

| 111:                                         | 64                           | 839.04 ms                                                  |

<sup>\*</sup> reset default

- Remember: Watchdog starts counting immediately after reset is released!

- ◆ Reset default with WDCLK = 10 MHz computed as (1/10 MHz) \* 512 \* 256 = 13.11 ms

# Resetting the Watchdog SysCtrlRegs.WDKEY (lab file: Watchdog.c)

15 - 8 7 - 0

reserved WDKEY

WDKEY write values:

55h - counter enabled for reset on next AAh write AAh - counter set to zero if reset enabled

- Writing any other value has no effect

- Watchdog should not be serviced solely in an ISR

- If main code crashes, but interrupt continues to execute, the watchdog will not catch the crash

- Could put the 55h WDKEY in the main code, and the AAh WDKEY in an ISR; this catches main code crashes and also ISR crashes

| WDKEY Write Results |                        |                                                   |  |

|---------------------|------------------------|---------------------------------------------------|--|

| Sequential<br>Step  | Value Written to WDKEY | Result                                            |  |

| 1                   | AAh                    | No action                                         |  |

| 2                   | AAh                    | No action                                         |  |

| 3                   | 55h                    | WD counter enabled for reset on next AAh write    |  |

| 4                   | 55h                    | WD counter enabled for reset on next AAh write    |  |

| 5                   | 55h                    | WD counter enabled for reset on next AAh write    |  |

| 6                   | AAh                    | WD counter is reset                               |  |

| 7                   | AAh                    | No action                                         |  |

| 8                   | 55h                    | WD counter enabled for reset on next AAh write    |  |

| 9                   | AAh                    | WD counter is reset                               |  |

| 10                  | 55h                    | WD counter enabled for reset on next AAh write    |  |

| 11                  | 23h                    | No effect; WD counter not reset on next AAh write |  |

| 12                  | AAh                    | No action due to previous invalid value           |  |

| 13                  | 55h                    | WD counter enabled for reset on next AAh write    |  |

| 14                  | AAh                    | WD counter is reset                               |  |

#### **General-Purpose Digital I/O**

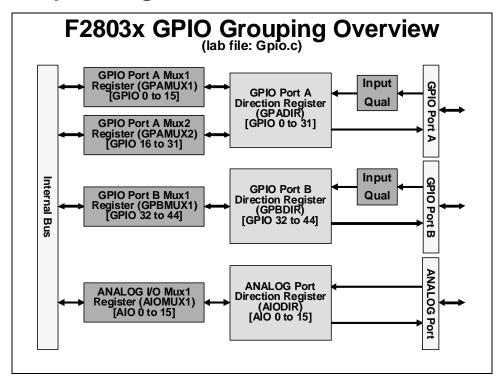

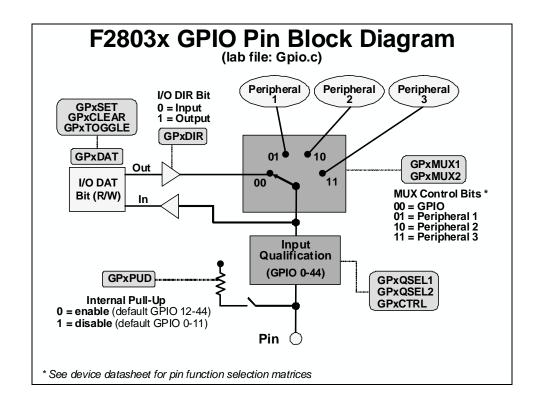

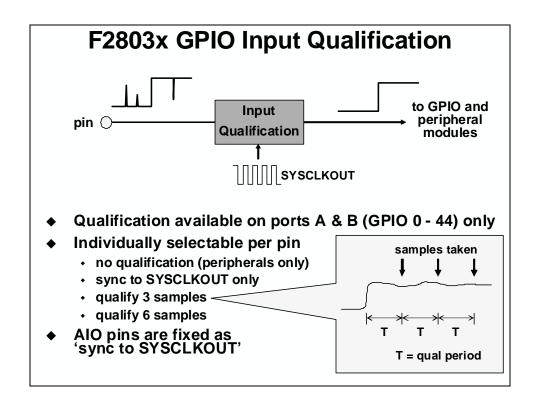

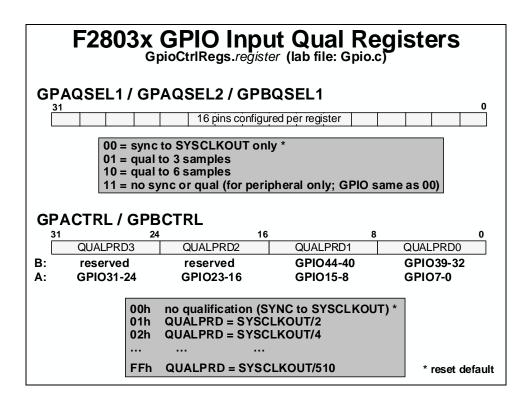

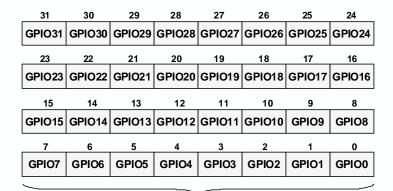

# F2803x GPIO Control Registers GpioCtrlRegs.register (lab file: Gpio.c)

| Register | Description                                       |

|----------|---------------------------------------------------|

| GPACTRL  | GPIO A Control Register [GPIO 0 – 31]             |

| GPAQSEL1 | GPIO A Qualifier Select 1 Register [GPIO 0 – 15]  |

| GPAQSEL2 | GPIO A Qualifier Select 2 Register [GPIO 16 – 31] |

| GPAMUX1  | GPIO A Mux1 Register [GPIO 0 - 15]                |

| GPAMUX2  | GPIO A Mux2 Register [GPIO 16 – 31]               |

| GPADIR   | GPIO A Direction Register [GPIO 0 - 31]           |

| GPAPUD   | GPIO A Pull-Up Disable Register [GPIO 0 - 31]     |

| GPBCTRL  | GPIO B Control Register [GPIO 32 – 44]            |

| GPBQSEL1 | GPIO B Qualifier Select 1 Register [GPIO 32 – 44] |

| GPBMUX1  | GPIO B Mux1 Register [GPIO 32 – 44]               |

| GPBDIR   | GPIO B Direction Register [GPIO 32 – 44]          |

| GPBPUD   | GPIO B Pull-Up Disable Register [GPIO 32 – 44]    |

| AIOMUX1  | ANALOG VO Mux1 Register [AIO 0 - 15]              |

| AIODIR   | ANALOG I/O Direction Register [AIO 0 - 15]        |

# F2803x GPIO Data Registers GpioDataRegs.register (lab file: Gpio.c)

| Register  | Description                                 |

|-----------|---------------------------------------------|

| GPADAT    | GPIO A Data Register [GPIO 0 – 31]          |

| GPASET    | GPIO A Data Set Register [GPIO 0 – 31]      |

| GPACLEAR  | GPIO A Data Clear Register [GPIO 0 - 31]    |

| GPATOGGLE | GPIO A Data Toggle [GPIO 0 - 31]            |

| GPBDAT    | GPIO B Data Register [GPIO 32 – 44]         |

| GPBSET    | GPIO B Data Set Register [GPIO 32 – 44]     |

| GPBCLEAR  | GPIO B Data Clear Register [GPIO 32 – 44]   |

| GPBTOGGLE | GPIO B Data Toggle [GPIO 32 – 44]           |

| AIODAT    | ANALOG I/O Data Register [AIO 0 - 15]       |

| AIOSET    | ANALOG I/O Data Set Register [AIO 0 – 15]   |

| AIOCLEAR  | ANALOG I/O Data Clear Register [AIO 0 – 15] |

| AIOTOGGLE | ANALOG VO Data Toggle [AIO 0 – 15]          |

# **External Interrupts**

# **External Interrupts**

- 3 external interrupt signals: XINT1, XINT2 and XINT3

- ◆ XINT1, XINT2 and XINT3 can be mapped to any of GPIO0-31

- ◆ XINT1, XINT2 and XINT3 also each have a free-running 16-bit counter that measures the elapsed time between interrupts

- The counter resets to zero each time the interrupt occurs

# **External Interrupt Registers**

| Interrupt | Pin Selection Register | Configuration Register  | Counter Register        |

|-----------|------------------------|-------------------------|-------------------------|

|           | (GpioIntRegs.register) | (XIntruptRegs.register) | (XIntruptRegs.register) |

| XINT1     | GPIOXINT1SEL           | XINT1CR                 | XINT1CTR                |

| XINT2     | GPIOXINT2SEL           | XINT2CR                 | XINT2CTR                |

| XINT3     | GPIOXINT3SEL           | XINT3CR                 | XINT3CTR                |

- ◆ Pin Selection Register chooses which pin(s) the signal comes out on

- ◆ Configuration Register controls the enable/disable and polarity

- ◆ Counter Register holds the interrupt counter

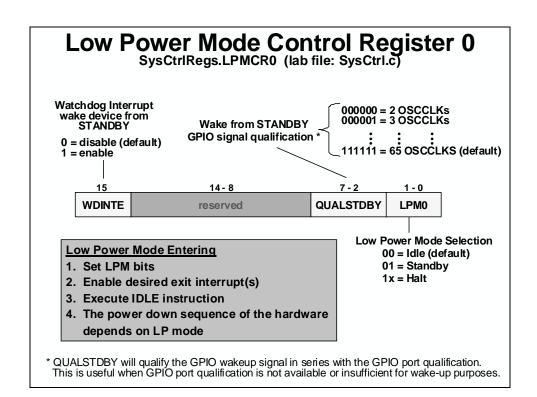

### **Low Power Modes**

# **Low Power Modes**

| Low Power<br>Mode | CPU Logic<br>Clock | Peripheral<br>Logic Clock | Watchdog<br>Clock | PLL /<br>OSC |

|-------------------|--------------------|---------------------------|-------------------|--------------|

| Normal Run        | on                 | on                        | on                | on           |

| IDLE              | off                | on                        | on                | on           |

| STANDBY           | off                | off                       | on                | on           |

| HALT              | off                | off                       | off               | off          |

See device datasheet for power consumption in each mode

# **Low Power Mode Exit**

| Exit<br>Interrupt<br>Low Power<br>Mode | RESET | GPIO<br>Port A<br>Signal | Watchdog<br>Interrupt | Any<br>Enabled<br>Interrupt |

|----------------------------------------|-------|--------------------------|-----------------------|-----------------------------|

| IDLE                                   | yes   | yes                      | yes                   | yes                         |

| STANDBY                                | yes   | yes                      | yes                   | no                          |

| HALT                                   | yes   | yes                      | no                    | no                          |

# **GPIO Low Power Wakeup Select**SysCtrlRegs.GPIOLPMSEL

Wake device from HALT and STANDBY mode (GPIO Port A)

0 = disable (default)

1 = enable

# **Register Protection**

# **Write-Read Protection**

DevEmuRegs.DEVICECNF.bit.ENPROT

Suppose you need to write to a peripheral register and then read a different register for the same peripheral (e.g., write to control, read from status register)?

- CPU pipeline protects W-R order for the same address

- Write-Read protection mechanism protects W-R order for different addresses

- Peripheral Frame 1 and Peripheral Frame 2 zones protected

- Write-read protection mode bit ENPROT located in the DEVICECNF register is enabled by default

| Peripheral Frame Registers |                |  |

|----------------------------|----------------|--|

| PF0 PF1                    |                |  |

| eCAN                       | System Control |  |

| COMP                       | SPI            |  |

| ePWM                       | SCI            |  |

| eCAP                       | Watchdog       |  |

| eQEP                       | XINT           |  |

| LIN                        | ADC            |  |

| GPIO                       | 12C            |  |

Protected address: 0x4000 - 0x7FFF

# **EALLOW Protection** (1 of 2)

- **♦** EALLOW stands for *Emulation Allow*

- ◆ Code access to protected registers allowed only when EALLOW = 1 in the ST1 register

- The emulator can always access protected registers

- EALLOW bit controlled by assembly level instructions

- 'EALLOW' sets the bit (register access enabled)

- 'EDIS' clears the bit (register access disabled)

- EALLOW bit cleared upon ISR entry, restored upon exit

# **EALLOW Protection** (2 of 2)

### The following registers are protected:

**Device Emulation**

Flash

**Code Security Module**

**PIE Vector Table**

LIN (some registers)

eCANA/B (control registers only; mailbox RAM not protected)

ePWM1-7 and COMP1-3 (some registers)

**GPIO** (control registers only)

**System Control**

See device datasheet and peripheral users guides for detailed listings

### **EALLOW register access C-code example:**

```

asm(" EALLOW"); // enable protected register access

SysCtrlRegs.WDKEY=0x55; // write to the register

asm(" EDIS"); // disable protected register access

```

# **Lab 5: System Initialization**

### Objective

The objective of this lab is to perform the processor system initialization. Additionally, the peripheral interrupt expansion (PIE) vectors will be initialized and tested using the information discussed in the previous module. This initialization process will be used again in all of the lab exercises throughout this workshop. The system initialization for this lab will consist of the following:

- Setup the clock module PLL, LOSPCP = /4, low-power modes to default values, enable all module clocks

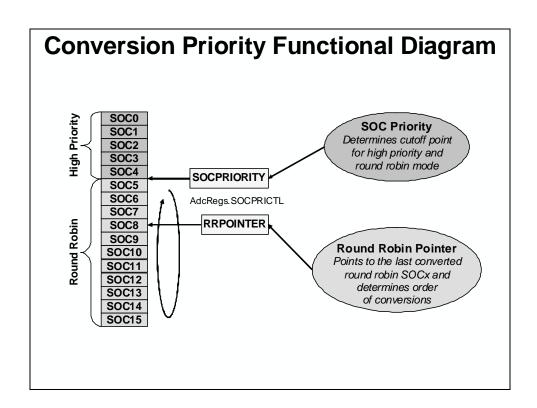

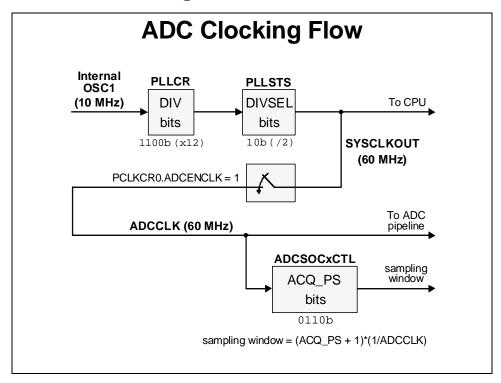

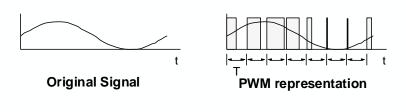

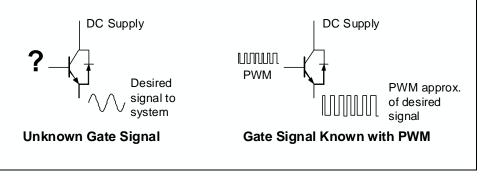

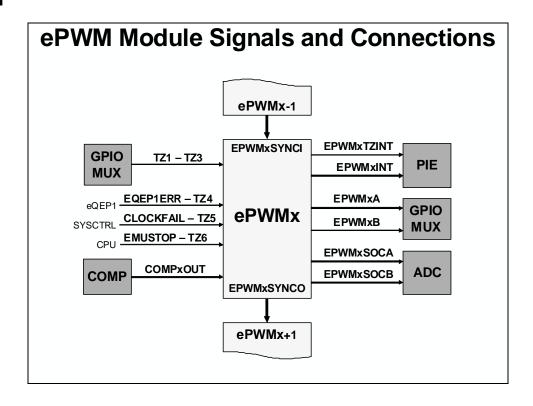

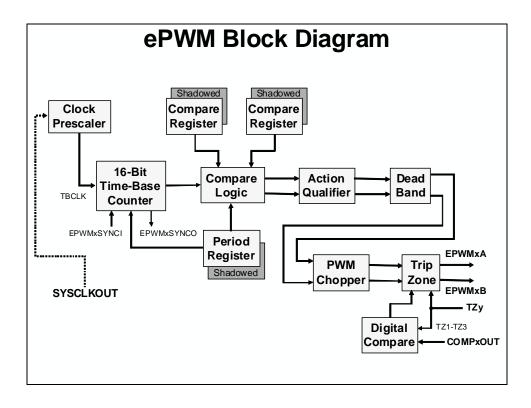

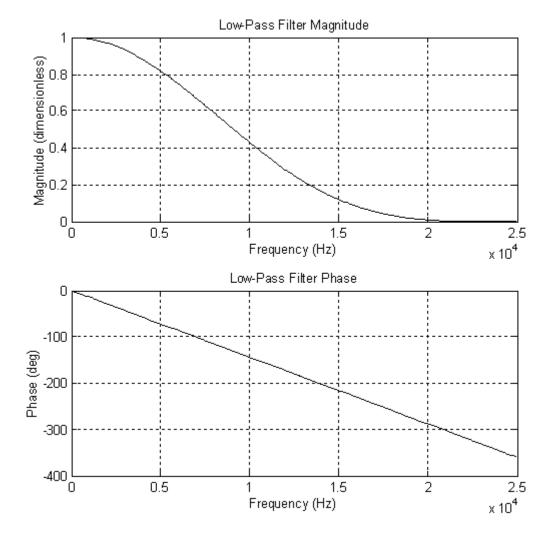

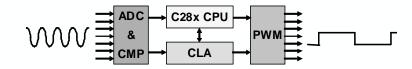

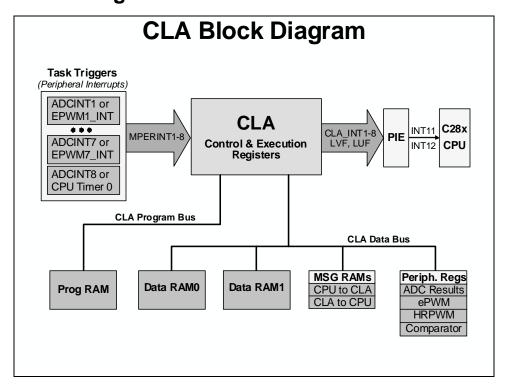

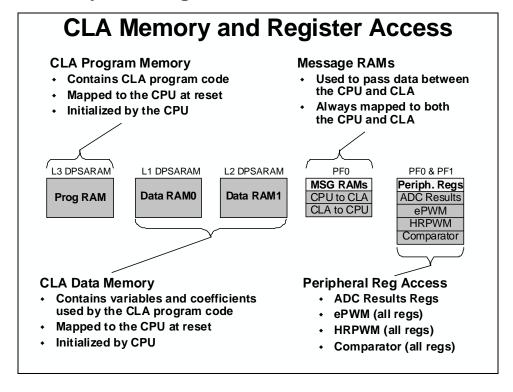

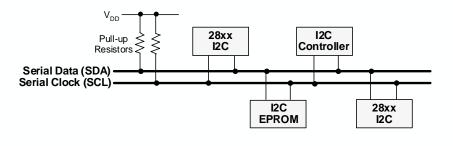

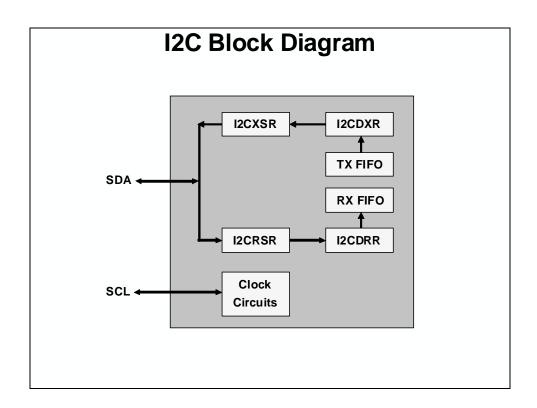

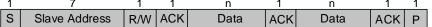

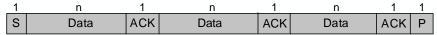

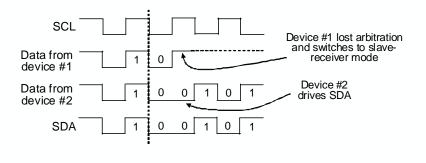

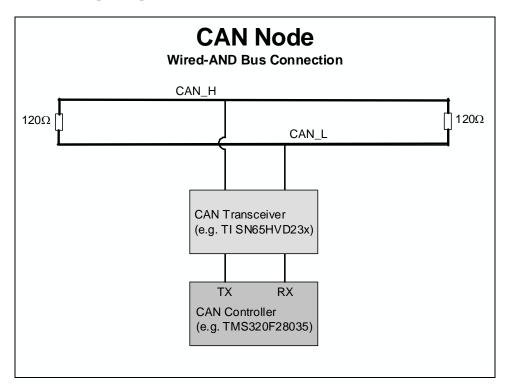

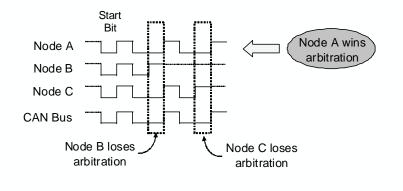

- Disable the watchdog clear WD flag, disable watchdog, WD prescale = 1