# PCILynx 1394 to PCI Bus Interface TSB12LV21BPGF Functional Specification

SCPA020A April 1999

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1999, Texas Instruments Incorporated

| 1.1       Scope of Document         1.2       Feature Set         1.3       Applicable Documents         2       Performance Requirements         3.1       Packaging Requirements         3.2       Pin Assignment Requirements         4       Hardware Functional Description         4.1       System Overview         4.2.1       PCI Bus Logic         4.2.2       DNA Logic         4.2.3       FIFO Overun and Underrun         4.2.4       FIFO Logic         4.2.5       1394 Link Layer Logic         4.2.5       1394 Link Layer Logic         5       Hardware Register Definitions         5.1       Memory and Configuration Address Space Register Map         5.1       Memory and Configuration Address Space Register Definitions         5.2       PCI Configuration and Miscellaneous Register Definitions         5.2.1       Device-Vendr ID @000         5.2.2       Class Code – Revision ID @008         5.2.3       Class Code – Revision ID @008         5.2.4       Header Type-Latency Timer-Cache Line Size @000         5.2.5       Memory Access Base Address 0 – PCILym Internal Registers @010         6       5.2.6       Memory Access Base Address 0 – PCILym Internal Registers @010 <th>1</th> <th>Introd</th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1 | Introd |          |                                                                      |     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------|----------|----------------------------------------------------------------------|-----|

| 1.3       Applicable Documents         2       Performance Requirements         3.1       Packaging Requirements         3.2       Pin Assignment Requirements         4       Hardware Functional Description         4.1       System Overview         4.2       ASIC Functional Partitioning         4.2.3       FIFO Overrue and Underrun         4.2.4       TFIC Dogic         4.2.5       1394 Link Layer Logic         4.2.4       FIFO Logic         4.2.5       1394 Link Layer Logic         5       Hardware Register Definitions         6       5.1         7       Hardware Register Definitions         6       5.2         7       Class Code – Revision ID @000         5.2.3       Class Code – Revision ID @000         5.2.4       Header Type-Latency Timer-Cache Line Size @00C         5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010         6       5.2.6         6.2.7       Memory Access Base Address 2 – AUX Port @018         5.2.8       Subsystem ID @02C         5.2.9       Expansion ROM Base Address 2 – AUX Port @018         5.2.1       Max Latency–Min, Grant–IntPin–Int_Line Register @03C         5.2.10 <th></th> <th>1.1</th> <th>Scope of</th> <th>of Document</th> <th>. 1</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   | 1.1    | Scope of | of Document                                                          | . 1 |

| 2         Performance Requirements           31         Packaging Requirements           32         Pin Assignment Requirements           41         System Overview           42         ASIC Functional Partitioning           42.1         System Overview           42.2         DMA Logic           42.4         ASIC Functional Partitioning           42.2         DMA Logic           42.2         SIFIP Overrun and Underrun           42.4         FIFO Logic           42.4         SIFIP Overrun and Underrun           42.5         1394 Link Layer Logic           5         Hardware Register Definitions           6         5.1           5.1         Memory and Configuration Address Space Register Map           5.2         PCI Configuration and Miscellaneous Register Definitions           6         5.2.1         Device-Vendor ID @000           5.2.2         Class Code – Revisin ID @008           5.2.3         Class Code – Revisin ID @008           5.2.4         Header Type-Latency Timer-Cache Line Size @00C           5.2.5         Memory Access Base Address 0 – PCILynx Internal Registers @010           6         5.2.6         Memory Access Base Address 2 – AUX Port @018           6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | 1.2    | Feature  | Set                                                                  | . 1 |

| 3         Mechanical Requirements           3.1         Piackaging Requirements           3.2         Pin Assignment Requirements           4         Hardware Functional Description           4.1         System Overview           4.2         ASIC Functional Partitioning           4.2.1         PCI Bus Logic           4.2.2         DMA Logic           4.2.3         FIFO Overrun and Underrun           4.2.4         FIFO Logic           4.2.5         1394 Link Layer Logic           5         Hardware Register Definitions           6         5.1           5.1         Memory and Configuration Address Space Register Map           6.1         Memory and Miscellaneous Register Definitions           6         5.2.1         Device-Vendor ID @000           5.2.2         Class Code – Revision ID @008           6.2.3         Class Code – Revision ID @008           5.2.4         Header Type-Latency Timer-Cache Line Size @00C           5.2.5         Memory Access Base Address 1 – External RAM Port @014           6         5.2.6           5.2.7         Memory Access Base Address 2 – AUX Port @014           5.2.8         Subsystem ID @02C           5.2.1         Miscellaneous Control @044                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   | 1.3    | Applical | ole Documents                                                        | . 2 |

| 3         Mechanical Requirements           3.1         Piackaging Requirements           3.2         Pin Assignment Requirements           4         Hardware Functional Description           4.1         System Overview           4.2         ASIC Functional Partitioning           4.2.1         PCI Bus Logic           4.2.2         DMA Logic           4.2.3         FIFO Overrun and Underrun           4.2.4         FIFO Logic           4.2.5         1394 Link Layer Logic           5         Hardware Register Definitions           6         5.1           5.1         Memory and Configuration Address Space Register Map           6.1         Memory and Miscellaneous Register Definitions           6         5.2.1         Device-Vendor ID @000           5.2.2         Class Code – Revision ID @008           6.2.3         Class Code – Revision ID @008           5.2.4         Header Type-Latency Timer-Cache Line Size @00C           5.2.5         Memory Access Base Address 1 – External RAM Port @014           6         5.2.6           5.2.7         Memory Access Base Address 2 – AUX Port @014           5.2.8         Subsystem ID @02C           5.2.1         Miscellaneous Control @044                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2 | Perfor | mance F  | Requirements                                                         | . 3 |

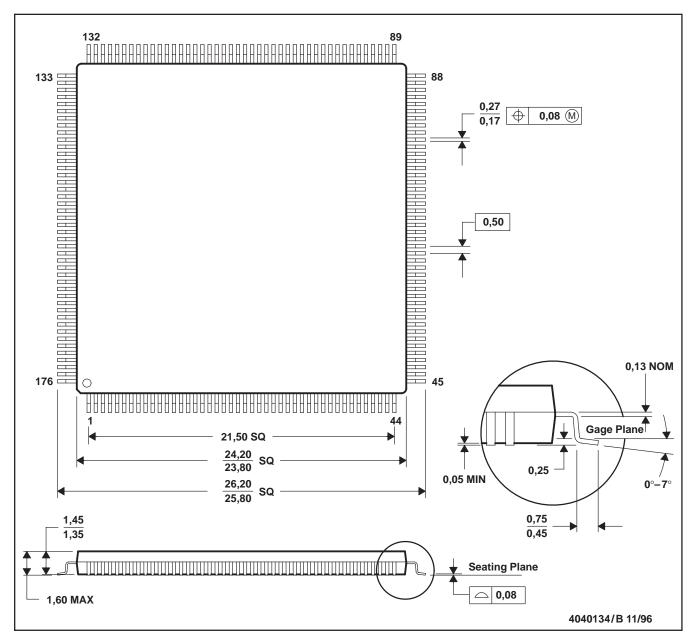

| 3.1       Packaging Requirements         3.2       Pin Assignment Requirements         4       Hardware Functional Description         4.1       System Overview         4.2       ASIC Functional Partitioning         4.2.1       PCI Bus Logic         4.2.2       DMA Logic         4.2.3       FIFO Overrun and Underrun         4.2.4       FIFO Logic         4.2.5       1394 Link Layer Logic         5       Hardware Register Definitions         6       1.1         Memory and Configuration Address Space Register Map         6.1       Device-Vendor ID @000         5.2       PCI Configuration and Miscellaneous Register Definitions         6       5.2         S.2.1       Device-Vendor ID @000         6       5.2.3         Class Code – Revision ID @008         5.2.3       Class Code – Revision ID @008         6       5.2.4         Fuedor Type-Latency TImer-Cache Llne Size @00C         6       5.2.5         Memory Access Base Address 0 – PCLlynx Internal Registers @010         6       5.2.6         Memory Access Base Address @030         5.2.8       Subsystem ID @02C         6       5.2.8     <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |        |          | •                                                                    |     |

| 3.2 Pin Assignment Requirements         4 Hardware Functional Description         4.1 System Overview         4.2 ASIC Functional Partitioning         4.2.1 PCI Bus Logic         4.2.2 DMA Logic         4.2.2 DMA Logic         4.2.3 FIFO Overrun and Underrun         4.2.4 FIFO Logic         4.2.5 1394 Link Layer Logic         5         Fardware Register Definitions         6         5.1 Memory and Configuration Address Space Register Map         5.2 PCI Configuration and Miscellaneous Register Definitions         6         5.2 PCI Configuration and Miscellaneous Register Definitions         6         5.2.1 Device-Vendor ID @000         6         5.2.2 Command – Status @004         6         5.2.3 Class Code – Revision ID @008         5.2.4 Header Type-Latency Timer-Cache Line Size @00C         5.2.5 Memory Access Base Address 0 – PCLlynk Internal Registers @010         6       5.2.6 Memory Access Base Address 0 – PCLLynk Internal Register @014         6.2.7 Memory Access Base Address @030         6.2.8 Subsystem ID @02C         6       5.2.10 Max_Latency-Ming Grant-Int_Line Register @03C         5.2.11 Miscellaneous Control @044         5.2.13 PCI Interrupt Status @048                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 3 |        |          |                                                                      |     |

| 4         Hardware Functional Description           4.1         System Overview           4.2         ASIC Functional Partitioning           4.2.1         PCI Bus Logic           4.2.2         DMA Logic           4.2.3         FIFO Overrun and Underrun           4.2.4         FIFO Logic           4.2.5         1394 Link Layer Logic           5         Hardware Register Definitions           6         1           5.1         Memory and Configuration Address Space Register Map           5.2         PCI Configuration and Miscellaneous Register Definitions           5.2.1         Device-Vendor ID @000           5.2.2         Command – Status @004           5.2.3         Class Code – Revision ID @008           5.2.4         Header Type-Latency Timer-Cache Line Size @00C           5.2.5         Memory Access Base Address 0 – PCILynx Internal Registers @010           5.2.6         Memory Access Base Address 2 – AUX Port @018           5.2.7         Memory Access Base Address 2 – AUX Port @018           5.2.8         Subsystem ID @02C           6         S.2.9           5.2.10         Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C           5.2.11         Miscellateneous Control @040           5.2.13<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |   |        |          |                                                                      |     |

| 4.1       System Overview         4.2       ASIC Functional Partitioning         4.2.1       PCI Bus Logic         4.2.2       DMA Logic         4.2.3       FIFO Overrun and Underrun         4.2.4       FIFO Logic         4.2.5       1394 Link Layer Logic         5       Hardware Register Definitions         6       5.1         Memory and Configuration Address Space Register Map         6.2       PCI Configuration and Miscellaneous Register Definitions         6.2.1       Device-Vendor ID @000         5.2.2       Command - Status @004         6.5.2.3       Class Code – Revision ID @008         5.2.4       Header Type-Latency Timer-Cache Line Size @00C         5.2.5       Memory Access Base Address 0 – PCLynx Internal Registers @010         6.5.2.6       Memory Access Base Address 0 – PCLynx Internal Registers @010         6.5.2.7       Memory Access Base Address 0 – PCLynx Internal Register @018         5.2.8       Subsystem ID @02C         6.5.2.9       Expansion ROM Base Address @030         5.2.10       Mac Latency-Min_Grant-IntPin-Int_Line Register @03C         5.2.11       Miscellaneous Control @044         5.2.12       Serial EEPROM Control @044         5.2.13       PCI CHO[1-0] Cont                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |        |          |                                                                      |     |

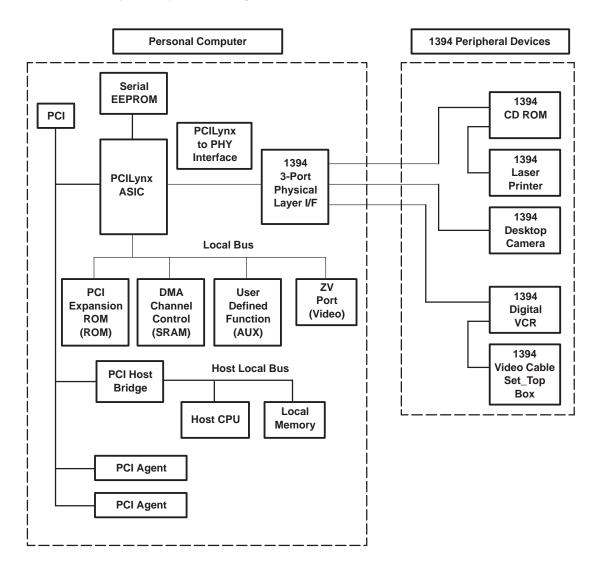

| 4.2       ASIC Functional Partitioning         4.2.1       PCI Bus Logic         4.2.2       DMA Logic         4.2.3       FIFO Overrun and Underrun         4.2.4       FIFO Overrun and Underrun         4.2.5       1394 Link Layer Logic         5       Hardware Register Definitions       6         5.1       Memory and Configuration Address Space Register Map       6         5.2       PCI Configuration and Miscellaneous Register Definitions       6         5.2.1       Device-Vendor ID @000       6         5.2.2       Command – Status @004       6         5.2.3       Class Code – Revision ID @008       6         5.2.4       Header Type-Latency TImer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 1 – External RAM Port @014       6         5.2.6       Memory Access Base Address 2 – AUX Port @018       6         5.2.8       Subsystem ID @02C       6         5.2.9       Expansion ROM Base Address @030       6         5.2.10       Max_Latency-Min_Grant-IntPin-Int_Line Register @03C       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Enable @04C       7         5.2.15       PCI aeplO[1-0] Contr                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4 | Hardw  |          |                                                                      |     |

| 4.2.1       PCI Bus Logic       2         4.2.2       DMA Logic       2         4.2.3       FIFO Overrun and Underrun       2         4.2.4       FIFO Logic       4         4.2.5       1394 Link Layer Logic       5         5       Hardware Register Definitions       6         5.1       Memory and Configuration Address Space Register Map       6         5.2       PCI Configuration and Miscellaneous Register Definitions       6         5.2.1       Device-Vendor ID @000       6         5.2.2       Command – Status @004       6         5.2.3       Class Code – Revision ID @008       6         5.2.4       Header Type-Latency Timer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.6       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.7       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.4       Header Type-Latency Timer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.6       Memory Access Base Address 0 – PCILynx Internal Register @014       6         5.2.10       M                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |        |          |                                                                      |     |

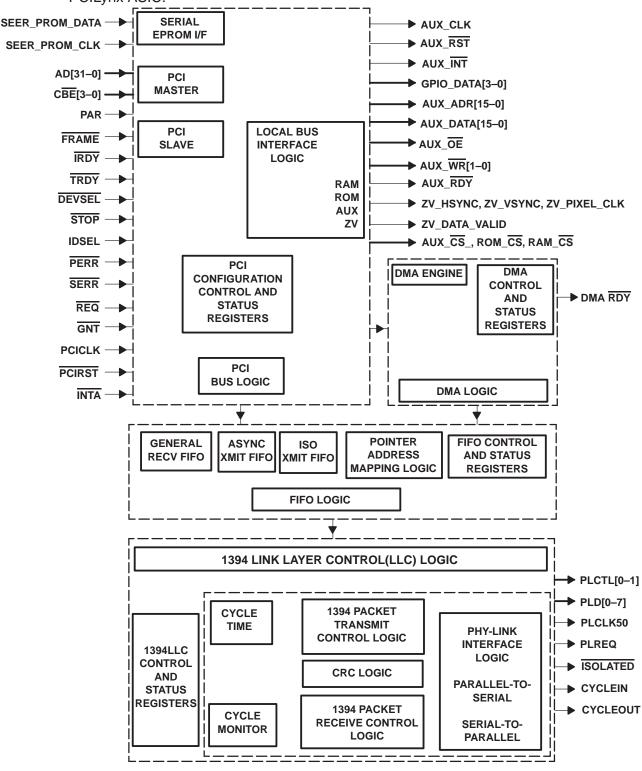

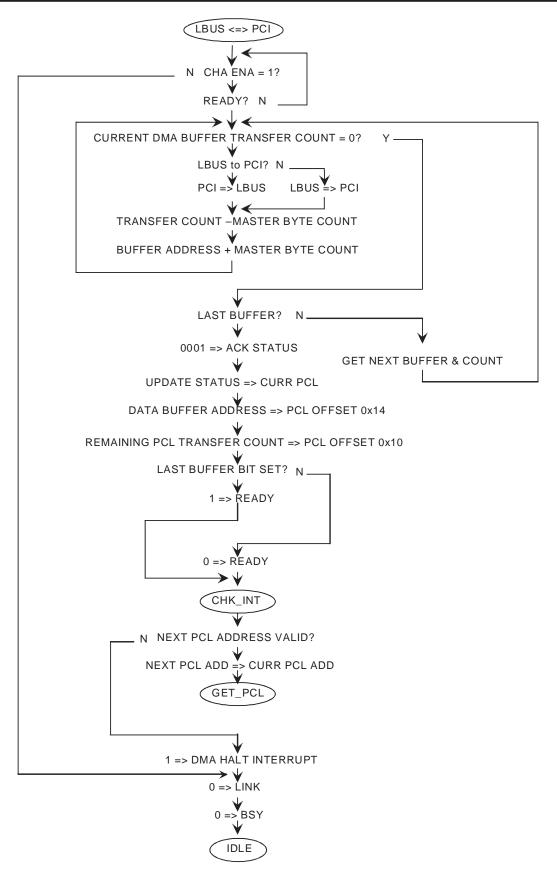

| 4.2.2       DMA Logic       2         4.2.3       FIFO Overrun and Underrun       2         4.2.4       FIFO Logic       4         4.2.5       1394 Link Layer Logic       5         5       Hardware Register Definitions       6         5.1       Memory and Configuration Address Space Register Map       6         5.2       PCI Configuration and Miscellaneous Register Definitions       6         5.2.1       Device-Vendor ID @000       6         5.2.2       Command – Status @004       6         5.2.3       Class Code – Revision ID @008       6         5.2.4       Header Type-Latency Timer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 1 – External RAM Port @014       6         5.2.6       Memory Access Base Address 2 – AUX Port @018       6         5.2.9       Expansion ROM Base Address @030       6         5.2.10       Max_Latency-Min_Grant-IntPin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.13       Serial EEPROM Control @048       7         5.2.14       PCI Interrupt Status @048       7         5.2.15       PCI Test Register @050       7         5.2.14       PCI Interru                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   | 4.2    |          | •                                                                    |     |

| 4.2.3       FIFO Overrun and Underrun       2         4.2.4       FIFO Logic       4         4.2.5       1394 Link Layer Logic       5         5       Hardware Register Definitions       6         5.1       Memory and Configuration Address Space Register Map       6         5.2       PCI Configuration and Miscellaneous Register Definitions       6         5.2       PCI Configuration and Miscellaneous Register Definitions       6         5.2.2       Command – Status @004       6         5.2.3       Class Code – Revision ID @008       6         5.2.4       Header Type-Latency Timer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.6       Memory Access Base Address 2 – AUX Port @018       6         5.2.7       Memory Access Base Address 2 – AUX Port @014       6         5.2.10       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EPROM Control @044       7         5.2.14       PCI Interrupt Status @046       7         5.2.15       PCI rest Register @050       7         5.2.16       Local Bus Control Register @084                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |        |          |                                                                      |     |

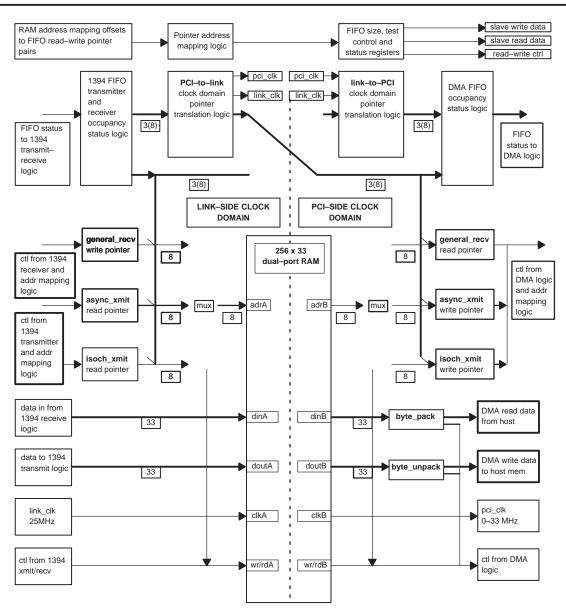

| 4.2.4       FIFO Logic       4         4.2.5       1394 Link Layer Logic       5         5       Hardware Register Definitions       6         5.1       Memory and Configuration Address Space Register Definitions       6         5.2       PCI Configuration and Miscellaneous Register Definitions       6         5.2.1       Device-Vendor ID @000       6         5.2.2       Command – Status @004       6         5.2.3       Class Code – Revision ID @008       6         5.2.4       Header Type-Latency TImer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.6       Memory Access Base Address 1 – External RAM Port @014       6         5.2.7       Memory Access Base Address 2 – AUX Port @018       6         5.2.8       Subsystem ID @02C       6         5.2.9       Expansion ROM Base Address @030       6         5.2.10       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Enable @04C       7         5.2.17       Local Bus Control Register @0B0 (ROM, RAM, AUX, and ZV r                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |        |          |                                                                      |     |

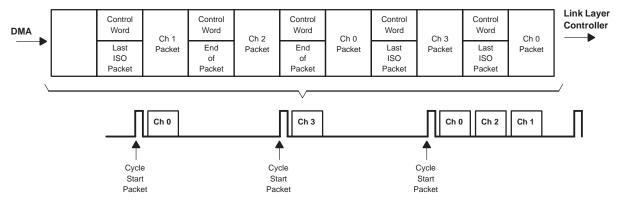

| 42.5       1394 Link Layer Logic       5         5       Hardware Register Definitions       6         5.1       Memory and Configuration Address Space Register Map       6         5.2       PCI Configuration and Miscellaneous Register Definitions       6         5.2.1       Device-Vendor ID @000       6         5.2.2       Command – Status @004       6         5.2.3       Class Code – Revision ID @008       6         5.2.4       Header Type-Latency Timer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.6       Memory Access Base Address 2 – AUX Port @018       6         5.2.7       Memory Access Base Address 2 – AUX Port @018       6         5.2.8       Subsystem ID @02C       6         5.2.10       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Status @048       7         5.2.15       PCI GPIO[3-2] Control Register @080       7         5.2.16       Local Bus Address Register @0808       7 <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |        |          |                                                                      |     |

| <ul> <li>5 Hardware Register Definitions</li> <li>5.1 Memory and Configuration Address Space Register Map</li> <li>5.2 PCI Configuration and Miscellaneous Register Definitions</li> <li>5.2.1 Device-Vendro ID @000</li> <li>5.2.2 Command – Status @004</li> <li>6.2.3 Class Code – Revision ID @008</li> <li>5.2.4 Header Type-Latency TImer-Cache Line Size @00C</li> <li>5.2.5 Memory Access Base Address 0 – PCILynx Internal Registers @010</li> <li>5.2.6 Memory Access Base Address 1 – External RAM Port @014</li> <li>5.2.7 Memory Access Base Address 2 – AUX Port @018</li> <li>5.2.8 Subsystem ID @02C</li> <li>5.2.9 Expansion ROM Base Address @030</li> <li>5.2.10 Max_Latency–Min_Grant–Int_Pin–Int_Line Register @03C</li> <li>5.2.11 Miscellaneous Control @044</li> <li>5.2.13 PCI Interrupt Status @048</li> <li>7.2.13 PCI Interrupt Status @048</li> <li>7.2.14 PCI Interrupt Status @048</li> <li>7.2.15 PCI Test Register @050</li> <li>7.2.16 Local Bus Control Register @0B0 {ROM, RAM, AUX, and ZV registers}</li> <li>7.2.17 Local Bus Address Register @0B0 {ROM, RAM, AUX, and ZV registers}</li> <li>7.2.18 PCI_GPIO[3-2] Control Register A @0B8</li> <li>7.2.19 PCI_GPIO[3-2] Control Register A @0B8</li> <li>7.2.19 DCI_GPIO DATA Read-Write Ports @0C0 through @0FC</li> <li>7.3.1 DMA Channel 0 through 4 – Previous Packet Control List Address/Temp</li> <li>@100, 120, 140, 160, 180</li> <li>7.3.2 DMA Channel 0 through 4 – Current Packet Control List Address</li> <li>@104, 124, 144, 164, 184</li> <li>7.3.3 DMA Channel 0 through 4 – DMA Channel Status @108, 128, 148, 168, 188</li> <li>5.3.4 DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170, 190</li> <li>8 5.3.5 DMA Channel 0 through 4 – DMA Ready Register @114, 134, 154, 174, 194</li> </ul> |   |        |          | •                                                                    |     |

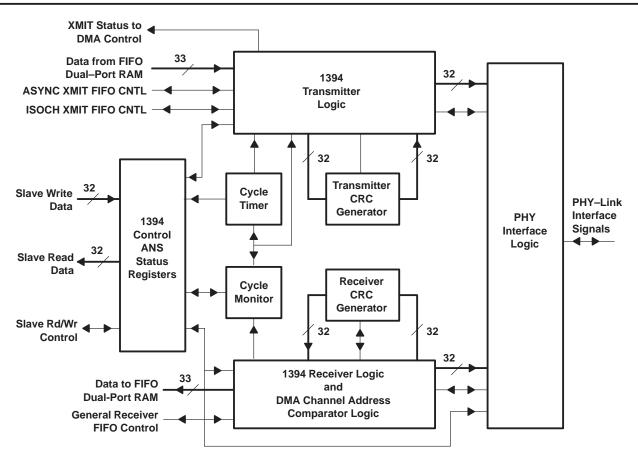

| 5.1       Memory and Configuration Address Space Register Map       6         5.2       PCI Configuration and Miscellaneous Register Definitions       6         5.2.1       Device-Vendor ID @000       6         5.2.2       Command – Status @004       6         5.2.3       Class Code – Revision ID @008       6         5.2.4       Header Type-Latency Timer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.6       Memory Access Base Address 1 – External RAM Port @014       6         5.2.7       Memory Access Base Address 2 – AUX Port @018       6         5.2.8       Subsystem ID @02C       6         5.2.9       Expansion ROM Base Address @030       6         5.2.10       Max_Latency-Min_Grant-IntPin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @044       7         5.2.12       Serial EEPROM Control @044       7         5.2.14       PCI Interrupt Status @048       7         5.2.15       PCI Register @050       7         5.2.16       Local Bus Control Register @018 (ROM, RAM, AUX, and ZV registers)       7         5.2.19       PCI_GPIO[1-0] Control Register @018       7         5.2.10 <t< th=""><th></th><th></th><th>4.2.5</th><th>1394 Link Layer Logic</th><th>53</th></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |        | 4.2.5    | 1394 Link Layer Logic                                                | 53  |

| 5.2       PCI Configuration and Miscellaneous Register Definitions       6         5.2.1       Device-Vendor ID @000       6         5.2.2       Command – Status @004       6         5.2.3       Class Code – Revision ID @008       6         5.2.4       Header Type-Latency TImer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.6       Memory Access Base Address 2 – AUX Port @018       6         5.2.7       Memory Access Base Address 2 – AUX Port @018       6         5.2.8       Subsystem ID @02C       6         5.2.9       Expansion ROM Base Address @030       5         5.2.10       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Enable @04C       7         5.2.15       PCI Test Register @050       7         5.2.16       Local Bus Address Register @0B4       7         5.2.19       PCI_GPIO[1–0] Control Register B @0BC       7         5.2.19       PCI_GPIO[2–2] Control Register B @0BC       7 <th>5</th> <th>Hardw</th> <th>vare Reg</th> <th>ister Definitions</th> <th>62</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 5 | Hardw  | vare Reg | ister Definitions                                                    | 62  |

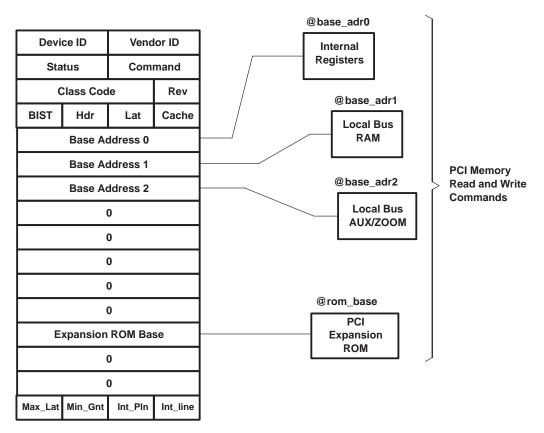

| 5.2.1       Device-Vendor ID @000       6         5.2.2       Command – Status @004       6         5.2.3       Class Code – Revision ID @008       6         5.2.4       Header Type-Latency TImer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.6       Memory Access Base Address 1 – External RAM Port @014       6         5.2.7       Memory Access Base Address 2 – AUX Port @018       6         5.2.8       Subsystem ID @02C       6         5.2.9       Expansion ROM Base Address @030       6         5.2.10       Max Latency-Min Grant-Int_Pin-Int_Line Register @03C       7         5.2.13       PCI Interrupt Status @044       7         5.2.14       PCI Interrupt Status @048       7         5.2.15       PCI Interrupt Enable @04C       7         5.2.17       Local Bus Control Register @0B0 {ROM, RAM, AUX, and ZV registers}       7         5.2.17       Local Bus Address Register @0B4       7         5.2.18       PCI_GPIO[1-0] Control Register A @0B8       7         5.2.19       PCI_GPIO[3-2] Control Register A @0B8       7         5.2.19       PCI_GPIO[3-2] Control Register A @0B8       7         5.2.19       PCI_GPIO[3-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 5.1    |          |                                                                      |     |

| 5.2.2       Command – Status @004       6         5.2.3       Class Code – Revision ID @008       6         5.2.4       Header Type-Latency Timer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.6       Memory Access Base Address 1 – External RAM Port @014       6         5.2.7       Memory Access Base Address 2 – AUX Port @018       6         5.2.8       Subsystem ID @02C       6         5.2.9       Expansion ROM Base Address @030       6         5.2.10       Max Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Enable @04C       7         5.2.15       PCI Test Register @050       7         5.2.16       Local Bus Control Register @084       7         5.2.17       Local Bus Control Register @084       7         5.2.18       PCI_GPIO[1–0] Control Register A @088       7         5.2.19       PCI_GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Co                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   | 5.2    | PCI Cor  | nfiguration and Miscellaneous Register Definitions                   | 66  |

| 5.2.3       Class Code – Revision ID @008       6         5.2.4       Header Type-Latency Timer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.6       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.7       Memory Access Base Address 2 – AUX Port @018       6         5.2.8       Subsystem ID @02C       6         5.2.9       Expansion ROM Base Address @030       6         5.2.10       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Enable @04C       7         5.2.17       Local Bus Control Register @050       7         5.2.18       PCI_GPIO[1-0] Control Register @084       7         5.2.19       PCI_GPIO[2]-2] Control Register B @08C       7         5.2.19       PCI_GPIO[1-0] Control Register B @08C       7         5.2.19       PCI_GPIO[1-0] Control Register Definitions       7         5.2.10       PCI BPIO DATA Read-Write Ports @0CO through @0FC       7         5.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |        |          |                                                                      |     |

| 5.2.4       Header Type-Latency Timer-Cache Line Size @00C       6         5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.6       Memory Access Base Address 1 – External RAM Port @014       6         5.2.7       Memory Access Base Address 2 – AUX Port @018       6         5.2.8       Subsystem ID @02C       6         5.2.9       Expansion ROM Base Address @030       6         5.2.10       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Enable @04C       7         5.2.15       PCI Test Register @050       7         5.2.16       Local Bus Control Register @0B0 (ROM, RAM, AUX, and ZV registers)       7         5.2.17       Local Bus Control Register @0B4       7         5.2.19       PCI_GPIO[1-0] Control Register B @0BC       7         5.2.10       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       @104, 124, 144, 164, 184       7         5.3.2       DMA Channel 0 through 4 –                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |        |          |                                                                      |     |

| 5.2.5       Memory Access Base Address 0 – PCILynx Internal Registers @010       6         5.2.6       Memory Access Base Address 1 – External RAM Port @014       6         5.2.7       Memory Access Base Address 2 – AUX Port @018       6         5.2.8       Subsystem ID @02C       6         5.2.9       Expansion ROM Base Address @030       6         5.2.10       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Status @048       7         5.2.15       PCI Test Register @050       7         5.2.16       Local Bus Control Register @0B0 {ROM, RAM, AUX, and ZV registers}       7         5.2.12       Local Bus Address Register @0B4       7         5.2.18       PCI_GPIO[1-0] Control Register A @0B8       7         5.2.19       PCI_GPIO[2-2] Control Register B @0BC       7         5.2.10       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       @100, 120, 140, 160, 180       7         5.3.2       DMA Channel 0 through 4 – Current                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |   |        |          |                                                                      |     |

| 5.2.6       Memory Access Base Address 1 – External RAM Port @014       6         5.2.7       Memory Access Base Address 2 – AUX Port @018       6         5.2.8       Subsystem ID @02C       6         5.2.9       Expansion ROM Base Address @030       6         5.2.10       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Enable @04C       7         5.2.15       PCI Test Register @050       7         5.2.16       Local Bus Control Register @0B4       7         5.2.17       Local Bus Address Register @0B4       7         5.2.19       PCI_GPIO[1–0] Control Register A @0B8       7         5.2.19       PCI_GPIO[3–2] Control Register B @0BC       7         5.2.19       PCI_GPIO[3–2] Control Register Definitions       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       @100, 120, 140, 160, 180       7         5.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       @104, 124, 144, 164, 184       7         5.3.3       DMA Channel 0 through 4 – Current D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |   |        |          |                                                                      |     |

| 5.2.7       Memory Access Base Address 2 – AUX Port @018       6         5.2.8       Subsystem ID @02C       6         5.2.9       Expansion ROM Base Address @030       6         5.2.0       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.10       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Enable @04C       7         5.2.15       PCI Test Register @050       7         5.2.16       Local Bus Control Register @0B0 {ROM, RAM, AUX, and ZV registers}       7         5.2.17       Local Bus Address Register @0B4       7         5.2.18       PCI_GPIO[1–0] Control Register A @0B8       7         5.2.19       PCI_GPIO[3–2] Control Register A @0BC       7         5.2.19       PCI_GPIO[3–2] Control Register B @0BC       7         5.2.10       DAC Ananel 0 through 4 – Previous Packet Control List Address/Temp       7         6.3.1       DMA Channel 0 through 4 – Current Packet Control List Address       @100, 120, 140, 160, 180       7         5.3.2       DMA Channel 0 through 4 – Current Data Buffer A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |        |          |                                                                      |     |

| 5.2.8       Subsystem ID @02C       6         5.2.9       Expansion ROM Base Address @030       6         5.2.10       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Enable @04C       7         5.2.15       PCI Test Register @050       7         5.2.16       Local Bus Control Register @0B0 {ROM, RAM, AUX, and ZV registers}       7         5.2.16       Local Bus Control Register @0B4       7         5.2.17       Local Bus Address Register @0B4       7         5.2.18       PCI_GPIO[1-0] Control Register A @0B8       7         5.2.19       PCI_GPIO[3-2] Control Register B @0BC       7         5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       @100, 120, 140, 160, 180       7         5.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       @104, 124, 144, 164, 184       7         5.3.3       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C       8         5.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |        |          |                                                                      |     |

| 5.2.9       Expansion ROM Base Address @030       6         5.2.10       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Status @048       7         5.2.15       PCI Interrupt Enable @04C       7         5.2.16       Local Bus Control Register @050       7         5.2.17       Local Bus Control Register @0B4       7         5.2.18       PCI_GPIO[1-0] Control Register A @0B8       7         5.2.19       PCI_GPIO[3-2] Control Register B @0BC       7         5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       @100, 120, 140, 160, 180       7         5.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       @104, 124, 144, 164, 184       7         5.3.3       DMA Channel 0 through 4 – Current Data Buffer Address @108, 128, 148, 168, 188       8         5.3.4       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C       8         5.3.5       DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |        |          | •                                                                    |     |

| 5.2.10       Max_Latency-Min_Grant-Int_Pin-Int_Line Register @03C       6         5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Status @048       7         5.2.15       PCI Interrupt Enable @04C       7         5.2.16       Local Bus Control Register @050       7         5.2.17       Local Bus Control Register @0B0 {ROM, RAM, AUX, and ZV registers}       7         5.2.18       PCI_GPIO[1-0] Control Register @0B4       7         5.2.19       PCI_GPIO[3-2] Control Register A @0B8       7         5.2.19       PCI_GPIO[3-2] Control Register B @0BC       7         5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3.1       DMA Channel 0 through 4 - Previous Packet Control List Address/Temp       0         @100, 120, 140, 160, 180       7       7       7         5.3.2       DMA Channel 0 through 4 - Current Packet Control List Address       0         @104, 124, 144, 164, 184       7       7         5.3.3       DMA Channel 0 through 4 - Current Data Buffer Address @108, 128, 148, 168, 188       8         5.3.4       DMA Channel 0 through 4 - DMA Channel Status @                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |        |          |                                                                      |     |

| 5.2.11       Miscellaneous Control @040       7         5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Enable @04C       7         5.2.15       PCI Test Register @050       7         5.2.16       Local Bus Control Register @0B0 {ROM, RAM, AUX, and ZV registers}       7         5.2.17       Local Bus Address Register @0B4       7         5.2.18       PCI_GPI0[1–0] Control Register A @0B8       7         5.2.19       PCI_GPI0[3–2] Control Register B @0BC       7         5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.2.31       DMA Control and Status Register Definitions       7         5.31       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       @100, 120, 140, 160, 180         6.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       @104, 124, 144, 164, 184         7.3.3       DMA Channel 0 through 4 – Current Data Buffer Address @108, 128, 148, 168, 188       8         5.33       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C       8         5.35       DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170, 190       8         5.3.6       DMA Channel 0 through 4 – DMA Ready Regist                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |        |          | Expansion ROM Base Address @030                                      | 69  |

| 5.2.12       Serial EEPROM Control @044       7         5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Enable @04C       7         5.2.15       PCI Test Register @050       7         5.2.16       Local Bus Control Register @0B0 {ROM, RAM, AUX, and ZV registers}       7         5.2.17       Local Bus Address Register @0B4       7         5.2.18       PCI_GPIO[1–0] Control Register A @0B8       7         5.2.19       PCI_GPIO[3–2] Control Register B @0BC       7         5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.31       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       @100, 120, 140, 160, 180         @100, 120, 140, 160, 180       7       5.3.2       DMA Channel 0 through 4 – Current Packet Control List Address         @104, 124, 144, 164, 184       7       5.3.3       DMA Channel 0 through 4 – Current Data Buffer Address @108, 128, 148, 168, 188       8         5.3.4       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C       8       8         5.3.5       DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170, 190       8         5.3.6       DMA Channel 0 through 4 – DMA Ready Register @114, 134, 154, 174, 194       8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |        |          |                                                                      |     |

| 5.2.13       PCI Interrupt Status @048       7         5.2.14       PCI Interrupt Enable @04C       7         5.2.15       PCI Test Register @050       7         5.2.16       Local Bus Control Register @0B0 {ROM, RAM, AUX, and ZV registers}       7         5.2.17       Local Bus Address Register @0B4       7         5.2.18       PCI_GPIO[1–0] Control Register A @0B8       7         5.2.19       PCI_GPIO[3–2] Control Register B @0BC       7         5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.31       DMA Control and Status Register Definitions       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       7         @100, 120, 140, 160, 180       7       7         5.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       7         5.3.3       DMA Channel 0 through 4 – Current Packet Control List Address       7         5.3.3       DMA Channel 0 through 4 – Current Data Buffer Address @108, 128, 148, 168, 188       8         5.3.4       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C       8         5.3.5       DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170, 190       8         5.3.6       DMA Channel 0 through 4 – DMA Ready Register @114, 134, 154,                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |   |        | -        |                                                                      |     |

| 5.2.14       PCI Interrupt Enable @04C       7         5.2.15       PCI Test Register @050       7         5.2.16       Local Bus Control Register @0B0 {ROM, RAM, AUX, and ZV registers}       7         5.2.17       Local Bus Address Register @0B4       7         5.2.18       PCI_GPIO[1–0] Control Register A @0B8       7         5.2.19       PCI_GPIO[3–2] Control Register B @0BC       7         5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3.1       DMA Control and Status Register Definitions       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       @100, 120, 140, 160, 180       7         5.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       @104, 124, 144, 164, 184       7         5.3.3       DMA Channel 0 through 4 – Current Data Buffer Address @108, 128, 148, 168, 188       8         5.3.4       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C       8         5.3.5       DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170, 190       8         5.3.6       DMA Channel 0 through 4 – DMA Ready Register @114, 134, 154, 174, 194       8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |        | -        |                                                                      |     |

| 5.2.15       PCI Test Register @050       7         5.2.16       Local Bus Control Register @0B0 {ROM, RAM, AUX, and ZV registers}       7         5.2.17       Local Bus Address Register @0B4       7         5.2.18       PCI_GPIO[1–0] Control Register A @0B8       7         5.2.19       PCI_GPIO[3–2] Control Register B @0BC       7         5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3       DMA Control and Status Register Definitions       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       @100, 120, 140, 160, 180       7         5.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       @104, 124, 144, 164, 184       7         5.3.3       DMA Channel 0 through 4 – Current Data Buffer Address @108, 128, 148, 168, 188       8         5.3.4       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C       8         5.3.5       DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170, 190       8         5.3.6       DMA Channel 0 through 4 – DMA Ready Register @114, 134, 154, 174, 194       8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |   |        |          |                                                                      |     |

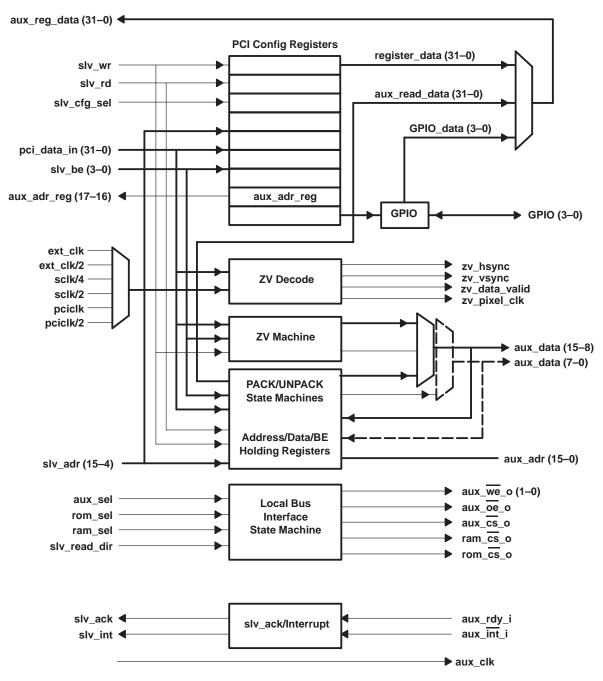

| 5.2.16       Local Bus Control Register @0B0 {ROM, RAM, AUX, and ZV registers}       7         5.2.17       Local Bus Address Register @0B4       7         5.2.18       PCI_GPIO[1–0] Control Register A @0B8       7         5.2.19       PCI_GPIO[3–2] Control Register B @0BC       7         5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3       DMA Control and Status Register Definitions       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       @100, 120, 140, 160, 180       7         5.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       @104, 124, 144, 164, 184       7         5.3.3       DMA Channel 0 through 4 – Current Data Buffer Address @108, 128, 148, 168, 188       8         5.3.4       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C       8         5.3.5       DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170, 190       8         5.3.6       DMA Channel 0 through 4 – DMA Ready Register @114, 134, 154, 174, 194       8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |        |          | •                                                                    |     |

| 5.2.17       Local Bus Address Register @0B4       7         5.2.18       PCI_GPIO[1–0] Control Register A @0B8       7         5.2.19       PCI_GPIO[3–2] Control Register B @0BC       7         5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3       DMA Control and Status Register Definitions       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       7         @100, 120, 140, 160, 180       7         5.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       7         @104, 124, 144, 164, 184       7         5.3.3       DMA Channel 0 through 4 – Current Data Buffer Address @108, 128, 148, 168, 188       8         5.3.4       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C       8         5.3.5       DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170, 190       8         5.3.6       DMA Channel 0 through 4 – DMA Ready Register @114, 134, 154, 174, 194       8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |        |          |                                                                      |     |

| 5.2.18       PCI_GPIO[1–0] Control Register A @0B8       7         5.2.19       PCI_GPIO[3–2] Control Register B @0BC       7         5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3       DMA Control and Status Register Definitions       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       7         6.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       7         7.3.3       DMA Channel 0 through 4 – Current Packet Control List Address       7         7.3.3       DMA Channel 0 through 4 – Current Packet Control List Address       7         7.3.3       DMA Channel 0 through 4 – Current Data Buffer Address @108, 128, 148, 168, 188       8         7.3.4       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C       8         7.3.5       DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170, 190       8         7.3.6       DMA Channel 0 through 4 – DMA Ready Register @114, 134, 154, 174, 194       8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |   |        |          |                                                                      |     |

| 5.2.19       PCI_GPIO[3–2] Control Register B @0BC       7         5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3       DMA Control and Status Register Definitions       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       7         @100, 120, 140, 160, 180       7         5.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       7         §2.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       7         §3.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       7         §3.3.3       DMA Channel 0 through 4 – Current Data Buffer Address @108, 128, 148, 168, 188       8         §3.3.4       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C       8         §3.3.5       DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170, 190       8         §3.3.6       DMA Channel 0 through 4 – DMA Ready Register @114, 134, 154, 174, 194       8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |        |          |                                                                      |     |

| 5.2.20       PCI GPIO DATA Read-Write Ports @0C0 through @0FC       7         5.3       DMA Control and Status Register Definitions       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       7         @100, 120, 140, 160, 180       7         5.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       7         §1.3.2       DMA Channel 0 through 4 – Current Packet Control List Address       7         §1.3.3       DMA Channel 0 through 4 – Current Packet Control List Address       7         §1.3.4       DMA Channel 0 through 4 – Current Data Buffer Address @108, 128, 148, 168, 188       8         §1.3.4       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C       8         §1.3.5       DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170, 190       8         §1.3.6       DMA Channel 0 through 4 – DMA Ready Register @114, 134, 154, 174, 194       8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |   |        |          | PCI_GPIO[3–2] Control Register B @0BC                                | 77  |

| 5.3       DMA Control and Status Register Definitions       7         5.3.1       DMA Channel 0 through 4 – Previous Packet Control List Address/Temp       7         0.100, 120, 140, 160, 180       7         5.3.2       DMA Channel 0 through 4 – Current Packet Control List Address         0.104, 124, 144, 164, 184       7         5.3.3       DMA Channel 0 through 4 – Current Data Buffer Address @108, 128, 148, 168, 188         5.3.4       DMA Channel 0 through 4 – DMA Channel Status @10C, 12C, 14C, 16C, 18C         5.3.5       DMA Channel 0 through 4 – DMA Channel Control @110, 130, 150, 170, 190         5.3.6       DMA Channel 0 through 4 – DMA Ready Register @114, 134, 154, 174, 194                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |   |        |          |                                                                      |     |

| <ul> <li>5.3.1 DMA Channel 0 through 4 – Previous Packet Control List Address/Temp <ul> <li>@ 100, 120, 140, 160, 180</li> <li>5.3.2 DMA Channel 0 through 4 – Current Packet Control List Address</li> <li>@ 104, 124, 144, 164, 184</li> <li>5.3.3 DMA Channel 0 through 4 – Current Data Buffer Address @ 108, 128, 148, 168, 188</li> <li>5.3.4 DMA Channel 0 through 4 – DMA Channel Status @ 10C, 12C, 14C, 16C, 18C</li> <li>5.3.5 DMA Channel 0 through 4 – DMA Channel Control @ 110, 130, 150, 170, 190</li> <li>8</li> <li>5.3.6 DMA Channel 0 through 4 – DMA Ready Register @ 114, 134, 154, 174, 194</li> </ul></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   | 5.3    |          |                                                                      |     |