# 2.4GHz IEEE 802.15.4 和 ZigBee® 应用的 CC253X 片上系统解决方案

## 用户指南

文件编号: SWRU191

2009 年 4 月

## 目录

|                       |    |

|-----------------------|----|

| 序言.....               | 13 |

| 1 简介.....             | 15 |

| 1.1 概述.....           | 16 |

| 1.1.1 CPU 和内存.....    | 17 |

| 1.1.2 时钟和电源管理.....    | 17 |

| 1.1.3 外设.....         | 17 |

| 1.1.4 无线电.....        | 18 |

| 1.2 应用.....           | 19 |

| 2 8051 CPU.....       | 20 |

| 2.1 8051 CPU 简介.....  | 21 |

| 2.2 存储器.....          | 21 |

| 2.2.1 存储器映射.....      | 21 |

| 2.2.2 CPU 存储空间.....   | 23 |

| 2.2.3 物理存储器.....      | 24 |

| 2.2.4 XDATA 存储空间..... | 29 |

| 2.2.5 存储器仲裁.....      | 29 |

| 2.3 CPU 寄存器.....      | 29 |

| 2.3.1 数据指针.....       | 30 |

| 2.3.2 寄存器 R0-R7.....  | 30 |

| 2.3.3 程序状态字.....      | 30 |

| 2.3.4 累加器.....        | 31 |

| 2.3.5 B 寄存器.....      | 31 |

| 2.3.6 堆栈指针.....       | 31 |

| 2.4 指令集总结.....        | 31 |

| 2.5 中断.....           | 35 |

| 2.5.1 中断屏蔽.....       | 35 |

| 2.5.2 中断处理.....       | 39 |

| 2.5.3 中断优先级.....      | 41 |

| 3 调试接口.....           | 44 |

| 3.1 调试模式.....         | 45 |

| 3.2 调试传输.....         | 45 |

| 3.3 调试命令.....         | 47 |

| 3.4 锁位.....           | 47 |

| 3.4.1 调试配置.....       | 48 |

| 3.4.2 调试状态.....       | 48 |

| 3.4.3 硬件断点.....       | 50 |

| 3.4.4 闪存编程.....       | 50 |

| 3.5 调试接口和供电模式.....    | 51 |

|                         |           |

|-------------------------|-----------|

| 3.6 寄存器.....            | 51        |

| <b>4 电源管理和时钟.....</b>   | <b>52</b> |

| 4.1 电源管理简介.....         | 53        |

| 4.1.1 主动和空闲模式.....      | 53        |

| 4.1.2 PM1.....          | 54        |

| 4.1.3 PM2.....          | 54        |

| 4.1.4 PM3.....          | 54        |

| 4.2 电源管理控制.....         | 54        |

| 4.3 电源管理寄存器.....        | 55        |

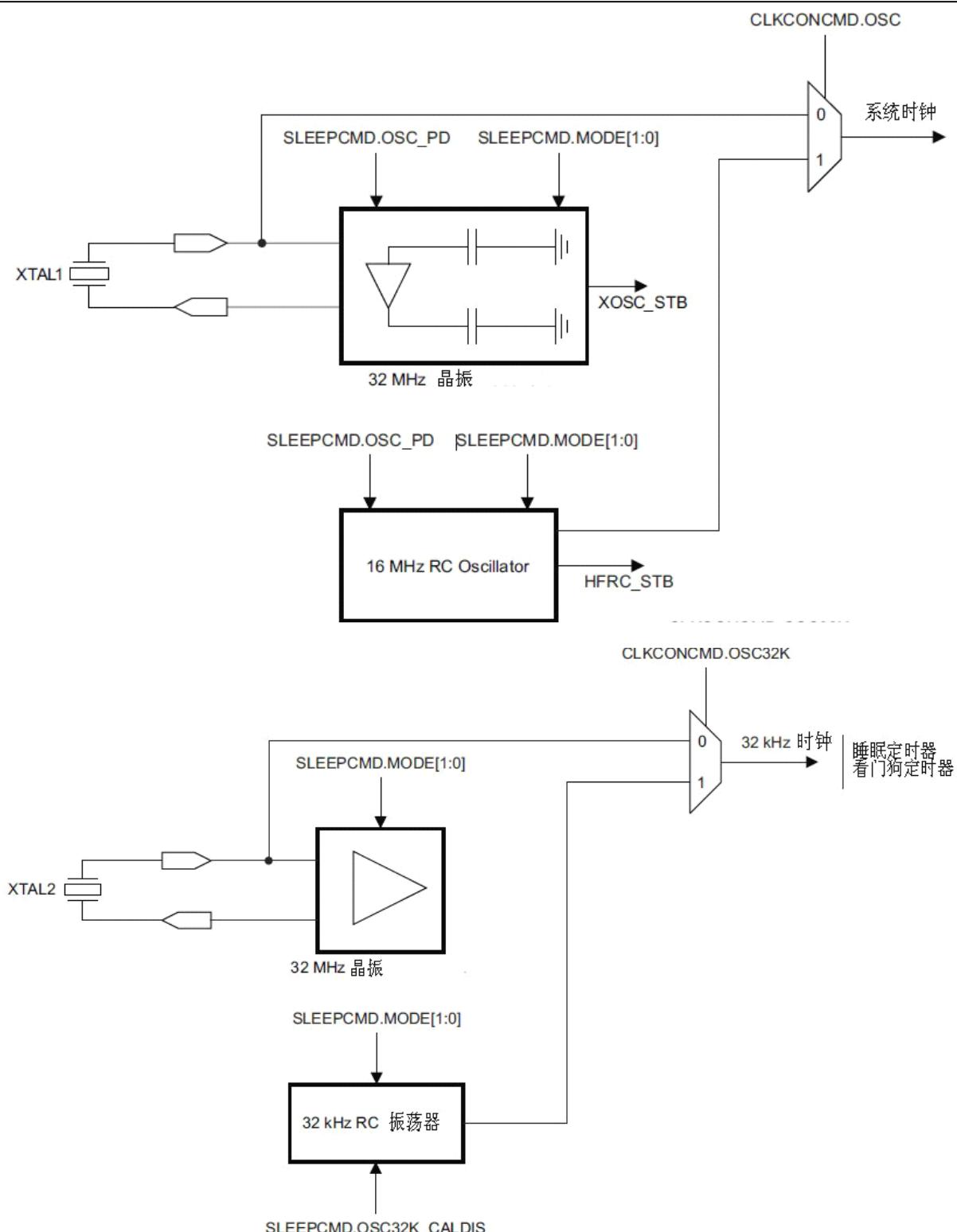

| 4.4 振荡器和时钟.....         | 58        |

| 4.4.1 振荡器.....          | 58        |

| 4.4.2 系统时钟.....         | 58        |

| 4.4.3 32 kHz 振荡器.....   | 59        |

| 4.4.4 振荡器和时钟寄存器.....    | 59        |

| 4.5 定时器标记产生.....        | 61        |

| 4.6 数据保留.....           | 61        |

| <b>5 复位.....</b>        | <b>62</b> |

| 5.1 上电复位和布朗输出探测器.....   | 63        |

| 5.2 时钟丢失探测器.....        | 63        |

| <b>6 闪存控制器.....</b>     | <b>64</b> |

| 6.1 闪存存储器组织.....        | 65        |

| 6.2 闪存写.....            | 65        |

| 6.2.1 闪存写步骤.....        | 65        |

| 6.2.2 写多次到一个字.....      | 66        |

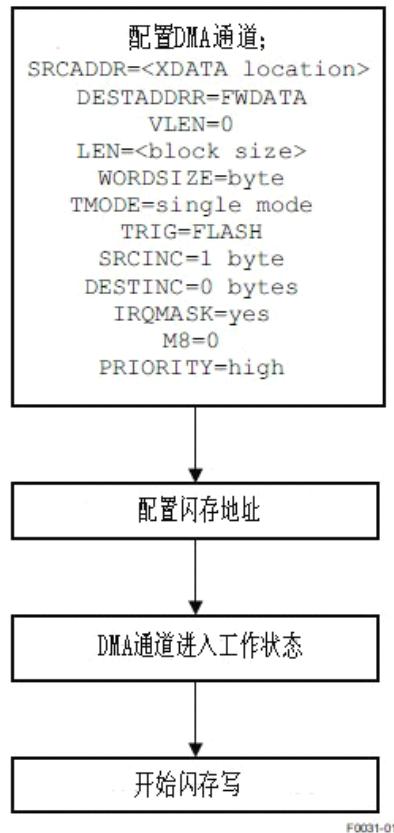

| 6.2.3 DMA 闪存写.....      | 66        |

| 6.2.4 CPU 闪存写.....      | 67        |

| 6.3 闪存页面擦除.....         | 67        |

| 6.3.1 从闪存存储器执行闪存擦除..... | 68        |

| 6.4 闪存 DMA 触发.....      | 68        |

| 6.5 闪存控制器的寄存器.....      | 68        |

| <b>7 I/O 端口.....</b>    | <b>70</b> |

| 7.1 未使用的 I/O 引脚.....    | 71        |

| 7.2 低 I/O 电压.....       | 71        |

| 7.3 通用 I/O.....         | 71        |

| 7.4 通用 I/O 中断.....      | 71        |

| 7.5 通用 I/O DMA.....     | 72        |

| 7.6 外设 I/O.....         | 72        |

| 7.6.1 定时器 1.....        | 73        |

| 7.6.2 定时器 3.....        | 73        |

| 7.6.3 定时器 4.....        | 74        |

| 7.6.4 USART 0.....      | 74        |

| 7.6.5 USART 1.....      | 74        |

---

|                                |           |

|--------------------------------|-----------|

| 7.6.6 ADC.....                 | 75        |

| 7.7 调试接口.....                  | 75        |

| 7.8 32 kHz XOSC 输入.....        | 75        |

| 7.9 无线测试输出信号.....              | 75        |

| 7.10 掉电信号 MUX (PMUX).....      | 75        |

| 7.11 I/O 引脚.....               | 75        |

| <b>8 DMA 控制器.....</b>          | <b>83</b> |

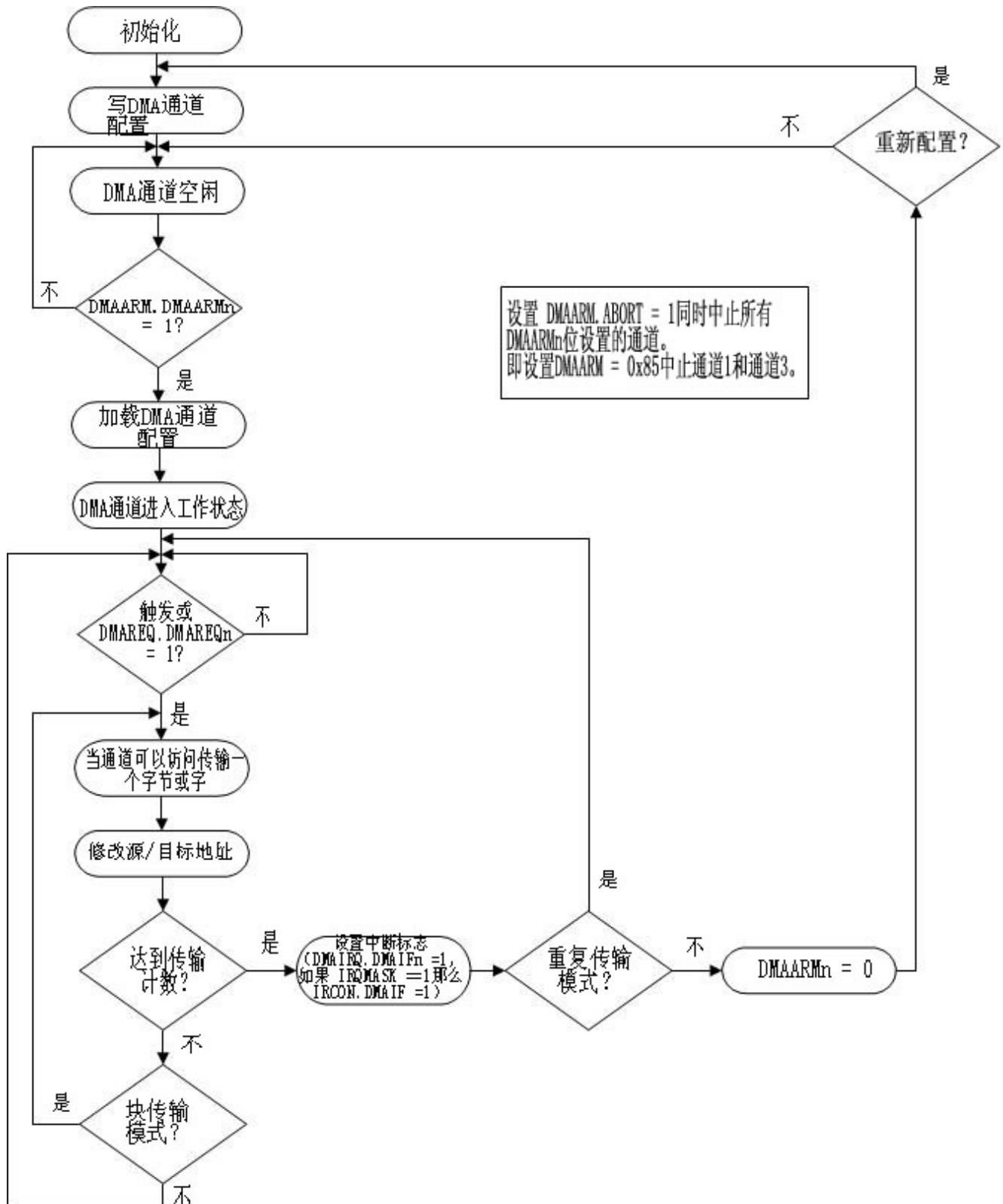

| 8.1 DMA 操作.....                | 84        |

| 8.2 DMA 配置参数.....              | 86        |

| 8.2.1 源地址.....                 | 86        |

| 8.2.2 目标地址.....                | 86        |

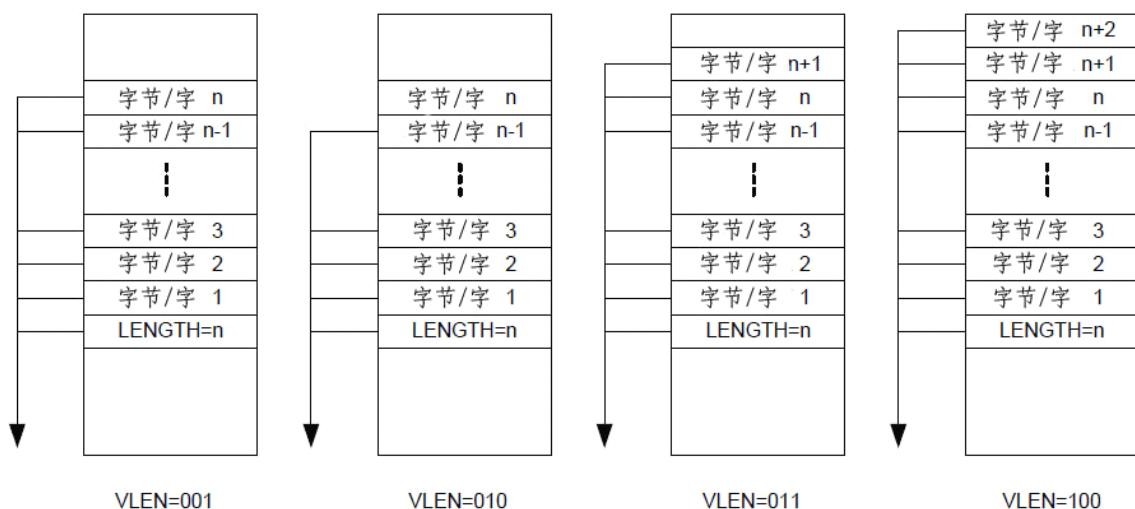

| 8.2.3 传送数量.....                | 86        |

| 8.2.4 VLEN 设置.....             | 87        |

| 8.2.5 触发事件.....                | 87        |

| 8.2.6 源和目标增量.....              | 87        |

| 8.2.7 DMA 传输模式.....            | 88        |

| 8.2.8 DMA 优先级.....             | 88        |

| 8.2.9 字节或字传输.....              | 88        |

| 8.2.10 中断屏蔽.....               | 88        |

| 8.2.11 模式 8 设置.....            | 88        |

| 8.3 DMA 配置安装.....              | 88        |

| 8.4 停止 DMA 传输.....             | 89        |

| 8.5 DMA 中断.....                | 89        |

| 8.6 DMA 配置数据结构.....            | 89        |

| 8.7 DMA 存储访问.....              | 89        |

| 8.8 DMA 寄存器.....               | 92        |

| <b>9 定时器 1 (16 位定时器) .....</b> | <b>94</b> |

| 9.1 16 位计数器.....               | 95        |

| 9.2 定时器 1 操作.....              | 95        |

| 9.3 自由运行模式.....                | 95        |

| 9.4 模模式.....                   | 96        |

| 9.5 正计数/倒计数模式.....             | 96        |

| 9.6 通道模式控制.....                | 97        |

| 9.7 输入捕获模式.....                | 97        |

| 9.8 输出比较模式.....                | 97        |

| 9.9 IR 信号产生和线性化.....           | 102       |

| 9.9.1 简介.....                  | 102       |

| 9.9.2 调制码.....                 | 102       |

| 9.9.3 非调制码.....                | 103       |

| 9.9.4 学习.....                  | 104       |

| 9.9.5 其他注意事项.....              | 104       |

| 9.10 定时器 1 中断.....             | 104       |

---

|                                       |            |

|---------------------------------------|------------|

| 9.11 定时器 1 DMA 触发.....                | 104        |

| 9.12 定时器 1 寄存器.....                   | 105        |

| 9.13 作为数组访问定时器 1 寄存器.....             | 109        |

| <b>10 定时器 3 和定时器 4 (8 位定时器) .....</b> | <b>110</b> |

| 10.1 8 位定时器计数器.....                   | 111        |

| 10.2 定时器 3/定时器 4 模式控制.....            | 111        |

| 10.2.1 自由运行模式.....                    | 111        |

| 10.2.2 倒计数模式.....                     | 111        |

| 10.2.3 模模式.....                       | 111        |

| 10.2.4 正/倒计数模式.....                   | 111        |

| 10.3 通道模式控制.....                      | 111        |

| 10.4 输入捕获模式.....                      | 112        |

| 10.5 输出比较模式.....                      | 112        |

| 10.6 定时器 3 和定时器 4 中断.....             | 112        |

| 10.7 定时器 3 和定时器 4 DMA 触发.....         | 113        |

| 10.8 定时器 3 和定时器 4 寄存器.....            | 113        |

| <b>11 睡眠定时器.....</b>                  | <b>117</b> |

| 11.1 概述.....                          | 118        |

| 11.2 定时器比较.....                       | 118        |

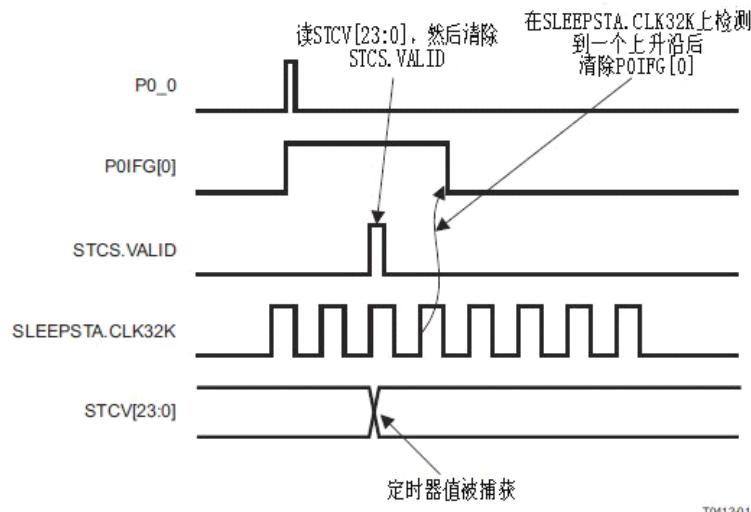

| 11.3 定时器捕获.....                       | 118        |

| 11.4 睡眠定时器寄存器.....                    | 119        |

| <b>12 ADC.....</b>                    | <b>121</b> |

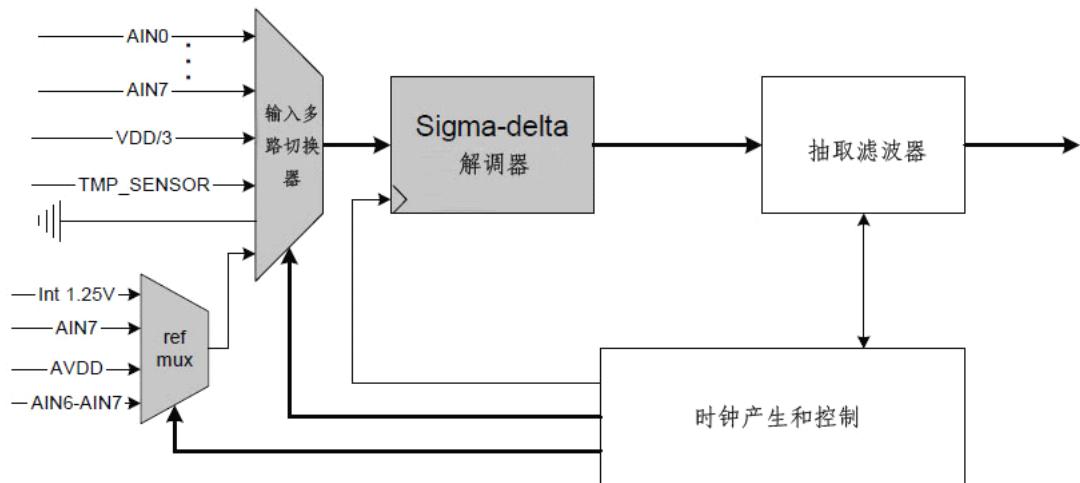

| 12.1 ADC 简介.....                      | 122        |

| 12.2 ADC 操作.....                      | 122        |

| 12.2.1 ADC 输入.....                    | 122        |

| 12.2.2 ADC 转换序列.....                  | 123        |

| 12.2.3 单个 ADC 转换.....                 | 123        |

| 12.2.4 ADC 运行模式.....                  | 123        |

| 12.2.5 ADC 转换结果.....                  | 124        |

| 12.2.6 ADC 参考电压.....                  | 124        |

| 12.2.7 ADC 转换时间.....                  | 124        |

| 12.2.8 ADC 中断.....                    | 124        |

| 12.2.9 ADC DMA 触发.....                | 124        |

| 12.2.10 ADC 寄存器.....                  | 125        |

| <b>13 随机数发生器.....</b>                 | <b>128</b> |

| 13.1 简介.....                          | 129        |

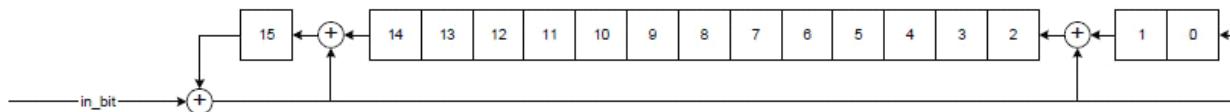

| 13.2 随机数发生器的运行.....                   | 129        |

| 13.2.1 伪随机数序列的生成.....                 | 129        |

| 13.2.2 种子数的产生.....                    | 129        |

| 13.2.3 CRC16.....                     | 130        |

| 13.3 随机数发生器的寄存器.....                  | 130        |

| <b>14 AES 协处理器.....</b>               | <b>131</b> |

---

|        |                      |     |

|--------|----------------------|-----|

| 14.1   | AES 操作.....          | 132 |

| 14.2   | 密钥和 IV.....          | 132 |

| 14.3   | 填充输入数据.....          | 132 |

| 14.4   | 和 CPU 通信.....        | 132 |

| 14.5   | 运行模式.....            | 132 |

| 14.6   | CBC-MAC.....         | 133 |

| 14.7   | CCM 模式.....          | 133 |

| 14.8   | 在层之间共享 AES 协处理器..... | 135 |

| 14.9   | AES 中断.....          | 135 |

| 14.10  | AES DMA 触发.....      | 135 |

| 14.11  | AES 寄存器.....         | 135 |

| 15     | <b>看门狗定时器</b> .....  | 137 |

| 15.1   | 看门狗模式.....           | 138 |

| 15.2   | 定时器模式.....           | 138 |

| 15.3   | 看门狗定时器寄存器.....       | 138 |

| 16     | <b>USART</b> .....   | 140 |

| 16.1   | UART 模式.....         | 141 |

| 16.1.1 | UART 发送.....         | 141 |

| 16.1.2 | UART 接收.....         | 141 |

| 16.1.3 | UART 硬件流控制.....      | 142 |

| 16.1.4 | UART 特征格式.....       | 142 |

| 16.2   | SPI 模式.....          | 142 |

| 16.2.1 | SPI 主模式操作.....       | 142 |

| 16.2.2 | SPI 从模式操作.....       | 143 |

| 16.3   | SSN 从模式选择引脚.....     | 143 |

| 16.4   | 波特率的产生.....          | 143 |

| 16.5   | 清除 USART.....        | 144 |

| 16.6   | USART 中断.....        | 144 |

| 16.7   | USART DMA 触发.....    | 144 |

| 16.8   | USART 寄存器.....       | 145 |

| 17     | <b>USB 控制器</b> ..... | 149 |

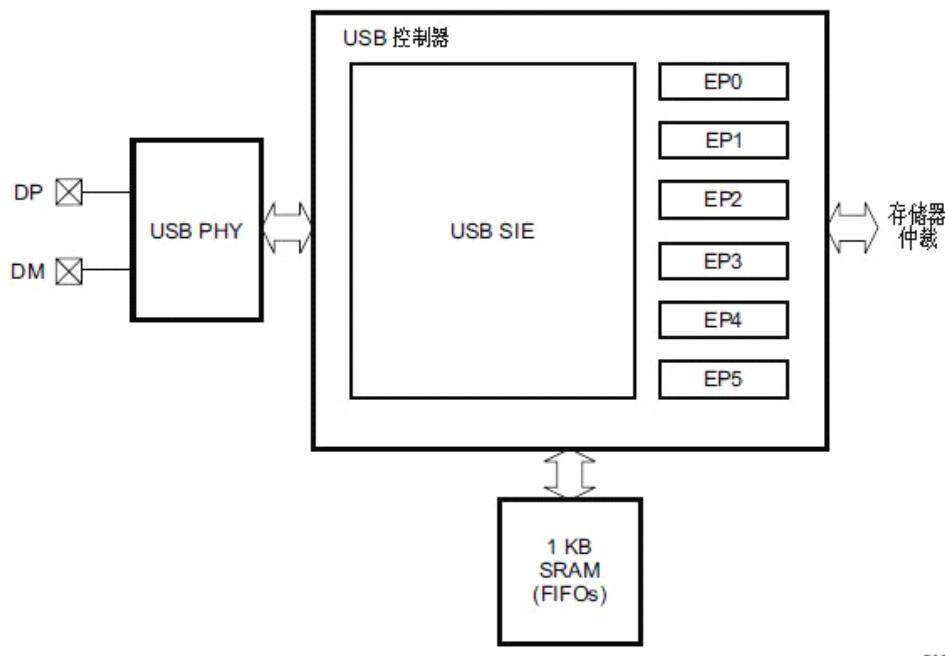

| 17.1   | USB 简介.....          | 150 |

| 17.2   | USB 使能.....          | 150 |

| 17.3   | 48 MHz USB PLL.....  | 150 |

| 17.4   | USB 中断.....          | 151 |

| 17.5   | 端口 0.....            | 151 |

| 17.6   | 端口-0 中断.....         | 151 |

| 17.6.1 | 错误情况.....            | 152 |

| 17.6.2 | 配置传输 (IDLE 状态) ..... | 152 |

| 17.6.3 | IN 传输 (TX 状态) .....  | 152 |

| 17.6.4 | OUT 传输 (RX 状态) ..... | 153 |

| 17.7   | 端口 1-5.....          | 153 |

---

---

|         |                              |     |

|---------|------------------------------|-----|

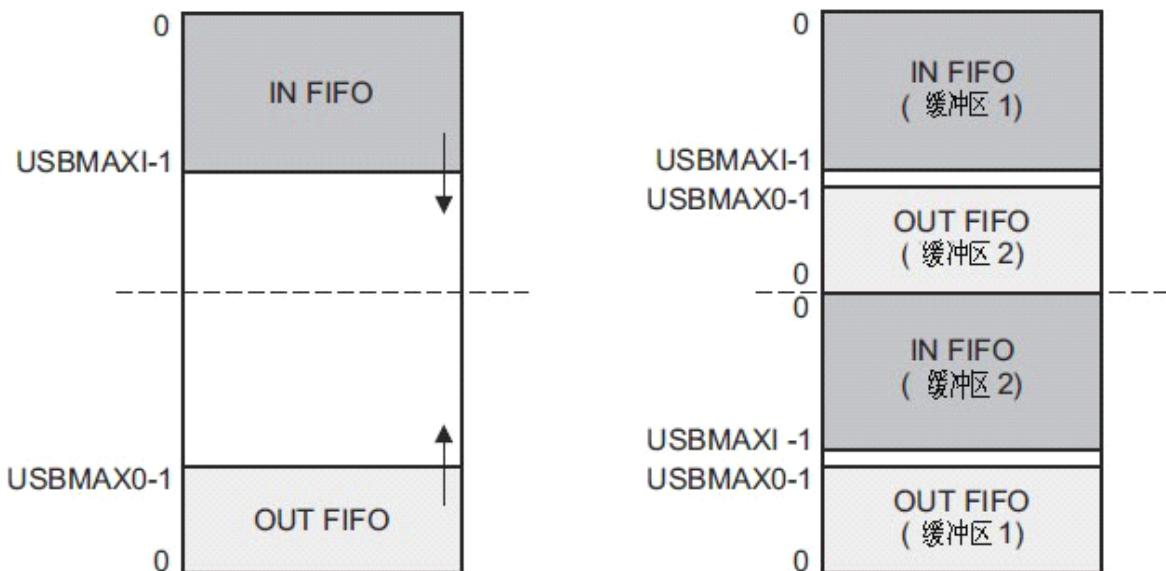

| 17.7.1  | FIFO 管理.....                 | 153 |

| 17.7.2  | 双缓冲.....                     | 154 |

| 17.7.3  | FIFO 访问.....                 | 155 |

| 17.7.4  | 端口 1-5 中断.....               | 155 |

| 17.7.5  | 批量/中断 IN 端口.....             | 156 |

| 17.7.6  | 同步 IN 端口.....                | 156 |

| 17.7.7  | 批量/中断 OUT 端口.....            | 156 |

| 17.7.8  | 同步 OUT 端口.....               | 156 |

| 17.8    | DMA.....                     | 157 |

| 17.9    | USB 复位.....                  | 157 |

| 17.10   | 挂起和恢复.....                   | 157 |

| 17.11   | 远程唤醒.....                    | 157 |

| 17.12   | USB 寄存器.....                 | 158 |

| 18      | <b>定时器 2 (MAC 定时器) .....</b> | 164 |

| 18.1    | 定时器操作.....                   | 165 |

| 18.1.1  | 概述.....                      | 165 |

| 18.1.2  | 正计数.....                     | 165 |

| 18.1.3  | 定时器溢出.....                   | 165 |

| 18.1.4  | 定时器 Delta 递增.....            | 165 |

| 18.1.5  | 定时器比较.....                   | 165 |

| 18.1.6  | 溢出计数.....                    | 165 |

| 18.1.7  | 溢出计数更新.....                  | 166 |

| 18.1.8  | 溢出计数器溢出.....                 | 166 |

| 18.1.9  | 溢出计数器比较.....                 | 166 |

| 18.1.10 | 捕获输入.....                    | 166 |

| 18.2    | 中断.....                      | 166 |

| 18.3    | 事件输出 (DMA 触发和 CSP 事件) .....  | 167 |

| 18.4    | 定时器启动/停止同步.....              | 167 |

| 18.4.1  | 概述.....                      | 167 |

| 18.4.2  | 定时器同步停止.....                 | 167 |

| 18.4.3  | 定时器同步启动.....                 | 167 |

| 18.5    | 定时器 2 寄存器.....               | 168 |

| 19      | <b>无线电.....</b>              | 172 |

| 19.1    | RF 内核.....                   | 173 |

| 19.1.1  | 中断.....                      | 173 |

| 19.1.2  | 中断寄存器.....                   | 173 |

| 19.2    | FIFO 访问.....                 | 177 |

| 19.3    | DMA.....                     | 177 |

| 19.4    | 存储器映射.....                   | 177 |

| 19.4.1  | RX FIFO.....                 | 178 |

| 19.4.2  | TX FIFO.....                 | 178 |

| 19.4.3  | 帧过滤和源匹配存储器映射.....            | 178 |

---

---

|         |                              |     |

|---------|------------------------------|-----|

| 19.5    | 频率和通道编程.....                 | 179 |

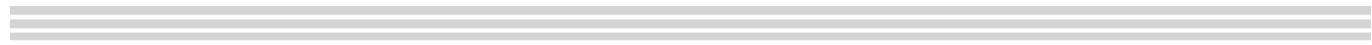

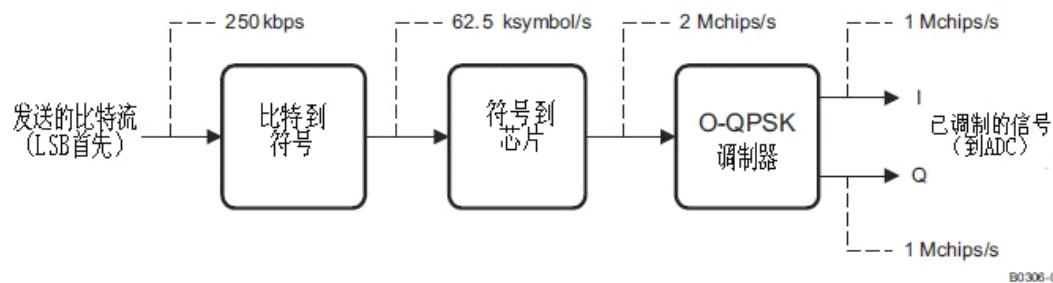

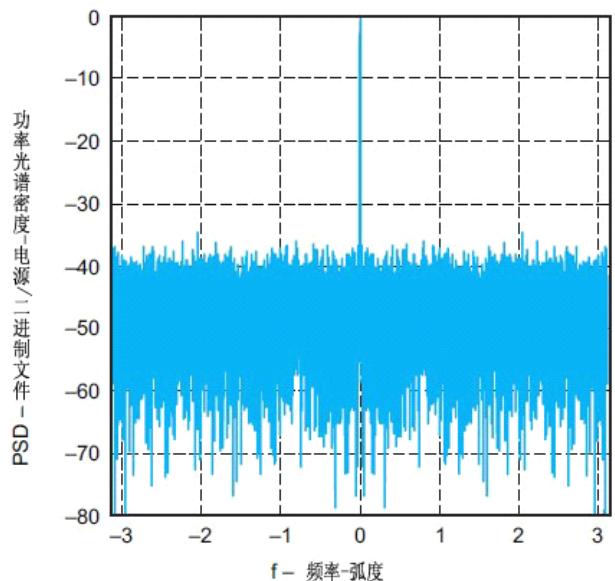

| 19.6    | IEEE 802.15.4-2006 调制格式..... | 179 |

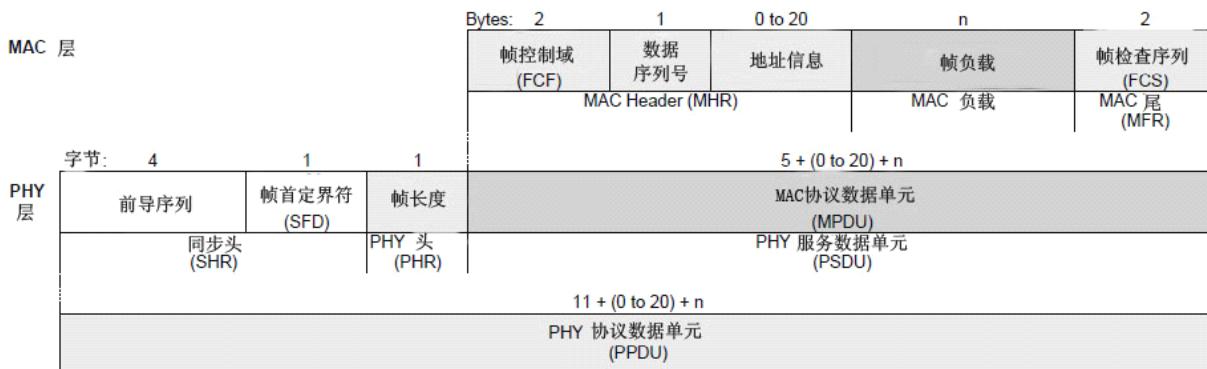

| 19.7    | IEEE 802.15.4-2006 帧格式.....  | 181 |

| 19.7.1  | PHY 层.....                   | 181 |

| 19.7.2  | MAC 层.....                   | 181 |

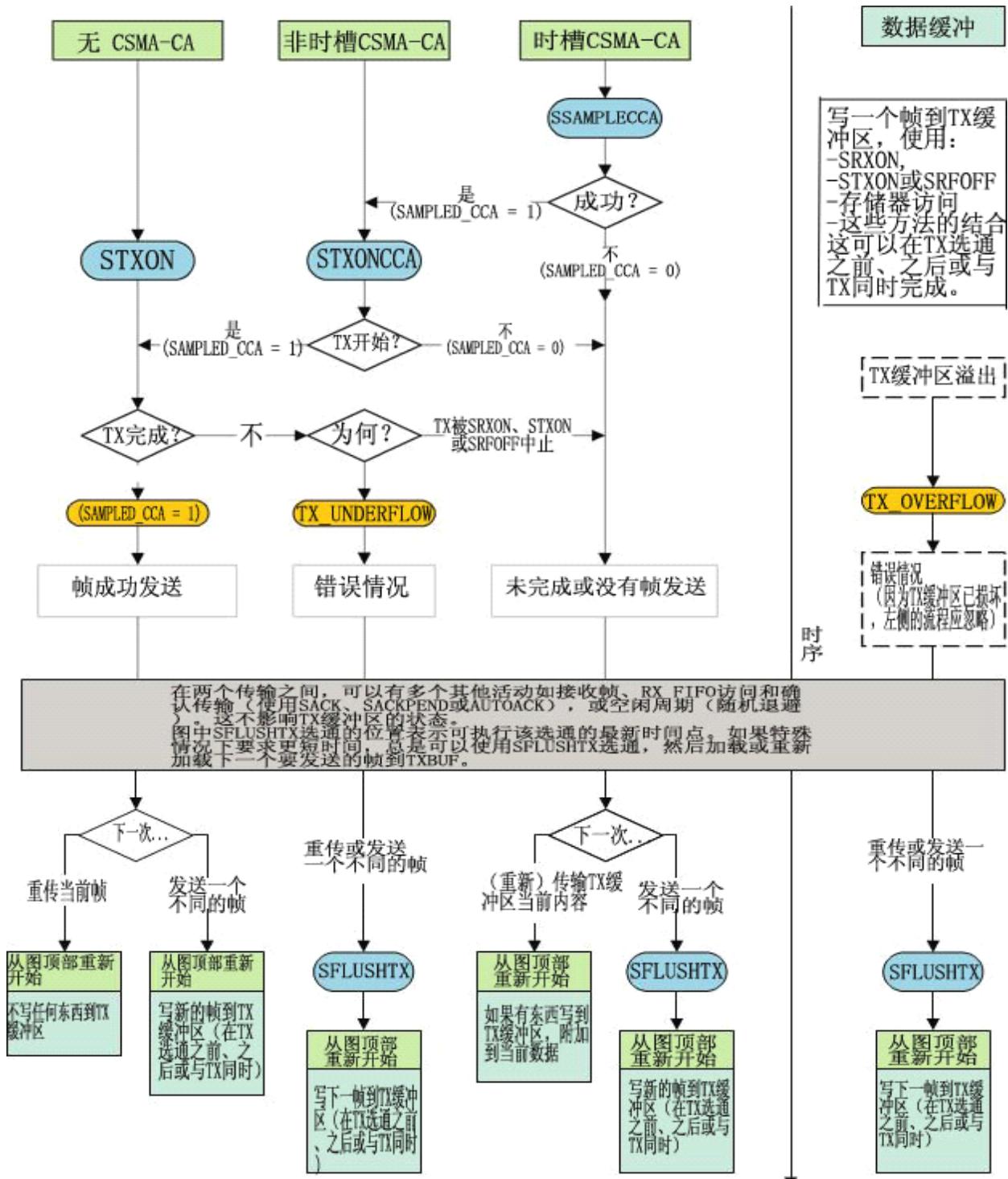

| 19.8    | 发送模式.....                    | 182 |

| 19.8.1  | TX 控制.....                   | 182 |

| 19.8.2  | TX 状态时序.....                 | 182 |

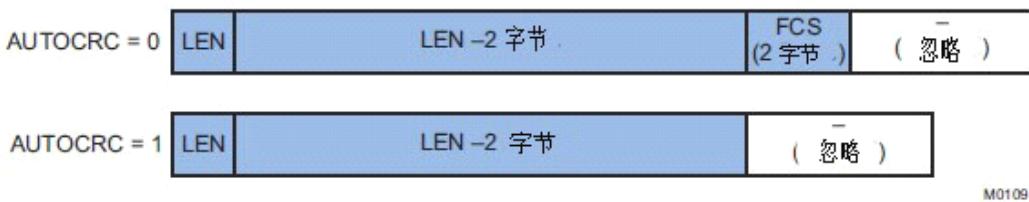

| 19.8.3  | TX FIFO 访问.....              | 182 |

| 19.8.4  | 重传.....                      | 183 |

| 19.8.5  | 错误情况.....                    | 183 |

| 19.8.6  | TX 溢出图.....                  | 184 |

| 19.8.7  | 帧处理.....                     | 185 |

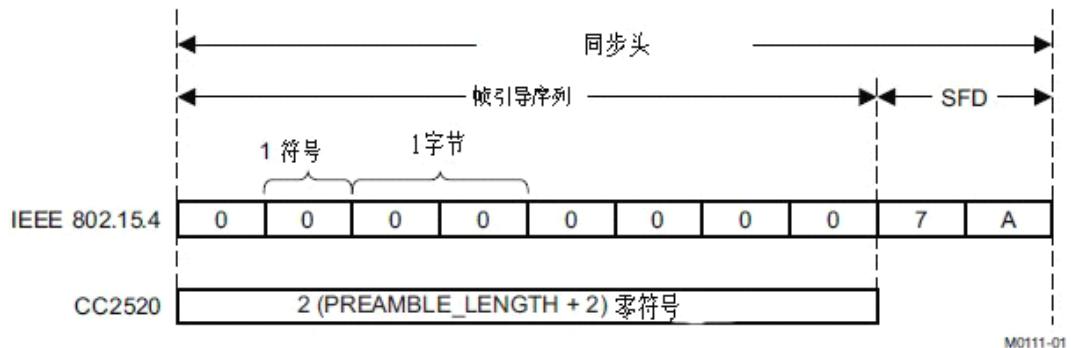

| 19.8.8  | 同步头.....                     | 185 |

| 19.8.9  | 帧长度域.....                    | 185 |

| 19.8.10 | 帧校验序列.....                   | 185 |

| 19.8.11 | 中断.....                      | 186 |

| 19.8.12 | 空闲通道评估.....                  | 186 |

| 19.8.13 | 输出功率编程.....                  | 186 |

| 19.8.14 | 提示和技巧.....                   | 186 |

| 19.9    | 接收模式.....                    | 186 |

| 19.9.1  | RX 控制.....                   | 186 |

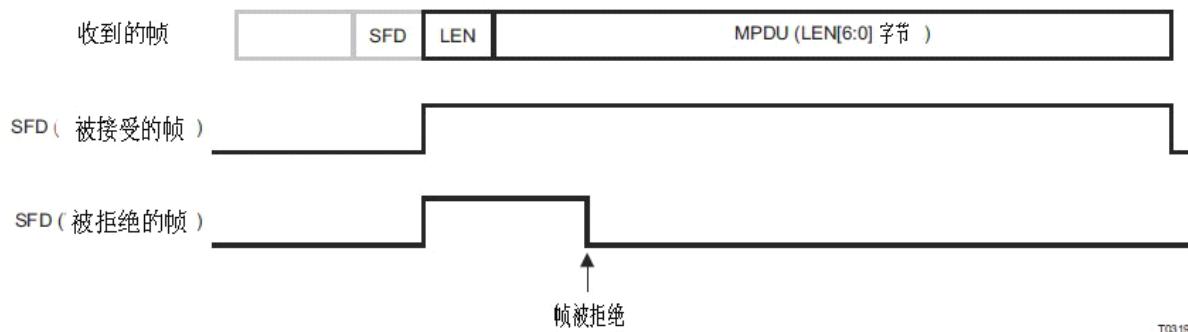

| 19.9.2  | RX 状态时序.....                 | 187 |

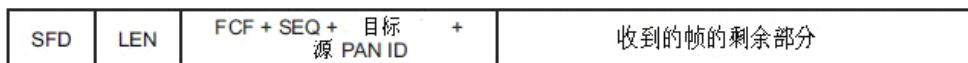

| 19.9.3  | 帧处理.....                     | 187 |

| 19.9.4  | 同步头和帧长度域.....                | 187 |

| 19.9.5  | 帧过滤.....                     | 188 |

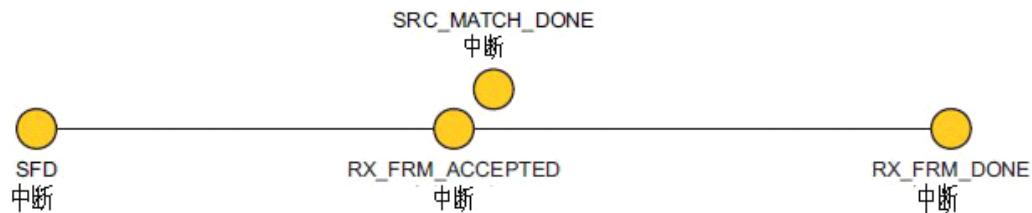

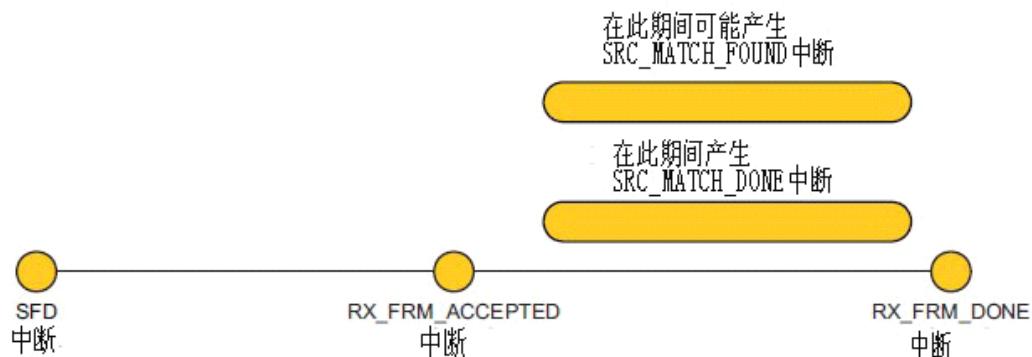

| 19.9.6  | 源地址匹配.....                   | 191 |

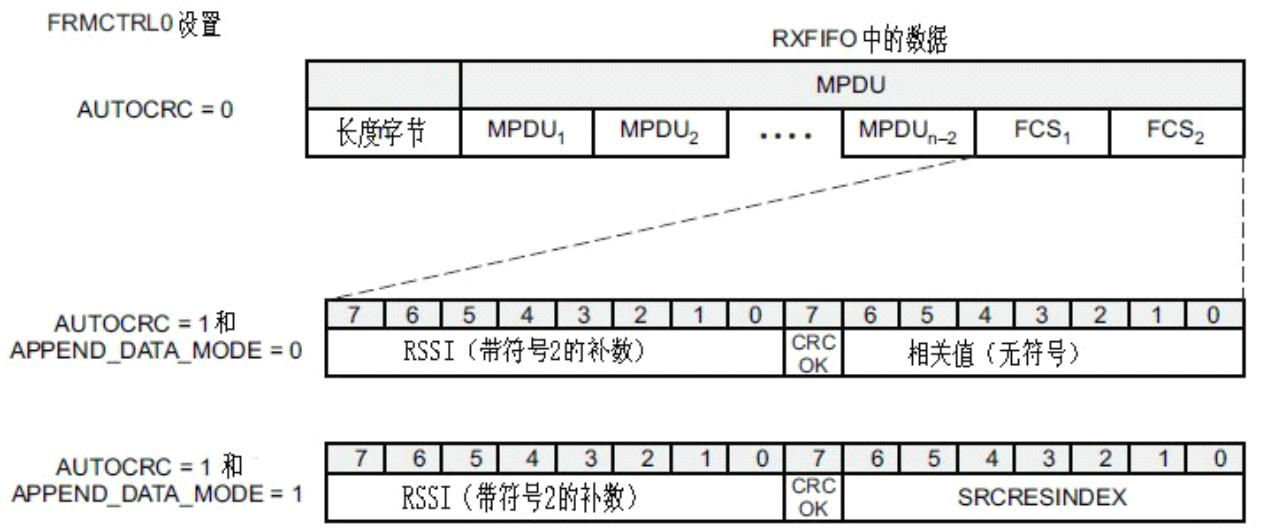

| 19.9.7  | 帧校验序列.....                   | 194 |

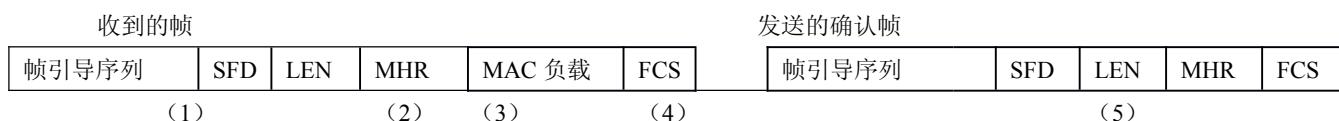

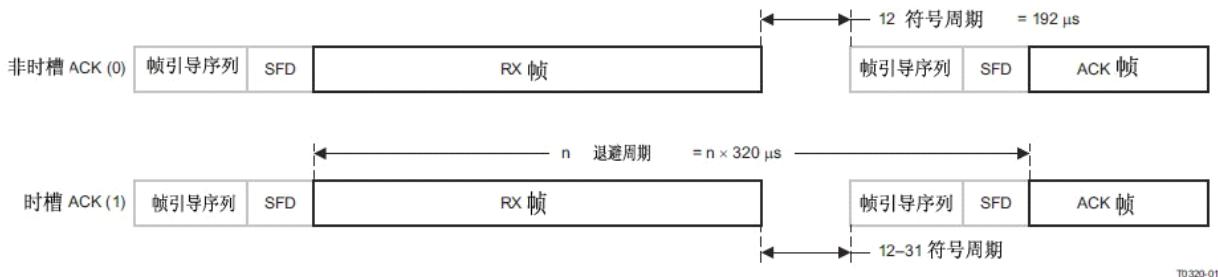

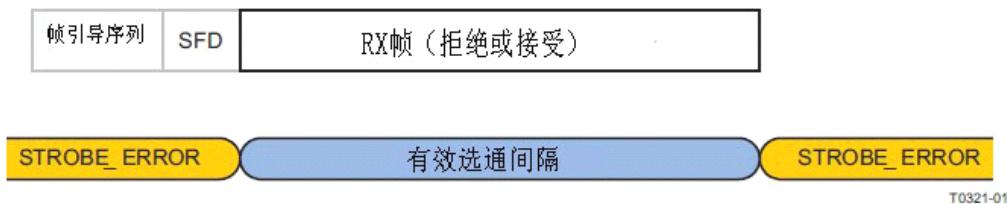

| 19.9.8  | 确认传输.....                    | 194 |

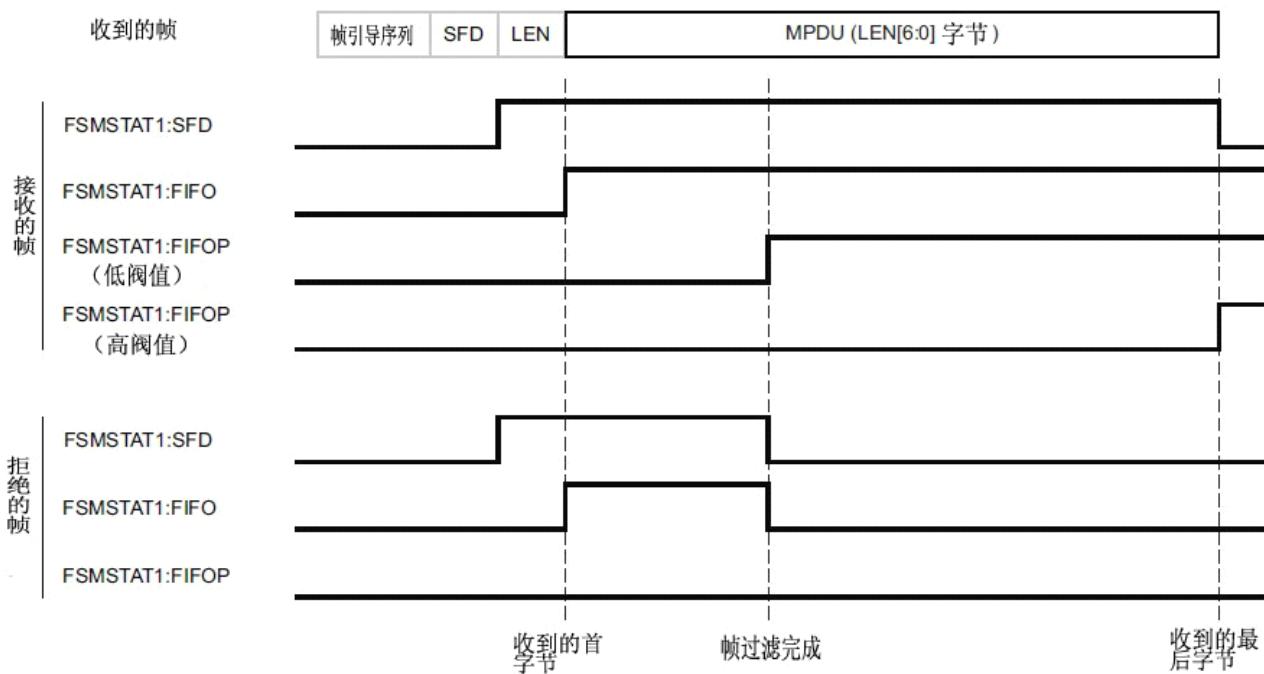

| 19.10   | RX FIFO 访问.....              | 196 |

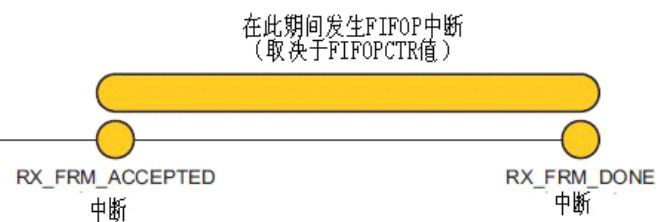

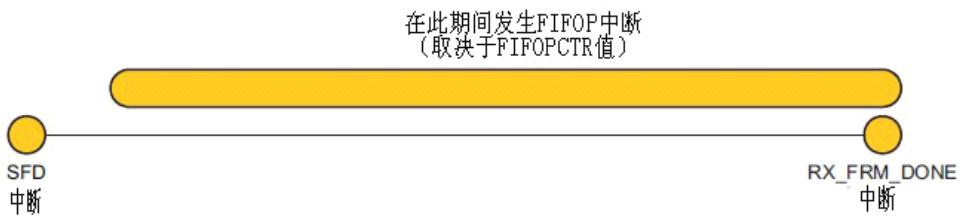

| 19.10.1 | 使用 FIFO 和 FIFOP.....         | 196 |

| 19.10.2 | 错误情况.....                    | 197 |

| 19.10.3 | RSSI.....                    | 197 |

| 19.10.4 | 链路质量指示.....                  | 198 |

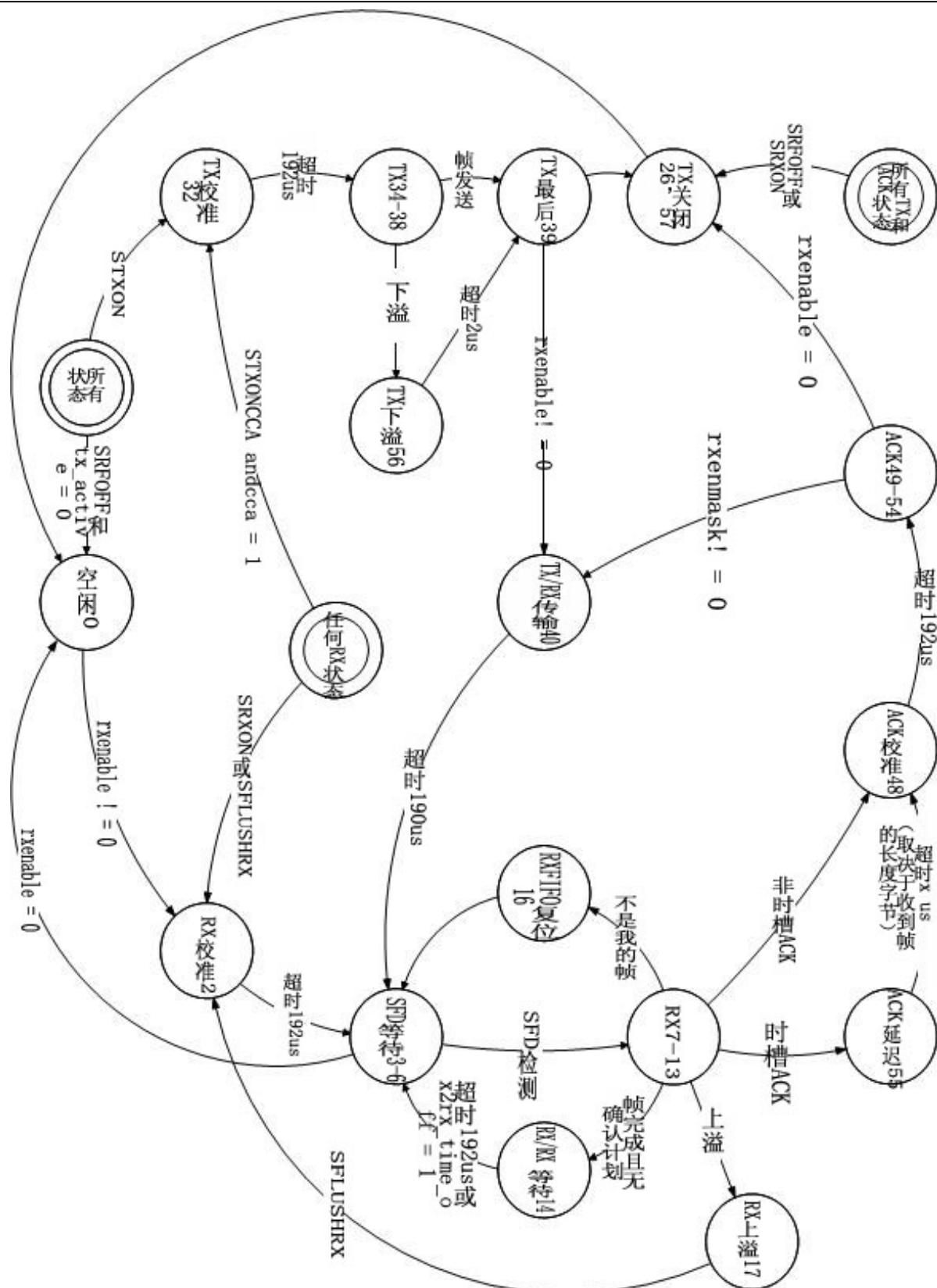

| 19.11   | 无线电控制状态机制.....               | 198 |

| 19.12   | 随机数的产生.....                  | 200 |

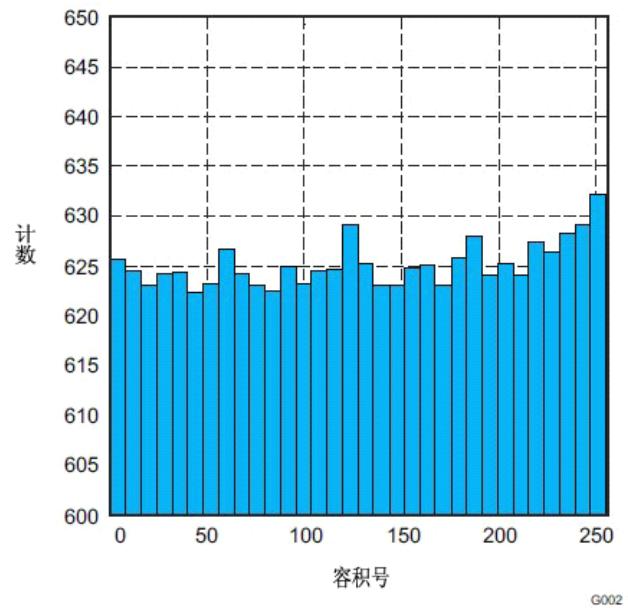

| 19.13   | 数据包分析器和无线电测试输出信号.....        | 201 |

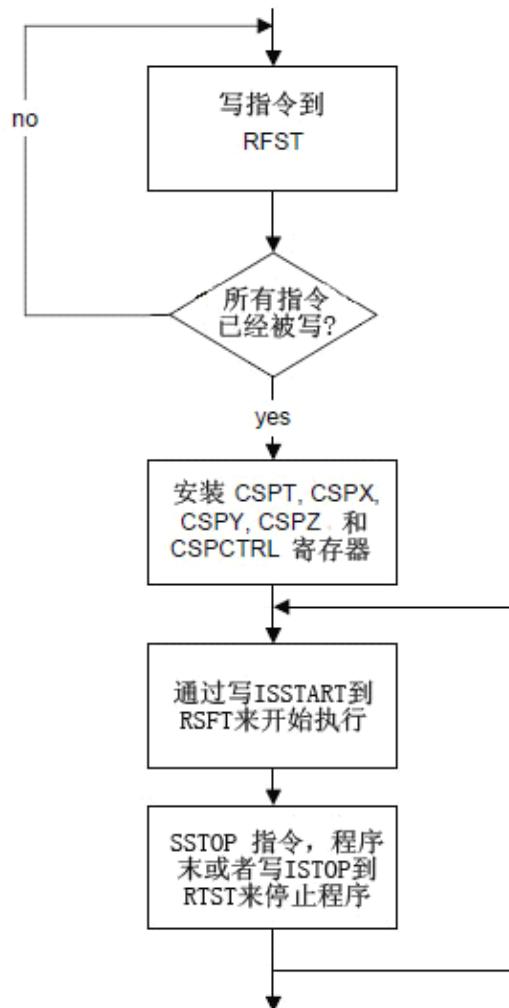

| 19.14   | 命令选通/ CSMA-CA 处理器.....       | 202 |

| 19.14.1 | 指令存储器.....                   | 202 |

| 19.14.2 | 数据寄存器.....                   | 203 |

| 19.14.3 | 程序运行.....                    | 203 |

| 19.14.4 | 中断请求.....                    | 203 |

---

---

|         |                                                                                                   |     |

|---------|---------------------------------------------------------------------------------------------------|-----|

| 19.14.5 | 随机数指令.....                                                                                        | 203 |

| 19.14.6 | 运行 CSP 程序.....                                                                                    | 203 |

| 19.14.7 | 寄存器.....                                                                                          | 204 |

| 19.14.8 | 指令集综述.....                                                                                        | 205 |

| 19.14.9 | 指令集定义.....                                                                                        | 206 |

| 19.15   | 寄存器.....                                                                                          | 219 |

| 19.15.1 | 寄存器设置更新.....                                                                                      | 219 |

| 19.15.2 | 寄存器访问模式.....                                                                                      | 220 |

| 19.15.3 | 寄存器描述.....                                                                                        | 220 |

| 20      | 稳压器.....                                                                                          | 238 |

| 21      | 可用的软件.....                                                                                        | 239 |

| 21.1    | 用于评估的 SmartRF™ 软件 ( <a href="http://www.ti.com/smartrfstudio">www.ti.com/smartrfstudio</a> )..... | 240 |

| 21.2    | RemoTI™ 网络协议( <a href="http://www.ti.com/remoti">www.ti.com/remoti</a> ).....                     | 240 |

| 21.3    | SimpliciTI™ 网络协议( <a href="http://www.ti.com/simpliciti">www.ti.com/simpliciti</a> ).....         | 241 |

| 21.4    | TIMAC 软件( <a href="http://www.ti.com/timac">www.ti.com/timac</a> ).....                           | 241 |

| 21.5    | Z-Stack™ 软件( <a href="http://www.ti.com/z-stack">www.ti.com/z-stack</a> ).....                    | 242 |

| A       | 缩写.....                                                                                           | 243 |

| B       | 其他信息.....                                                                                         | 246 |

| B.1     | 德州仪器低功耗 RF 网站.....                                                                                | 247 |

| B.2     | 低功耗 RF 网络社区.....                                                                                  | 247 |

| B.3     | 德州仪器低功耗 RF 开发商网络.....                                                                             | 247 |

| B.4     | 低功耗 RF 电子简讯.....                                                                                  | 247 |

| C       | 参考书目.....                                                                                         | 248 |

## 图清单

|                                                         |     |

|---------------------------------------------------------|-----|

| 图 1-1 CC253x 方框图.....                                   | 16  |

| 图 2-1 XDATA 存储空间 (显示 SFR 和 DATA 映射) .....               | 22  |

| 图 2-2 CODE 存储空间.....                                    | 23  |

| 图 2-4 中断概览.....                                         | 37  |

| 图 3-1 外部调试接口时序.....                                     | 45  |

| 图 3-2 一个字节的传输.....                                      | 45  |

| 图 3-3 典型的命令序列——没有额外等待响应.....                            | 46  |

| 图 3-4 典型的命令序列。等待响应.....                                 | 47  |

| 图 3-5 突发脉冲写命令 (前 2 个字节) .....                           | 50  |

| 图 4-1 系统时钟概览.....                                       | 57  |

| 图 6-1 使用 DMA 的闪存写.....                                  | 67  |

| 图 8-1 DMA 操作.....                                       | 85  |

| 图 8-2 可变长度 (VLEN) 传输选项.....                             | 87  |

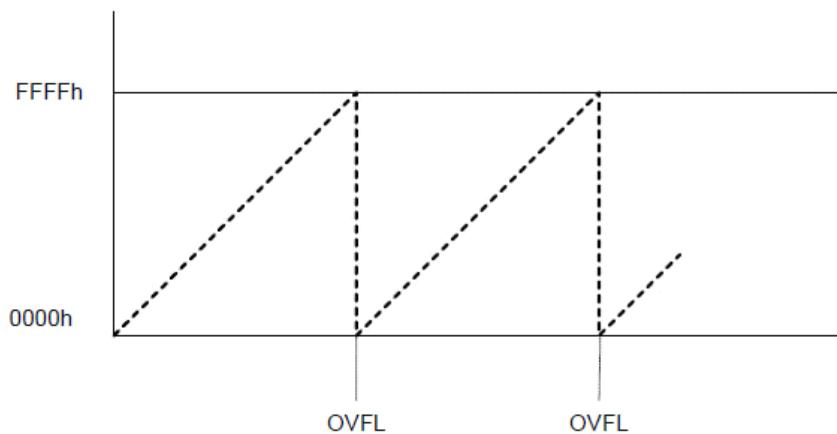

| 图 9-1 自由运行模式.....                                       | 95  |

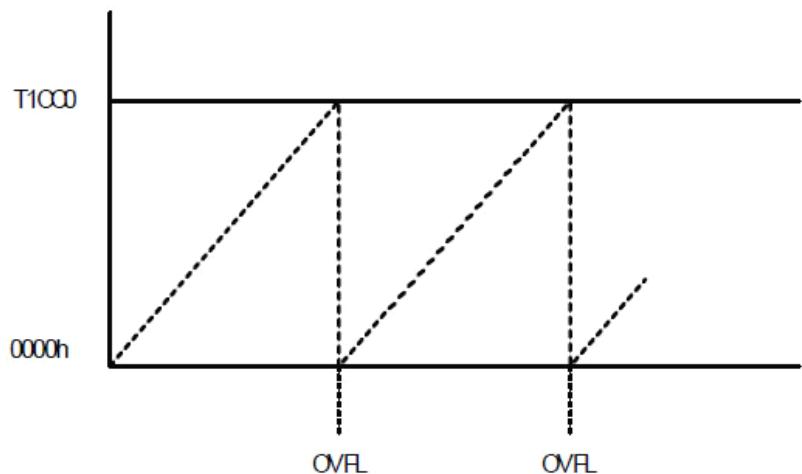

| 图 9-2 模模式.....                                          | 96  |

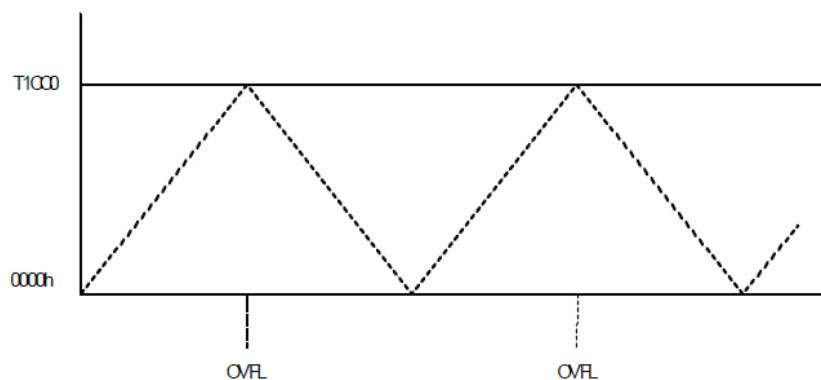

| 图 9-3 正计数/倒计数模式.....                                    | 96  |

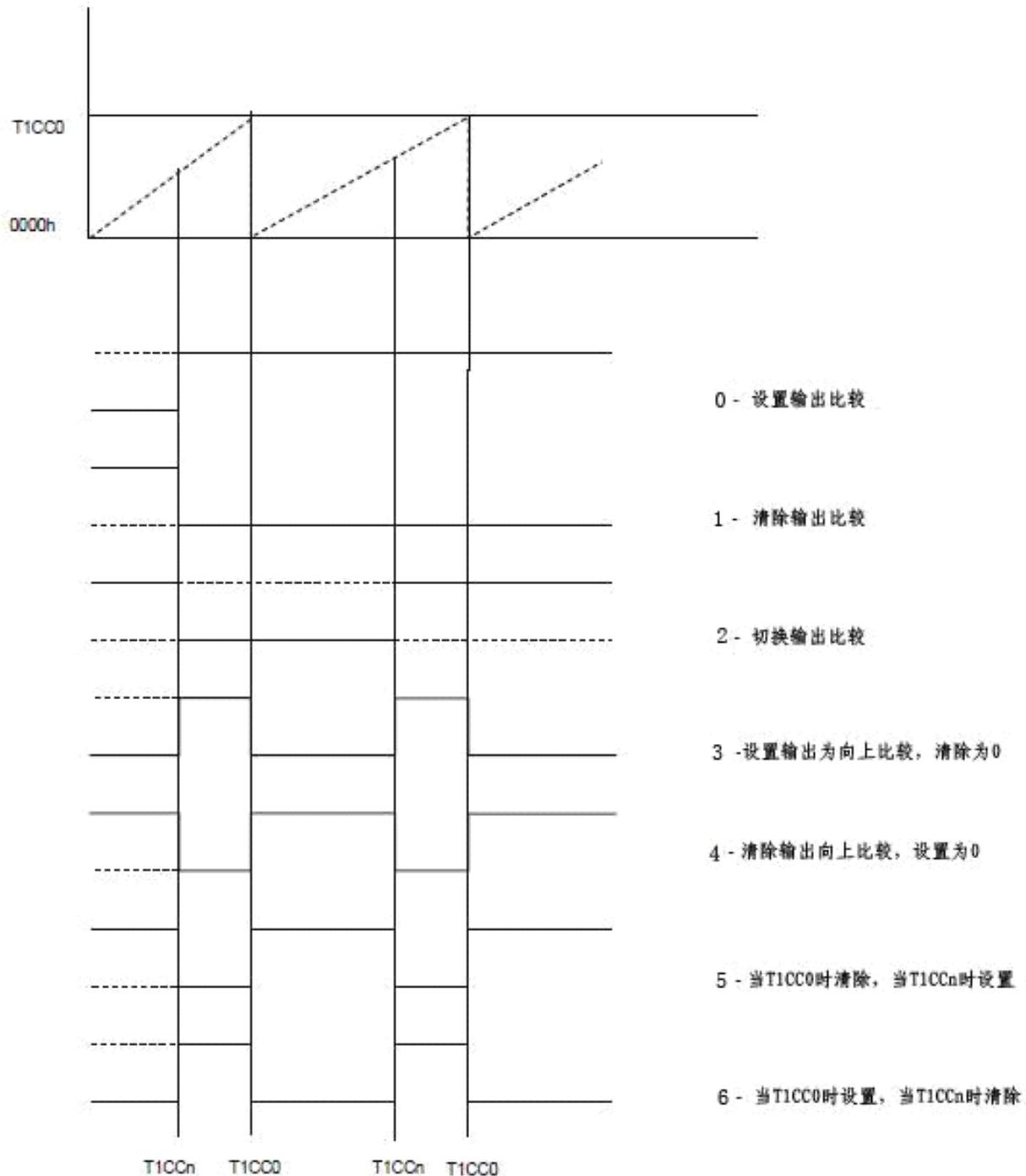

| 图 9-4 输出比较模式, 定时器自由运行模式.....                            | 99  |

| 图 9-5 输出比较模式, 定时器模模式.....                               | 100 |

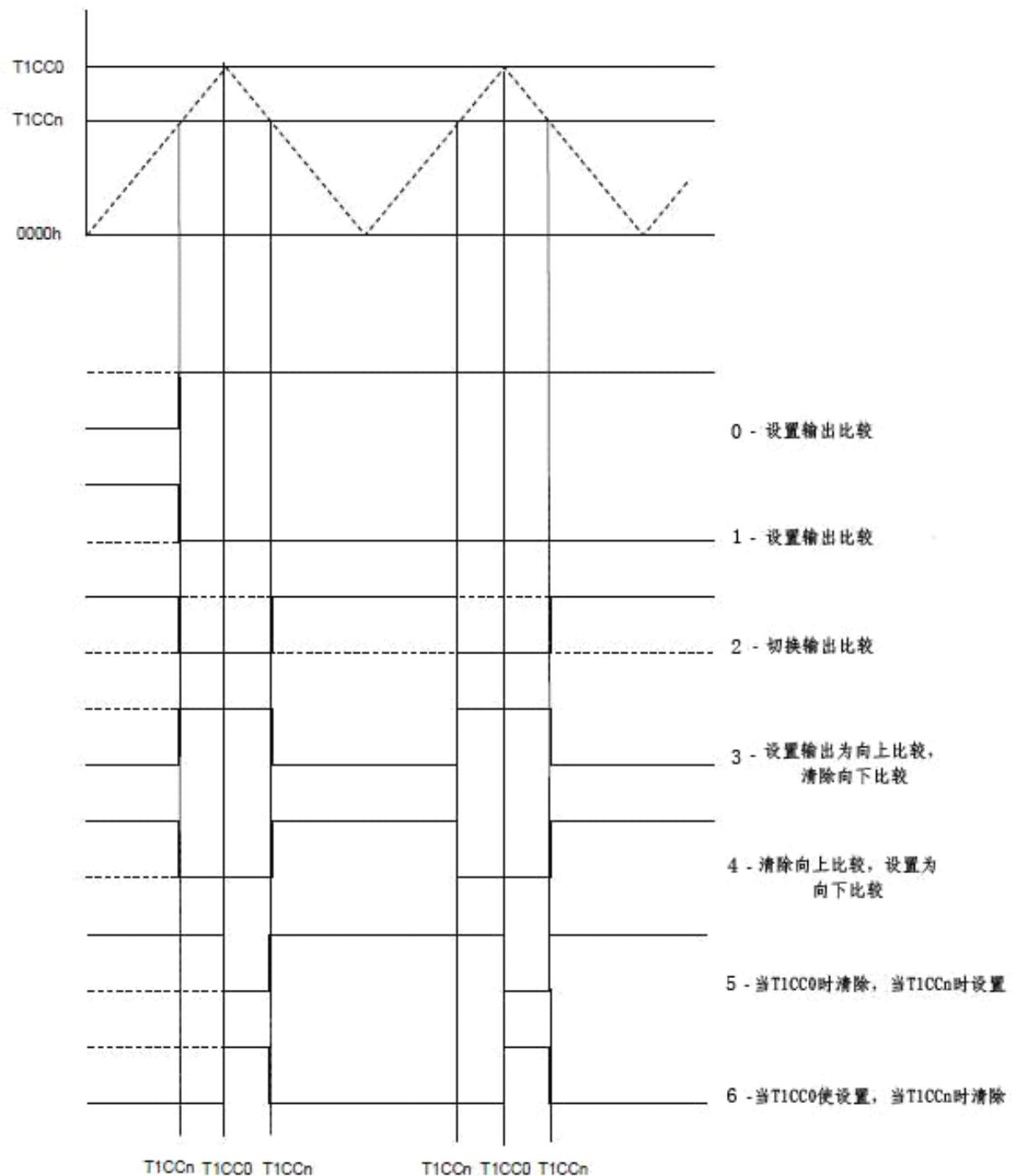

| 图 9-6 输出比较模式, 定时器正计数/倒计数模式.....                         | 101 |

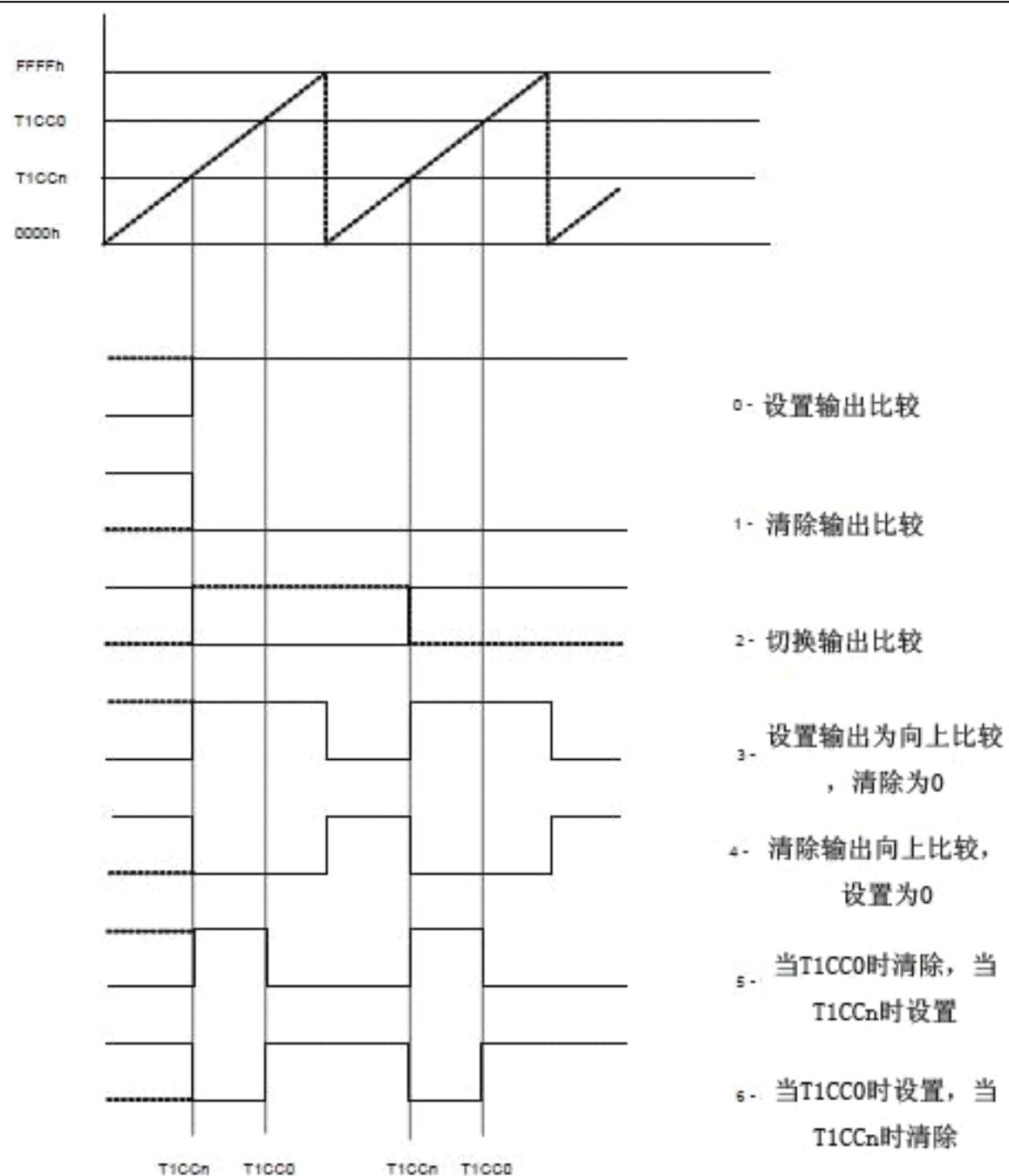

| 图 9-7 定时器在 IR 产生模式的方框图.....                             | 103 |

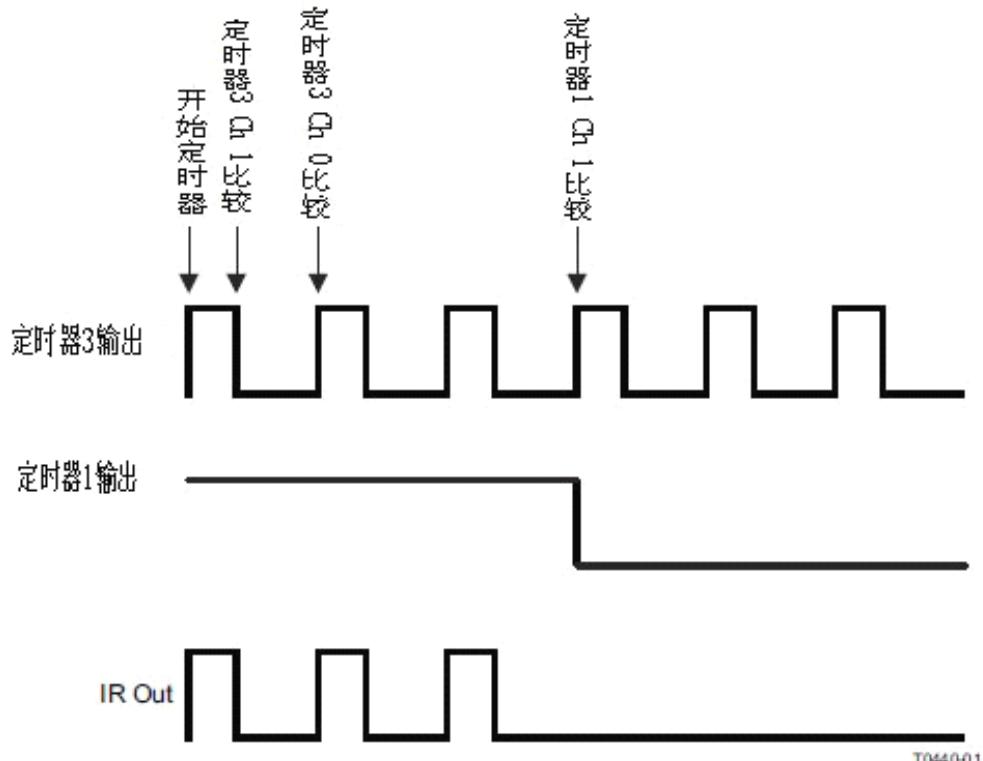

| 图 9-8 调制的波形示例.....                                      | 103 |

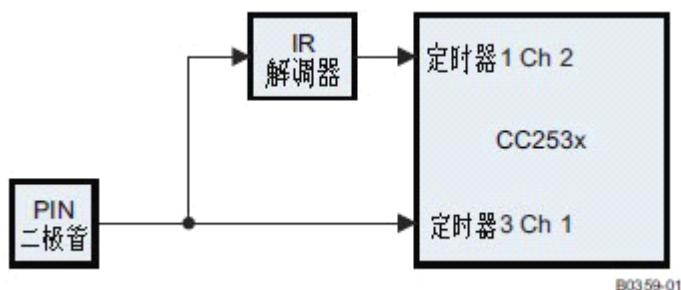

| 图 9-9 IR 线性化的方框图.....                                   | 104 |

| 图 11-1 睡眠定时器捕获 (使用 P0_0 的上升沿为例) .....                   | 119 |

| 图 12-1 ADC 方框图.....                                     | 122 |

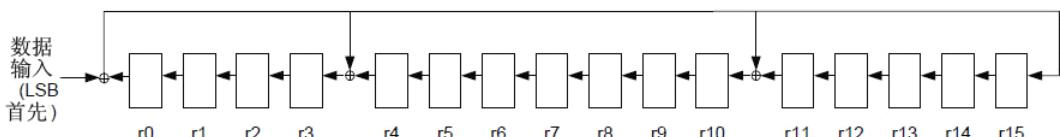

| 图 13-1 随机数发生器的基本结构.....                                 | 129 |

| 图 14-1 信息认证计划块 0.....                                   | 133 |

| 图 14-2 认证标志字节.....                                      | 133 |

| 图 14-3 信息加密程序块.....                                     | 134 |

| 图 14-4 加密标志字节.....                                      | 134 |

| 图 17-1 USB 控制器方框图.....                                  | 150 |

| 图 17-2 IN/OUT FIFO.....                                 | 154 |

| 图 19-1 调制.....                                          | 180 |

| 图 19-2 I / Q 当传送一个 0 符号芯片序列时的相位, $TC = 0.5 \mu s$ ..... | 180 |

| 图 19-3 IEEE 802.15.4 帧格式 [1]的示意图展示.....                 | 181 |

| 图 19-4 帧控制域的格式 (FCF) .....                              | 181 |

| 图 19-5 写入 TX FIFO 的帧数据.....                             | 183 |

| 图 19-6 TX 溢出.....                                       | 184 |

| 图 19-7 发送的同步头.....                                      | 185 |

| 图 19-8 FCS 硬件实现.....                                    | 186 |

| 图 19-9 SFD 信号时序.....                                    | 188 |

| 图 19-10 过滤脚本 (接收期间产生异常) .....                           | 190 |

---

|         |                         |     |

|---------|-------------------------|-----|

| 图 19-11 | 短地址和扩展地址的匹配算法.....      | 192 |

| 图 19-12 | 源地址匹配产生的中断.....         | 193 |

| 图 19-13 | 不同设置下 RX FIFO 的数据.....  | 194 |

| 图 19-14 | 确认帧格式.....              | 194 |

| 图 19-15 | 确认时序.....               | 195 |

| 图 19-16 | 命令选通时序.....             | 195 |

| 图 19-17 | FIFO 和 FIFOP 信号的行为..... | 197 |

| 图 19-18 | 主要的 FSM.....            | 199 |

| 图 19-19 | 随机字节的 FFT.....          | 201 |

| 图 19-21 | 运行一个 CSP 程序.....        | 204 |

| 图 19-22 | 硬件结构 R*寄存器访问模式的例子.....  | 220 |

## 表清单

|                                         |     |

|-----------------------------------------|-----|

| 表 1 寄存器位约定.....                         | 14  |

| 表 2-1 SFR 概览.....                       | 25  |

| 表 2-2 XREG 寄存器概览.....                   | 28  |

| 表 2-3 指令集综述.....                        | 32  |

| 表 2-4 影响标志设置的指令 <sup>(1)</sup> .....    | 35  |

| 表 2-5 中断概览.....                         | 36  |

| 表 2-6 优先级设置.....                        | 42  |

| 表 2-7 中断优先组.....                        | 42  |

| 表 2-8 中断轮流探测顺序.....                     | 43  |

| 表 3-1 闪存锁保护位结构定义.....                   | 48  |

| 表 3-2 调试命令.....                         | 48  |

| 表 3-3 调试配置.....                         | 49  |

| 表 3-4 调试状态.....                         | 49  |

| 表 4-1 供电模式.....                         | 53  |

| 表 6-1 写序列的例子.....                       | 66  |

| 表 7-1 外设 I/O 引脚映射.....                  | 72  |

| 表 8-1 DMA 触发源.....                      | 89  |

| 表 8-2 DMA 配置数据结构.....                   | 90  |

| 表 9-1 初始的比较输出值（比较模式）.....               | 98  |

| 表 9-2 38kHz 载波的频率误差计算.....              | 102 |

| 表 10-1 初始的比较输出值（比较模式）.....              | 112 |

| 表 16-1 32 MHz 系统时钟常用的波特率设置.....         | 144 |

| 表 17-1 USB 中断标志中断使能屏蔽寄存器.....           | 151 |

| 表 17-2 EP1-5 的 FIFO 大小.....             | 154 |

| 表 18-1 内部寄存器.....                       | 169 |

| 表 19-1 帧过滤和源匹配存储器映射.....                | 178 |

| 表 19-2 IEEE 802.15.4-2006 符号到芯片的映射..... | 180 |

| 表 19-3 FSM 状态映射.....                    | 200 |

| 表 19-4 指令集综述.....                       | 205 |

| 表 19-5 寄存器概览.....                       | 219 |

| 表 19-6 需要从其默认值更新的寄存器.....               | 219 |

| 表 19-7 寄存器位访问模式.....                    | 220 |

## 关于本手册

2.4GHz 的 CC253x 片上系统解决方案适合于广泛的应用。它们可以很容易建立在基于 IEEE 802.15.4 标准协议（RemoTI™网络协议、TIMAC 软件和用于 ZigBee®兼容解决方案的 Z-Stack™软件）上面，或是专门的 SimpliciTI™网络协议上面。但是它们的使用不仅限于这些协议。例如 CC253x 系列还适合于 6LoWPAN 和无线 HART 的实现。

本手册的每一章描述了一个模块或外设的详细信息，但是并没有完全列出 CC253x 系列所有设备的全部功能。

关于详细的技术参数，比如功率消耗和 RF 性能，见设备具体的数据手册。

## 德州仪器的相关文档和软件

相关文档（如 CC2530 数据手册 <http://www-s.ti.com/sc/techlit/swrs081>）可在附录 C 中找到。

关于可以用于 CC253x 片上系统解决方案（例如用于无线电性能和功能评估的 SmartRF™软件）的软件的更多信息见第 21 章，这一章还包括关于 RemoTI 网络协议、SimpliciTI 网络协议、TIMAC 软件和 Z-Stack 软件的更多信息。

## FCC 警告

这一设备仅用于实验室测试环境。它可以产生、使用且可以辐射射频能量，但是尚未测试是否兼容根据 FCC 规则 15 部分计算设备的限制，它的设计是为了提供合理的保护，免受射频干扰。这一设备在其他环境下的运行可能导致对射频通信的干扰，在这种情况下自费的用户需要采取可能要求的纠正这一干扰的一切措施。

## 如果你需要帮助

所有技术支持渠道均通过 TI 产品信息中心（PIC）——[www.ti.com/support](http://www.ti.com/support) 提供。

要发送电子邮件请求，请在以下链接输入您的联系信息以及您的请求——[PIC 请求表](#)。

还可以访问 TI E2E 社区的低功耗 RF 和 ZigBee 部分（[www.ti.com/lprf-forum](http://www.ti.com/lprf-forum)），在这里您可以很容易与其他 CC253x 用户沟通，并找到 FAQ、设计说明、应用说明、视频等等。

您还可以参见 [TI 模拟&混合信号知识库](#)。

## 词汇表

本用户指南使用的缩略语可在附录 A 中找到。

RemoTI、Z-Stack、SimpliciTI、SmartRF 是德州仪器的商标。

Microsoft、Windows 是微软公司的商标。

ZigBee 是 ZigBee 联盟的注册商标。

## 设备

CC253x 片上系统解决方案系列包括若干设备。下表提供了每个设备不同外设、内存大小等的概述和信息。

CC253x 系列概览

| 特征         | CC2530F32/F64/F128/F256   | CC2531F256 |

|------------|---------------------------|------------|

| FLASH_SIZE | 32 KB/64 KB/128 KB/256 KB | 256KB      |

| SRAM_SIZE  | 8KB                       | 8KB        |

| USB        | 不包括                       | 包括         |

图例：

FLASH\_SIZE –闪存的大小，以字节为单位

SRAM\_SIZE –SRAM 的大小，以字节为单位

## 寄存器约定

每个 SFR 和 XREG 寄存器在一个单独的表中描述，每个表标题按照以下格式：

SFR 寄存器：寄存器名称（SFR 地址）——寄存器描述

XREG 寄存器：寄存器名称（XDATA 地址）——寄存器描述

每个表的每一行中有五列描述寄存器部分，描述如下：

列 1——位：说明指定行描述的是寄存器的哪一位

列 2——名称：寄存器部分的具体名称

列 3——复位：寄存器部分的复位/初始值

列 4——R/W：表示各个位是否可访问的密钥（更多详细信息见表 1）

列 5——描述：寄存器部分的更多信息，通常是不同值的描述

在寄存器描述中，每个寄存器位用一个符号（R/W）表示寄存器位的访问模式。寄存器值总是以二进制表示法给定，除非前缀是 0x 表示十六进制表示法。

表 1 寄存器位约定

| 符号  | 访问模式 |

|-----|------|

| R/W | 读/写  |

| R   | 只读   |

| R0  | 读作 0 |

| R1  | 读作 1 |

| W   | 只写   |

| W0  | 写作 0 |

| W1  | 写作 1 |

| H0  | 硬件清除 |

| H1  | 硬件设置 |

## 简介

如前言所述，CC253x 设备系列为广泛的应用提供了解决方案。为了帮助用户开发这些应用，这一用户指南的重点是 CC253x 设备系列不同的构造模块的用法。关于详细的设备描述、完整的功能列表和性能参数，读者可以参见各个设备的数据手册。

为了方便获取相关信息，以下小节引导读者到本指南不同的章节。

| 标题           | 页  |

|--------------|----|

| 1.1 概述.....  | 16 |

| 1.2 应用 ..... | 19 |

## 1.1 概述

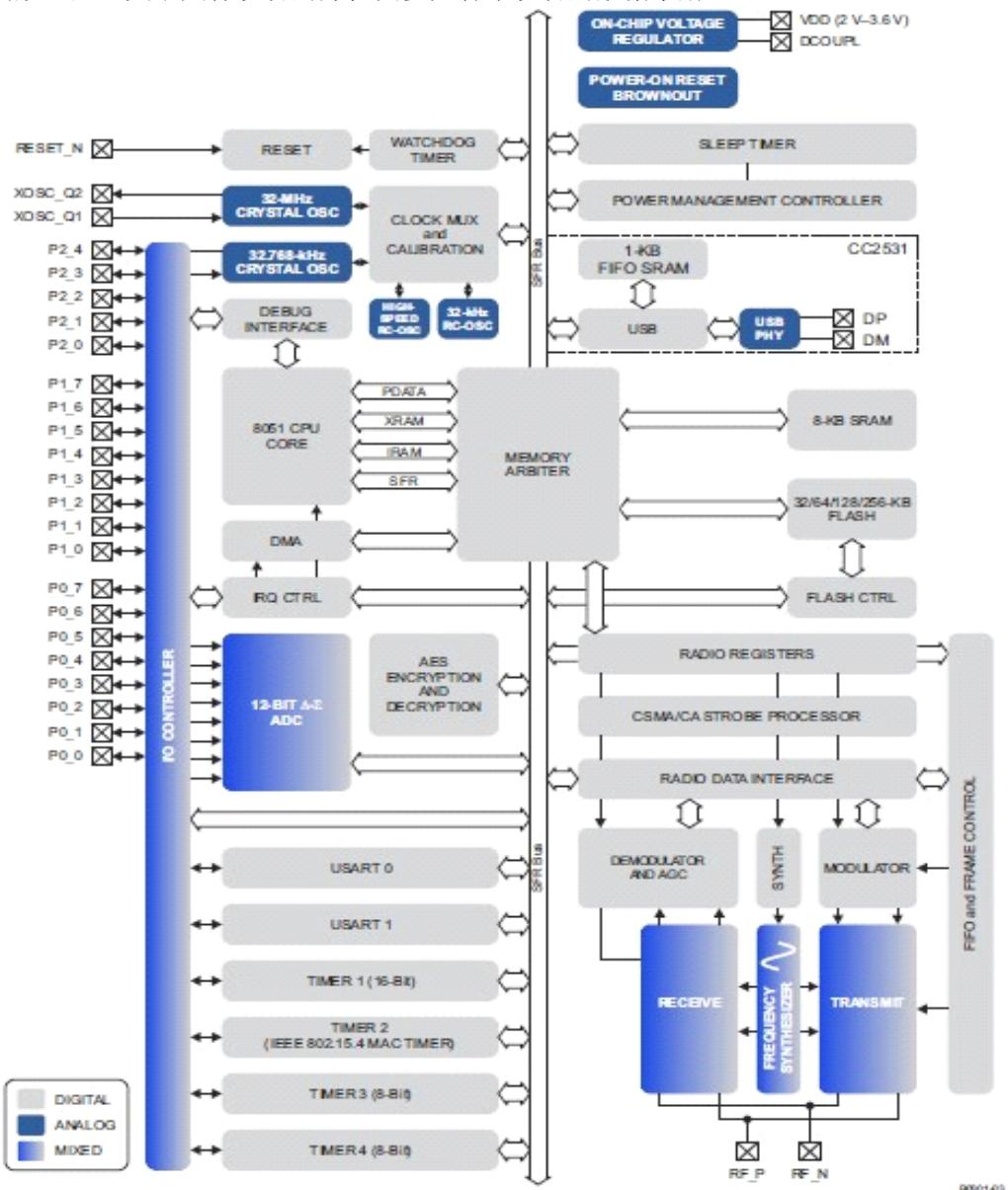

图 1-1 的方框图显示了 CC253x 设备系列不同的构造模块。并没有列出 CC253x 所有设备的所有模块和外设的全部功能和函数，因此关于具体设备的方框图参见各个设备的数据手册。

图 1-1 CC253x 方框图

模块大致可以分为三种类型：CPU 和内存相关的模块；外设、时钟和电源管理相关的模块；无线电相关的模块。

### 1.1.1 CPU 和内存

CC253x 设备系列使用的 **8051 CPU 内核** 是一个单周期的 8051 兼容内核。它有三个不同的存储器访问总线 (SFR、DATA 和 CODE/XDATA)，以单周期访问 SFR、DATA 和主 SRAM。它还包括一个调试接口和一个 18 输入的扩展中断单元。CPU 和内存的详细功能见第 2 章。

**中断控制器** 提供了 18 个中断源，分为六个中断组，每组与四个中断优先级相关。当设备从空闲模式回到活动模式，也会发出一个中断服务请求。一些中断还可以从睡眠模式唤醒设备（供电模式 1-3），详细信息参见第 4 章。

**内存仲裁器** 位于系统中心，因为它通过 SFR 总线，把 CPU 和 DMA 控制器和物理存储器和所有外设连接在一起。内存仲裁器有四个存取访问点，访问每一个可以映射到三个物理存储器之一：一个 8-KB SRAM、一个闪存存储器和一个 XREG/SFR 寄存器。它负责执行仲裁，并确定同时到同一个物理存储器的内存访问的顺序。

**8-KB SRAM** 映射到 DATA 存储空间和 XDATA 存储空间的一部分。8-KB SRAM 是一个超低功耗的 SRAM，当数字部分掉电时（供电模式 2 和 3）能够保留自己的内容。这对于低功耗应用是一个很重要的功能。

**32/64/128/256 KB 闪存块** 为设备提供了内电路可编程的非易失性程序存储器，映射到 CODE 和 XDATA 存储空间。除了保存程序代码和常量，非易失性程序存储器允许应用程序保存必须保留的数据，这样在设备重新启动之后可以使用这些数据。使用这个功能，例如可以利用已经保存的网络具体数据，就不需要经过完整的启动、网络寻找和加入过程。

### 1.1.2 时钟和电源管理

数字内核和外设由一个 1.8-V 低差 **稳压器** 供电（第 20 章）。另外 CC253x 包括一个电源管理功能（第 4 章），可以实现使用不同供电模式的长电池寿命的低功耗应用运行。有五种不同的 **复位源** 来复位设备，详细信息见第 5 章。

### 1.1.3 外设

CC2530 包括许多不同的外设，允许应用程序设计者开发先进的应用。

**调试接口**（第 3 章）执行一个专有的两线串行接口，用于内电路调试。通过这个调试接口，可以执行整个闪存存储器的擦除、控制使能哪个振荡器、停止和开始执行用户程序、执行 8051 内核提供的指令、设置代码断点，以及内核中全部指令的单步调试。使用这些技术，可以很好地执行内电路的调试和外部闪存的编程。

设备含有闪存存储器以存储程序代码。闪存存储器可通过用户软件和调试接口编程（如上所述）。**闪存控制器**（第 6 章）处理写入和擦除嵌入式闪存存储器。闪存控制器允许页面擦除和 4 字节编程。

**I/O 控制器**（第 7 章）负责所有通用 I/O 引脚。CPU 可以配置外设模块是否控制某个引脚或它们是否受软件控制，如果是的话，每个引脚配置为一个输入还是输出，是否连接衬垫里的一个上拉或下拉电阻。CPU 中断可以分别在每个引脚上使能。每个连接到 I/O 引脚的外设可以在两个不同的 I/O 引脚位置之间选择，以确保在不同应用程序中的灵活性。

系统可以使用一个多功能的五通道 **DMA 控制器**（第 8 章），使用 XDATA 存储空间访问存储器，因此能够访问所有物理存储器。每个通道（触发器、优先级、传输模式、寻址模式、源和目标指针和传输计数）用 DMA 描述符在存储器任何地方配置。许多硬件外设（AES 内核、闪存控制器、USART、定时器、ADC 接口）通过使用 DMA 控制器在 SFR 或 XREG 地址和闪存/SRAM 之间进行数据传输，获得高效率操作。

**定时器 1**（第 9 章）是一个 16 位定时器，具有定时器/计数器/PWM 功能。它有一个可编程的分频器，一个 16 位周期值，和五个各自可编程的计数器/捕获通道，每个都有一个 16 位比较值。每个计数器/捕获通道可以用

---

作一个 PWM 输出或捕获输入信号边沿的时序。它还可以配置在 IR 产生模式，计算定时器 3 周期，输出和定时器 3 的输出相与，用最小的 CPU 互动产生调制的消费型 IR 信号（见 9.9 节）。

**定时器 2 (MAC 定时器)** (第 18 章) 是专门为支持 IEEE 802.15.4 MAC 或软件中其他时槽的协议设计。定时器有一个可配置的定时器周期和一个 8 位溢出计数器，可以用于保持跟踪已经经过的周期数。一个 16 位捕获寄存器也用于记录收到/发送一个帧开始界定符的精确时间，或传输结束的精确时间，还有一个 16 位输出比较寄存器可以在具体时间产生不同的选通命令（开始 RX，开始 TX，等等）到无线模块。

**定时器 3 和定时器 4** (第 10 章) 是 8 位定时器，具有定时器/计数器/PWM 功能。它们有一个可编程的分频器，一个 8 位的周期值，一个可编程的计数器通道，具有一个 8 位的比较值。每个计数器通道可以用作一个 PWM 输出。

**睡眠定时器** (第 11 章) 是一个超低功耗的定时器，计算 32-kHz 晶振或 32-kHz RC 振荡器的周期。睡眠定时器在除了供电模式 3 的所有工作模式下不断运行。这一定时器的典型应用是作为实时计数器，或作为一个唤醒定时器跳出供电模式 1 或 2。

**ADC** (第 12 章) 支持 7 到 12 位的分辨率，分别在 30 kHz 或 4 kHz 的带宽。DC 和音频转换可以使用高达八个输入通道 (端口 0)。输入可以选择作为单端或差分。参考电压可以是内部电压、AVDD 或是一个单端或差分外部信号。ADC 还有一个温度传感输入通道。ADC 可以自动执行定期抽样或转换通道序列的程序。

**随机数发生器** (第 13 章) 使用一个 16 位 LFSR 来产生伪随机数，这可以被 CPU 读取或由选通命令处理器直接使用。例如随机数可以用作产生随机密钥，用于安全。

**AES 协处理器** (第 14 章) 允许用户使用带有 128 位密钥的 AES 算法加密和解密数据。这一内核能够支持 IEEE 802.15.4 MAC 安全、ZigBee 网络层和应用层要求的 AES 操作。

一个内置的**看门狗定时器** (第 15 章) 允许设备在固件挂起的情况下复位自身。当看门狗定时器由软件使能，它必须定期清除；否则，当它超时它就复位设备。或者它可以配置用作一个通用 32-kHz 定时器。

**USART 0 和 USART 1** (第 16 章) 每个被配置为一个 SPI 主/从或一个 UART。它们为 RX 和 TX 提供了双缓冲，以及硬件流控制，因此非常适合于高吞吐量的全双工应用。每个都有自己的高精度波特率发生器，因此可以使普通定时器空闲出来用作其他用途。

**USB 2.0 全速控制器** (仅 CC2531 可用) 有 5 个端点，1KB FIFO RAM 的双缓冲。它的功能描述在第 17 章。

#### 1.1.4 无线电

CC253x 设备系列提供了一个 **IEEE 802.15.4 兼容无线收发器**。RF 内核控制模拟无线模块。另外，它提供了 MCU 和无线设备之间的一个接口，这使得可以发出命令、读取状态、自动操作和确定无线设备事件的顺序。无线设备还包括一个数据包过滤和地址识别模块。关于无线电的更多详细信息可以在第 19 章找到。

## 1.2 应用

如概述（1.1 节）所示，这一用户指南的重点是使用可用的不同模块，来建立基于 CC253x 设备系列的不同类型的应用程序。如果查看完整的应用程序开发过程，另外的一些信息很有用。但是，因为这样的信息和帮助不是设备特定的（即不是 CC253x 设备系列唯一的），读者可以参考以下段落的另外的信息源。

第一步是通过购买一个 **开发套件**（见设备具体的产品网站，找到相关开发套件的链接），设置开发环境（HW 工具等）。开发套件带有一个现成的演示和关于如何设置开发环境的信息；安装所需的驱动（通过安装 **SmartRF 软件** 可以轻松完成，21.1 节），设置编译器工具链，等等。只要已经安装了开发环境，就可以准备开始应用程序的开发了。

写应用程序软件的最简单的方法是把应用程序建立在可用的标准协议之一（**RemoTI** 网络协议，21.2 节；**TIMAC** 软件，21.4 节；或用于 ZigBee 兼容解决方案的 **Z-Stack** 软件，21.5 节）上面；或者专门的 **SimpliciTI** 网络协议（21.3 节）上面。它们都带有一些实例应用程序。

对于用户具体 HW 的硬件布局设计，设计人员可以在不同的产品页面（B.1 节）上找到参考设计。通过复制这些设计，设计人员能够获得最佳性能。已开发的 HW 可以使用 SmartRF Studio 软件（21.1 节）很容易地进行测试。

如果最终的系统没有达到预期的性能，建议在开发套件的硬件上尝试开发的软件，看看在这里工作地如何。要检查用户具体的 HW，使用 SmartRF Studio 软件，在相同的设置下来比较开发套件性能和用户具体的 HW，这是一个良好的开端。

用户还可以通过加入 **低功耗 RF 网络社区**（B.2 节）和订阅 **低功耗 RF 电子简讯**（B.4 节），找到另外的信息和帮助。

要联系第三方以帮助开发或者要使用模块，查询德州仪器 **低功耗 RF 开发商网络**（B.3 节）。

**8051 CPU**

片上系统解决方案是基于一个增强的 8051 内核。关于此内核、存储映射、指令集和中断的更多详细信息在以下章节描述。

| 标题              | 页  |

|-----------------|----|

| 2.1 8051 CPU 简介 | 22 |

| 2.2 存储器         | 22 |

| 2.3 CPU 寄存器     | 30 |

| 2.4 指令集总结       | 32 |

| 2.5 中断          | 36 |

## 2.1 8051 CPU 简介

增强型 8051 内核使用标准的 8051 指令集。因为以下原因指令执行比标准的 8051 更快：

- 每个指令周期是一个时钟，而标准的 8051 每个指令周期是 12 个时钟。

- 消除了总线状态的浪费。

因为一个指令周期与可能的内存存取是一致的，大多数单字节指令在一个时钟周期内执行。除了速度提高之外，增强型 8051 内核还包括结构上的改善：

- 第二个数据指针

- 一个扩展的 18 源中断单元

8051 内核的对象代码兼容业界标准的 8051 微控制器。即对象代码使用 8051 内核上执行的业界标准的 8051 编译器或汇编器编译，在功能上是等同的。但是，因为 8051 内核使用了不同于许多其他 8051 类型的一个指令时序，带有时序循环的已有代码可能需要修改。而且，因为诸如定时器和串行端口的外设单元不同于其他 8051 内核，包含使用外设单元 SFR 的指令的代码不能正确运行。

闪存预取默认不是使能的，但是提高了 CPU 高达 33% 的性能。这一设置的代价是功率消耗略有增加，但是因为这样更快，大多数情况下提高了能源消耗。闪存预取可以在 FCTL 寄存器中使能。

## 2.2 存储器

8051 CPU 结构有四个不同的存储空间。8051 有单独的存储空间用于程序存储和数据存储。8051 存储空间如下（详细信息见 2.2.1 节和 2.2.2 节）：

**CODE:** 一个只读的存储空间，用于程序存储。这一存储空间地址是 64KB。

**DATA:** 一个读/写的数据存储空间，可以直接或间接被一个单周期 CPU 指令访问。这一存储空间地址是 256 字节。DATA 存储空间较低的 128 字节可以直接或间接寻址，较高的 128 字节只能间接寻址。

**XDATA:** 一个读/写的数据存储空间，通常需要 4-5 个 CPU 指令周期来访问。这一存储空间地址是 64KB。而且访问 XDATA 存储器慢于访问 DATA，因为 CODE 和 XDATA 存储空间共享 CPU 内核上的一个通用总线，因此来自 CODE 的指令预取可以不必和 XDATA 访问并行执行。

**SFR:** 一个读/写的寄存器存储空间，可以直接被一个 CPU 指令访问。这一存储空间含有 128 字节。对于地址是被 8 整除的 SFR 寄存器，每一位还可以单独寻址。

这四个存储空间在 8051 结构中是分开的，但是在设备中有部分是重叠的，以减轻 DMA 传输和硬件调试操作的负担。

不同的存储空间如何映射到三个物理存储器（闪存程序存储器、SRAM 和存储映射存储器）在 2.2.1 节和 2.2.2 节描述。

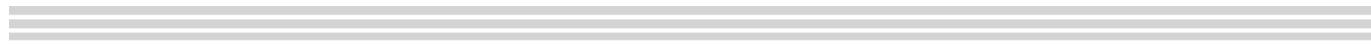

### 2.2.1 存储器映射

存储器映射在两个重要方面不同于标准的 8051 内存映射，如以下段落所述。

首先，为了使得 DMA 控制器访问全部物理存储空间，并由此使得 DMA 在不同 8051 存储空间之间进行传输，CODE 和 SFR 部分存储空间映射到 XDATA 存储空间。

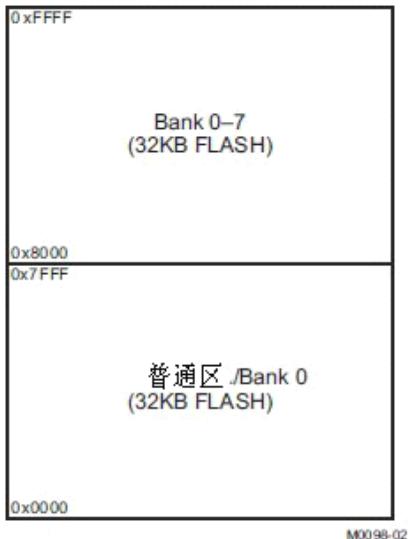

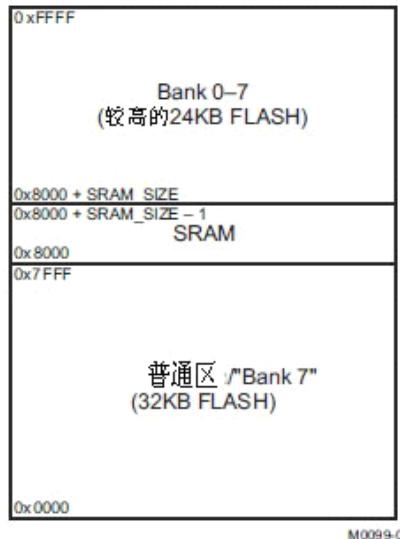

第二, CODE 存储器空间映射可以使用两个备用机制。第一个机制是标准的 8051 映射, 只有程序存储器(即闪存存储器)映射到 CODE 存储空间。这一映射设备复位后默认使用的。

第二个机制用于执行来自 SRAM 的代码。在这种模式下, SRAM 映射到 0x8000 到(0x8000 + SRAM\_SIZE - 1)的区域。这一映射如图 2-2 所示。执行来自 SRAM 的代码提高了性能, 并减少了功率消耗。

XDATA 较高的 32KB 是一个只读的区域, 叫做 XBANK。任何可用的 32KB 闪存区可以在这里被映射出来。这使得软件可以访问整个闪存存储器。这一区域典型用作存储另外的常量数据。

所有 8051 存储空间的映射的详细信息见 2.2.2 节。

显示不同的物理存储器如何映射到 CPU 存储空间的存储映射见图 2-1 到图 2-3。可用的闪存区的编号取决于闪存大小的选项。

图 2-1 XDATA 存储空间 (显示 SFR 和 DATA 映射)

图 2-2 CODE 存储空间

图 2-3 用于运行来自 SRAM 的代码的 CODE 存储空间

## 2.2.2 CPU 存储空间

**XDATA 存储空间:** XDATA 存储映射见图 2-1。

SRAM 映射到的地址范围是 0x0000 到(SRAM\_SIZE – 1)。

XREG 区域映射到 1-KB 地址区域(0x6000–0x63FF)。这些寄存器是另外的寄存器，有效地扩展 SFR 寄存器空间。一些外设寄存器和大多数无线电控制和数据寄存器映射到这里。

SFR 寄存器映射到地址区域(0x7080–0x70FF)。

闪存信息页面 (2 KB) 映射到地址区域(0x7800–0x7FFF)。这是一个只读区域，包含有关设备的各种信息。

XDATA 存储空间(0x8000–0xFFFF)的较高 32KB 是一个只读的闪存代码区 (XBANK)，可以使用 MEMCTR.XBANK[2:0]位映射到任何一个可用的闪存区。

闪存存储器 SRAM 和寄存器到 XDATA 的映射允许 DMA 控制器和 CPU 访问在一个统一的地址空间内的所有物理存储器。

写入存储映射中未执行的区域 (图中的阴影部分) 没有影响。从为执行的区域读出返回 0x00。写只读区域比如闪存区域将被忽略。

**CODE 存储空间:** CODE 存储空间是 64KB，分为一个普通区域 (0x0000–0x7FFF) 和一个区域 (0x8000–0xFFFF)，如图 2-2。普通区域总是映射到物理闪存存储器较低的 32KB (区 0)。另一区域可以映射到任一可用的 32-KB 闪存区 (从 0 到 7)。可用的闪存区的编号取决于闪存大小的选项。使用闪存区选择寄存器 FMAP 来选择闪存区。在 32 KB 设备上，闪存存储器不能映射到上面的区域。从这些设备的这一区域读返回 0x00。

要允许从 SRAM 执行程序，可以映射可用的 SRAM 到区域 (范围从 0x8000 到(0x8000+SRAM\_SIZE-1)) 较低的区域。当前选择的区的其余部分仍映射到地址区域 (0x8000 + SRAM\_SIZE) 到 0xFFFF。设置 MEMCTR.XMAP 位来使能这一功能。

**DATA 存储空间:** DATA 存储器 8 位的地址区域映射到 SRAM 较高的 256 字节，即地址范围从(SRAM\_SIZE-256)到(SRAM\_SIZE-1)。

**SFR 存储空间:** 128 个条目的硬件寄存器区域是通过这一存储空间访问的。SFR 寄存器还可以通过 XDATA 地址空间 (地址范围是(0x7080 –0x70FF)) 访问。一些 CPU 具体的 SFR 寄存器驻留在 CPU 内核，只能使用 SFR 存储空间访问，不能通过复制映射到 XDATA 存储空间访问。这些具体的 SFR 寄存器列在 SFR 寄存器表中。

## 2.2.3 物理存储器

**RAM:** 所有设备都包括静态 RAM。上电时，RAM 的内容是未定义的。RAM 内容在所有供电模式下都保留。

**闪存存储器:** 片上闪存存储器主要是为了保存程序代码和常量数据。闪存存储器有以下功能：

- 页面大小：2 KB

- 闪存页面擦除时间：20ms

- 闪存芯片（批量）擦除时间：20ms

- 闪存写时间（4 字节）：20 $\mu$ s

- 数据保留（室温下）：100 年

- 编程/擦除次数：20,000 次

闪存存储器由一组 2 KB 的页面组成。较高的可用页面的 16 字节包括页面锁位和调试锁位。每一个页面都有一个锁位，除了不是处于调试模式就暗示锁定的锁位页面。当页面的锁位是 0，可以擦除/写该页。当调试锁位是 0，调试接口上的大多数命令被忽略。调试锁位的主要目的是保护闪存的内容不被读出。闪存控制器用作写和擦除闪存存储器的内容。

当 CPU 从闪存存储器中读指令和常量，它通过一个缓存取出指令。指令的四个字节和常量数据的四个字节被缓存，在 4 字节的边界。即例如当 CPU 从地址 0x00F1 读，字节 0x00F0–0x00F3 被缓存。一个单独的预取单元可以用来预取指令的另外 4 个字节。这一缓存主要是为了通过减少访问闪存存储器的总时间来减少功率消耗。缓存可以通过 FCTL.CM[1:0]寄存器位禁用。这样做增加了功率消耗，是不推荐的。当使用默认缓存模式和带预取的缓存模式，即不能准确确定读取一组指令花费的时钟周期数量，从闪存读的执行时间不是精确到周期的。要获得精确到周期的执行，就要使能实时缓存模式，确保所有 DMA 传输有低优先级。预取模式提高性能高达 33%，但因为浪费了闪存读，代价是增加了功率消耗。一般地，性能可以提高 15%-20%。但是由于等待闪存返回指令/数据浪费的时钟周期较少，总的能量是减少的（取决于应用程序）。这是非常依赖于应用程序的，需要有效的使用供电模式。

**信息页面**是一个 2 KB 的只读区域，存储设备信息。其他信息中它包括来自 TI 地址范围的一个唯一的 IEEE 地址。它以最低位优先的形式存储在 XDATA 地址 0x780C。将出版一个单独的设计说明，详细介绍信息页面的内容。

**SFR 寄存器:** 特殊功能寄存器 (SFR) 控制 8051CPU 内核和/或外设的一些功能。许多 8051CPU 内核的 SFR 和标准的 8051SFR 相同。但是有一些控制功能的另外的 SFR，是标准 8051 中所没有的。另外的 SFR 用于和外设单元以及 RF 收发器接口。

表 2-1 显示了设备中所有 SFR 的地址。8051 内部 SFR 以灰色背景显示，而其他 SFR 是具体于设备的 SFR。

---

**注意:** 所有内部 SFR（在表 2-1 中以灰色背景显示）只能通过 SFR 空间访问，因为这些寄存器没有映射到 XDATA 空间。但例外是端口寄存器（P0、P1 和 P2）可以从 XDATA 中读取。

---

**表 2-1 SFR 概览**

| 寄存器名称    | SFR 地址 | 模块  | 描述                          |

|----------|--------|-----|-----------------------------|

| ADCCON1  | 0xB4   | ADC | ADC 控制 1                    |

| ADCCON2  | 0xB5   | ADC | ADC 控制 2                    |

| ADCCON3  | 0xB6   | ADC | ADC 控制 3                    |

| ADCL     | 0xBA   | ADC | ADC 数据低字节                   |

| ADCH     | 0xBB   | ADC | ADC 数据高字节                   |

| RNDL     | 0xBC   | ADC | 随机数发生器数据低字节                 |

| RNDH     | 0xBD   | ADC | 随机数发生器数据高字节                 |

| ENCDI    | 0xB1   | AES | 加密/解密输入数据                   |

| ENCDO    | 0xB2   | AES | 加密/解密输出数据                   |

| ENCCS    | 0xB3   | AES | 加密/解密控制和状态                  |

| P0       | 0x80   | CPU | 端口 0。可从 XDATA (0x7080) 中读出。 |

| SP       | 0x81   | CPU | 栈指针                         |

| DPL0     | 0x82   | CPU | 数据指针 0 低字节                  |

| DPH0     | 0x83   | CPU | 数据指针 0 高字节                  |

| DPL1     | 0x84   | CPU | 数据指针 1 低字节                  |

| DPH1     | 0x85   | CPU | 数据指针 1 高字节                  |

| PCON     | 0x87   | CPU | 供电模式控制                      |

| TCON     | 0x88   | CPU | 中断标志                        |

| P1       | 0x90   | CPU | 端口 1。可从 XDATA (0x7090) 读出。  |

| DPS      | 0x92   | CPU | 数据指针选择                      |

| S0CON    | 0x98   | CPU | 中断标志 2                      |

| IEN2     | 0x9A   | CPU | 中断使能 2                      |

| S1CON    | 0x9B   | CPU | 中断标志 3                      |

| P2       | 0xA0   | CPU | 端口 2。可从 XDATA (0x70A0) 读出。  |

| IEN0     | 0xA8   | CPU | 中断使能 0                      |

| IP0      | 0xA9   | CPU | 中断优先级 0                     |

| IEN1     | 0xB8   | CPU | 中断使能 1                      |

| IP1      | 0xB9   | CPU | 中断优先级 1                     |

| IRCON    | 0xC0   | CPU | 中断标志 4                      |

| PSW      | 0xD0   | CPU | 程序状态字                       |

| ACC      | 0xE0   | CPU | 累加器                         |

| IRCON2   | 0xE8   | CPU | 中断标志 5                      |

| B        | 0xF0   | CPU | B 寄存器                       |

| DMAIRQ   | 0xD1   | DMA | DMA 中断标志                    |

| DMA1CFG1 | 0xD2   | DMA | DMA 通道 1-4 配置地址低字节          |

| DMA1CFGH | 0xD3   | DMA | DMA 通道 1-4 配置地址高字节          |

| DMA0CFG1 | 0xD4   | DMA | DMA 通道 0 配置地址低字节            |

| DMA0CFGH | 0xD5   | DMA | DMA 通道 0 配置地址高字节            |

| DMAARM   | 0xD6   | DMA | DMA 通道准备工作                  |

| DMAREQ   | 0xD7   | DMA | DMA 通道开始请求和状态               |

| —        | 0xAA   | —   | 保留                          |

| —        | 0x8E   | —   | 保留                          |

| —        | 0x99   | —   | 保留                          |

| —        | 0xB0   | —   | 保留                          |

| —        | 0xB7   | —   | 保留                          |

| —        | 0xC8   | —   | 保留                          |

表 2-1 SFR 概览 (续表)

| 寄存器名称     | SFR 地址 | 模块     | 描述                   |

|-----------|--------|--------|----------------------|

| P0IFG     | 0x89   | IOC    | 端口 0 中断状态标志          |

| P1IFG     | 0x8A   | IOC    | 端口 1 中断状态标志          |

| P2IFG     | 0x8B   | IOC    | 端口 2 中断状态标志          |

| PICTL     | 0x8C   | IOC    | 端口引脚中断屏蔽和边沿          |

| P0IEN     | 0xAB   | IOC    | 端口 0 中断屏蔽            |

| P1IEN     | 0x8D   | IOC    | 端口 1 中断屏蔽            |

| P2IEN     | 0xAC   | IOC    | 端口 2 中断屏蔽            |

| P0INP     | 0x8F   | IOC    | 端口 0 输入模式            |

| PERCFG    | 0xF1   | IOC    | 外设 I/O 控制            |

| APCFG     | 0xF2   | IOC    | 模拟外设 I/O 配置          |

| P0SEL     | 0xF3   | IOC    | 端口 0 功能选择            |

| P1SEL     | 0xF4   | IOC    | 端口 1 功能选择            |

| P2SEL     | 0xF5   | IOC    | 端口 2 功能选择            |

| P1INP     | 0xF6   | IOC    | 端口 1 输入模式            |

| P2INP     | 0xF7   | IOC    | 端口 2 输入模式            |

| P0DIR     | 0xFD   | IOC    | 端口 0 方向              |

| P1DIR     | 0xFE   | IOC    | 端口 1 方向              |

| P2DIR     | 0xFF   | IOC    | 端口 2 方向              |

| PMUX      | 0xAE   | IOC    | 掉电信号 Mux             |

| MEMCTR    | 0xC7   | MEMORY | 内存系统控制               |

| FMAP      | 0x9F   | MEMORY | 闪存存储器区映射             |

| RFIRQF1   | 0x91   | RF     | RF 中断标志 MSB          |

| RFD       | 0xD9   | RF     | RF 数据                |

| RFST      | 0xE1   | RF     | RF 命令选通              |

| RFIRQF0   | 0xE9   | RF     | RF 中断标志 LSB          |

| RFERRF    | 0xBF   | RF     | RF 错误中断标志            |

| ST0       | 0x95   | ST     | 睡眠定时器 0              |

| ST1       | 0x96   | ST     | 睡眠定时器 1              |

| ST2       | 0x97   | ST     | 睡眠定时器 2              |

| STLOAD    | 0xAD   | ST     | 睡眠定时器负载状态            |

| SLEEPCMD  | 0xBE   | PMC    | 睡眠模式控制命令             |

| SLEEPSTA  | 0x9D   | PMC    | 睡眠模式控制状态             |

| CLKCONCMD | 0xC6   | PMC    | 时钟控制命令               |

| CLKCONSTA | 0x9E   | PMC    | 时钟控制状态               |

| T1CC0L    | 0xDA   | 定时器 1  | 定时器 1 通道 0 捕获/比较值低字节 |

| T1CC0H    | 0xDB   | 定时器 1  | 定时器 1 通道 0 捕获/比较值高字节 |

| T1CC1L    | 0xDC   | 定时器 1  | 定时器 1 通道 1 捕获/比较值低字节 |

| T1CC1H    | 0xDD   | 定时器 1  | 定时器 1 通道 1 捕获/比较值高字节 |

| T1CC2L    | 0xDE   | 定时器 1  | 定时器 1 通道 2 捕获/比较值低字节 |

| T1CC2H    | 0xDF   | 定时器 1  | 定时器 1 通道 2 捕获/比较值高字节 |

| T1CNTL    | 0xE2   | 定时器 1  | 定时器 1 计数器低字节         |

| T1CNTH    | 0xE3   | 定时器 1  | 定时器 1 计数器高字节         |

| T1CTL     | 0xE4   | 定时器 1  | 定时器 1 控制和状态          |

| T1CCTL0   | 0xE5   | 定时器 1  | 定时器 1 通道 0 捕获/比较控制   |

| T1CCTL1   | 0xE6   | 定时器 1  | 定时器 1 通道 1 捕获/比较控制   |

表 2-1 SFR 概览 (续表)

| 寄存器名称    | SFR 地址 | 模块      | 描述                  |

|----------|--------|---------|---------------------|

| T1CCTL2  | 0xE7   | 定时器 1   | 定时器 1 通道 2 捕获/比较控制  |

| T1STAT   | 0xAF   | 定时器 1   | 定时器 1 状态            |

| T2CTRL   | 0x94   | 定时器 2   | 定时器 2 控制            |

| T2EVTCFG | 0x9C   | 定时器 2   | 定时器 2 事件配置          |

| T2IRQF   | 0xA1   | 定时器 2   | 定时器 2 中断标志          |

| T2M0     | 0xA2   | 定时器 2   | 定时器 2 复用寄存器 0       |

| T2M1     | 0xA3   | 定时器 2   | 定时器 2 复用寄存器 1       |

| T2MOVF0  | 0xA4   | 定时器 2   | 定时器 2 复用溢出寄存器 0     |

| T2MOVF1  | 0xA5   | 定时器 2   | 定时器 2 复用溢出寄存器 1     |

| T2MOVF2  | 0xA6   | 定时器 2   | 定时器 2 复用溢出寄存器 2     |

| T2IRQM   | 0xA7   | 定时器 2   | 定时器 2 中断屏蔽          |

| T2MSEL   | 0xC3   | 定时器 2   | 定时器 2 复用选择          |

| T3CNT    | 0xCA   | 定时器 3   | 定时器 3 计数器           |

| T3CTL    | 0xCB   | 定时器 3   | 定时器 3 控制            |

| T3CCTL0  | 0xCC   | 定时器 3   | 定时器 3 通道 0 比较控制     |

| T3CC0    | 0xCD   | 定时器 3   | 定时器 3 通道 0 比较值      |

| T3CCTL1  | 0xCE   | 定时器 3   | 定时器 3 通道 1 比较控制     |

| T3CCTL1  | 0xCF   | 定时器 3   | 定时器 3 通道 1 比较值      |

| T4CNT    | 0xEA   | 定时器 4   | 定时器 4 计数器           |

| T4CTL    | 0xEB   | 定时器 4   | 定时器 4 控制            |

| T4CCTL0  | 0xEC   | 定时器 4   | 定时器 4 通道 0 比较控制     |

| T4CC0    | 0xED   | 定时器 4   | 定时器 4 通道 0 比较值      |

| T4CCTL1  | 0xEE   | 定时器 4   | 定时器 4 通道 1 比较控制     |

| T4CC1    | 0xEF   | 定时器 4   | 定时器 4 通道 1 比较值      |

| TIMIF    | 0xD8   | TMINT   | 定时器 1/3/4 联合中断屏蔽/标志 |

| U0CSR    | 0x86   | USART 0 | USART 0 控制和状态       |

| U0DBUF   | 0xC1   | USART 0 | USART 0 接收/发送数据缓存   |

| U0BAUD   | 0xC2   | USART 0 | USART 0 波特率控制       |

| U0UCR    | 0xC4   | USART 0 | USART 0 UART 控制     |

| U0GCR    | 0xC5   | USART 0 | USART 0 通用控制        |

| U1CSR    | 0xF8   | USART 1 | USART 1 控制和状态       |

| U1DBUF   | 0xF9   | USART 1 | USART 1 接收/发送数据缓存   |

| U1BAUD   | 0xFA   | USART 1 | USART 1 波特率控制       |

| U1UCR    | 0xFB   | USART 1 | USART 1 UART 控制     |

| U1GCR    | 0xFC   | USART 1 | USART 1 通用控制        |

| WDCTL    | 0xC9   | WDT     | 看门狗定时器控制            |

**XREG 寄存器:** XREG 寄存器是 XDATA 存储空间中的另外的寄存器。这些寄存器主要用于无线电配置和控制。每个寄存器的完整描述在 3.6 节。表 2-2 给出了寄存器地址空间的概述。

表 2-2 XREG 寄存器概览

| XDATA 地址      | 寄存器名称     | 描述                                        |

|---------------|-----------|-------------------------------------------|

| 0x6000–0x61FF | —         | 无线电寄存器                                    |

| 0x6200–0x622B | —         | USB 寄存器                                   |

| 0x6249        | CHVER     | 芯片版本                                      |

| 0x624A        | CHIPID    | 芯片识别标志                                    |

| 0x6260        | DBGDATA   | 调试接口写数据                                   |

| 0x6270        | FCTL      | 闪存控制                                      |

| 0x6271        | FADDRL    | 闪存地址低字节                                   |

| 0x6272        | FADDRH    | 闪存地址高字节                                   |

| 0x6273        | FWDATA    | 闪存写数据                                     |

| 0x6276        | CHIPINFO0 | 芯片信息字节 0                                  |

| 0x6277        | CHIPINFO1 | 芯片信息字节 1                                  |

| 0x6290        | CLD       | 时钟丢失探测                                    |

| 0x62A0        | T1CCTL0   | 定时器 1 通道 0 捕获/比较控制 (SFR 寄存器另外的 XREG 映射)   |

| 0x62A1        | T1CCTL1   | 定时器 1 通道 1 捕获/比较控制 (SFR 寄存器另外的 XREG 映射)   |

| 0x62A2        | T1CCTL2   | 定时器 1 通道 2 捕获/比较控制 (SFR 寄存器另外的 XREG 映射)   |

| 0x62A3        | T1CCTL3   | 定时器 1 通道 3 捕获/比较控制                        |

| 0x62A4        | T1CCTL4   | 定时器 1 通道 4 捕获/比较控制                        |

| 0x62A6        | T1CC0L    | 定时器 1 通道 0 捕获/比较值低字节 (SFR 寄存器另外的 XREG 映射) |

| 0x62A7        | T1CC0H    | 定时器 1 通道 0 捕获/比较值高字节 (SFR 寄存器另外的 XREG 映射) |

| 0x62A8        | T1CC1L    | 定时器 1 通道 1 捕获/比较值低字节 (SFR 寄存器另外的 XREG 映射) |

| 0x62A9        | T1CC1H    | 定时器 1 通道 1 捕获/比较值高字节 (SFR 寄存器另外的 XREG 映射) |

| 0x62AA        | T1CC2L    | 定时器 1 通道 2 捕获/比较值低字节 (SFR 寄存器另外的 XREG 映射) |

| 0x62AB        | T1CC2H    | 定时器 1 通道 2 捕获/比较值高字节 (SFR 寄存器另外的 XREG 映射) |

| 0x62AC        | T1CC3L    | 定时器 1 通道 3 捕获/比较值低字节                      |

| 0x62AD        | T1CC3H    | 定时器 1 通道 3 捕获/比较值高字节                      |

| 0x62AE        | T1CC4L    | 定时器 1 通道 4 捕获/比较值低字节                      |

| 0x62AF        | T1CC4H    | 定时器 1 通道 4 捕获/比较值高字节                      |

| 0x62B0        | STCC      | 睡眠定时器捕获控制                                 |

| 0x62B1        | STCS      | 睡眠定时器捕获状态                                 |

| 0x62B2        | STCV0     | 睡眠定时器捕获值字节 0                              |

| 0x62B3        | STCV1     | 睡眠定时器捕获值字节 1                              |

| 0x62B4        | STCV2     | 睡眠定时器捕获值字节 2                              |

## 2.2.4 XDATA 存储空间

**MPAGE** 寄存器在指令 MOVX A,@Ri 和 MOVX @Ri, A 期间使用。MPAGE 给出最高 8 位地址，而寄存器 Ri 给出最低 8 位地址。

在一些 8051 的实现中，这种类型的 XDATA 访问是使用 P2 给出最高位地址执行的。因此现有的软件必须适应使用 MPAGE 而不是 P2。

**MPAGE (0x93) - 内存页面选择**

| 位   | 名称         | 复位   | R/W | 描述                 |

|-----|------------|------|-----|--------------------|

| 7:0 | MPAGE[7:0] | 0x00 | R/W | 内存页面，MOVX 指令中地址的高位 |

## 2.2.5 存储器仲裁

存储器仲裁处理 CPU 和 DMA 访问所有物理存储器（除了 CPU 内部寄存器）。当 CPU 和 DMA 之间发生访问冲突时，存储器仲裁停止总线主机之一，这样冲突就被解决。

控制寄存器 MEMCTR 和 FMAP 用于控制存储器子系统的各个方面。MEMCTR 和 FMAP 寄存器描述如下。

MEMCTR.XMAP 必须设置以使得程序从 RAM 执行。

闪存区映射寄存器 FMAP 控制物理 32-KB 代码区映射到 CODE 存储空间的程序地址区域 0x8000–0xFFFF。

**MEMCTR (0xC7) - 存储器仲裁控制**

| 位   | 名称         | 复位   | R/W | 描述                                                                                                                                                                                                  |

|-----|------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:4 | —          | 0000 | R0  | 保留                                                                                                                                                                                                  |

| 3   | XMAP       | 0    | R/W | XDATA 映射到代码。当设置了这一位，SRAM XDATA 区域从 0x0000 到 (SRAM_SIZE-1) 映射到 CODE 区域的 0x8000 到 (0x8000 + SRAM_SIZE - 1)。这使得程序代码从 RAM 执行。<br>0: SRAM 映射到 CODE 功能禁用<br>1: SRAM 映射到 CODE 功能使能                         |

| 2:0 | XBANK[2:0] | 000  | R/W | XDATA 区选择。控制物理闪存存储器的哪个代码区映射到 XDATA 区域 (0x8000–0xFFFF)。当设置为 0，映射到根部区。<br>有效设置取决于设备的闪存大小。写一个无效设置被忽略，即不会更新 XBANK[2:0]。<br>32-KB 版本：只能是 0 (即总是映射到根部区)<br>64-KB 版本：0-1<br>128-KB 版本：0-3<br>256-KB 版本：0-7 |

**FMAP (0x9F) - 闪存区映射**

| 位   | 名称       | 复位     | R/W | 描述                                                                                                                                                                                                                 |

|-----|----------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:3 | —        | 0000 0 | R0  | 未使用                                                                                                                                                                                                                |

| 2:0 | MAP[2:0] | 001    | R/W | 闪存区映射。控制物理闪存存储器的哪个代码区映射到 XDATA 区域 (0x8000–0xFFFF)。当设置为 0，映射到根部区。有效设置取决于设备的闪存大小。写一个无效设置被忽略，即不会更新 MAP[2:0]。<br>32-KB 版本：不能写值。上面的区域只能用于从 SRAM 运行程度代码。见 MEMCTR.XMAP。<br>64-KB 版本：0-1<br>128-KB 版本：0-3<br>256-KB 版本：0-7 |

## 2.3 CPU 寄存器

本节描述了 CPU 的内部寄存器。

### 2.3.1 数据指针

有两个数据指针 DPTR0 和 DPTR1 来加快数据块到存储器/从存储器取出的移动。数据指针一般用于访问 CODE 或 XDATA 空间。例如：

MOVC A,@A+DPTR

MOV A,@DPTR

数据指针选择位（数据指针选择寄存器 DPS 中的位 0）选择执行一条使用数据指针的指令（即前面所述的指令之一）期间哪个数据指针是活动的。

数据指针宽度为两字节，包括以下 SFR：

- DPTR0-DPH0:DPL0

- DPTR1-DPH1:DPL1

DPH0 (0x83) - 数据指针-0 高字节

| 位   | 名称        | 复位   | R/W | 描述          |

|-----|-----------|------|-----|-------------|

| 7:0 | DPH0[7:0] | 0x00 | R/W | 数据指针-0, 高字节 |

DPL0 (0x82) - 数据指针-0 低字节

| 位   | 名称        | 复位   | R/W | 描述          |

|-----|-----------|------|-----|-------------|

| 7:0 | DPL0[7:0] | 0x00 | R/W | 数据指针-0, 低字节 |

DPH1 (0x85) - 数据指针-1 高字节

| 位   | 名称        | 复位   | R/W | 描述          |

|-----|-----------|------|-----|-------------|

| 7:0 | DPH1[7:0] | 0x00 | R/W | 数据指针-1, 高字节 |

DPL1 (0x84) - 数据指针-1 低字节

| 位   | 名称        | 复位   | R/W | 描述          |

|-----|-----------|------|-----|-------------|

| 7:0 | DPL1[7:0] | 0x00 | R/W | 数据指针-1, 低字节 |

DPS (0x92) - 数据指针选择

| 位   | 名称  | 复位       | R/W | 描述                                        |

|-----|-----|----------|-----|-------------------------------------------|

| 7:1 | -   | 0000 000 | R0  | 未使用                                       |

| 0   | DPS | 0        | R/W | 数据指针选择。选择活动的数据指针。<br>0: DPTR0<br>1: DPTR1 |

### 2.3.2 寄存器 R0-R7

有 4 组寄存器（不要与 CODE 存储空间区混淆，它只适用于闪存存储器组织），每组包括 8 个寄存器。这四组寄存器分别映射到 DATA 存储空间地址的 0x00-0x07, 0x08-0x0F, 0x10-0x17, 0x18-0x1F。每个寄存器组包括 8 个 8 位寄存器 R0-R7。寄存器组可以通过程序状态字 PSW.RS[1:0] 来选择使用。寄存器组 0 使用内部触发器来存储值（SRAM 被绕过/未使用），而组 1-3 使用 SRAM 来存储。这样做是为了节省电力。一般地，通过使用寄存器组 0，而不是寄存器组 1—3，电流消耗大约可以下降 200uA。

### 2.3.3 程序状态字

程序状态字 (PSW) 接位显示 CPU 的当前状态，可以理解为一个可位寻址的特殊功能寄存器。PSW 如下所示，包括进位标志、BCD 操作的辅助进位标志、寄存器选择位、溢出标志和奇偶标志等。PSW 的其余二位没有规定，可用于用户自定义的状态标志。

**PSW (0xD0) - 程序状态字**

| 位   | 名称      | 复位 | R/W | 描述                                                                                                                                                |

|-----|---------|----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   | CY      | 0  | R/W | 进位标志。当最后的算术运算结果导致进位（加法期间）或者借用（减法期间）时，设置为1，否则通过所有算术运算清零。                                                                                           |

| 6   | AC      | 0  | R/W | BCD运算的辅助进位标志。当最后的算术运算导致一个进位到（加法期间）或者借用（减法期间）时，设置为1，否则通过算术运算清零。                                                                                    |

| 5   | F0      | 0  | R/W | 用户自定义，位寻址                                                                                                                                         |

| 4:3 | RS[1:0] | 00 | R/W | 寄存器组选择位。在DATA空间，一组R7-R0寄存器使用了选择四个可能的寄存器组。<br>00: 寄存器组0, 0x00 - 0x07<br>01: 寄存器组1, 0x08 - 0x0F<br>10: 寄存器组2, 0x10 - 0x17<br>11: 寄存器组3, 0x18 - 0x1F |

| 2   | OV      | 0  | R/W | 溢出标志，通过算术运算设置。当最后的算术运算导致一个进位（加法），借位（减法），或者溢出（乘或除）时，设置为1，否则，该位通过所有运算清0。                                                                            |

| 1   | F1      | 0  | R/W | 用户自定义，位寻址                                                                                                                                         |

| 0   | P       | 0  | R/W | 奇偶校验标志，假如它包含一个奇数1的数，相同的累加器通过硬件设置为1。否则清0。                                                                                                          |

**2.3.4 累加器**

ACC 是一个累加器，它是大多数算法指令、数据传输和其它指令的源和目标地址。指令中累加器的助记符（涉及累加器的指令中）是 A 而不是 ACC。

**ACC (0xE0) - 累加器**

| 位   | 名称       | 复位   | R/W | 描述  |

|-----|----------|------|-----|-----|

| 7:0 | ACC[7:0] | 0x00 | R/W | 累加器 |

**2.3.5 B 寄存器**

B 寄存器在执行乘法和除法指令期间作为第二个 8 位参数运用，若不进行乘/除法运算，B 寄存器也可当成一般寄存器使用，来存储临时数据。

**B (0xF0) - B 寄存器**

| 位   | 名称     | 复位   | R/W | 描述                |

|-----|--------|------|-----|-------------------|

| 7:0 | B[7:0] | 0x00 | R/W | B寄存器，用于 MUL/DIV指令 |

**2.3.6 堆栈指针**

堆栈驻留在 DATA 存储空间并向上增长。PUSH 指令执行时，首先把堆栈指针（SP）加 1，然后把字节复制到堆栈中。SP 初始地址为 0x07，复位后就增加 1，变为 0x08，这是第二个寄存器组第一个寄存器（R0）的地址。因此为了使用多个寄存器组，SP 可以初始化到一块没有用于数据存储的位置。

**SP (0x81) - 堆栈指针**

| 位   | 名称      | 复位   | R/W | 描述   |

|-----|---------|------|-----|------|

| 7:0 | SP[7:0] | 0x07 | R/W | 堆栈指针 |

**2.4 指令集总结**

8051 指令集总结在表 2-3 中。所有助记符的版权归© Intel 公司，1980 年所有。

以下约定在指令集总结中使用：

- Rn - 当前选择寄存器组中的寄存器 R7-R0。

- direct - 8 位内部数据位置的地址。这可以是 DATA 区域 (0x00 - 0x7F) 或 SFR 区域 (0x80 - 0xFF)。

- @Ri-8 位内部的位置，DATA 区域 (0x00 - 0xFF)，通过寄存器 R1 或 R0 间接寻址。

- #data - 指令所含的 8 位常量。

- #data16 - 指令所含的 16 位常量。

- addr16 - 16 位目标地址。用于 LCALL 和 LJMP。64-KB CODE 存储空间中任何地方都可以作为一行使用。

- addr11 - 11 位目标地址。用于 ACALL 和 AJMP。这一行将在程序存储器的同一个 2KB 的页面，作为下面指令的第一个字节。

- rel- (2 的补数) 8 位偏移字节。用于 SJMP 和所有另外的跳转。范围是-128 到 127 字节，和下面指令的第一个字节有关。

- bit - DATA 区域或 SFR 区域的直接寻址位。

影响 CPU 标志设置的指令列在表 2-4 中，这些标志位于 PSW 中。注意对 PSW 寄存器或 PSW 位的操作也将影响标志的设置。还要注意许多指令的周期数假定是单周期访问存储器被访问的元素，即最好的情况。这并非总是如此。例如从闪存读可能需要 1-3 个周期。

表 2-3 指令集综述

| 助记符           | 描述                | 十六进制操作码 | 字节数 | 周期 |

|---------------|-------------------|---------|-----|----|

| 算术运算          |                   |         |     |    |

| ADD A,Rn      | 添加寄存器到累加器         | 28-2F   | 1   | 1  |

| ADD A,direct  | 添加直接字节到累加器        | 25      | 2   | 2  |

| ADD A,@Ri     | 添加直接RAM到累加器       | 26-27   | 1   | 2  |

| ADD A,#data   | 添加直接数据到累加器        | 24      | 2   | 2  |

| ADDC A,Rn     | 添加寄存器到带有进位标志的累加器  | 38-3F   | 1   | 1  |

| ADDC A,direct | 添加直接字节到带有进位标志的 A  | 35      | 2   | 2  |

| ADDC A,@Ri    | 添加直接RAM到带有进位标志的 A | 36-37   | 1   | 2  |

| ADDC A,#data  | 添加直接数据到带有进位标志的 A  | 34      | 2   | 2  |

| SUBB A,Rn     | 从带有借位的 A 减去寄存器    | 98-9F   | 1   | 1  |

| SUBB A,direct | 从带有借位的 A 减法直接字节   | 95      | 2   | 2  |

| SUBB A,@Ri    | 从带有借位的 A 减去间接RAM  | 96-97   | 1   | 2  |

| SUBB A,#data  | 从带有借位的 A 减去直接数据   | 94      | 2   | 2  |

| INC A         | 递增累加器             | 04      | 1   | 1  |

| INC Rn        | 递增寄存器             | 08-0F   | 1   | 2  |

| INC direct    | 递增直接字节            | 05      | 2   | 3  |

| INC @Ri       | 递增直接RAM           | 06-07   | 1   | 3  |

| INC DPTR      | 递增数据指针            | A3      | 1   | 1  |

| DEC A         | 递减累加器             | 14      | 1   | 1  |

| DEC Rn        | 递减寄存器             | 18-1F   | 1   | 2  |

| DEC direct    | 递减直接字节            | 15      | 2   | 3  |

| DEC @Ri       | 递减直接RAM           | 16-17   | 1   | 3  |

| MUL AB        | A 和 B 相乘          | A4      | 1   | 5  |

| DIV AB        | A 除以 B            | 84      | 1   | 5  |

| DA A          | 十进制校准累加器          | D4      | 1   | 1  |

| 逻辑运算          |                   |         |     |    |

| ANL A,Rn      | AND 寄存器到累加器       | 58-5F   | 1   | 1  |

| ANL A,direct  | AND 直接字节到累加器      | 55      | 2   | 2  |

| ANL A,@Ri     | AND 间接RAM到累加器     | 56-57   | 1   | 2  |

表 2-3 指令集综述 (续表)

| 助记符                 | 描述                  | 十六进制操作码 | 字节数 | 周期 |

|---------------------|---------------------|---------|-----|----|

| ANL A,#data         | AND直接数据到累加器         | 54      | 2   | 2  |

| ANL direct,A        | AND累加器到直接字节         | 52      | 2   | 3  |

| ANL direct,#data    | AND直接数据到直接字节        | 53      | 3   | 4  |

| ORL A,Rn            | OR寄存器到累加器           | 48-4F   | 1   | 1  |

| ORL A,direct        | OR直接字节到累加器          | 45      | 2   | 2  |

| ORL A,@Ri           | OR间接RAM到累加器         | 46-47   | 1   | 2  |

| ORL A,#data         | OR直接数据到累加器          | 44      | 2   | 2  |

| ORL direct,A        | OR累加器到直接字节          | 42      | 2   | 3  |

| ORL direct,#data    | OR直接数据到直接字节         | 43      | 3   | 4  |

| XRL A,Rn            | 专用OR寄存器到累加器         | 68-6F   | 1   | 1  |

| XRL A,direct        | 专用OR直接字节到累加器        | 65      | 2   | 2  |

| XRL A,@Ri           | 专用OR间接RAM到累加器       | 66-67   | 1   | 2  |

| XRL A,#data         | 专用OR直接数据到累加器        | 64      | 2   | 2  |

| XRL direct,A        | 专用OR累加器到直接字节        | 62      | 2   | 3  |

| XRL direct,#data    | 专用OR直接数据到直接字节       | 63      | 3   | 4  |

| CLR A               | 清除累加器               | E4      | 1   | 1  |

| CPL A               | 补充累加器               | F4      | 1   | 1  |

| RL A                | 累加器左循环              | 23      | 1   | 1  |

| RLC A               | 累加器通过进位左循环          | 33      | 1   | 1  |

| RR A                | 累加器右循环              | 03      | 1   | 1  |

| RRC A               | 累加器通过进位右循环          | 13      | 1   | 1  |

| SWAP A              | 在累加器里交换半字节          | C4      | 1   | 1  |

| 数据传输                |                     |         |     |    |

| MOV A,Rn            | 移动寄存器到累加器           | E8-EF   | 1   | 1  |

| MOV A,direct        | 移动直接字节到累加器          | E5      | 2   | 2  |

| MOV A,@Ri           | 移动间接RAM到累加器         | E6-E7   | 1   | 2  |

| MOV A,#data         | 移动直接数据到累加器          | 74      | 2   | 2  |

| MOV Rn,A            | 移动累加器到寄存器           | F8-FF   | 1   | 2  |

| MOV Rn,direct       | 移动直接字节到寄存器          | A8-AF   | 2   | 4  |

| MOV Rn,#data        | 移动直接数据到寄存器          | 78-7F   | 2   | 2  |

| MOV direct,A        | 移动累加器到直接字节          | F5      | 2   | 3  |

| MOV direct,Rn       | 移动寄存器到直接字节          | 88-8F   | 2   | 3  |

| MOV direct1,direct2 | 移动直接字节到直接字节         | 85      | 3   | 4  |

| MOV direct,@Ri      | 移动间接RAM到直接字节        | 86-87   | 2   | 4  |

| MOV direct,#data    | 移动直接数据到直接字节         | 75      | 3   | 3  |

| MOV @Ri,A           | 移动累加器到直接RAM         | F6-F7   | 1   | 3  |

| MOV @Ri,direct      | 移动直接字节到间接RAM        | A6-A7   | 2   | 5  |

| MOV @Ri,#data       | 移动直接数据到间接RAM        | 76-77   | 2   | 3  |

| MOV DPTR,#data16    | 加载带有16位常数的数据指针      | 90      | 3   | 3  |

| MOVC A,@A+DPTR      | 移动关于DPTR的代码字节到累加器   | 93      | 1   | 3  |

| MOVC A,@A+PC        | 移动关于PC到的代码字节到累加器    | 83      | 1   | 3  |

| MOVX A,@Ri          | 移动外部的RAM (8位地址) 到A  | E2-E3   | 1   | 3  |

| MOVX A,@DPTR        | 移动外部的RAM (16位地址) 到A | E0      | 1   | 3  |

| MOVX @Ri,A          | 移动A到外部RAM (8位地址)    | F2-F3   | 1   | 4  |

| MOVX @DPTR,A        | 移动A到外部RAM (16位地址)   | F0      | 1   | 4  |

| PUSH direct         | 压直接字节到栈             | C0      | 2   | 4  |

**表 2-3 指令集综述 (续表)**

| 助记符                | 描述                   | 十六进制操 | 字节数 | 周期 |

|--------------------|----------------------|-------|-----|----|

| POP direct         | 从栈中弹出直接字节            | D0    | 2   | 3  |

| XCH A,Rn           | 交换寄存器和累加器            | C8-CF | 1   | 2  |

| XCH A,direct       | 交换直接字节和累加器           | C5    | 2   | 3  |

| XCH A,@Ri          | 交换直接RAM和累加器          | C6-C7 | 1   | 3  |

| XCHD A,@Ri         | 交换间接低位半字节RAM和A       | D6-D7 | 1   | 3  |

| <b>程序分支</b>        |                      |       |     |    |

| ACALL addr11       | 绝对子程序调用              | xxx11 | 2   | 6  |

| LCALL addr16       | 长期子程序调用              | 12    | 3   | 6  |

| RET                | 从子程序返回               | 22    | 1   | 4  |

| RETI               | 从中断返回                | 32    | 1   | 4  |

| AJMP addr11        | 绝对跳转                 | xxx01 | 2   | 3  |

| LJMP addr16        | 长期跳转                 | 02    | 3   | 4  |

| SJMP rel           | 短期跳转 (相对地址)          | 80    | 2   | 3  |

| JMP @A+DPTR        | 相对 DPTR的间接跳转         | 73    | 1   | 2  |

| JZ rel             | 如果累加器是0, 跳转          | 60    | 2   | 3  |

| JNZ rel            | 如果累加器不是0, 跳转         | 70    | 2   | 3  |

| JC rel             | 如果进位标志设置, 跳转         | 40    | 2   | 3  |

| JNC                | 如果进位标志未设置, 跳转        | 50    | 2   | 3  |

| JB bit,rel         | 如果直接位设置, 跳转          | 20    | 3   | 4  |

| JNB bit,rel        | 如果直接位未设置, 跳转         | 30    | 3   | 4  |

| JBC bit,direct rel | 如果直接位设置并且清除位, 跳转     | 10    | 3   | 4  |

| CJNE A,direct rel  | 比较直接位和A, 如果不等, 跳转    | B5    | 3   | 4  |

| CJNE A,#data rel   | 直接字节和A相比较, 如果不等, 跳转  | B4    | 3   | 4  |

| CJNE Rn,#data rel  | 直接和Reg.相比较. 如果不等, 跳转 | B8-BF | 3   | 4  |

| CJNE @Ri,#data rel | 直接和间接相比较, 如果不等, 跳转   | B6-B7 | 3   | 4  |

| DJNZ Rn,rel        | 递减寄存器, 如果不为零, 跳转     | D8-DF | 2   | 3  |

| DJNZ direct,rel    | 递减直接字节, 如果不为零, 跳转    | D5    | 3   | 4  |

| NOP                | 无操作                  | 00    | 1   | 1  |

| <b>布尔变量操作</b>      |                      |       |     |    |

| CLR C              | 清空进位标志               | C3    | 1   | 1  |

| CLR bit            | 清空直接位                | C2    | 2   | 3  |

| SETB C             | 设置进位标志               | D3    | 1   | 1  |

| SETB bit           | 设置直接位                | D2    | 2   | 3  |

| CPL C              | 补充进位标志               | B3    | 1   | 1  |

| CPL bit            | 补充直接位                | B2    | 2   | 3  |

| ANL C,bit          | AND直接位到进位标志          | 82    | 2   | 2  |

| ANL C,/bit         | 直接位到进位的AND补充         | B0    | 2   | 2  |

| ORL C,bit          | OR直接位到进位标志           | 72    | 2   | 2  |

| ORL C,/bit         | 直接位到进位的OR补充          | A0    | 2   | 2  |

| MOV C,bit          | 移动直接位到进位标志           | A2    | 2   | 2  |

| MOV bit,C          | 移动进位标志到直接位           | 92    | 2   | 3  |

表 2-4 影响标志设置的指令<sup>(1)</sup>

| 指令         | CY | OV | AC |

|------------|----|----|----|

| ADD        | x  | x  | x  |

| ADDC       | x  | x  | x  |

| SUBB       | x  | x  | x  |

| MUL        | 0  | x  | -  |

| DIV        | 0  | x  | -  |

| DA         | x  | -  | -  |

| RRC        | x  | -  | -  |

| RLC        | x  | -  | -  |

| SETB C     | 1  | -  | -  |

| CLR C      | x  | -  | -  |

| CPL C      | x  | -  | -  |

| ANL C,bit  | x  | -  | -  |

| ANL C,/bit | x  | -  | -  |

| ORL C,bit  | x  | -  | -  |

| ORL C,/bit | x  | -  | -  |

| MOV C,bit  | x  | -  | -  |

| CJNE       | x  | -  | -  |

(1) 0=设置为 0, 1=设置为 1, x=设置为 0/1, --=不影响

## 2.5 中断

CPU 有 18 个中断源。每个中断源都有它自己的位于一系列 SFR 寄存器中的中断请求标志。相应标志位请求的每个中断可以分别使能或禁用。中断源的定义和中断向量如表 2-5 所示。

中断分别组合为不同的、可以选择的优先级别。

中断使能寄存器在 2.5.1 节中描述。中断优先级设置在 2.5.3 节中描述。

### 2.5.1 中断屏蔽

每个中断请求可以通过设置中断使能 SFR 寄存器的中断使能位 IEN0, IEN1 或者 IEN2 使能或禁止。CPU 的中断使能 SFR 如下面描述并总结在表 2-5 中。

注意某些外部设备有若干事件, 可以产生与外设相关的中断请求。这些中断请求可以作用在端口 0、端口 1、端口 2、定时器 1、定时器 2、定时器 3、定时器 4 和无线电上。对于每个内部中断源对应的 SFR 寄存器, 这些外部设备都有中断屏蔽位。

为了使能任一中断功能, 应当采取下列步骤:

- 1、清除中断标志。

- 2、如果有, 则设置 SFR 寄存器中对应的各中断使能位为 1。

- 3、设置寄存器 IEN0、IEN1 和 IEN2 中对应的中断使能位为 1。

- 4、设置 IEN0 中的 EA 位为 1 使能全局中断。

- 5、在该中断对应的向量地址上, 运行该中断的服务程序。关于地址见表 2-5。

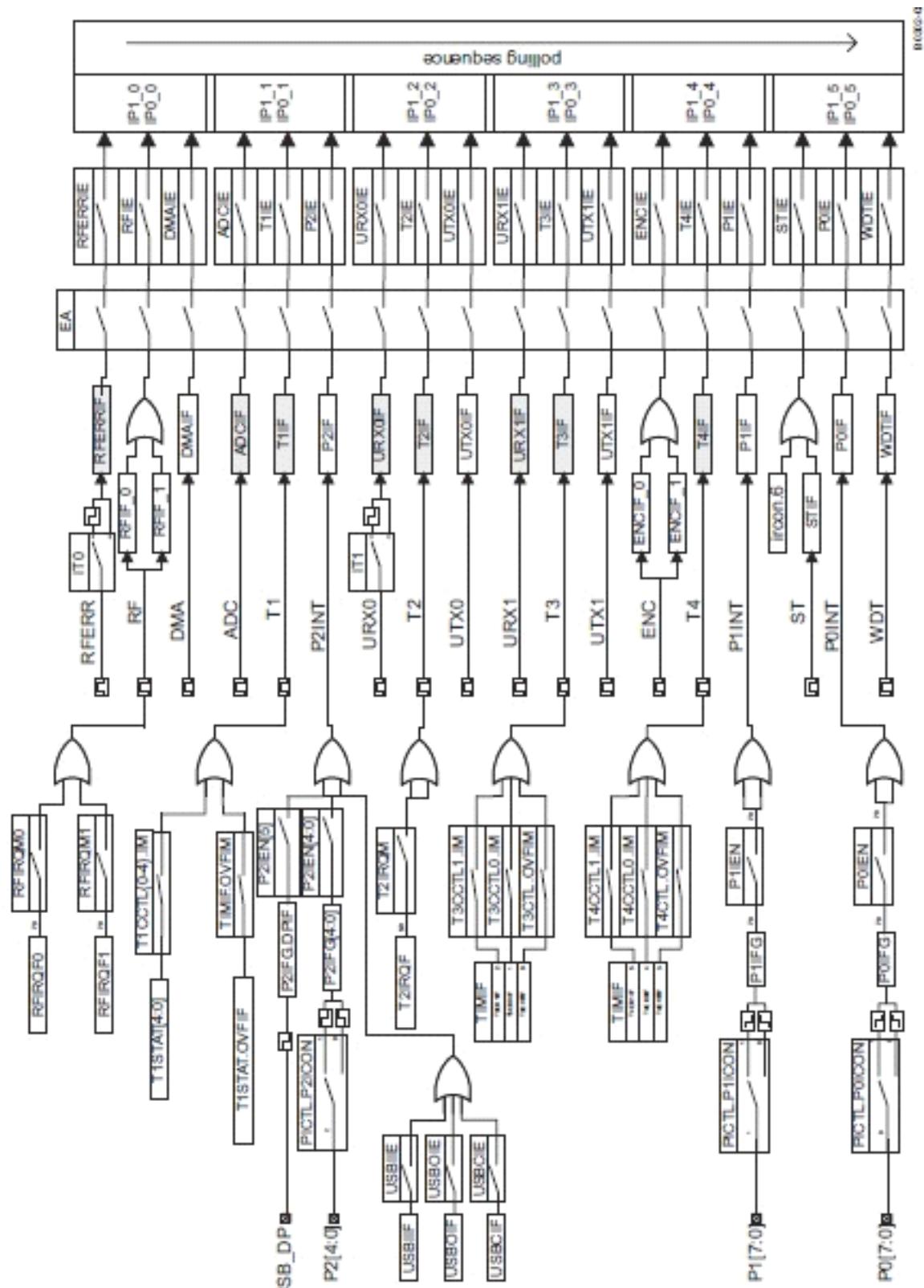

图 2-4 给出了所有中断源以及相关控制和状态寄存器的完整概述。阴影框是调用中断服务例程时由硬件自动清除的中断。▲ 表示一次执行, 由于电平源或由于边沿形成。对于错过这个的中断作为电平触发对待 (适

用于端口 P0、P1 和 P2）。转换框用默认状态显示，↑或↓表示上升或下降沿探测，即在什么时候中断产生。一般来说，如果可用的话，对于不是自动清除的标志，对于脉冲或边沿形成的中断源，应在清除源标志位之前清除 CPU 中断标志寄存器。对于电平源，必须在清除 CPU 标志之前清除源。

表 2-5 中断概览

| 中断<br>号码 | 描述                     | 中断名称  | 中断向量 | 中断屏蔽, CPU    | 中断标志, CPU                     |

|----------|------------------------|-------|------|--------------|-------------------------------|

| 0        | RF TX FIFO下溢或RX FIFO溢出 | RFERR | 03h  | IEN0.RFERRIE | TCON.RFERRIF <sup>(1)</sup>   |

| 1        | ADC转换结束                | ADC   | 0Bh  | IEN0.ADCIE   | TCON.ADCIF <sup>(1)</sup>     |

| 2        | USART0 RX完成            | URX0  | 13h  | IEN0.URX0IE  | TCON.URX0IF <sup>(1)</sup>    |

| 3        | USART1 RX完成            | URX1  | 1Bh  | IEN0.URX1IE  | TCON.URX1IF <sup>(1)</sup>    |

| 4        | AES加密/解密完成             | ENC   | 23h  | IEN0.ENCIE   | S0CON.ENCIF                   |

| 5        | 睡眠计时器比较                | ST    | 2Bh  | IEN0.STIE    | IRCON.STIF                    |

| 6        | 端口2输入/USB              | P2INT | 33h  | IEN2.P2IE    | IRCON2.P2IF <sup>(2)</sup>    |

| 7        | USART0 TX完成            | UTX0  | 3Bh  | IEN2.UTX0IE  | IRCON2.UTX0IF                 |

| 8        | DMA传送完成                | DMA   | 43h  | IEN1.DMAIE   | IRCON.DMAIF                   |

| 9        | 定时器1(16位)捕获/比较/溢出      | T1    | 4Bh  | IEN1.T1IE    | IRCON.T1IF <sup>(1) (2)</sup> |

| 10       | 定时器2                   | T2    | 53h  | IEN1.T2IE    | IRCON.T2IF <sup>(1) (2)</sup> |

| 11       | 定时器3(8位)捕获/比较/溢出       | T3    | 5Bh  | IEN1.T3IE    | IRCON.T3IF <sup>(1) (2)</sup> |

| 12       | 定时器4(8位)捕获/比较/溢出       | T4    | 63h  | IEN1.T4IE    | IRCON.T4IF <sup>(1) (2)</sup> |

| 13       | 端口0输入                  | P0INT | 6Bh  | IEN1.P0IE    | IRCON.P0IF <sup>(2)</sup>     |

| 14       | USART 1 TX完成           | UTX1  | 73h  | IEN2.UTX1IE  | IRCON2.UTX1IF                 |

| 15       | 端口1输入                  | P1INT | 7Bh  | IEN2.P1IE    | IRCON2.P1IF <sup>(2)</sup>    |

| 16       | RF通用中断                 | RF    | 83h  | IEN2.RFIE    | S1CON.RFIF <sup>(2)</sup>     |

| 17       | 看门狗计时溢出                | WDT   | 8Bh  | IEN2.WDTIE   | IRCON2.WDTIF                  |

(1) 当调用中断服务例程时清除硬件。

(2) 另外的 IRQ 掩码和 IRQ 标志位存在。

图 2-4 中断概览

**IENO (0xA8) – 中断使能 0**

| 位 | 名称     | 复位 | R/W | 描述                                                 |

|---|--------|----|-----|----------------------------------------------------|

| 7 | EA     | 0  | R/W | 禁用所有中断。<br>0: 无中断被确认<br>1: 通过设置对应的使能位将每个中断源分别使能和禁止 |

| 6 | -      | 0  | R0  | 不使用, 读出来是 0                                        |

| 5 | STIE   | 0  | R/W | 睡眠定时器中断使能<br>0: 中断禁止<br>1: 中断使能                    |

| 4 | ENCIE  | 0  | R/W | AES 加密/解密中断使能<br>0: 中断禁止<br>1: 中断使能                |

| 3 | URX1IE | 0  | R/W | USART 1 RX 中断使能<br>0: 中断禁止<br>1: 中断使能              |

| 2 | URX0IE | 0  | R/W | USART0 RX 中断使能<br>0: 中断禁止<br>1: 中断使能               |

| 1 | ADCIE  | 0  | R/W | ADC 中断使能<br>0: 中断禁止<br>1: 中断使能                     |

| 0 | RFERIE | 0  | R/W | RF TX/RX FIFO 中断使能<br>0: 中断禁止<br>1: 中断使能           |

**IEN1 (0xB8) – 中断使能 1**

| 位   | 名称    | 复位 | R/W | 描述                              |

|-----|-------|----|-----|---------------------------------|

| 7:6 | -     | 00 | R0  | 不使用, 读出来为0                      |

| 5   | P0IE  | 0  | R/W | 端口0中断使能<br>0: 中断禁止<br>1: 中断使能   |

| 4   | T4IE  | 0  | R/W | 定时器4中断使能<br>0: 中断禁止<br>1: 中断使能  |

| 3   | T3IE  | 0  | R/W | 定时器3中断使能<br>0: 中断禁止<br>1: 中断使能  |

| 2   | T2IE  | 0  | R/W | 定时器2中断使能<br>0: 中断禁止<br>1: 中断使能  |

| 1   | T1IE  | 0  | R/W | 定时器1中断使能<br>0: 中断禁止<br>1: 中断使能  |

| 0   | DMAIE | 0  | R/W | DMA传输中断使能<br>0: 中断禁止<br>1: 中断使能 |

IEN2 (0x9A) - 中断使能 2

| 位   | 名称     | 复位 | R/W | 描述                                   |

|-----|--------|----|-----|--------------------------------------|

| 7:6 | -      | 00 | R0  | 没有使用, 读出来是0                          |

| 5   | WDTIE  | 0  | R/W | 看门狗定时器中断使能<br>0: 中断禁止<br>1: 中断使能     |

| 4   | P1IE   | 0  | R/W | 端口1中断使能<br>0: 中断禁止<br>1: 中断使能        |

| 3   | UTX1IE | 0  | R/W | USART 1 TX中断使能<br>0: 中断禁止<br>1: 中断使能 |

| 2   | UTX0IE | 0  | R/W | USART 0 TX中断使能<br>0: 中断禁止<br>1: 中断使能 |

| 1   | P2IE   | 0  | R/W | 端口2中断使能<br>0: 中断禁止<br>1: 中断使能        |

| 0   | RFIE   | 0  | R/W | RF一般中断使能<br>0: 中断禁止<br>1: 中断使能       |

### 2.5.2 中断处理

当中断发生时, CPU 就指向表 2-5 所描述的中断向量地址。一旦中断服务开始, 就只能被更高优先级的中断打断。中断服务程序由中断指令 RETI (从中断指令返回) 终止, 当 RETI 执行时, CPU 将返回到中断发生时的下一条指令。

当中断发生时, 不管该中断使能或禁止, CPU 都会在中断标志寄存器中设置中断标志位。如果当设置中断标志时中断使能, 那么在下一个指令周期, 由硬件强行产生一个 LCALL 到对应的向量地址, 运行中断服务程序。

中断的响应需要不同的时间, 取决于该中断发生时 CPU 的状态。当 CPU 正在运行的中断服务程序, 其优先级大于或等于新的中断时, 新的中断暂不运行, 直至新的中断的优先级高于正在运行的中断服务程序。在其他情况下, 中断响应的时间取决于当前的指令, 最快响应一个中断的时间是 7 个机器指令周期, 其中 1 个机器指令周期用于探测中断, 其余 6 个用来执行 LCALL。

---

**注意:** 如果一个中断被禁用且中断标志被轮询, 8051 汇编指令 JBC 不能用于轮询中断标志, 当设置时要把它清除。如果使用了, 中断标志可能立即重新生效。

---

**TCON (0x88) - 中断标志**

| 位 | 名称      | 复位 | R/W   | 描述                                                                           |

|---|---------|----|-------|------------------------------------------------------------------------------|

| 7 | URX1IF  | 0  | R/WH0 | USART 1 RX中断标志。当USART 1 RX中断发生时设为1且当CPU指向中断向量服务例程时清除。<br>0: 无中断未决<br>1: 中断未决 |

| 6 | -       | 0  | R/W   | 没有使用                                                                         |

| 5 | ADCIF   | 0  | R/WH0 | ADC中断标志。ADC中断发生时设为1且CPU指向中断向量例程时清除。<br>0: 无中断未决<br>1: 中断未决                   |

| 4 | -       | 0  | R/W   | 没有使用                                                                         |

| 3 | URX0IF  | 0  | R/WH0 | USART 0 RX中断标志。当USART0中断发生时设为1且CPU指向中断向量例程时清除。<br>0: 无中断未决<br>1: 中断未决        |

| 2 | IT1     | 1  | R/W   | 保留。必须一直设为1。设置为零将使能低级别中断探测，几乎总是如此（启动中断请求时执行一次）。                               |

| 1 | RFERRIF | 0  | R/WH0 | RF TX/RX FIFO 中断标志。当RFERR中断发生时设为1且CPU指向中断向量例程时清除。<br>0: 无中断未决<br>1: 中断未决     |

| 0 | IT0     | 1  | R/W   | 保留。必须一直设为1。设置为零将使能低级别中断探测，几乎总是如此（启动中断请求时执行一次）。                               |

**S0CON (0x98) - 中断标志 2**

| 位   | 名称      | 复位      | R/W | 描述                                                                                                 |

|-----|---------|---------|-----|----------------------------------------------------------------------------------------------------|

| 7:2 | -       | 0000 00 | R/W | 没有使用                                                                                               |

| 1   | ENCIF_1 | 0       | R/W | AES中断。ENC有两个中断标志, ENCIF_1和ENCIF_0, 设置其中一个标志就会请求中断服务。当AES协处理器请求中断时两个标志都要设置。<br>0: 无中断未决<br>1: 中断未决  |

| 0   | ENCIF_0 | 0       | R/W | AES中断。ENC有两个中断标志, ENCIF_1和 ENCIF_0, 设置其中一个标志就会请求中断服务。当AES协处理器请求中断时两个标志都要设置。<br>0: 无中断未决<br>1: 中断未决 |

**S1CON (0x9B) - 中断标志 3**

| 位   | 名称     | 复位      | R/W | 描述                                                                                          |

|-----|--------|---------|-----|---------------------------------------------------------------------------------------------|

| 7:2 | -      | 0000 00 | R/W | 没有使用                                                                                        |

| 1   | RFIF_1 | 0       | R/W | RF一般中断。RF有两个中断标志, RFIF_1和RFIF_0, 设置其中一个标志就会请求中断服务。当无线电请求中断时两个标志都要设置。<br>0: 无中断未决<br>1: 中断未决 |

| 0   | RFIF_0 | 0       | R/W | RF一般中断。RF有两个中断标志, RFIF_1和RFIF_0。设置其中一个标志就会请求中断服务。当无线电请求中断时两个标志都要设置。<br>0: 无中断未决<br>1: 中断未决  |

**IRCON (0xCO) - 中断标志 4**

| 位 | 名称    | 复位 | R/W       | 描述                                                                |

|---|-------|----|-----------|-------------------------------------------------------------------|

| 7 | STIF  | 0  | R/W       | 睡眠定时器中断标志<br>0: 无中断未决<br>1: 中断未决                                  |

| 6 | -     | 0  | R/W       | 必须写为0。写入1总是使能中断源。                                                 |

| 5 | P0IF  | 0  | R/W       | 端口0中断标志<br>0: 无中断未决<br>1: 中断未决                                    |

| 4 | T4IF  | 0  | R/W<br>H0 | 定时器4中断标志。当定时器4中断发生时设为1并且当CPU指向中断向量服务例程时清除。<br>0: 无中断未决<br>1: 中断未决 |

| 3 | T3IF  | 0  | R/W<br>H0 | 定时器3中断标志。当定时器3中断发生时设为1并且当CPU指向中断向量服务例程时清除。<br>0: 无中断未决<br>1: 中断未决 |

| 2 | T2IF  | 0  | R/W<br>H0 | 定时器2中断标志。当定时器2中断发生时设为1并且当CPU向量指向中断服务例程时清除。<br>0: 无中断未决<br>1: 中断未决 |

| 1 | T1IF  | 0  | R/W<br>H0 | 定时器1中断标志。当定时器1中断发生时设为1并且当CPU向量指向中断服务例程时清除。<br>0: 无中断未决<br>1: 中断未决 |

| 0 | DMAIF | 0  | R/W       | DMA完成中断标志<br>0: 无中断未决<br>1: 中断未决                                  |

**IRCON2 (0xE8) - 中断标志 5**

| 位   | 名称     | 复位  | R/W | 描述                                    |

|-----|--------|-----|-----|---------------------------------------|

| 7:5 | -      | 000 | R/W | 没有使用                                  |

| 4   | WDTIF  | 0   | R/W | 看门狗定时器中断标志<br>0: 无中断未决<br>1: 中断未决     |

| 3   | P1IF   | 0   | R/W | 端口1中断标志<br>0: 无中断未决<br>1: 中断未决        |

| 2   | UTX1IF | 0   | R/W | USART 1 TX中断标志<br>0: 无中断未决<br>1: 中断未决 |

| 1   | UTX0IF | 0   | R/W | USART 0 TX中断标志<br>0: 无中断未决<br>1: 中断未决 |

| 0   | P2IF   | 0   | R/W | 端口2中断标志<br>0: 无中断未决<br>1: 中断未决        |

### 2.5.3 中断优先级

中断组合成为 6 个中断优先组，每组的优先级通过设置寄存器 IP0 和 IP1 实现。为了给中断（也就是它所在的中断优先组）赋值优先级，需要设置 IP0 和 IP1 的对应位，如表 2-6 所示。

中断优先级及其赋值的中断源显示在表 2-7 中。每组赋值为 4 个中断优先级之一。当进行中断服务请求时，不允许被较低级别或同级的中断打断。

当同时收到几个相同优先级的中断请求时,采取如同表 2-8 所列的轮流探测顺序来判定哪个中断优先响应。注意图 2-4 的轮询顺序是表 2-8 选择的算法,不是图中列在 IP 位之间的轮询。

IP1 (0xB9) - 中断优先级 1

| 位   | 名称       | 复位 | R/W | 描述                             |

|-----|----------|----|-----|--------------------------------|

| 7:6 | -        | 00 | R/W | 不使用                            |

| 5   | IP1_IPG5 | 0  | R/W | 中断第5组, 优先级控制位1, 参考表2-7: 中断优先级组 |

| 4   | IP1_IPG4 | 0  | R/W | 中断第4组, 优先级控制位1, 参考表2-7: 中断优先级组 |

| 3   | IP1_IPG3 | 0  | R/W | 中断第3组, 优先级控制位1, 参考表2-7: 中断优先级组 |

| 2   | IP1_IPG2 | 0  | R/W | 中断第2组, 优先级控制位1, 参考表2-7: 中断优先级组 |

| 1   | IP1_IPG1 | 0  | R/W | 中断第1组, 优先级控制位1, 参考表2-7: 中断优先级组 |

| 0   | IP1_IPG0 | 0  | R/W | 中断第0组, 优先级控制位1, 参考表2-7: 中断优先级组 |

IP0 (0xA9) - 中断优先级 0

| 位   | 名称       | 复位 | R/W | 描述                             |

|-----|----------|----|-----|--------------------------------|

| 7:6 | -        | 00 | R/W | 没有使用                           |

| 5   | IP0_IPG5 | 0  | R/W | 中断第5组, 优先级控制位0, 参考表2-7: 中断优先级组 |

| 4   | IP0_IPG4 | 0  | R/W | 中断第4组, 优先级控制位0, 参考表2-7: 中断优先级组 |

| 3   | IP0_IPG3 | 0  | R/W | 中断第3组, 优先级控制位0, 参考表2-7: 中断优先级组 |

| 2   | IP0_IPG2 | 0  | R/W | 中断第2组, 优先级控制位0, 参考表2-7: 中断优先级组 |

| 1   | IP0_IPG1 | 0  | R/W | 中断第1组, 优先级控制位0, 参考表2-7: 中断优先级组 |

| 0   | IP0_IPG0 | 0  | R/W | 中断第0组, 优先级控制位0, 参考表2-7: 中断优先级组 |

表 2-6 优先级设置

| IP1_x | IP0_x | 优先级      |

|-------|-------|----------|

| 0     | 0     | 0 - 最低级别 |

| 0     | 1     | 1        |

| 1     | 0     | 2        |

| 1     | 1     | 3 - 最高级别 |

表 2-7 中断优先组

| 组    | 中断    |       |       |

|------|-------|-------|-------|

| IPG0 | RFERR | RF    | DMA   |

| IPG1 | ADC   | T1    | P2INT |

| IPG2 | URX0  | T2    | UTX0  |

| IPG3 | URX1  | T3    | UTX1  |

| IPG4 | ENC   | T4    | P1INT |

| IPG5 | ST    | POINT | WDT   |

表 2-8 中断轮流探测顺序

| 中断向量编号 | 中断名称  |             |

|--------|-------|-------------|

| 0      | RFERR | 轮流探测顺序<br>↓ |

| 16     | RF    |             |

| 8      | DMA   |             |

| 1      | ADC   |             |

| 9      | T1    |             |

| 2      | URX0  |             |

| 10     | T2    |             |

| 3      | URX1  |             |

| 11     | T3    |             |

| 4      | ENC   |             |

| 12     | T4    |             |

| 11     | ST    |             |

| 5      | P0INT |             |

| 6      | P2INT |             |

| 7      | UTX0  |             |

| 14     | UTX1  |             |

| 15     | P1INT |             |

| 17     | WDT   |             |

## 第 3 章

SWRU191-April 2009

## 调试接口

两线调试接口允许对片上闪存进行编程，可以访问存储器和寄存器内容，以及调试功能，比如断点、单步和寄存器修改。

调试接口使用 I/O 引脚 P2.1 和 P2.2 分别作为调试模式中的调试数据和调试时钟。当设备不在调试模式下，这些 I/O 引脚只能用于通用 I/O。因此调试接口不干预任何外设 I/O 引脚。

| 标题                 | 页  |

|--------------------|----|

| 3.1 调试模式.....      | 46 |

| 3.2 调试传输 .....     | 46 |

| 3.3 调试命令.....      | 48 |

| 3.4 锁存位 .....      | 48 |

| 3.5 调试接口和供电模式..... | 52 |

| 3.6 寄存器 .....      | 52 |

### 3.1 调试模式

强制在引脚 P2.2 (调试时钟) 上进行两个上升沿传输, 同时 RESET\_N 输入保持低电平时, 则进入调试模式。

当处于调试模式, P2.1 是调试数据的双向引脚, P2.2 是调试时钟输入引脚。

**注意:** 注意调试器不能和一个划分过的系统时钟一起使用。当运行调试器时, 当 CLKCONCMD.OSC=0 时 CLKCONCMD.CLKSPD 的值必须设置为 000, 或者当 CLKCONCMD.OSC=1 时设置为 001。

### 3.2 调试传输

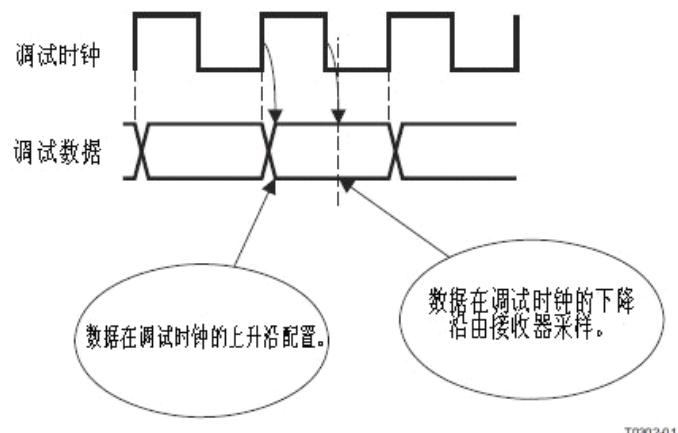

调试接口使用一个类似于 SPI 的双线接口, 包括 P2.1 (调试数据) 和 P2.2 (调试时钟) 引脚。数据在调试时钟的上升沿, 双向调试数据引脚上传输, 在这个时钟的下降沿进行采样。

调试数据引脚的方向取决于发出的命令。数据在调试时钟的上升沿驱动, 在下降沿采样。图 3-1 显示了数据是如何采样的。

图 3-1 外部调试接口时序

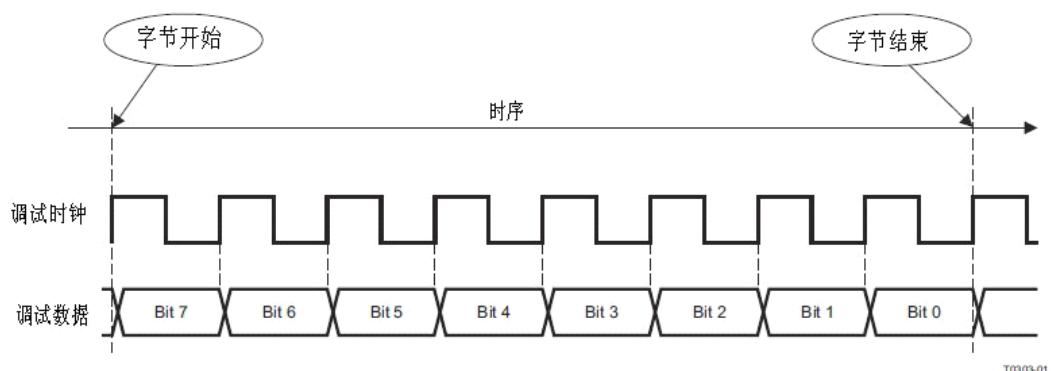

数据是以字节为导向的, MSB 首先传输。一个字节的顺序如图 3-2。

图 3-2 一个字节的传输

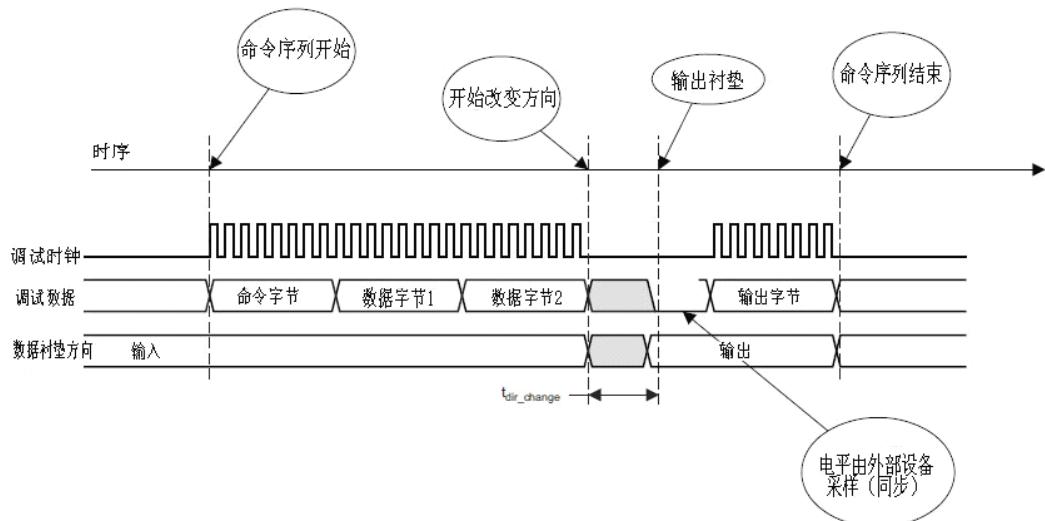

一个调试命令序列总是通过主机通过串行接口发送一个命令开始的。这一命令编码决定进一步参数应该含有的字节数，以及是否需要一个响应。基于这个命令，调试模块控制调试数据衬垫的方向。一个典型的命令序列如图 3-3。注意为了使图清楚，简化了调试数据信号，没有显示每个位的变化。方向不是对外部明确指明的，但是必须由命令协议的主机产生。

图 3-3 典型的命令序列——没有额外等待响应

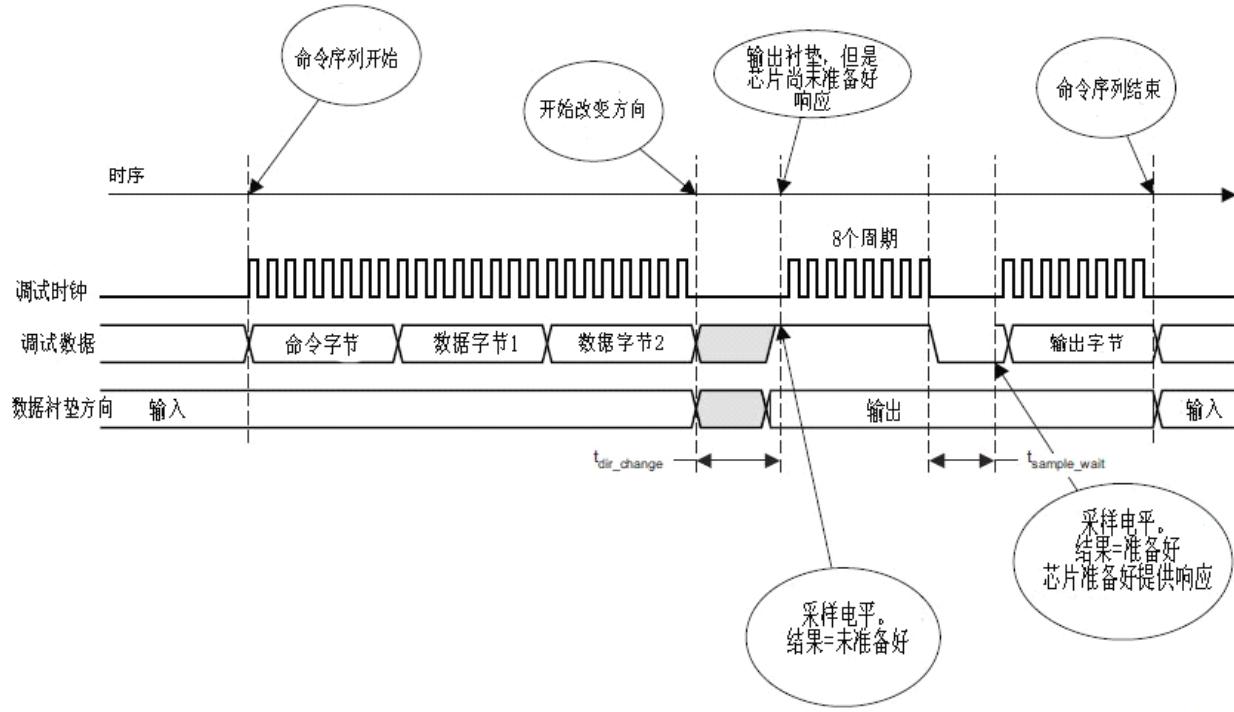

对于需要响应的命令，必须在命令和响应之间有一个短暂的空闲期，以允许衬垫改变方向。最小等待时间( $t_{dir\_change}$ )过后，芯片通过下拉数据衬垫为低电平，表示是否准备好传输响应数据。对数据衬垫采样的外部调试器，探测到这一指示，开始记录响应数据。如果数据衬垫在等待时间过后是高电平，这向调试器表示芯片还没有准备好。图 3-4 显示等待是如何工作的。

图 3-4 典型的命令序列。等待响应

如果调试接口通过上拉数据线为高电平表示它没有准备好返回数据，外部设备在重新采样准备好的电平之前，必须发出正好 8 个时钟脉冲。这必须重复直到电平变为低。等待周期相当于从调试接口读取一个字节，但是忽略结果。注意衬垫在调试时钟的下降沿开始改变方向。因此，衬垫驱动器不能驱动程序员的驱动器，直到程序员改变衬垫的方向。这个持续时间在一个程序实现中必须尽量使它最小。

### 3.3 调试命令

调试命令显示在表 3-2 中。以下章节详细描述了一些调试命令。

最低三位（即 X）无论什么值都可以。

### 3.4 锁位