# SEED-VPM642 用户指南

2008

*DSP Development Systems*

# **SEED-VPM642 用户指南**

TMS320DM642 视频 DSP 处理模板

版本号：E

2008.8

<http://www.seeddsp.com>

## **声明**

北京合众达电子技术有限责任公司保留随时对其产品进行修正、改进和完善的权利，同时也保留在不作任何通告的情况下，终止其任何一款产品的供应和服务的权利。用户在下订单前应获取相关信息的最新版本，并验证这些信息是当前的和完整的。

版权© 2008，北京合众达电子技术有限责任公司

## 前言

# 阅前必读

---

### 简介:

本用户指南是 TMS320DM642 视频 DSP 处理模板硬件使用说明书，详细描述了 SEED-VPM642 的硬件构成、原理，以及它的使用方法和编程指导。

### 保修:

所有由北京合众达电子技术有限责任公司生产制造的硬件和软件产品，保修期为从发货之日起壹年。在保修期内由于产品质量原因引起的损坏，北京合众达电子技术有限责任公司负责免费维修或更换。当在保修期内软件进行了升级，北京合众达电子技术有限责任公司将免费提供。

### 参考资料:

**TMS320C6000 Technical Brief** (文献号SPRU197)：介绍C6000系列DSP的入门知识及开发工具

**TMS320C6000 Cpu and Instruction Set Reference Guide** (文献号SPRU189)：介绍TMS320C6000系列DSP的CPU结构、指令组、流水线及中断。

**TMS320C6000 Peripherals Reference Guide** (文献号SPRU190)：描述C6000系列DSP片上的通用外设，包括DSP片上数据各程序存储器、外部存储接口（EMIF）、主机接口（HPI）、串口、DMA/EDMA控制器、扩展总线（XBUS）、时钟和锁相环电路（PLL）和省电工作方式等。

**TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor** (文献号SPRS200)：描述 TMS320DM642 定点 DSP 的特点、电气指标、时序、以及引脚封装等。

**TMS320DM642 Technical OverView** (文献号 SPRU615)：介绍 TMS320DM642 的各种技术及应用。

**TMS320C6000 DSP External Memory Interface (EMIF) Reference Guide** (文献号SPRU266)：描述DSP的EMIF外设的功能。

**TMS320C6000 DSP Enhanced Direct Memory Access (EDMA) Controller Reference Guide** (文献号 SPRU234) : 描述DSP的EDMA的功能。

**TMS320C6000 DSP 32-Bit Timer Reference Guide** (文献号 SPRU582) : 描述DSP的定时器的功能。

**TMS320C6000 DSP Host Post Interface (HPI) Reference Guide** (文献号 SPRU578) : 描述DSP的HPI功能。

**TMS320C64x DSP Video Port / VCXO Interpolated Control (VIC) Port Reference Guide** (文献号 SPRU629) : 描述视频口与VIC口的功能。

**TMS320C6000 DSP Multichannel Audio Serial Port (McASP) Reference Guide** (文献号 SPRU041) : 描述外设McASP的功能与使用。

**TMS320C6000 DSP Inter-Integrated Circuit (I<sup>2</sup>C) Module Reference Guide** (文献号 SPRU175) : 描述外设I<sup>2</sup>C的功能。

**TMS320C6000 DSP Ethernet Media Access Controller (EMAC) / Management Data Input / Output (MDIO) Module Reference Guide** (文献号 SPRU628) : 描述外设EMAC与MDIO的功能。

**TMS320C600 DSP Peripheral Component Interconnect (PCI) Reference Guide** (文献号 SPRU581) : 描述外设 PCI 的功能。

**TMS320C6000 DSP General-purpose Input / Output (GPIO) Reference Guide** (文献号 SPRU584) : 描述外设 GPIO 的功能。

**TMS320C6000 Assembly Language Tools User's Guide** (文献号 SPRU186) : 描述 TMS320C6000 系列 DSP 的汇编语言工具（汇编器、链接器和其他开发汇编语言程序的工具），汇编器命令、宏命令、通用目标文件格式（COFF）和符号调试命令等。

**TMS320C6000 Optimizing C Compiler User's Guide** (文献号 SPRU1187) : 描述 TMS320C6000 系列 DSP 的 C 编译器和汇编优化器。此 C 编译器将标准的 ANSI C 源程序编译为 TMS320C54x 系列 DSP 的汇编源程序，汇编优化器则帮助你优化你的汇编源程序。

**TMS320C6X Chip Support Library API Reference Guide** (文献号 SPRU401) : 描述对 TMS320C6000 系列 DSP 片上外设支持库的函数和宏命令的内容，相应的函数和宏以头文件和字母顺序二种方式进行排序列表，并进行详细描述，同时给出如何使用它们的程序例子。

**TMS320C6000 Programmer's Guide** (文献号 SPRU198) : 描述对' C6000 系列 DSP 的 C 和汇编源程序进行优化的方法，包括相应的应用程序例子。

**DSP/BIOS User's Guide** (文献号 SPRU423) : 描述如何用 DSP/BIOS 工具和 APIs 对嵌入式实时 DSP 应用程序进行分析。

**TVP5150PBS:** 描述 TVP5150PBS 的低功耗 NTSC/PAL 视频解码芯片的特点、电气指标、时序、以及引脚封装等。

**SAA7121H:** 描述视频编码芯片 SAA7121H 的特点、电气指标、时序、以及引脚封装等。

**BCM5221:** 描述 EMAC 接口芯片 BCM5221 的特点、电气指标、时序、以及引脚封装等。

**TLV320AIC23B:** 描述 TLV320AIC23B 带耳机放大器的 96KHz 立体声 Codec 芯片的特点、电气指标、时序，以及引脚封装等。

**TL16C752B:** 描述 TL16C752B 带 64-字节 FIFO 的双路 UART 芯片的特点、电气指标、时序，以及引脚封装等。

**MAX3160:** 描述 MAX3160 RS232 / RS422 / RS485 多协议收发器芯片的特点、电气指标、时序，以及引脚封装等。

## 商标:

SEED 是北京合众达电子技术有限责任公司的注册商标。

TI、XDS510 是 Texas Instruments 的注册商标。

## 更多帮助:

- 网址: <http://www.seeddsp.com>

- 合众达总公司

地址: 北京市海淀区中关村南大街 12 号寰太大厦 1201 号

邮编: 100081

电话: 010-59796855

传真: 010-62161218

- 北京分公司

地址: 北京市海淀区中关村南大街 12 号寰太大厦 1201 号

邮编: 100081

电话: 010-59796855

传真: 010-51518866

E-mail: [beijing@seeddsp.com](mailto:beijing@seeddsp.com)

- 天津办事处

地址: 天津市河西区气象台路 48 号增 1 号先特写字楼 506 室

邮编: 300074

电话: 022-23556617

传真: 022-23556617

E-mail: [tianjin@seeddsp.com](mailto:tianjin@seeddsp.com)

- 哈尔滨办事处

地址: 哈尔滨市南岗区文君街 69 号文君花园 E 栋 5 单元 301

邮编: 150001

电话: 0451-86203773

手机: 13796604918

E-mail: [leon@seeddsp.com](mailto:leon@seeddsp.com)

- 上海分公司

地址: 上海市黄浦区成都北路 500 号峻岭广场 2208 室

邮编: 200003

电话: 021-63276977

传真: 021-63270962

E-mail: [shanghai@seeddsp.com](mailto:shanghai@seeddsp.com)

- 杭州办事处

地址: 杭州市西湖区文二路 207 号耀江文欣大厦 1209 室

邮编: 310012

电话: 0571-88259367

传真: 0571-88259357

E-mail: [hangzhou@seeddsp.com](mailto:hangzhou@seeddsp.com)

- 深圳分公司

地址: 深圳市福田区泰然工贸园苍松大厦北座 3A02 室

邮编: 518027

电话: 0755-33981828

传真: 0755-33981838

E-mail: [shenzhen@seeddsp.com](mailto:shenzhen@seeddsp.com)

- 广州办事处

地址: 广州市天河区天河北路 615 号鸿翔大夏天麟第 1808 室

邮编: 510630

电话: 020-38473795 020-38473796

传真: 020-38473798

E-mail: [guangzhou@seeddsp.com](mailto:guangzhou@seeddsp.com)

- 香港分公司

地址: 香港九龍觀塘開源道 48 號威利廣場 22 楼 2208 室

电话: +852-34268098 34268099

传真: +852-34264806

E-mail: [seedhk@seeddsp.com](mailto:seedhk@seeddsp.com)

- 南京分公司

地址: 南京市中山东路 218 号长安国际中心 13 楼 F 座

电话: 025-84650405 84650406

传真: 025-84650557

邮编: 210002

E-mail: [nanjing@seeddsp.com](mailto:nanjing@seeddsp.com)

- 合肥办事处

地址: 合肥市金寨路 93 号鸿基广场 504 室 (中科大东区正大门对面)

电话: 0551-3668853 3668854

传真: 0551-3668853-808

邮编: 230026

E-mail: [hefei@seeddsp.com](mailto:hefei@seeddsp.com)

成都办事处

地址: 人民南路 3 段林荫街华西大厦 A 座 602 室

电话: 028-85441353 85431123

传真: 028-85458130

邮编: 610041

E-mail: [chengdu@seeddsp.com](mailto:chengdu@seeddsp.com)

武汉办事处

地址: 湖北省武汉市武昌街道口珞珈山路一号珞珈山大厦 B 座 1511 室

电话: 027-87660475 87660480

传真: 027-87660480-8809

邮编: 430070

E-mail: [wuhan@seeddsp.com](mailto:wuhan@seeddsp.com)

长沙办事处

地址: 湖南长沙河西岳麓区银盆南路 357—3 号威胜大厦 B 座 602 室

电话: 0731-8906758

传真: 0731-8906758

邮编: 410018

E-mail: [xusong@seeddsp.com](mailto:xusong@seeddsp.com)

西安办事处

地址: 陕西西安市长安中路 239 号通瑞大厦 466 室

电话: 029-85248062 88562762 85361239

传真: 029-85248062

邮编: 710061

E-mail: [xian@seeddsp.com](mailto:xian@seeddsp.com)

# 目录

---

---

|                                   |           |

|-----------------------------------|-----------|

| <b>第一章 入门.....</b>                | <b>1</b>  |

| 1.1 特点: .....                     | 1         |

| 1.2 功能框图 .....                    | 2         |

| 1.3 概述 .....                      | 3         |

| 1.4 技术指标 .....                    | 4         |

| <b>第二章 TMS320DM642 基本系统.....</b>  | <b>5</b>  |

| 2.1 TMS320DM642 简介 .....          | 5         |

| 2.2 TMS320DM642 存贮空间的配置.....      | 6         |

| 2.2.1 SEED-VPM642 存储空间的具体配置.....  | 7         |

| 2.3 Video Port和McASP .....        | 10        |

| 2.4 PCI、HPI和网络接口（EMAC与MDIO） ..... | 12        |

| 2.5 IIC .....                     | 13        |

| 2.6 系统时钟 .....                    | 14        |

| 2.7 定时器 .....                     | 15        |

| 2.8 McBSP和VIC .....               | 15        |

| 2.9 复位与中断.....                    | 15        |

| 2.10 上电自举方式的配置 .....              | 16        |

| 2.11 TMS320DM642 的输入与输出 .....     | 17        |

| 2.12 JTAG .....                   | 17        |

| <b>第三章 视频接口.....</b>              | <b>18</b> |

| 3.1 TMS320DM642 的VP口 .....        | 18        |

| 3.2 TVP5150PBS .....              | 19        |

| 3.2.1 TVP5150 视频输入 .....          | 19        |

| 3.2.2 TVP5150 的配置 .....           | 20        |

| 3.2.3 DSP与TVP5150 数字视频流的连接 .....  | 23        |

| 3.3 SAA7121H.....                 | 24        |

| 3.3.1 SAA7121H的配置 .....           | 25        |

| 3.3.2 DSP与SAA7121H的数据口连接 .....    | 25        |

| <b>第四章 音频输入与输出 .....</b>          | <b>27</b> |

| 4.1 TMS320DM642 的McASP接口 .....    | 27        |

| 4.2 TLV320AIC23B.....             | 29        |

| 4.3 TLV320AIC23B与DM642 的接口 .....  | 30        |

|            |                                   |           |

|------------|-----------------------------------|-----------|

| 4.3.1      | AIC23B的数据口 .....                  | 30        |

| 4.3.2      | AIC23B的控制口 .....                  | 32        |

| 4.3.3      | TLC320AIC23B的位时钟实现 .....          | 34        |

| 4.4        | TLV320AIC23B的模拟接口 .....           | 36        |

| 4.4.1      | 立体声输入与麦克风输入 .....                 | 37        |

| 4.4.2      | 立体声与耳机输出 .....                    | 38        |

| <b>第五章</b> | <b>UART &amp; 数字I / O接口 .....</b> | <b>39</b> |

| 5.1        | 数字I / O .....                     | 39        |

| 5.2        | TL16C752B .....                   | 40        |

| 5.2.1      | TL16C752BPT与DSP的连接 .....          | 40        |

| 5.2.2      | UART的寄存器说明 .....                  | 40        |

| 5.2.3      | 波特率的设置 .....                      | 45        |

| 5.3        | 异步串口接口电平 .....                    | 45        |

| <b>第六章</b> | <b>PCI、HPI与以太网接口 .....</b>        | <b>47</b> |

| 6.1        | 自动配置的实现 .....                     | 47        |

| 6.2        | PCI总线接口 .....                     | 47        |

| 6.2.1      | PCI简介 .....                       | 48        |

| 6.2.2      | PCI的寄存器 .....                     | 49        |

| 6.2.3      | PCI的初始化 .....                     | 52        |

| 6.2.4      | PCI内存的映射 .....                    | 53        |

| 6.3.       | HPI.....                          | 54        |

| 6.4        | 网络接口 .....                        | 55        |

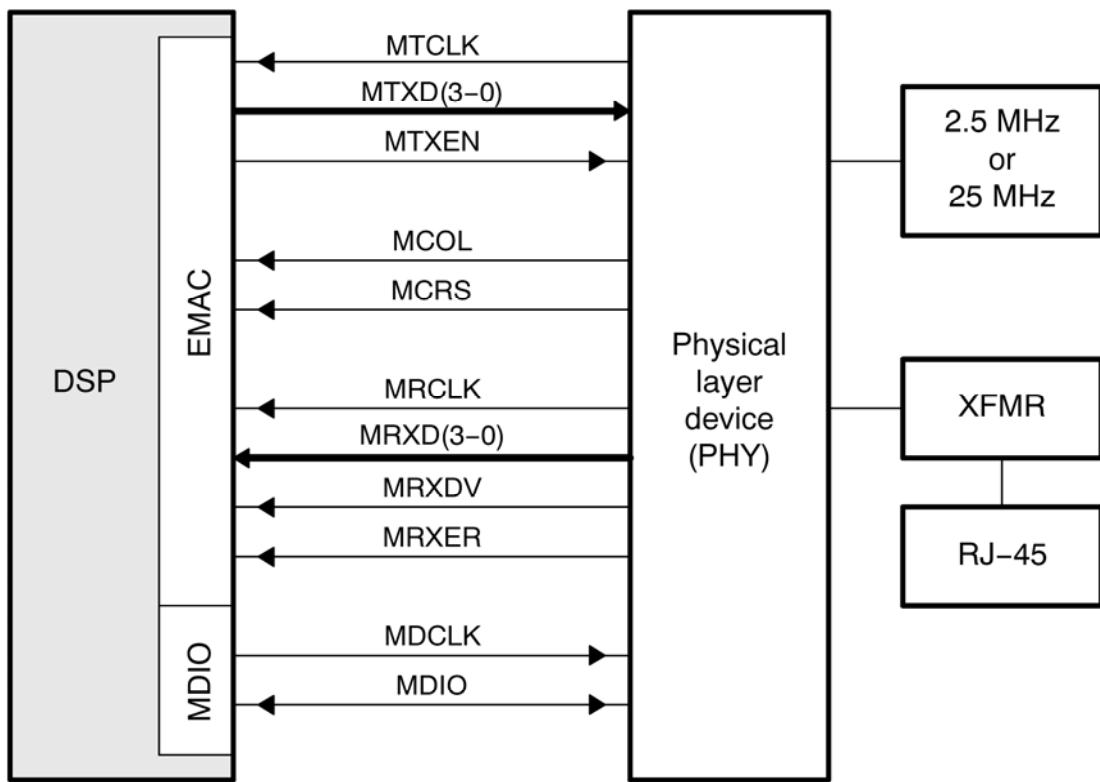

| 6.4.1      | 网络接口的简介 .....                     | 55        |

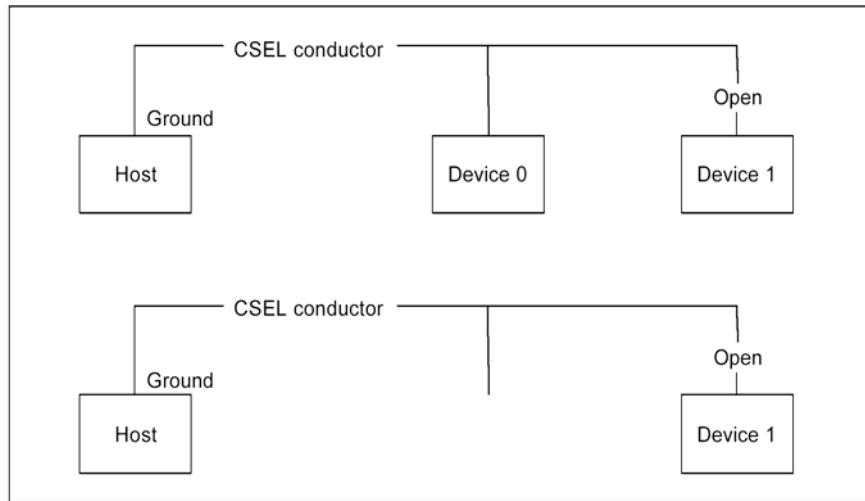

| 6.4.2      | PHY设备的连接 .....                    | 56        |

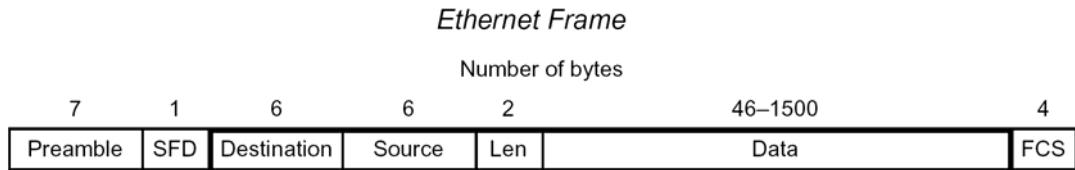

| 6.4.3      | EMAC的数据包 .....                    | 57        |

| <b>第七章</b> | <b>ATA硬盘接口 .....</b>              | <b>58</b> |

| 7.1        | ATA的简介 .....                      | 58        |

| 7.2        | ATA 硬盘接口的实现 .....                 | 59        |

| 7.3        | ATA数据的传送 .....                    | 63        |

| 7.4        | ATA的设备的配置及连接 .....                | 63        |

| <b>第八章</b> | <b>实时时钟 .....</b>                 | <b>65</b> |

| 8.1        | X1226 概述 .....                    | 65        |

| 8.1.1      | IIC总线 .....                       | 65        |

| 8.1.2      | X1226 的寻址 .....                   | 66        |

| 8.1.3      | X1226 片内CCR寄存器的映射 .....           | 68        |

| 8.2        | TMS320DM642 与X1226 接口 .....       | 69        |

| <b>第九章</b> | <b>ESAM加密模块 .....</b>             | <b>70</b> |

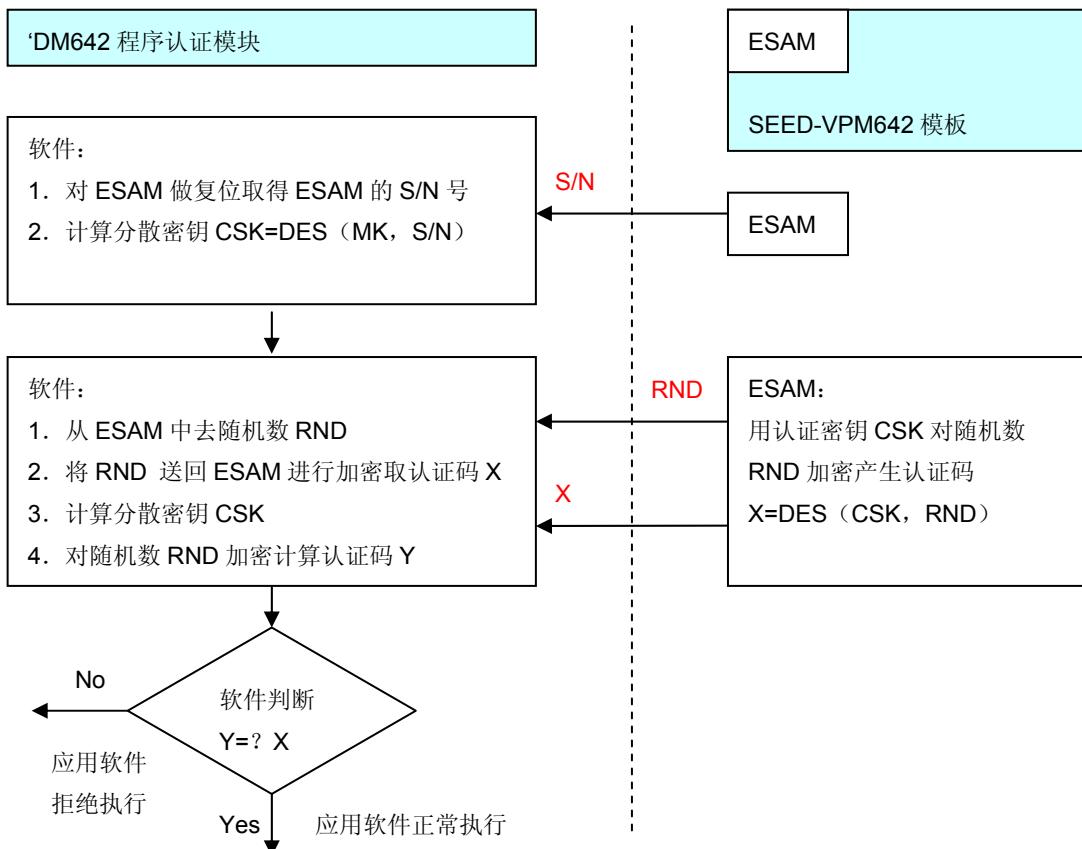

| 9.1        | ESAM加密模块概述: .....                 | 70        |

| 9.2        | ESAM模块的硬件设计: .....                | 71        |

|                              |                                       |           |

|------------------------------|---------------------------------------|-----------|

| 9.3                          | ESAM读写的实现 .....                       | 72        |

| 9.3.1                        | ESAM的读 .....                          | 72        |

| 9.3.2                        | ESAM的写 .....                          | 72        |

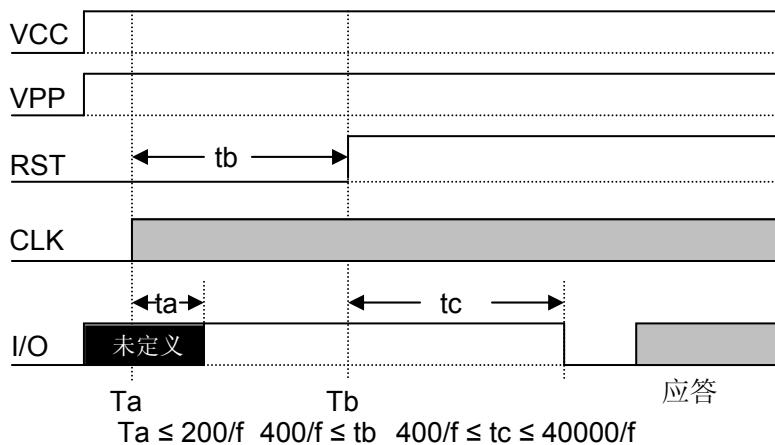

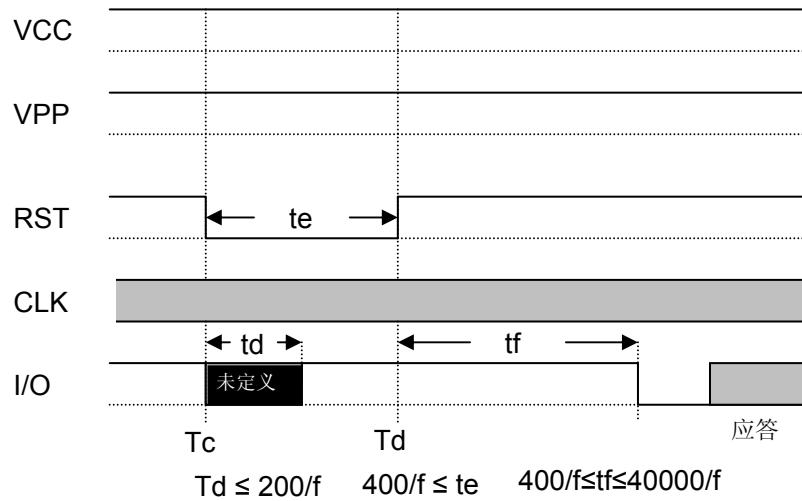

| 9.4                          | ESAM卡的复位及相关读 / 写时序: .....             | 73        |

| 9.4.1                        | 冷复位.....                              | 73        |

| 9.4.2                        | 热复位.....                              | 73        |

| 9.4.3                        | 读写时序说明 .....                          | 74        |

| <b>第十章 测试程序.....</b>         |                                       | <b>75</b> |

| 10.1                         | 存贮器系统的测试 .....                        | 76        |

| 10.1.1                       | SDRAM的测试.....                         | 76        |

| 10.1.2                       | FLASH的测试 .....                        | 77        |

| 10.2                         | Boot的测试 .....                         | 78        |

| 10.2.1                       | FLASH引导的过程.....                       | 78        |

| 10.2.2                       | FLASH引导的测试.....                       | 79        |

| 10.3                         | 音频的测试 .....                           | 80        |

| 10.3.1                       | AUDIO测试的内容 .....                      | 80        |

| 10.3.2                       | AUDIO的测试过程 .....                      | 80        |

| 10.4                         | 图像采集与回放的测试.....                       | 81        |

| 10.4.1                       | 第一路D1 静态图像的采集 .....                   | 81        |

| 10.4.2                       | 第 2~4 通路图像的采集与显示测试.....               | 82        |

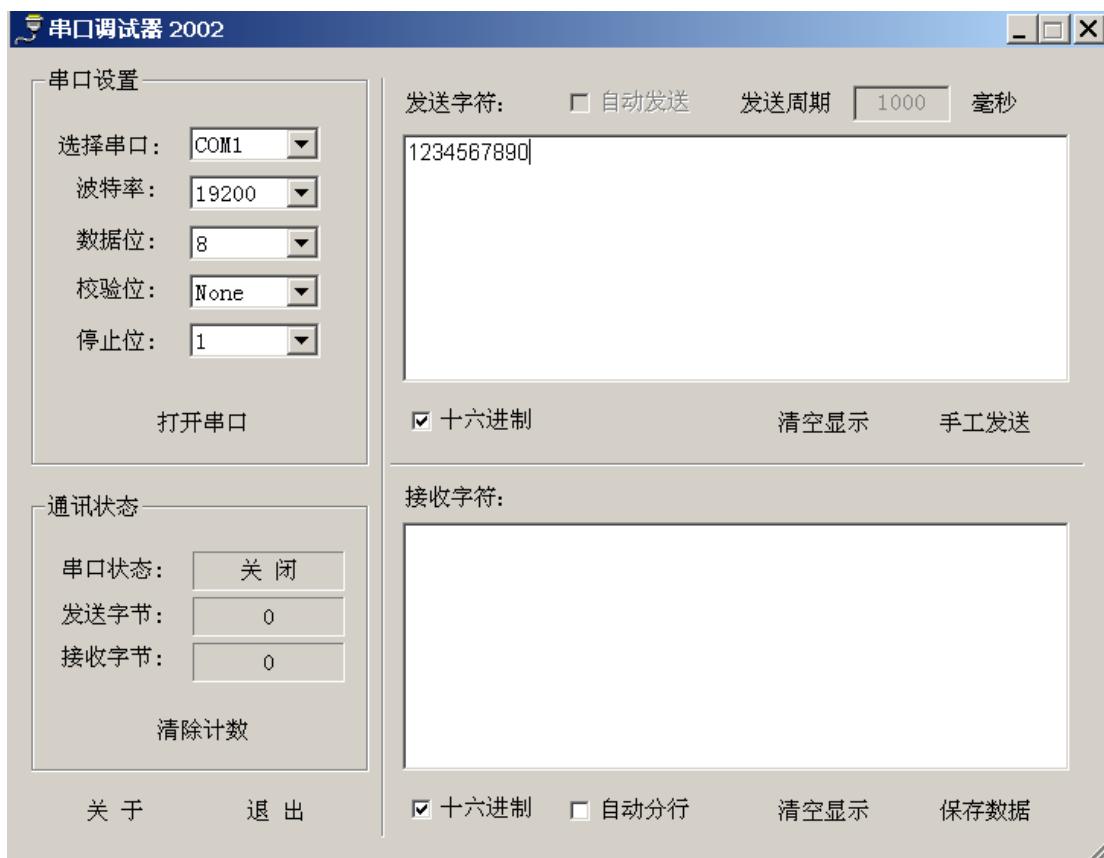

| 10.5                         | UART的测试 .....                         | 83        |

| 10.5.1                       | UART的测试内容 .....                       | 83        |

| 10.5.2                       | UART的测试过程 .....                       | 83        |

| 10.6                         | 以太网接口的测试 .....                        | 84        |

| 10.7                         | ATA硬盘接口的测试 .....                      | 84        |

| 10.8                         | 实时时钟的测试 .....                         | 85        |

| 10.8.1                       | RTC的测试 .....                          | 85        |

| 10.8.2                       | EEPROM的测试 .....                       | 85        |

| 10.9                         | ESAM模块的测试.....                        | 86        |

| <b>第十一章 连接器、跳针、机械尺寸.....</b> |                                       | <b>87</b> |

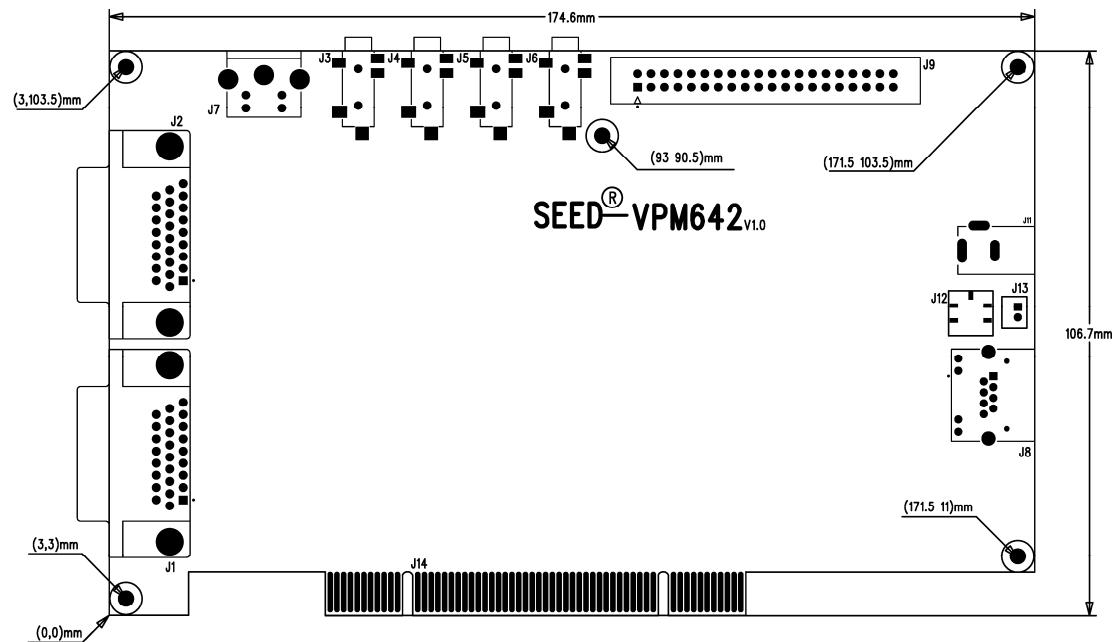

| 11.1                         | 物理布局 .....                            | 87        |

| 11.2                         | 连接器及开关 .....                          | 88        |

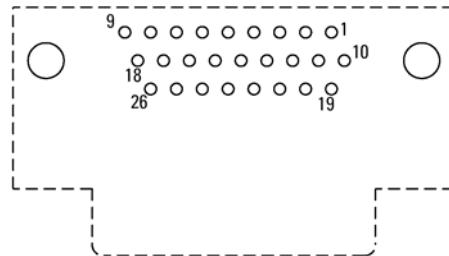

| 11.2.1                       | J1: 数字I/O、异步串口COM A和COM B .....       | 89        |

| 11.2.2                       | J2: 模拟视频、音频的输入 / 输出 .....             | 90        |

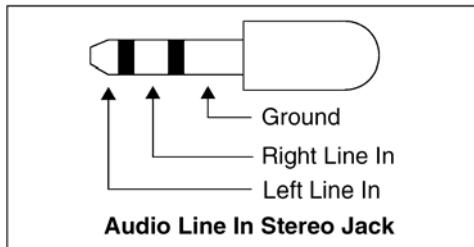

| 11.2.3                       | J3: 第 0 路音频立体声输出口Audio Line OUT ..... | 91        |

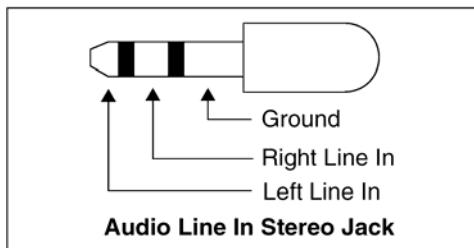

| 11.2.4                       | J4: 第 1 路音频立体声输出口Audio Line OUT ..... | 91        |

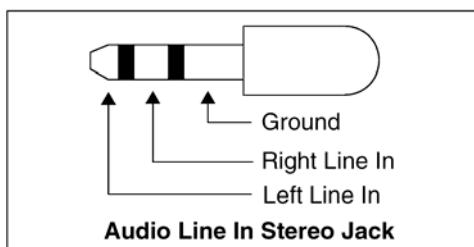

| 11.2.5                       | J5: 第 2 路音频立体声输出口Audio Line OUT ..... | 91        |

| 11.2.6                       | J6: 第 3 路音频立体声输出口Audio Line OUT ..... | 92        |

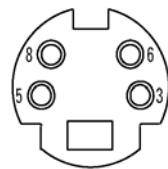

| 11.2.7                       | J7: 图像的S端输出 .....                     | 92        |

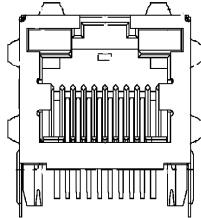

| 11.2.8                       | J8: 网络接口 .....                        | 93        |

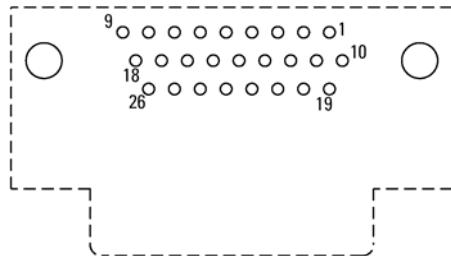

| 11.2.9                       | J9: ATA硬盘连接器 .....                    | 93        |

|                                 |            |

|---------------------------------|------------|

| 11.2.10 J10: JTAG仿真器接口 .....    | 95         |

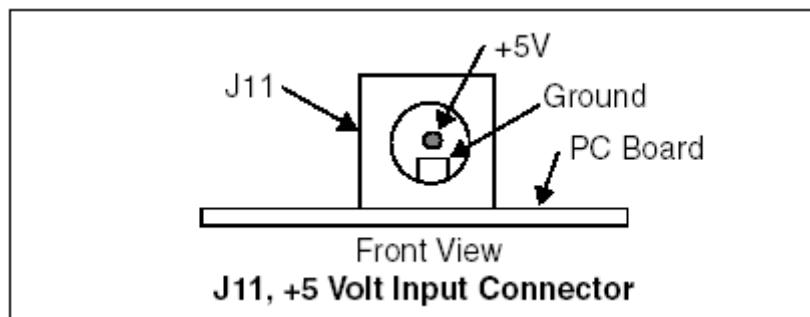

| 11.2.11 J11: +5V电源输入口 .....     | 95         |

| 11.2.12 J12: 复位按钮.....          | 95         |

| 11.2.13 J13: 外部复位输入.....        | 95         |

| 11.2.14 J14: PCI或HPI连接器 .....   | 96         |

| 11.3 指示灯 .....                  | 99         |

| <b>附录A 寄存器 .....</b>            | <b>100</b> |

| A.1 数字量输出寄存器（DOUTR） .....       | 100        |

| A.2 数字量输入寄存器（DINR） .....        | 100        |

| A.3 Flash页寄存器（FLASHPAGE）： ..... | 100        |

| A.4 ATA状态寄存器（ATASTATUS） .....   | 101        |

| A.5 串口配置寄存器（UARTSET） .....      | 101        |

| A.6 音频锁相环控制寄存器（AUDIOPLL） .....  | 102        |

| A.7 ESAM控制寄存器（ESAMCNTL） .....   | 102        |

| A.8 ESAM状态寄存器（ESAMSTATUS） ..... | 103        |

| A.9 看门狗使能寄存器（WATCHDOG） .....    | 103        |

| A.10 看门狗使能寄存器（WDUP） .....       | 103        |

| A.11 串口中断源寄存器（UARTINIT） .....   | 103        |

| <b>附录B 可编程器件说明 .....</b>        | <b>105</b> |

# 第 1 章

## 入门

---

### 1.1 特点:

- 采用 TMS320DM642，专用于数字媒体应用的高性能 32-位定点 DSP，工作主频最高达 720MHz，处理性能可达 5760MIPS

- ◆ 片上存贮器：

- L1P Cache: 16K×8-位

- L1D Cache: 16K×8-位

- L2 RAM/Cache: 256K×8-位

- ◆ 片上外设：

- 32 位的定时器： 3 通路；

- McBSP: 2 通路；

- McASP: 1 通路；

- Video Port: 3 通路；

- VIC: 1 通路；

- PCI: 1 通路；

- IIC: 1 通路；

- GPIO: 8 通路；

- EMAC&MDIO: 1 通路；

- 16/32 位 HPI: 1 通路；

- 外扩 SDSRAM，容量为 4M×64 位

- 外扩 Flash，容量为 4M×8 位

- 4 路 PAL/NTSC 标准模拟视频输入（CVBS 或 Y/C 可选），1 路 PAL/NTSC 标准模拟视频输出（CVBS + Y/C）

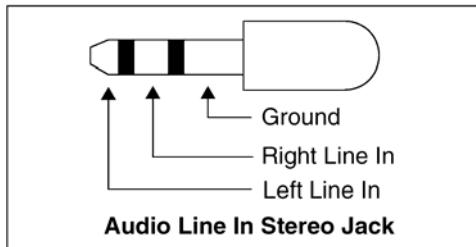

- 4 路立体声音频输入 / 输出（Microphone 输入或 Line In 可选）

- 8 路数字量输入，8 路数字量输出，用于状态和报警信号的输入 / 输出

- 2 路 UART 接口，接口标准 RS232 / RS422 / RS485 可配置

- 实时时钟 RTC + 512×8-位 EEPROM

- 32 位、33MHz，支持主 / 从模式的 PCI 2.2 标准

- 10M/100Mbase-TX 标准以太网接口

- 标准的 ATA 硬盘接口

- ESAM 硬件加密模块，支持 DES / 3DES 密钥算法，2K×8-位加密保护的 EEPROM，可存放密钥、设备序列号、或其他重要的代码或数据

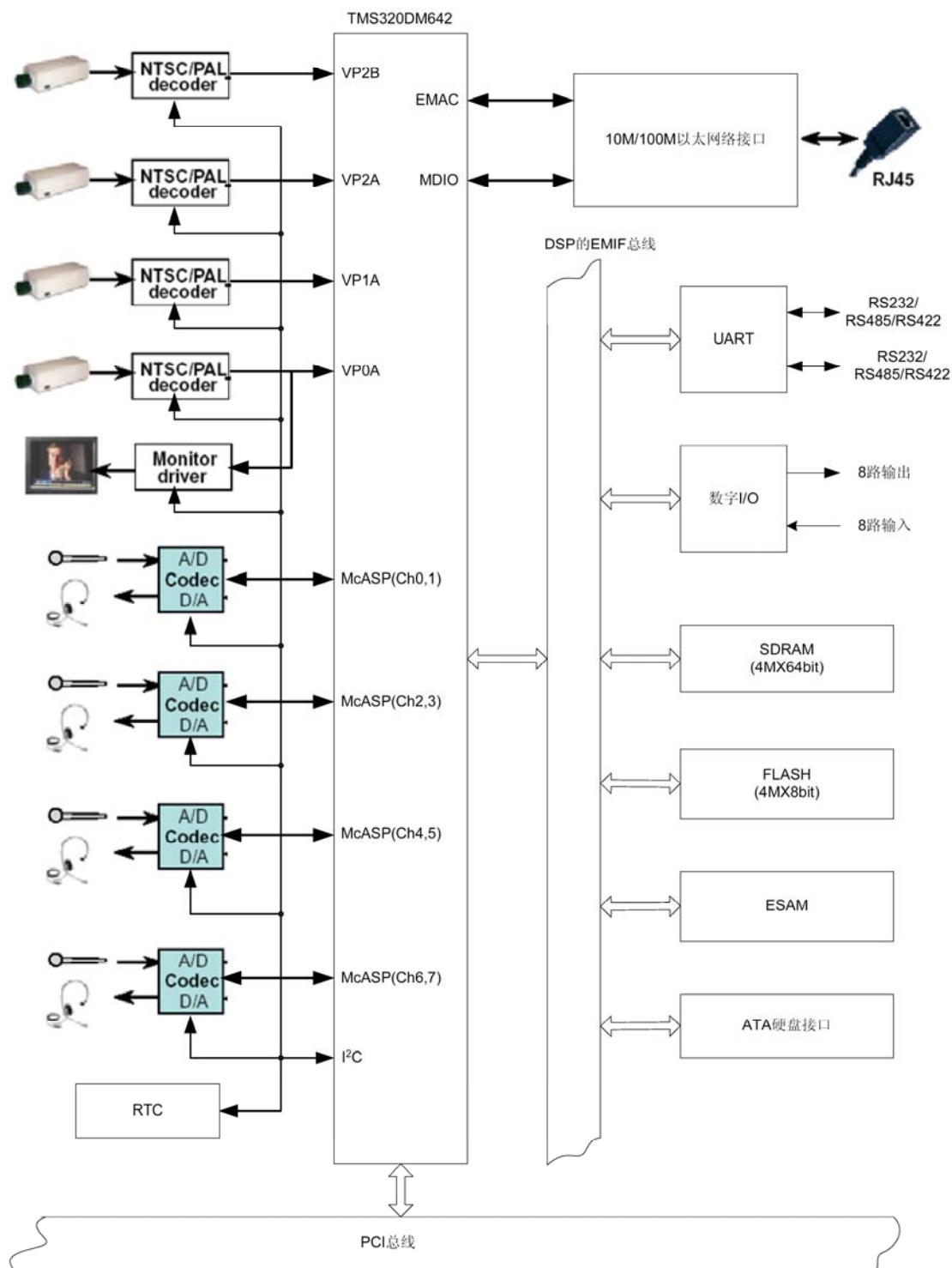

## 1.2 功能框图

注：

PCI与EMAC功能只能二选一；

VP0A的功能只能二选一。

### 1.3 概述

SEED-VPM642 是一款专为各种视频应用而开发的 PCI 插卡或带 10/100M 以太网接口的独立的模板，其上包含：专用于数字媒体应用的高性能 32-位定点 DSP TMS320DM642，其工作主频高达 720MHz，处理性能可达 5760MIPS，可实时实现多路数字视频 / 音频的编码运算，如：MPEG4、H.264、G.729 等；多路视 / 音频接口：4 路 PAL/NTSC 制标准复合或 Y/C 模拟视频输入，1 路 PAL/NTSC 制标准复合或 Y/C 模拟视频输出，4 路标准的 Microphone 输入或 Audio Line In 立体声输入，4 路标准的 Audio Line Out 立体声输出；2 路可编程切换的 RS232/RS422/RS485 异步接口，8 路数字输入、8 路数字输出，用于云台控制和环境监控；大容量本地存储：标准的 ATA 硬盘接口，方便本地存储，实现数字视频录像机功能；高速数据传输接口：标准的 32-位、33MHz、支持主 / 从模式的 PCI 2.2 总线、或 10/100M 以太网接口，方便实现数字视频服务器功能；实时时钟，为数字视频 / 音频提供实时时基信息；软 / 硬件加密功能，更好地保护产品开发者的知识产权。

SEED-VPM642 结构紧凑、布局合理，标准的半长 PCI 插卡（175mm×107mm），4 路视频输入 / 1 路视频输出和 4 路音频立体声输入、8 路开入 / 8 路开出和 2 路 RS232/RS422/RS485 异步串口分别由 2 个高密度 DB-26 连接器从 PC 机后面板引出，+5V 电源输入、RJ45 以太网接口则从对边引出，ATA 硬盘接口位于右上方，而 1 路 Y/C 视频输出和 4 路立体声音频输出则位于左上方。

SEED-VPM642 系统主要包含两部分，分别为 SEED-VPM642 的硬件系统与相应的测试软件。

在 SEED-VPM642 中主要集成了 DSP、SDRAM、FLASH、VIDEO、AUDIO、UART、IO、RTC、ESAM、ATA 与网络接口等外设。这样使其能够应用在视频与语音的处理及其相关的领域。

相应的测试软件包括以下几个部分：

- DSP 对 VIDEO 的操作的示例程序；

- DSP 对 AUDIO 的操作的示例程序；

- DSP 对 IO 的操作及 UART 与计算机通讯的示例程序；

- DSP 对 ESAM 的操作的示例程序；

- DSP 对 RTC 的操作的示例程序；

- DSP 对 SDRAM 与 FLASH 的操作示例；

- DSP 对 ATA 的操作的示例程序；

- DSP 对网络接口的操作的示例程序；

- PCI 的操作示例程序；

- DSP 的 Bootloader 示例程序；

## 1.4 技术指标

- 主处理器: TMS320DM642, 工作主频高达 720MHz, 处理能力可达 5760MIPS

- SDRAM: 4M×64-位, 工作时钟 133MHz

- Flash: 4M×8-位, 70ns (20 年数据保存, 1,000,000 次擦写)

- 视频输入: 4 通道, DB-26 连接器, PAL/NTSC 标准模拟视频信号 (CVBS 或 Y/C 可选), 最大输入范围: 0~1 V<sub>PP</sub>

NTSC: 720×525@30 帧 / 秒

PAL: 720×625@25 帧 / 秒

- 视频输出: 1 通道, DB-26 连接器, PAL/NTSC 标准模拟视频信号 (CVBS + Y/C 可选), 最大输出范围: CVBS: 0~1.23 V<sub>PP</sub>, Y: 0~1 V<sub>PP</sub>, C: 0~0.89 V<sub>PP</sub>

NTSC: 720×525@30 帧 / 秒

PAL: 720×625@25 帧 / 秒

- 音频输入: 4 通道, DB-26 连接器, Microphone 输入 (支持驻极体 Microphone, 并提供偏置电压)、或 Line In 输入 (输入范围: 2V<sub>RSM</sub>)

支持 8KHz~96KHz@16/20/24/32-位采样

- 音频输出: 4 通道, 标准 3.5mm Audio Jack 连接器, Line Out 输出 (输出范围: 1V<sub>RSM</sub>@10KΩ / 50pF 负载)

支持 8KHz~96KHz@16/20/24/32-位采样

- 异步串口: 2 通道, DB-26 连接器, RS232/RS422/RS485 可编程配置

传输率: RS232: 1Mbaud; RS422/RS485: 1.92Mbaud

- 数字 I/O: 8 路开入、8 路开出, DB-26 连接器

开入: V<sub>IH</sub>: 2.0V~5.5V, V<sub>IL</sub>: -0.5V~0.8V

开出: V<sub>OH</sub>: 2.4V@-4mA, V<sub>OL</sub>: 0.5V@8mA

- 实时时钟: 提供年、月、日、星期、时、分、秒等实时信息 (±30ppm)

提供 512×8-位 EEPROM (100 年数据保存, 100,000 次擦写)

IIC 总线 400KHz 数据传输率

- PCI 接口: 32 位、33MHz, 支持主 / 从模式的 PCI 2.2 标准

- 以太网接口: 10M/100Mbase-TX 标准, 标准的带绿、黄 2 个 LED 指示灯的 RJ45 连接器, 绿灯指示连接状态, 黄灯指示数据传输或传输速度

- ATA 接口: 带围墙的 40-芯 IDC 针式插座, 实现 ATA 的 PIO 4.0 传输方式

- 工作温度: 0~70°C

- 机械尺寸: 标准 PCI 半长卡 (175mm×107mm)

# TMS320DM642 基本系统

---

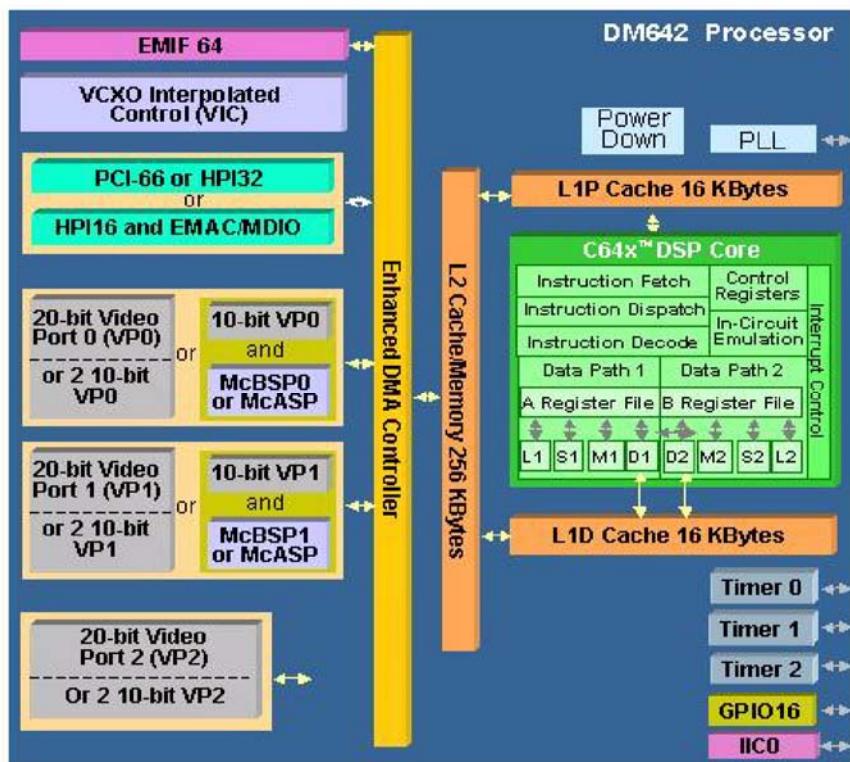

## 2.1 TMS320DM642 简介

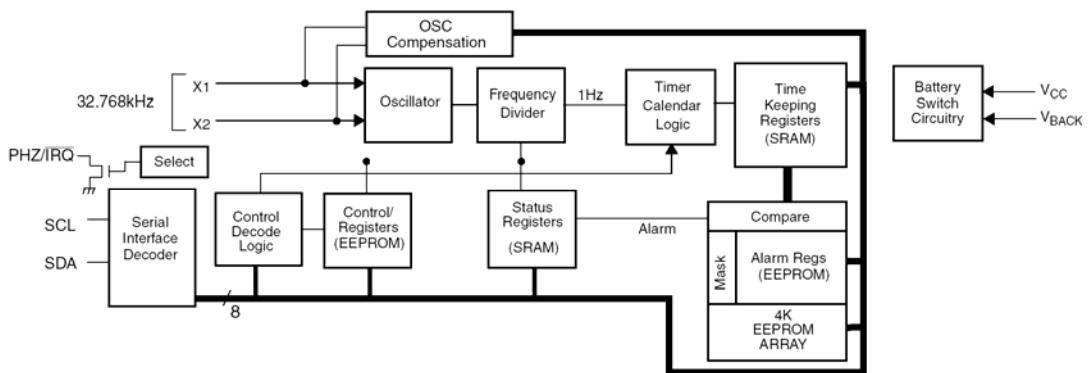

TMS320DM642 是美国德州仪器公司 (TI) 推出的一款面向数字多媒体应用的 DSP，它在 TI 的 C64x DSP 内核基础上进一步集成了完备的视频 / 音频输入 / 输出接口、以太网接口、PCI-66 总线等片上外设，不仅能使用户很方便地对音频 / 视频等各种复杂的运算进行高速处理，还能为方便、无缝地接口视频 / 音频编解码器件和以太网 / PCI 总线等数据传输接口。非常适用于 VoIP、数字视频服务器、多通道数字视频录像机 (DVR)、多通道数字视频监控等应用，提供高质量的视频编 / 解码解决方案。其功能框图如下：

## 2.2 TMS320DM642 存贮空间的配置

TMS320DM642 的程序 / 数据空间以字节为单位进行统一编址，整个寻址空间为 4G-字节。其片上存储器、片上外设、及外部存储器接口（EMIF）均映射到此 4G-字节空间中。

TMS320DM642 的存贮空间映射如下图所示：

| Memory Block Description                      | Block Size<br>(Bytes) | HEX Address Range     |

|-----------------------------------------------|-----------------------|-----------------------|

| Internal RAM (L2)                             | 256K                  | 0000 0000 ~ 0003 FFFF |

| Reserved                                      | 768K                  | 0004 0000 ~ 000F FFFF |

| Reserved                                      | 23M                   | 0010 0000 ~ 017F FFFF |

| External Memory Interface A (EMIFA) Registers | 256K                  | 0180 0000 ~ 0183 FFFF |

| L2 Registers                                  | 256K                  | 0184 0000 ~ 0187 FFFF |

| HPI Registers                                 | 256K                  | 0188 0000 ~ 018B FFFF |

| McBSP 0 Registers                             | 256K                  | 018C 0000 ~ 018F FFFF |

| McBSP 1 Registers                             | 256K                  | 0190 0000 ~ 0193 FFFF |

| Timer 0 Registers                             | 256K                  | 0194 0000 ~ 0197 FFFF |

| Timer 1 Registers                             | 256K                  | 0198 0000 ~ 019B FFFF |

| Interrupt Selector Registers                  | 256K                  | 019C 0000 ~ 019F FFFF |

| EDMA RAM and EDMA Registers                   | 256K                  | 01A0 0000 ~ 01A3 FFFF |

| Reserved                                      | 512K                  | 01A4 0000 ~ 01AB FFFF |

| Timer 2 Registers                             | 256K                  | 01AC 0000 ~ 01AF FFFF |

| GP0 Registers                                 | 256K - 4K             | 01B0 0000 ~ 01B3 EFFF |

| Device Configuration Registers                | 4K                    | 01B3 F000 ~ 01B3 FFFF |

| I <sup>2</sup> C0 Data and Control Registers  | 16K                   | 01B4 0000 ~ 01B4 3FFF |

| Reserved                                      | 32K                   | 01B4 4000 ~ 01B4 BFFF |

| McASP0 Control Registers                      | 16K                   | 01B4 C000 ~ 01B4 FFFF |

| Reserved                                      | 192K                  | 01B5 0000 ~ 01B7 FFFF |

| Reserved                                      | 256K                  | 01B8 0000 ~ 01BB FFFF |

| Emulation                                     | 256K                  | 01BC 0000 ~ 01BF FFFF |

| PCI Registers                                 | 256K                  | 01C0 0000 ~ 01C3 FFFF |

| VP0 Control                                   | 16K                   | 01C4 0000 ~ 01C4 3FFF |

| VP1 Control                                   | 16K                   | 01C4 4000 ~ 01C4 7FFF |

| VP2 Control                                   | 16K                   | 01C4 8000 ~ 01C4 BFFF |

| VIC Control                                   | 16K                   | 01C4 C000 ~ 01C4 FFFF |

| Reserved                                      | 192K                  | 01C5 0000 ~ 01C7 FFFF |

| EMAC Control                                  | 4K                    | 01C8 0000 ~ 01C8 0FFF |

| EMAC Wrapper                                  | 8K                    | 01C8 1000 ~ 01C8 2FFF |

| EWRAP Registers                               | 2K                    | 01C8 3000 ~ 01C8 37FF |

| MDIO Control Registers                        | 2K                    | 01C8 3800 ~ 01C8 3FFF |

|                    |           |                       |

|--------------------|-----------|-----------------------|

| Reserved           | 3.5M      | 01C8 4000 ~ 01FF FFFF |

| QDMA Registers     | 52        | 0200 0000 ~ 0200 0033 |

| Reserved           | 928M - 52 | 0200 0034 ~ 2FFF FFFF |

| McBSP 0 Data       | 64M       | 3000 0000 ~ 33FF FFFF |

| McBSP 1 Data       | 64M       | 3400 0000 ~ 37FF FFFF |

| Reserved           | 64M       | 3800 0000 ~ 3BFF FFFF |

| McASP0 Data        | 1M        | 3C00 0000 - 3C0F FFFF |

| Reserved           | 64M - 1M  | 3C10 0000 - 3FFF FFFF |

| Reserved           | 832M      | 4000 0000 - 73FF FFFF |

| VP0 Channel A Data | 32M       | 7400 0000 - 75FF FFFF |

| VP0 Channel B Data | 32M       | 7600 0000 - 77FF FFFF |

| VP1 Channel A Data | 32M       | 7800 0000 - 79FF FFFF |

| VP1 Channel B Data | 32M       | 7A00 0000 - 7BFF FFFF |

| VP2 Channel A Data | 32M       | 7C00 0000 - 7DFF FFFF |

| VP2 Channel B Data | 32M       | 7E00 0000 - 7FFF FFFF |

| EMIFA CE0          | 256M      | 8000 0000 - 8FFF FFFF |

| EMIFA CE1          | 256M      | 9000 0000 - 9FFF FFFF |

| EMIFA CE2          | 256M      | A000 0000 - AFFF FFFF |

| EMIFA CE3          | 256M      | B000 0000 - BFFF FFFF |

| Reserved           | 1G        | C000 0000 - FFFF FFFF |

TMS320DM642 通过外部存贮器接口 (EMIF) 访问片外存储器，EMIF 由 64-位数据线 D[63:0]、20-位地址线 A[22:03]、8-位字节使能线 BE[7:0]、4-位片选线 CE3~CE0 和各类存储器的读 / 写控制信号 ARE/SADS/SDCAS/SRE、AOE/SOE/SDRAS、AWE/SWE/SDWE、ARDY、SDCKE、SOE3、HOLD、HOLDA、ECLKIN、ECLKOUT1、ECLKOUT2 组成，每个 CEx 空间有 256M-字节寻址空间，并且可配置为与 SRAM、Flash、SDRAM、ZBTSRAM 等各类存储器接口。

SEED-VPM642 上 EMIF 的外部输入时钟 ECLKIN 设计为 133MHz，因此 EMIF 以 133MHz 时钟进行工作。

关于 TMS320DM642 的 EMIFA 的设计与应用，请参看文档：**TMS320C6000 DSP External Memory Interface (EMIF) Reference Guide** (文献号 SPRU266)。

## 2.2.1 SEED-VPM642 存储空间的具体配置

SEED-VPM642 视频处理模板上，通过 EMIF 扩展的外部存储资源如下：

- Flash 最大 4M×8-位，8-位异步静态存储器接口；

- SDRAM 最大 4M×64-位，64-位同步动态存储器接口；

- |              |                                                                 |

|--------------|-----------------------------------------------------------------|

| □ 状态 / 控制寄存器 | $8 \times 8$ -位, 8-位异步静态存储器接口。这些寄存器位于 SEED-VPM642 模板的 CPLD 中实现; |

| □ UARTA      | $8 \times 8$ -位, 8-位异步静态存储器接口;                                  |

| □ UARTB      | $8 \times 8$ -位, 8-位异步静态存储器接口;                                  |

| □ ATA        | $16 \times 16$ -位, 16-位异步静态存储器接口;                               |

这些外扩的存储资源将被映射到 DM642 的 EMIF 的 4 个  $\overline{CE}_x$  存储空间中, 分配时将相同类型、相同数据宽度的存储器接口组合到同一个  $\overline{CE}_x$  存储空间中, 存储空间的具体分配如下。

### 2.2.1.1 $\overline{CE}_0$ 空间

TMS320DM642 的  $\overline{CE}_0$  子空间被配置为 64-位 SDRAM 接口, 分配给外扩的 SDRAM 使用。SDRAM 的工作时钟由 DM642 的 ECLKOUT1 提供, 其可由软件配置为 EMIF 的 ECLKIN、或 CPU 时钟/4、或 CPU 时钟/6, 最高为 133MHz。一般情况下, 配置为 ECLKIN, 即 133MHz。

SDRAM 在  $\overline{CE}_0$  子空间的具体定位为: 0x8000 0000~0x81FF FFFF。

SDRAM 的读 / 写时序参看《**MT48LC4M32BPG Data Sheet**》。

### 2.2.1.2 $\overline{CE}_1$ 空间

TMS320DM642 的  $\overline{CE}_1$  子空间被配置为 8-位异步具体存储器接口, 分配给了 SEED-VPM642 模板上的 Flash、状态 / 控制寄存器、UARTA、UARTB 等使用,  $\overline{CE}_1$  子空间的具体划分如下:

#### 2.2.1.2.1 Flash

SEED-VPM642 模板上最大可以配置  $4M \times 8$ -位的 Flash, DM642 将 EMIF 的  $\overline{CE}_1$  子空间配置为 8-位异步静态存储器接口来接口 Flash, Flash 的读 / 写时序参见《**Am29LV033C Data Sheet**》。Flash 在  $\overline{CE}_1$  子空间占据的具体空间定位为 0x9000 0000~0x9007 FFFF。

TMS320DM642 外部地址总线只有 A[22:3], 总共 20 根, 所以  $\overline{CE}_1$  子空间最大的寻址范围为  $1M \times 8$ -位。SEED-VPM642 板上  $\overline{CE}_1$  子空间除了分配给 Flash 以外, 还分配给状态 / 控制寄存器、UARTA、UARTB 等资源使用, 其中 Flash 只占据  $\overline{CE}_1$  子空间的前一半的寻址空间, 即最大的可寻址范围为  $512K \times 8$ -位, 而 Flash 的设计容量为  $4M \times 8$ -位, 所以为了解决到 Flash 所有的地址空间, 在 SEED-VPM642 模板上采用分页技术来实现对 Flash 的访问, 即将整个  $4M \times 8$ -位的 Flash 分成 8 个  $512K \times 8$ -位的页, 而页地址 PA21、PA20、PA19 则由页地址寄存器提供 (页地址寄存器位于 CPLD 中)。

Flash 页寄存器 (FLASHPAGE) :

地址: 0x9008 0011 (只写)

| D07 | D06 | D05 | D04 | D03 | D02  | D01  | D00  |

|-----|-----|-----|-----|-----|------|------|------|

| ×   | ×   | ×   | ×   | ×   | PA21 | PA20 | PA19 |

PA[21:19]: FLASH 的页地址

### 2.2.1.2.2 状态 / 控制寄存器

SEED-VPM642 模板上共有 7 个控制寄存器，用于设置板上各个外设的状态，其控制寄存器列表如下：

- |                 |                                |

|-----------------|--------------------------------|

| □ DIOOUT 寄存器    | 8-位，用于控制 8-位数字量输出；             |

| □ FLASHPAGE 寄存器 | 3-位，用于给出 Flash 的页地址 PA[21:19]； |

| □ UARTSET 寄存器   | 4-位，用于设置 UART 的工作方式；           |

| □ AUDIOPLL 寄存器  | 3-位，用于设置 音频锁相环 PLL1708；        |

| □ ESAMCNTL 寄存器  | 3-位，用于与嵌入式加密模块（ESAM）进行通信；      |

| □ WATCHDOG 寄存器  | 1-位，用于使能看门狗；                   |

| □ WDUP 寄存器      | 0-位，用于刷新看门狗。                   |

SEED-VPM642 模板上共有 3 个状态寄存器，用于采集当前模板上各个外设的运行状况，其列表如下：

- |                  |                           |

|------------------|---------------------------|

| □ DIOIN 寄存器      | 8-位，用于读取 8-位数字量输入；        |

| □ ATASTATUS 寄存器  | 1-位，用于读取 ATA 的工作状态；       |

| □ ESAMSTATUS 寄存器 | 1-位，用于与嵌入式加密模块（ESAM）进行通信。 |

SEED-VPM642 状态 / 控制寄存器的地址列表如下：

| 寄存器        | 地址          | 读与写 |

|------------|-------------|-----|

| DIOOUT     | 0x9008 0010 | 只写  |

| FLASHPAGE  | 0x9008 0011 | 只写  |

| UARTSET    | 0x9008 0012 | 只写  |

| AUDIOPLL   | 0x9008 0013 | 只写  |

| ESAMCNTL   | 0x9008 0014 | 只写  |

| WATCHDOG   | 0x9008 0015 | 只写  |

| WDUP       | 0x9008 0016 | 只写  |

| DIOIN      | 0x9008 0010 | 只读  |

| ATASTATUS  | 0x9008 0011 | 只读  |

| ESAMSTATUS | 0x9008 0014 | 只读  |

SEED-VPM642 状态 / 控制寄存器的详细说明参见附录 A。

### 2.2.1.2.3 UART

SEED-VPM642 模板上选用 TL16C752B 实现 2 路异步串口，'DM642 将 EMIF 的 CE1 子空间配置为 8 位异步静态存储器接口来接口 TL16C752B，每路异步串口占用 8 个 8 位存储单元，TL16C752B 在 CE1 子空间的具体定位如下表：

| 串口     | 字节地址                      |

|--------|---------------------------|

| UART A | 0x9008 0000 ~ 0x9008 0007 |

| UART B | 0x9008 0007 ~ 0x9008 000F |

TL16C752B 的读 / 写时序参见《**TL16C752B Data Sheet**》。

有关 SEED-VPM642 的 2 个异步串口的详细描述参见第 3 章《UART 接口》。

### 2.2.1.3 CE2空间

TMS320DM642 的 CE2 子空间被配置为 16 位异步静态存储器接口，分配给外扩的 ATA 标准硬盘接口，以 PIO 方式来实现硬盘的读 / 写操作。ATA 有 2 个片选空间 CS0 和 CS1，每个空间占用 8 个 16 位存储单元，ATA 在 CE2 子空间的具体定位如下表：

| 串口      | 字节地址                      |

|---------|---------------------------|

| ATA_CS0 | 0xA000,0000 ~ 0xA000,0007 |

| ATA_CS1 | 0xA000,0010 ~ 0xA000,0017 |

有关 SEED-VPM642 的硬盘接口的详细描述参见第 4 章《ATA 接口》。

### 2.2.1.4 CE3空间

此空间在 SEED-VPM642 模板上未使用。

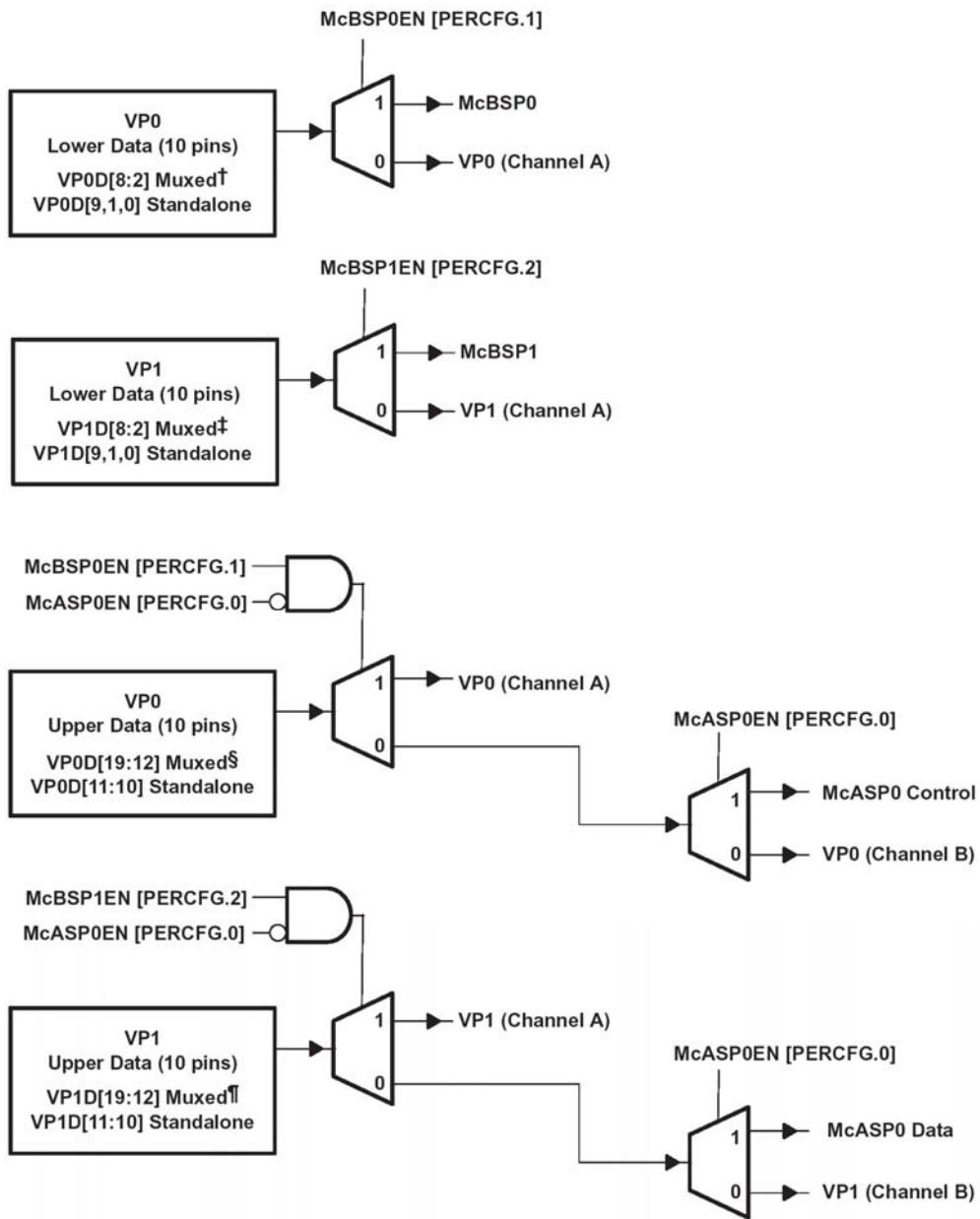

## 2.3 Video Port和McASP

TMS320DM642 共有三个视频口，分别为 VP0、VP1 和 VP2。其中 VP2 为单一功能的视频口。VP0 与 VP1 则与 McBSP、McASP 复用引脚的，其功能选择由 DM642 上的外设配置寄存器（PERCFG）进行配置的。PERCFG 寄存器的位域定义如下：

| 7        | 6     | 5     | 4     | 3      | 2        | 1        | 0        |

|----------|-------|-------|-------|--------|----------|----------|----------|

| Reserved | VP2EN | VP1EN | VP0EN | I2C0EN | MCBSP1EN | MCBSP0EN | MCASP0EN |

R-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-1 R/W-1 R/W-0

其中将相应的位置“1”，则使能该功能，置“0”，则禁止该功能。其操作方法参看 **TMS320DM642 Video/Imaging Fixed-Point Digital Signal Processor**（文献号 SPRS200）。这些功能模块的配置情况如下图所示：

SEED-VPM642 模板上，将 PERCFG 设置为 0x79，使能 3 个视频口和 McASP 口，具体配置如下：

- VP2:** 配置为 VP2A 和 VP2B 二个 8 位 BT.656 视频输入口，用于分别接口 2 路 BT.656 标准数字视频输入（分别对应第 3、第 4 路视频解码器的输出）；

- VP1:** 配置为 VP1A + McASP 数据口；

- VP1A 配置为 8 位 BT.656 视频输入口，用于接口 1 路 BT.656 标准数字视频输入（对应第 2 路视频解码器的输出）；

- McASP 数据口用于接口 4 路数字立体声音频输入 / 输出（对应第 1~4 路立体声音频 Codec 的数据口）。

- VP0: 配置为 VP0A + McASP 控制口。

- VP0A 配置为 8 位 BT.656 视频输入或输出口，用于接口 1 路 BT.656 标准数字视频输入或输出（对应第 1 路视频解码器的输出或对应视频编码器的输入）。

- McASP 控制口用于为 4 路数字立体声音频提供控制信号。

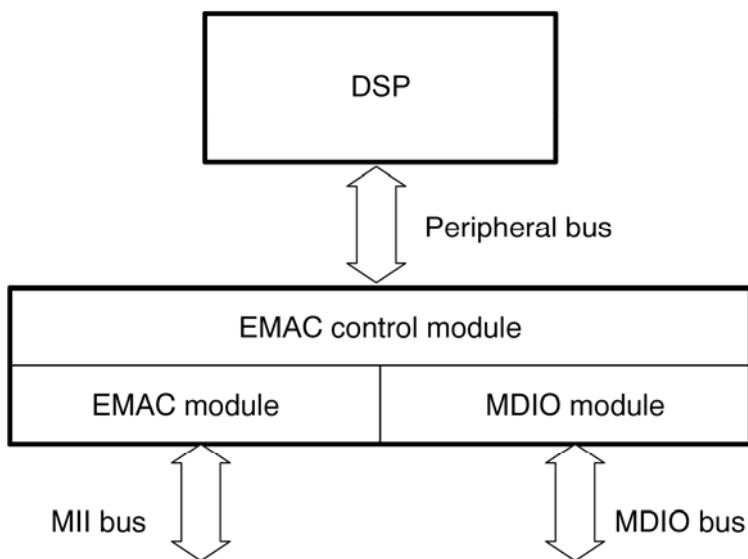

## 2.4 PCI、HPI和网络接口（EMAC与MDIO）

TMS320DM642 支持多种外部接口：PCI 接口、HPI 接口和以太网 MAC 接口，这些接口信号复用相同的引脚，它们的功能选择和配置是在上电复位时通过检测 TMS320DM642 上的特殊引脚（PCI\_EN、MAC\_EN、HD5、PCI\_EEAI）的状态来实现的，具体情况如下表所示：

PCI\_EN, HD5, and MAC\_EN Peripheral Selection (HPI, GP0[15:9], PCI, EMAC, and MDIO)

| PERIPHERAL SELECTION† |                   |              |                 | PERIPHERALS SELECTED |                |            |                               |               |           |

|-----------------------|-------------------|--------------|-----------------|----------------------|----------------|------------|-------------------------------|---------------|-----------|

| PCI_EN Pin [E2]       | PCI_EEAI Pin [L5] | HD5 Pin [Y1] | MAC_EN Pin [C5] | HPI Data Lower       | HPI Data Upper | 32-Bit PCI | EEPROM (Auto-Init)            | EMAC and MDIO | GP0[15:9] |

| 0                     | 0                 | 0            | 0               | √                    | Hi-Z           | Disabled   | N/A                           | Disabled      | √         |

| 0                     | 0                 | 0            | 1               | √                    | Hi-Z           | Disabled   | N/A                           | √             | √         |

| 0                     | 0                 | 1            | 0               | √                    | √              | Disabled   | N/A                           | Disabled      | √         |

| 0                     | 0                 | 1            | 1               | Disabled             |                | Disabled   | N/A                           | √             | √         |

| 1                     | 1                 | X            | X               | Disabled             |                | √          | Enabled (via External EEPROM) | Disabled      | Disabled  |

| 1                     | 0                 | X            | X               | Disabled             |                | √          | Disabled (default values)     | Disabled      | Disabled  |

- PCI\_EN 引脚： 内部下拉，PCI 接口使能。

- PCI\_EEAI 引脚： 内部下拉，使能通过外部 EEPROM 对 PCI 进行初始化。

- HD5 引脚： 内部既不上拉，也不下拉。通过外部上拉或下拉来选择 HPI16 / HPI32。

- MAC\_EN 引脚： 内部下拉，EMAC 和 MDIO 接口使能。

- PCI66 引脚： 内部下拉，决定 PCI 总线工作在 66MHz 频率下还是 PCI 工作在 33MHz 频率下。

SEED-VPM642 模板设计成根据模板安装的情况自动配置接口类型，可以自动配置成下列 3 种接口中的一种：

- 32-位 PCI 接口

- 32-位 HPI 接口

- 16-位 HPI 接口 + 以太网接口

所以，SEED-VPM642 模板既可当作 PC 机的 PCI 插卡来使用（可多板同时使用）；也可当作一个 32-位 HPI 接口设备来使用（也可多板同时使用）；也可独立使用，通过以太网接口实现远程通讯。

注：当用作 32-位 HPI 接口时，应将 PCI 连接器 J14 的 B10 接+3.3V、B3 接 GND。

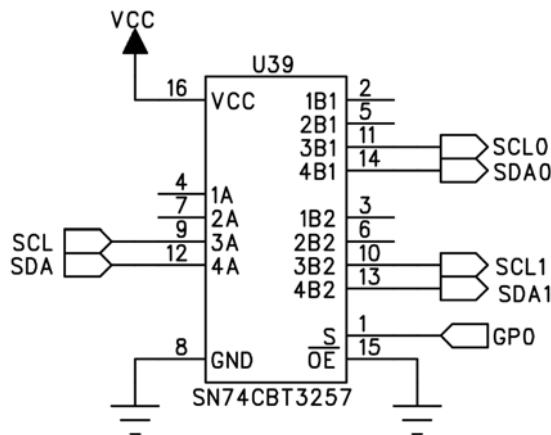

## 2.5 IIC

TMS320DM642 上集成有一条 IIC 总线，'DM642 为此 IIC 总线的主设备。SEED-VPM642 模板上用此 IIC 总线连接了下列从设备：

- 4 路视频解码器 TVP5150PBS 的控制口

- 1 路视频编码器 SAA7121H 的控制口

- 4 路音频编解码器 TLV320AIC23B 的控制口

- 1 路实时时钟 RTC

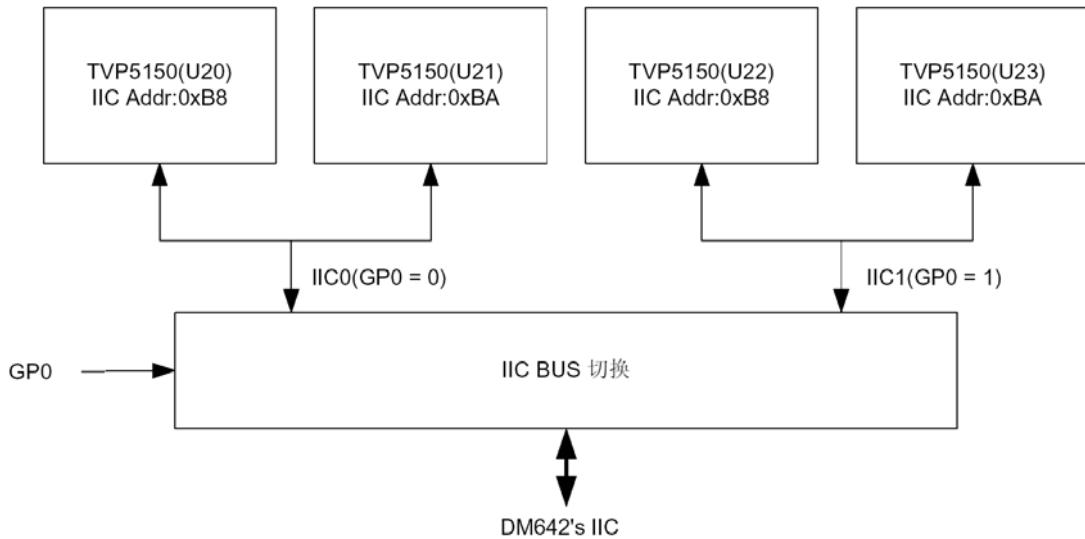

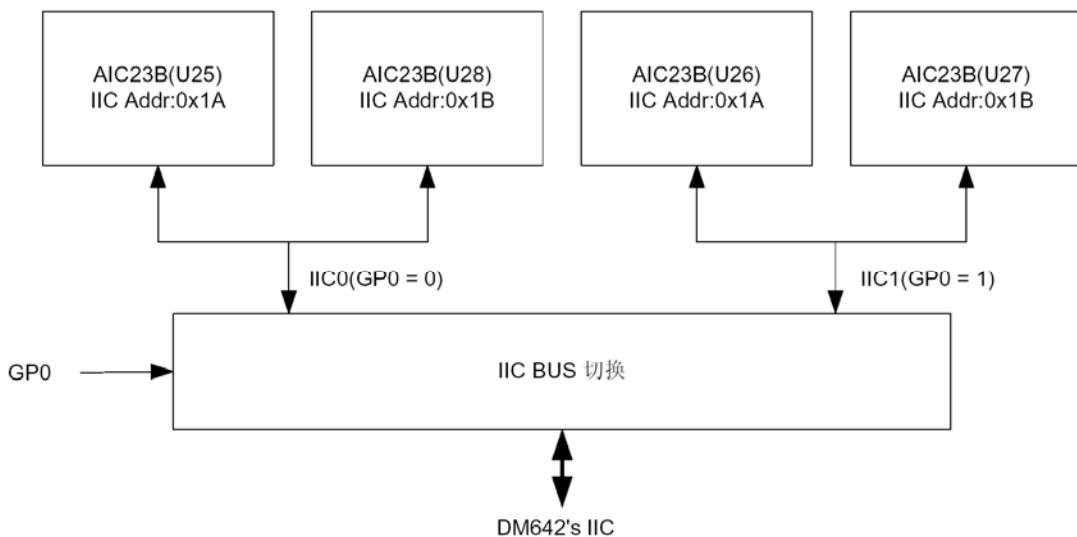

每个 IIC 总线的从设备均对应一个从设备地址，IIC 总线以此从设备地址来区分所访问的是哪个从设备。TVP5150PBS 与 TLV320AIC23B 均只能配置为 2 个不同的从设备地址，所以一条 IIC 总线中是不能同时连接 4 个 TVP5150PBS 或 TLV320AIC23B 的。SEED-VPM642 模板上，将 IIC 总线作总线切换，分为 IIC 1 与 IIC 0，如下图所示：

IIC 0 总线上连接：

- 第 1 路和第 2 路视频解码器 TVP5150PBS 的控制口

- 第 1 路和第 2 路音频编解码器 TLV320AIC23B 的控制口

IIC 1 总线上连接：

- 第 3 路和第 4 路视频解码器 TVP5150PBS 的控制口

- 视频编码器 SAA7121H 的控制口

- 第 3 路和第 4 路音频编解码器 TLV320AIC23B 的控制口

- 实时时钟 RTC

IIC 的总线切换由'DM642 的 GP0[0]口来控制。对 IIC 总线各从设备的具体操作说明详见相关从设备的章节。

## 2.6 系统时钟

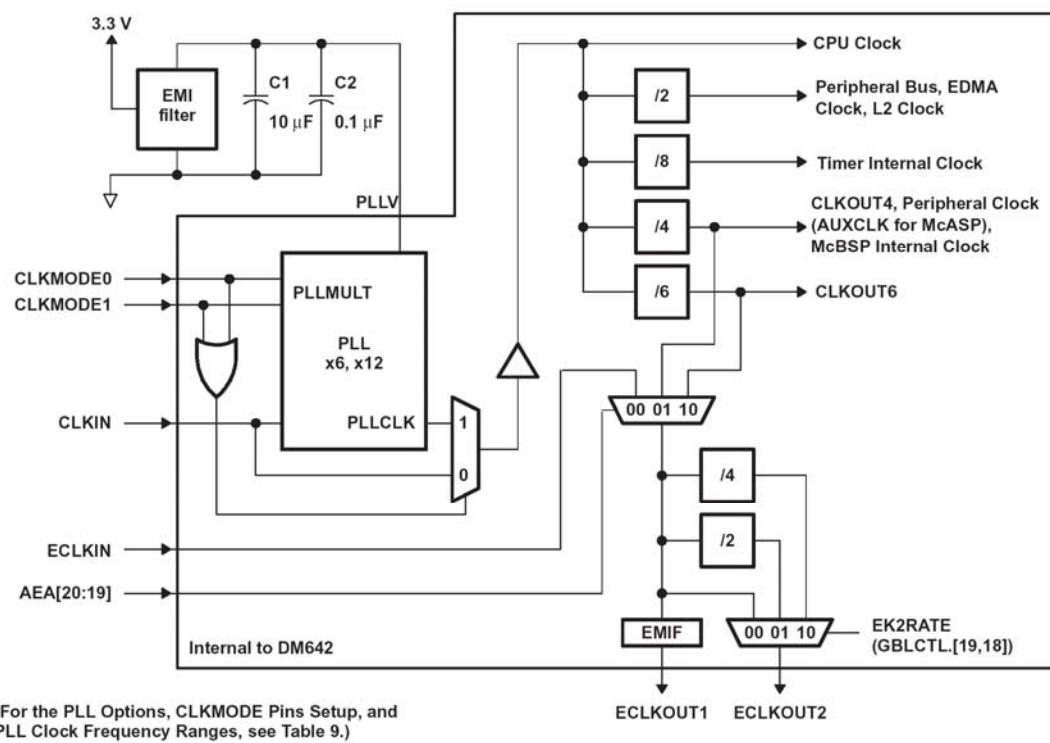

TMS320DM642 片上时钟电路如下图所示：

时钟电路由 PLL、分频器和多路切换器组成，给'DM642 的 CPU 内核、EMIF 和片上外设提供时钟。

SEED-VPM642 模板上输入时钟 CLKIN 为 50MHz, CLKMODE[1:0]上拉或下拉为 10, 即片内 PLL 设置为  $\times 12$ , CPU 内核频率为  $50 \times 12 = 600\text{MHz}$ 。ECLKIN 为 133MHz, AEA[20:19]上拉或下拉为 00, 即 EMIF 时钟 ECLKOUT1 配置为来自 ECLKIN, 为 133MHz。而片上外设总线、EDMA 传输和 L2 存储器的工作频率为 CPU 内核频率的 1/2, 即 300MHz; 片上定时器的工作频率为 CPU 内核时钟频率的 1/8, 即 75MHz; 片上外设 McASP 和 McBSP 的工作频率为 CPU 内核时钟频率的 1/4, 即 150MHz。

## 2.7 定时器

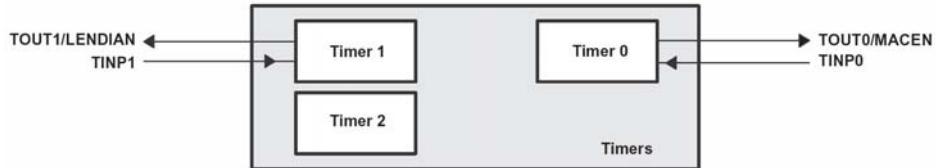

TMS320DM642 片上有三个 32-位的定时器，其功能框图如下图所示：

SEED-VPM642 模板上没有使用'DM642 的定时器硬件资源，这 3 个定时器可供用户软件编程使用。需要注意的是 Timer1 与 Timer0 的输出 TOUT1 与 TOUT2 与 TMS320DM642 的两个运行状态 LENDIAN 与 MACEN 复用管脚。在 SEED-VPM642 模板上将'DM642 配置为 Little Endian，即已将 TOUT1/LENDIAN 引脚上拉；而以太网接口是根据 SEED-VPM642 模板的安装情况自动配置的，所以 TOUT/MACEN 引脚将会根据安装情况自动上拉或下拉。

## 2.8 McBSP 和 VIC

在 SEED-VPM642，模板上未使用这 2 个外设的硬件资源。

## 2.9 复位与中断

TMS320DM642 除了片上外设产生的中断请求以外，还有 5 个外部中断引脚  $\overline{\text{INT}[7:4]}$  和  $\overline{\text{NMI}}$ 。其中断时序如下图所示：

这些信号在 SEED-VPM642 板上均已上拉。

由上图可以看出 TMS320DM642 是以沿方式触发中断的，其中低电平（即 1）最少保持 128ns，而高电平（即 2）亦最少要保持 128ns。

SEED-VPM642 模板上有下列多个中断源：

- INTA、INTB: UART 通道 A 和 B 产生的中断；

- RTCINT: 实时时钟产生的中断；

- ATAINT: 硬盘接口产生的中断；

- ESAMINT:** ESAM 模块产生的中断;

这些中断源与 TMS320DM642 的外部中断引脚的对应关系如下所示:

- NMI:** 系统未使用。

- INT4:** 对应 ESAM 模块的中断 ESAMINT。

- INT5:** 对应 UART 模块的中断 INTA 与 INTB。

- INT6:** 对应 ATA 模块的中断 ATAINT。

- INT7:** 对应 RTC 模块的中断 RTCINT。

SEED-VPM642 模板上有下列 4 个复位源，其中任何一个复位有效，将导致整个系统复位：

- 上电复位:** 系统上电后自动产生 200ms 复位信号，使系统从初始状态开始执行

- 手动复位:** 按动复位按钮时，产生复位信号，主要用于系统调试

- 看门狗复位:** 当看门狗使能时，系统如果没有在规定的时间间隔内（最小值为 0.9s、典型值为 1.6s、最大值为 2.5s）对看门狗电路进行刷新，则产生复位信号，使系统重新开始，提高系统抗干扰能力。看门狗电路在上电复位后，处于禁止状态，看门狗电路通过将系统控制寄存器 0 (WATCHDOG) 中的 WDEN 控制位置 1 来使能。看门狗电路使能后，通过对看门狗刷新口 (WDUP) 作写操作来刷新看门狗。

- 电源监测复位:** 监测+3.3V 主电源，如果其下跌至 2.93V (典型值)，产生复位信号，提高系统的可靠性。

TMS320DM642 复位时的一些关键引脚的设置决定了 DM642 工作状态选择或配置，SEED-VPM642 模板上这些关键引脚的默认配置总结如下：

- AEA[22:21]=11B:** 用于选择上电自举方式，为 8-位的 Flash 自举方式。

- CLKMODE[1:0]=10B:** CPU 的时钟为 CLKIN×12；

- AEA[20:19]=00B:** ECLKOUT1 为 EMIF 外部时钟输入 AECLKIN；

- TOUT1/LENDIAN 上拉:** 系统工作在 Little Endian；

## 2.10 上电自举方式的配置

TMS320DM642 有多种上电自举方式，通过复位时 AEA[22:21]引脚的状态来选择，引脚状态与上电自举方式的对应关系如下所示：

- 00** 无自举模式。

- 01** HPI 或 PCI 自举。

- 10** 此设置被禁止。

□ 11

EMIFA 通过 8-位的 Flash 自举。

在 SEED-VPM642 模板上实现了以上的 Flash、HPI 或 PCI 三种自举方式，默认方式为 EMIFA 通过 8-位的 Flash 自举。

## 2.11 TMS320DM642 的输入与输出

TMS320DM642 中共有 16 个通用的输入与输出 GP0[15:00]。但除了 GP0[0]以外，其它的 GP0 管脚均与其它的功能复用。列表如下：

- GP0[15:9]与 PCI 功能的控制引脚复用；

- GP0[8]与 PCI66 和 VDAC 功能复用；

- GP0[7:4]与外部中断 INT[7:4]功能复用；

- GP0[3]与 PCIEAI 功能复用；

- GP0[2]与 CLKOUT6 功能复用；

- GP0[1]与 CLKOUT4 功能复用。

在 SEED-VPM642 模板上，GP0[3]与 GP0[8]用来做指示灯使用，而 GP0[0]用来控制 IIC 总线的切换。

## 2.12 JTAG

TMS320DM642 的仿真接口为 JTAG 形式，它能与各种形式的 JTAG 仿真器相连接，实现对 DM642 的仿真与调试。

注：当使用者使用 SEED 的并口仿真器时，应为仿真器接+5V 电源。

## 第 3 章

# 视频接口

在 SEED-VPM642 系统中共实现了四通路的视频输入接口与一个通路的视频输出接口，四通路的视频输入接口可以同时完成对四路视频信号的采集。视频解码电路选用 TVP5150PBS，视频编码电路选用 SAA7121H。视频的解码与编码均支持 NTSC 和 PAL 制式。

### 3.1 TMS320DM642 的VP口

TMS320DM642 上集成了三个 Video Port (简称 VP) 口，每个视频口由 20-位数据线、2 个时钟信号 VPxCLK0 (输入) 和 VPxCLK1 (输入 / 输出)、3 个控制信号 VPxCTL0、VPxCTL1 和 VPxCTL2 组成。时钟信号作为视频源的时钟信号输入 / 输出，控制信号作为视频源的同步信号输入 / 输出 (行同步、帧同步、场标志，视频采集使能等)。

每个视频口被分为上 (B) 、下 (A) 2 个通道，VP0 的 A 通道与 McBSP0 复用，VP1 的 A 通道与 McBSP1 复用，VP0 和 VP1 的 B 通道与 McASP 复用，VP2 则为单功能引脚。

每个视频口可被配置为视频输入口或视频输出口，但是上 (B) 、下 (A) 2 个通道只能同时被配置为输入口，或同时被配置为输出口，不能一个通道配置为输入口，另一个通道配置为输出口。

VP0 和 VP1 可配置为单通道视频输入 / 输出 + McBSPx 或 McASP 口，VP2 可配置为双通道视频输入 / 输出口。在 SEED-VPM642 中 VP0 和 VP1 被配置成为单通道视频输入 / 输出口 + McASP 口，VP2 配置成为双通路的视频输入口。VP0 A 口接口第 1 通道视频输入或视频输出、VP1 A 口接口第 2 通道视频输入、VP2 A 口接口第 3 通道视频输入、VP2 B 口接口第 4 通道视频输入。

当 VP0 与 VP1 配置为单通道视频输入口时，VPxCLK0 作为视频源的输入时钟，VPxCLK1 未用。而 VPxCTL0、VPxCTL1 和 VPxCTL2 则分别作为视频源的 CAPEN/AVID/HSYNC、VBLNK/VSYNC、FID 输入同步信号。

当 VP2 配置为双通道视频输入口时，VPxCLK0 和 VPxCLK1 分别作为 2 个视频源的输入时钟，而 VPxCTL0 和 VPxCTL1 分别作为 2 个视频源的采集使能信号，VPxCTL2 未用。

双通道 BT.656 视频输入时，视频数据的行 / 场同步，通过各自的 BT.656 视频流中的时基信号来控制。BT.656 视频数据流的采样受 CAPEN 信号控制或受 BT.656 视频数据流

中的时基码控制。当 CAPEN 信号无效或在 EAV 和 SAV 时基码之间将不对视频数据流进行采样。

BT.656 视频数据流采集的起始、水平同步、垂直同步等，受输入信号 CAPEN 和视频通道控制寄存器 VCxCTL ( $x = A, B$ ) 中的 VCEN、EXC、HRST、VRST、FLDD 等控制位组合控制。

当配置为单通道视频输出口时，VPxCLK1 作为视频源输出时钟，VPxCLK0 作为输入时钟。而 VPxCTL0、VPxCTL1 和 VPxCTL2 分别作为输出视频的 HSYNC/HBLNK/AVID/FLD、VSYNC/VBLNK/CSYNC/FLD、CBLKN/FLD。

DM642 的视频口作为 8-位视频口时，其使用 10-位数据总线中的高 8-位，即 VPxD[9:2] 或 VPxD[19:12]。

更加详细的说明，参看文档 **TMS320C64x DSP Video Port/VCXO Interpolated Control (VIC) Port Reference Guide** (文献号 SPRU629)。

## 3.2 TVP5150PBS

TVP5150PBS 是一款高性能视频解码器，可将 NTSC、PAL 视频信号转换成数字色差信号 (YUV4:2:2)，支持两个复合视频或一个 S 端子输入。输出格式为 ITU-R BT.656，并支持 Macrovision™ 复制保护以及高级的 VBI 功能。不仅如此，TVP5150 还具备了封装小（32 脚的 TQFP）、功耗小的特点 (<150mW)，因此，非常适用于便携、批量大、高质量和高性能的视频产品。

详细的说明用户参阅文档 **TVP5150PBS**。

### 3.2.1 TVP5150 视频输入

视频解码器 TVP5150PBS 可以接受 2 路复合视频信号 (CVBS) 输入和 1 路超级视频信号 (S-Video = Super-Video, Y/C) 输入。输入电路如下图所示：

视频解码器 TVP5150PBS 视频信号输入范围为  $0.75V_{PP}$ , 而外部视频信号输入范围一般为  $1V_{PP}$ , 所以外部视频输入与 TVP5150APBS 视频输入之间串接  $18\Omega$  和  $56\Omega$  到地分压电阻网络, 以达到 TVP51500PBS 所需的输入电平。使用前一定要将视频信号输入的范围调整到  $1V_{PP}$ 。

外部视频信号输入可以采用复合视频和超级视频的形式, 其接法如下:

- 当使用复合视频信号输入时, CVBS/Y 作为复合视频输入, CVBS/C 接模拟地;

- 当使用超级视频信号时, CVBS/Y 作为亮度分量 Y 和 CVBS/C 作为色度分量 C。

在随 **SEED-VPM642** 系统自带的视频输入连接器中采用复合视频信号输入。

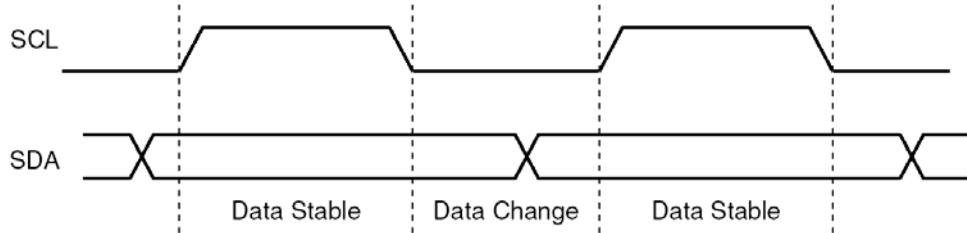

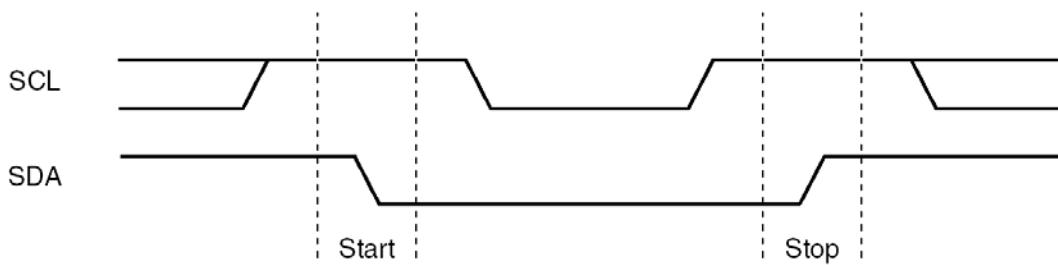

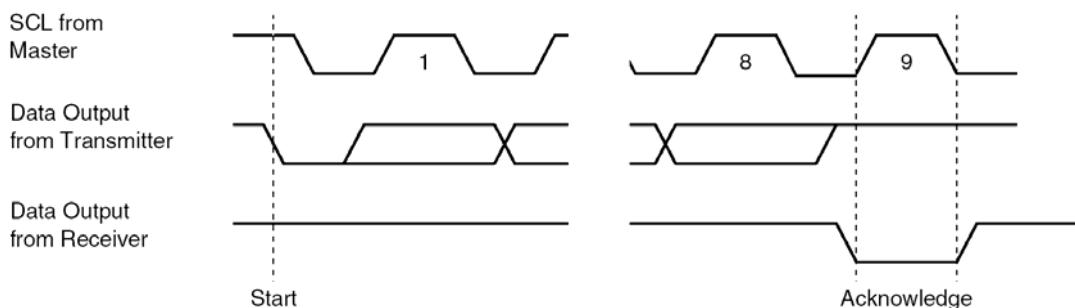

### 3.2.2 TVP5150 的配置

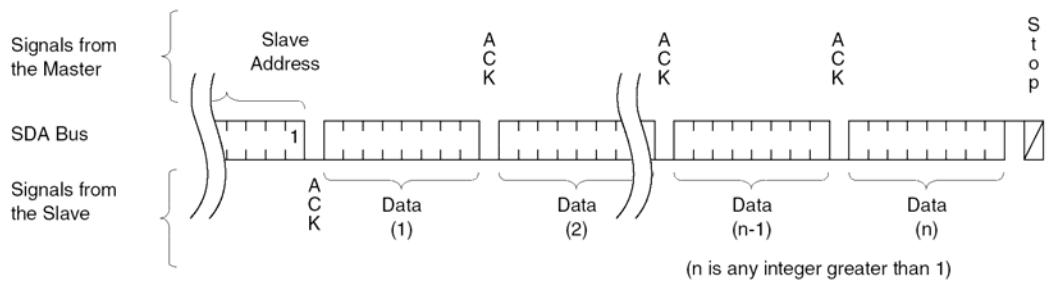

TVP5150PBS 的配置是通过标准的 IIC 总线来完成的。TVP5150PBS 的 IIC 标准总线是由串行数据输入 / 输出线 (SDA) 和时钟输入 / 输出线 (SCL) 组成的。TVP5150 只做为从设备, 不能做为主设备。IIC 总线的数据传送速率最高可达 400Kbits/s。在 SEED-VPM642 中我们采用 100kbits/s 的速率进行对 TVP5150 的配置。

详细的寄存器说明用户参阅文档 **TVP5150PBS** 中关于这部分的描述。

#### 3.2.2.1 TVP5150 配置的写

TMS320DM642 做为一个 IIC 总线的主设备初始化 TVP5150 配置的写操作时, 按如下程式进行:

- DSP 产生一个起始条件;

- DSP 发出一个 TVP5150 的地址 (0xBA 或 0xB8), 并标明写操作, 等待 TVP5150 响应;

- 接收到 TVP5150 的响应后, DSP 发出要配置寄存器的地址, 等待 TVP5150 响应;

- 接收到 TVP5150 的响应后, 发送要配置的数据, 等待 TVP5150 响应;

- 接收到 TVP5150 的响应后, 发送停止位, 结束一次配置。

整个写的过程列表如下:

|                                                  |                                         |

|--------------------------------------------------|-----------------------------------------|

| <b>Step 1</b>                                    | <b>0</b>                                |

| I <sup>2</sup> C Start (master)                  | S                                       |

| <b>Step 2</b>                                    | <b>7 6 5 4 3 2 1 0</b>                  |

| I <sup>2</sup> C General address (master)        | 1 0 1 1 1 0 X 0                         |

| <b>Step 3</b>                                    | <b>9</b>                                |

| I <sup>2</sup> C Acknowledge (slave)             | A                                       |

| <b>Step 4</b>                                    | <b>7 6 5 4 3 2 1 0</b>                  |

| I <sup>2</sup> C Write register address (master) | addr addr addr addr addr addr addr addr |

| <b>Step 5</b>                                    | <b>9</b>                                |

| I <sup>2</sup> C Acknowledge (slave)             | A                                       |

| <b>Step 6</b>                                    | <b>7 6 5 4 3 2 1 0</b>                  |

| I <sup>2</sup> C Write data (master)             | Data Data Data Data Data Data Data Data |

| <b>Step 7†</b>                                   | <b>9</b>                                |

| I <sup>2</sup> C Acknowledge (slave)             | A                                       |

| <b>Step 8</b>                                    | <b>0</b>                                |

| I <sup>2</sup> C Stop (master)                   | P                                       |

† Repeat steps 6 and 7 until all data have been written.

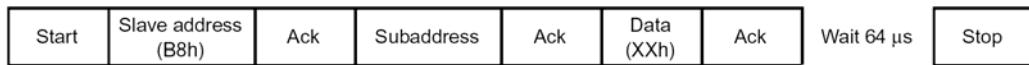

在进行配置寄存器（0x00~8F）时，TVP5150 需要一段延时来完成当前的配置，此时 TVP5150 保持 SCL 为低，通知 DSP 配置尚未完成。在编程时，一般不用查询当前的 SCL 的状态，而是延时配置需要的最大延时 64us。示例如下：

### 3.2.2.2 TVP5150 状态的读

当 TMS320DM642 要读取当前 TVP5150 的状态时，需通过 IIC 总线启动对 TVP5150 的寄存器的一个读操作。读操作分两部分进行，说明如下：

- 由 DSP 向 TVP5150 写入要读取的寄存器的地址；

- 由 DSP 向 TVP5150 发送读取寄存器数据的命令。

整个过程列表如下：

## Read Phase 1

|                                                 |          |      |      |      |      |      |      |      |

|-------------------------------------------------|----------|------|------|------|------|------|------|------|

| <b>Step 1</b>                                   | <b>0</b> |      |      |      |      |      |      |      |

| I <sup>2</sup> C Start (master)                 | S        |      |      |      |      |      |      |      |

| <b>Step 2</b>                                   | 7        | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C General address (master)       | 1        | 0    | 1    | 1    | 1    | 0    | X    | 0    |

| <b>Step 3</b>                                   | <b>9</b> |      |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (slave)            | A        |      |      |      |      |      |      |      |

| <b>Step 4</b>                                   | 7        | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Read register address (master) | addr     | addr | addr | addr | addr | addr | addr | addr |

| <b>Step 5</b>                                   | <b>9</b> |      |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (slave)            | A        |      |      |      |      |      |      |      |

| <b>Step 6</b>                                   | <b>0</b> |      |      |      |      |      |      |      |

| I <sup>2</sup> C Stop (master)                  | P        |      |      |      |      |      |      |      |

## Read Phase 2

|                                           |          |      |      |      |      |      |      |      |

|-------------------------------------------|----------|------|------|------|------|------|------|------|

| <b>Step 7</b>                             | <b>0</b> |      |      |      |      |      |      |      |

| I <sup>2</sup> C Start (master)           | S        |      |      |      |      |      |      |      |

| <b>Step 8</b>                             | 7        | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C General address (master) | 1        | 0    | 1    | 1    | 1    | 0    | X    | 1    |

| <b>Step 9</b>                             | <b>9</b> |      |      |      |      |      |      |      |

| I <sup>2</sup> C Acknowledge (slave)      | A        |      |      |      |      |      |      |      |

| <b>Step 10</b>                            | 7        | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

| I <sup>2</sup> C Read data (slave)        | Data     | Data | Data | Data | Data | Data | Data | Data |

| <b>Step 11†</b>                           | <b>9</b> |      |      |      |      |      |      |      |

| I <sup>2</sup> C Not Acknowledge (master) | Ā        |      |      |      |      |      |      |      |

| <b>Step 12</b>                            | <b>0</b> |      |      |      |      |      |      |      |

| I <sup>2</sup> C Stop (master)            | P        |      |      |      |      |      |      |      |

† Repeat steps 10 and 11 for all bytes read. Master does not acknowledge the last read data received.

### 3.2.2.3 DSP与TVP5150 配置连接

TVP5150 作为 IIC 总线的从设备，最多可配置为 2 个不同的从设备地址，一条 IIC 总线只能同时访问 2 个 TVP5150 配置口，而 SEED-VPM642 模板上有 4 个 TVP5150，所以用总线切换的方法将 IIC 分成二组，如下图所示：

由上图可见，'DM642 用通用 I/O 口 GP0[0]来控制 IIC 总线的切换，GP0[0]为“0”时，选通第 1 和第 2 通道 TVP5150，而 GP0[0]为“1”时，则选通第 3 和第 4 通道 TVP5150。每个通道的 TVP5150 的 IIC 总线从设备地址如图所示。

### 3.2.3 DSP与TVP5150 数字视频流的连接

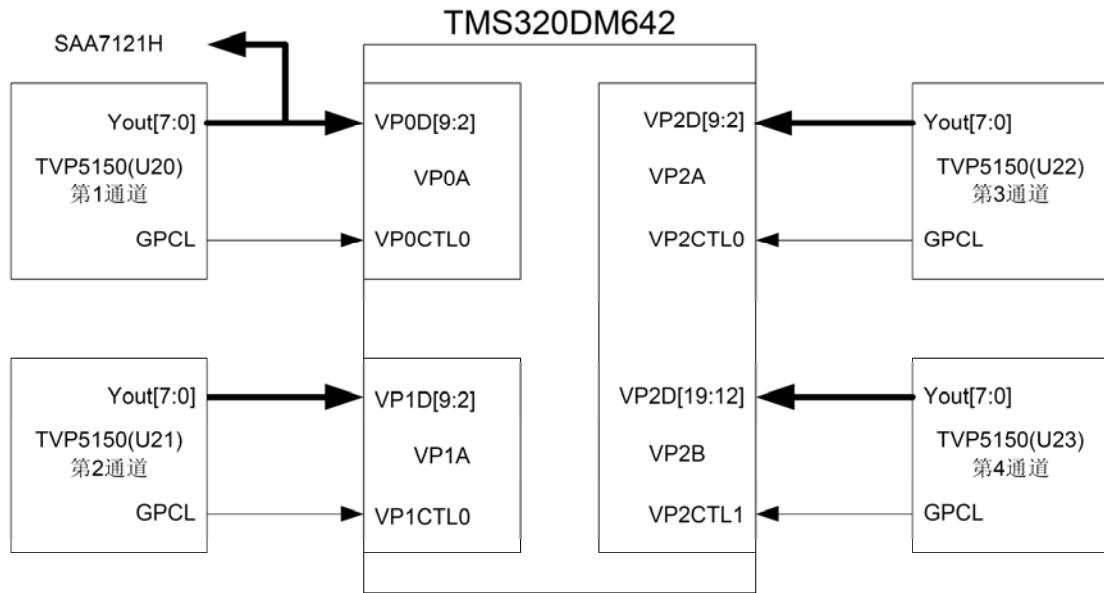

TMS320DM642 支持 BT.656 格式的视频数据流的输入格式，能与 TVP5150 的视频数据流进行无缝连接。TMS320DM642 共有三个 VP 端口，最多可以支持 6 路 8 位 BT.656 数字视频接口。在 SEED-VM642 模板上用其中的四路来支持视频输入，余下的 2 路选择 McASP 功能，实现四路的音频输入 / 输出（关于音频部分详见第四章）。VP 端口具体的配置如下：

- VP0 的 A 通道与第 1 通路的 TVP5150 (U20) 相连接；

注：此 A 通道同时与 **SAA7121H** 相连接（参看有关 **SAA7121H** 的说明）。

- VP1 的 A 通道与第 2 通路的 TVP5150 (U21) 相连接；

注：VP0 的 B 通道与 VP1 的 B 通道合起来做 **McASP** 功能（参看第四章）。

- VP2 的 A 部与第 3 通路的 TVP5150 (U22) 相连接；

- VP2 的 B 部与第 4 通路的 TVP5150 (U23) 相连接；

其原理框图如下所示：

由上图可见，TVP5150 的 GPCL 引脚用来作 VP 口的 CAPEN，来控制视频数据流的采集。当 GPCL 为“1”时，允许 VP 口对输入的视频数据流进行采集；GPCL 为“0”时，则禁止 VP 口对输入的视频数据流进行采集。

GPCL 状态可以通过对 TVP5150 的 Miscellaneous Control Register 寄存器（地址为 0x3）中的 GPCL 位进行设置来置“1”或清“0”。

除了 VP0A 外，其余的 VP 端口均为单一的视频输入的功能。即在使用时将 VP 口设置成为 Capture 模式。VP0A 在 SEED-VPM642 系统中，还与视频输出 SAA7121H 相连接，因而 VP0A 需要工作在 Capture 与 Display 两种工作模式。关于 VP0A 如何实现这两种工作模式的切换，将在 SAA7121H 的说明中作详细的描述。

### 3.3 SAA7121H

视频编码器 SAA7121H 支持 PAL 与 NTSC 格式的视频编码。其输入支持 BT.656 格式的数字视频。SAA7121H 有 1 路复合视频 (CVBS) 输出和 1 路超级视频 (S-Video, Y/C) 输出。在 SEED-VPM642 模板上复合视频 (CVBS) 输出由连接器 J2 引出，超级视频输出由连接器 J7 (S 端子) 引出。其视频信号输出电路如下图所示：

### 3.3.1 SAA7121H的配置

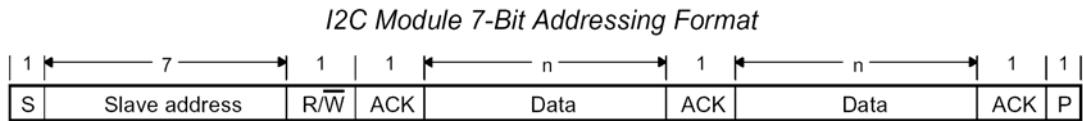

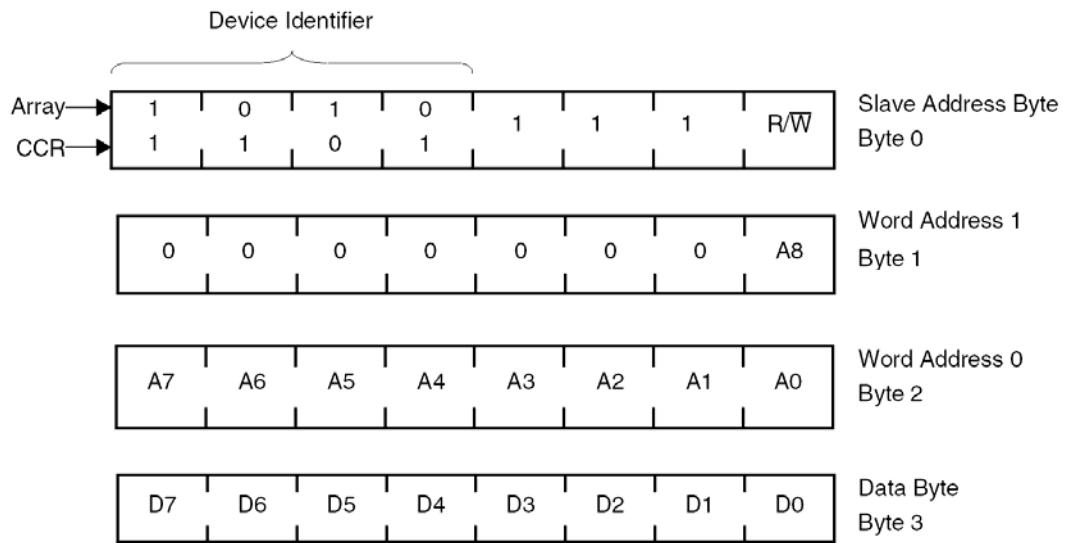

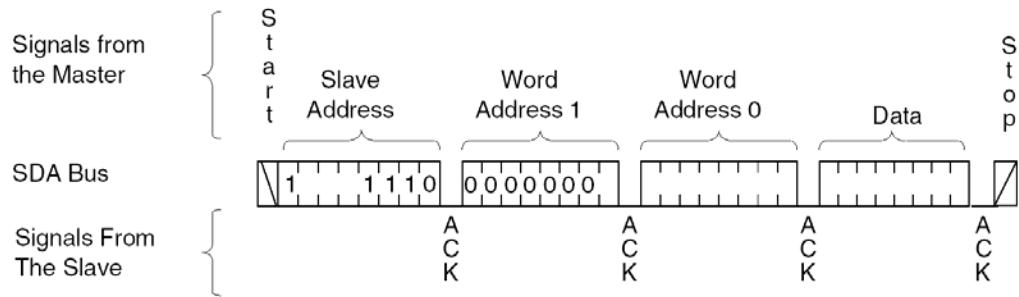

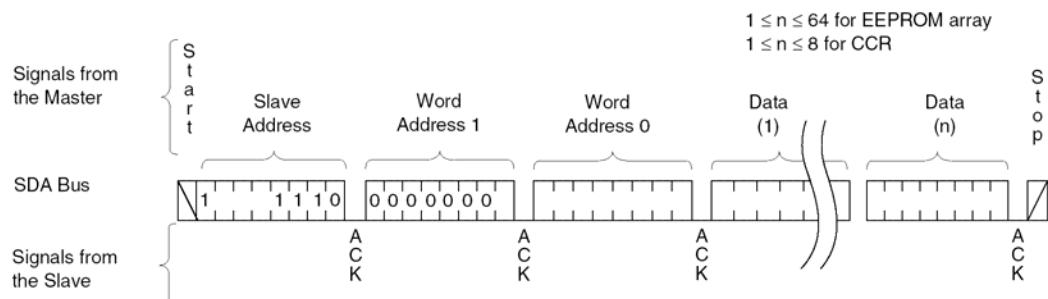

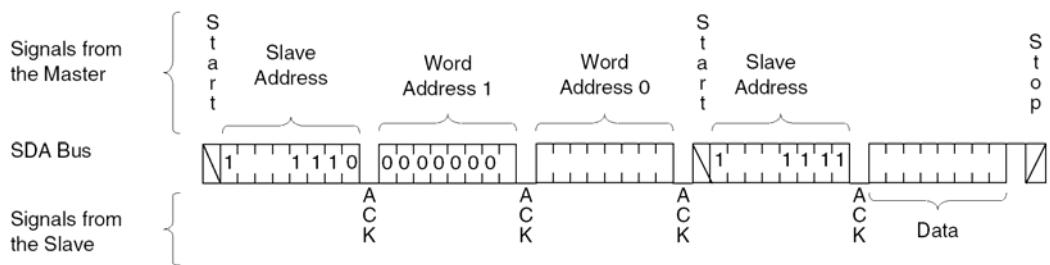

SAA7121H 的配置是通过标准的 IIC 总线来完成的。SAA7121H 的 IIC 总线只支持 7-位地址的格式，并只能做为从设备。它支持寄存器的地址自动加一的功能。其数据交换的最高速度为 400kbit/s。除了可读的状态寄存器外，其它的寄存器只写。其读写的数据格式如下图：

每一个 SAA7121H 根据 SA 管脚的状态可以配置 IIC 的地址，说明如下：

- 当 SA 为高时，其地址为 0x8C;

- 当 SA 为低时，其地址为 0x88; 。

SEED-VPM642 模板上将 SAA7121H 的 IIC 从设备地址配置为 0x88，并将其接口到 IIC1（见 3.2.2.3 章节的说明）上。在配置时需按如下步骤进行：

1. GPEN 寄存器的 GP0EN 置“1”使能 GP0[0]; GPDIR 寄存器的 GP0DIR 置“1”将 GP0[0] 配置为输出；GPVAL 寄存器的 GP0VAL 清“0”使 GP0[0] 输出低电平；

2. 按上图格式将 TMS320DM642 的 IIC 设为 7-位格式，并初始化；

3. 进行寄存器的读写。

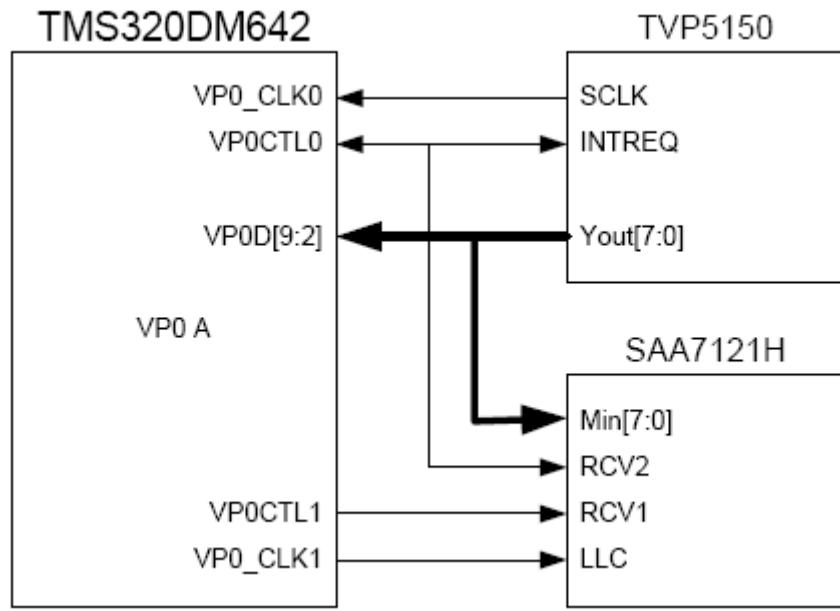

### 3.3.2 DSP与SAA7121H的数据口连接

TMS320DM642 的 VP 口支持 BT.656 格式的数字视频流的显示功能，能与 SAA7121H 的数据口进行无缝连接。在 SEED-VPM642 模板上，四个 VP 口已经均被 TVP5150 所使用，因此，SAA7121H 只能与其中的一 TVP5150 复用一个 VP 端口了，这里我们选择的是 VP0A 端口。TVP5150 (U20)、SAA7121H 与 VP0A 的连接原理如下图：

从原理框图上可以看出，VP0A 即要做视频输入口，也要支持视频输出口，**但这两种工作模式不能同时使用**，下面将这两种情况下做详细说明。

当 VP0A 做为 8-位的 BT.656 视频采集口时，仅需视频数据流串行时钟和采集使能控制信号，串行数据流串行时钟由 TVP5150 的 SCLK，采集使能控制信号则由 TVP5150PBS 的 INTREQ/GPCL/VBLK 引脚配置为通用输出引脚来控制。此时 SAA7121H 不起作用。

当 VP0A 做为 8-位的 BT.656 视频显示口时，SAA7121H 需要 HSYNC（行同步信号）、VSYNC（场同步信号）、LLC（27MHz 的行锁存号）。这三个信号均由 VP0A 进行提供。分别说明如下：

- LCC 信号是由 VPO\_CLK1 提供的，其输入由 TVP5150 (U20) 的 SCLK 输出提供。那 SCLK 既作为视频输入时钟信号，也作为视频输出时钟信号，还作为音频主时钟的锁相输入。所以，为了视频输出和音频采集能正常工作，第 1 路视频输入，必须保证有信号，而且 **SCLK 必须总是配置为输出有效**。

- HSYNC 信号是由 VP0CTL0 提供，连接到 RC2。但此时这个管脚也连接了 TVP5150 的 INTREQ/GPCL/VBLK 引脚，因此，TVP5150 的 **INTREQ/GPCL/VBLK** 引脚配置为输入。（操作寄存器 Miscellaneous Control Register）

- VSYNC 信号是由 VP0CTL1 提供的，连接到 RC1。此管脚不复用。

此时的 VP0D[9:2] 处于输出状态，会与 TVP5150 的 Yout[7:0] 产生总线冲突，因此 TVP5150APBS 的数据总线 YOUT[7:0] 通过杂项控制寄存器 (Miscellaneous Control Register) 的 Bit3 控制位配置为高阻状态。

## 第 4 章

# 音频输入与输出

SEED-VPM642 采用 4 片 TLV320AIC23B 实现 4 路立体声音频的输入 / 输出，TLV320AIC23B 是一种音频 Codec 器件，他的基本功能为：48KHz 带宽、96KHz 采样率，双声道立体声 A/D、D/A，音频输入包括：麦克风输入（提供麦克风偏置输出和前置放大器）和立体声输入（提供可编程放大器），音频输出包括：立体声输出（提供耳机功率放大器，能提供 30mW 输出功率，驱动  $32\Omega$  负载）。

TLC320AIC23B 与微处理器的接口有二个，一个是控制口，用于设置 TLV320AIC23B 的工作参数，另一个是数据口，用于传输 TLV320AIC23B 的 A/D、D/A 数据。在 SEED-VPM642 模板上，使用 DSP 的 IIC 总线进行 TLC320AIC23B 的配置，利用 DSP 的 McASP 与 4 片 TLC320AIC23B 进行数据的交换。

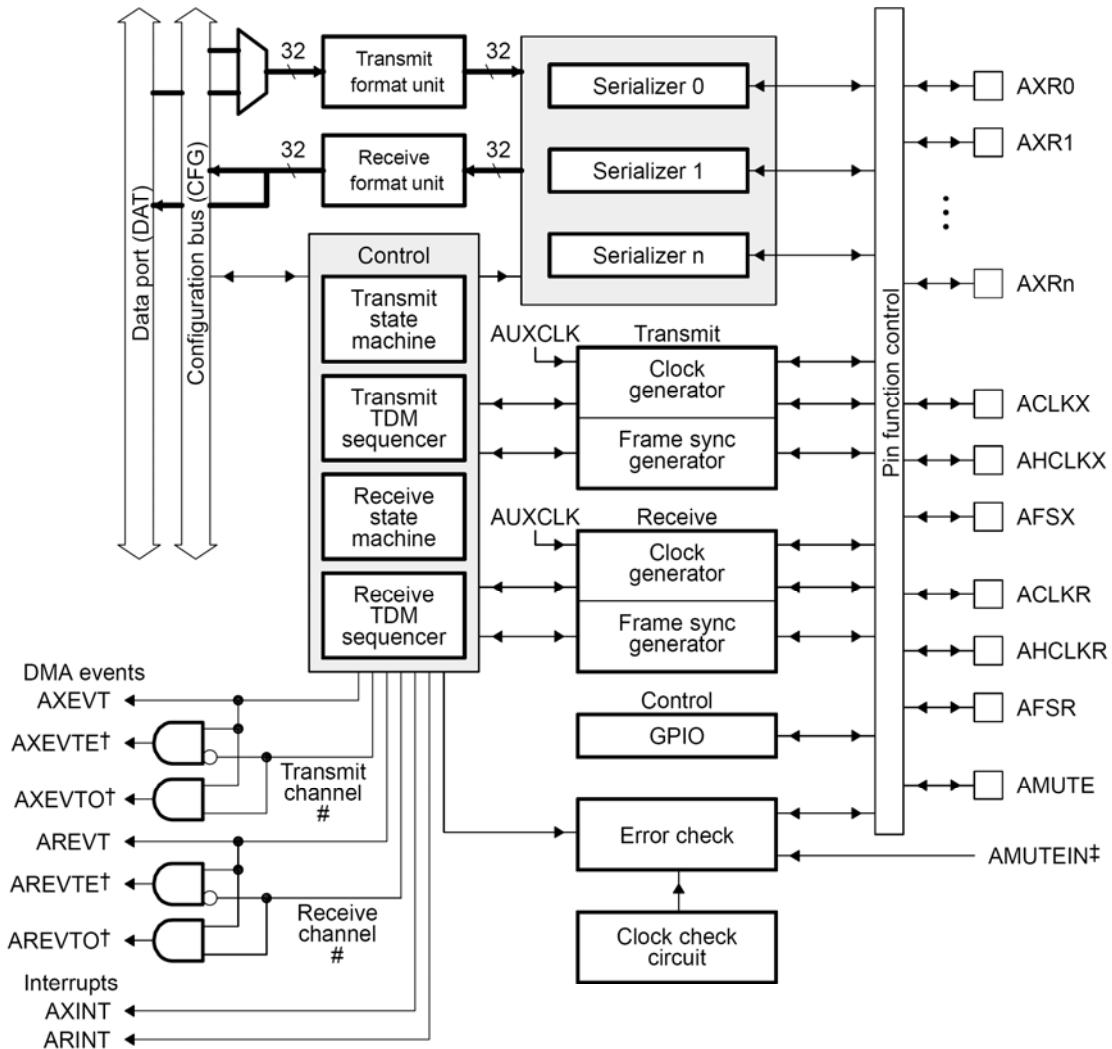

### 4.1 TMS320DM642 的McASP接口

TMS320DM642 的 Multichannel Audio Serial Port (McASP) 主要应用在多通路的音频处理中，McASP 数据的接收与发送两个部分，这两部分可以进行同步操作，也可以完全独立的进行工作。

McASP 主要包括以下几组功能引脚：

- 位时钟：ACLKX, ACLKR

- 帧同步：AFSX, AFSR

- 高频主时钟：AHCLKX, AHCLKR

- 数据的接收与发送：AXR[7:0]

- 静音输入与输出：AMUTEIN, AMUTE

McASP 同步串行通信协议简单说明如下：

- McASP 串行数据流起始时刻称为帧同步事件。帧同步事件由位时钟采样帧同步信号给出。

- McASP 串行数据流长度：串行传输的数据流位数达到设定的长度后，结束本次传输，等下一个帧同步信号达到，再发起另一次串行传输。

- McASP 串行数据流传输速度：即每一个串行位的持续时间，由位时钟决定。

- McASP 帧同步事件与何时采样与输出串行数据位流，即 AFSR (FSX)、ACLKR (CLKX)、AXR[7:0]三者之间的关系。确定 McASP 可支持的外部器件的协议，主要有以下三种：

- I2S 数据格式，及相似的位-流格式；

- 从 2 到 32 通路的 TDM 格式的数据流；

- S/P DIF、IEC60958-1、AES-3 格式。

McASP 的基本框图如下所示：

更加详细的说明请参看文档：**TMS320C6000 DSP Multichannel Audio Serial Port (McASP) Reference Guide**（文献号 SPRU041）。

在 SEED-VPM642 系统中，McASP 将同时接入 4 路音频输入与 4 路音频输出。其协议采用 Burst Frame Sync Mode。

## 4.2 TLV320AIC23B

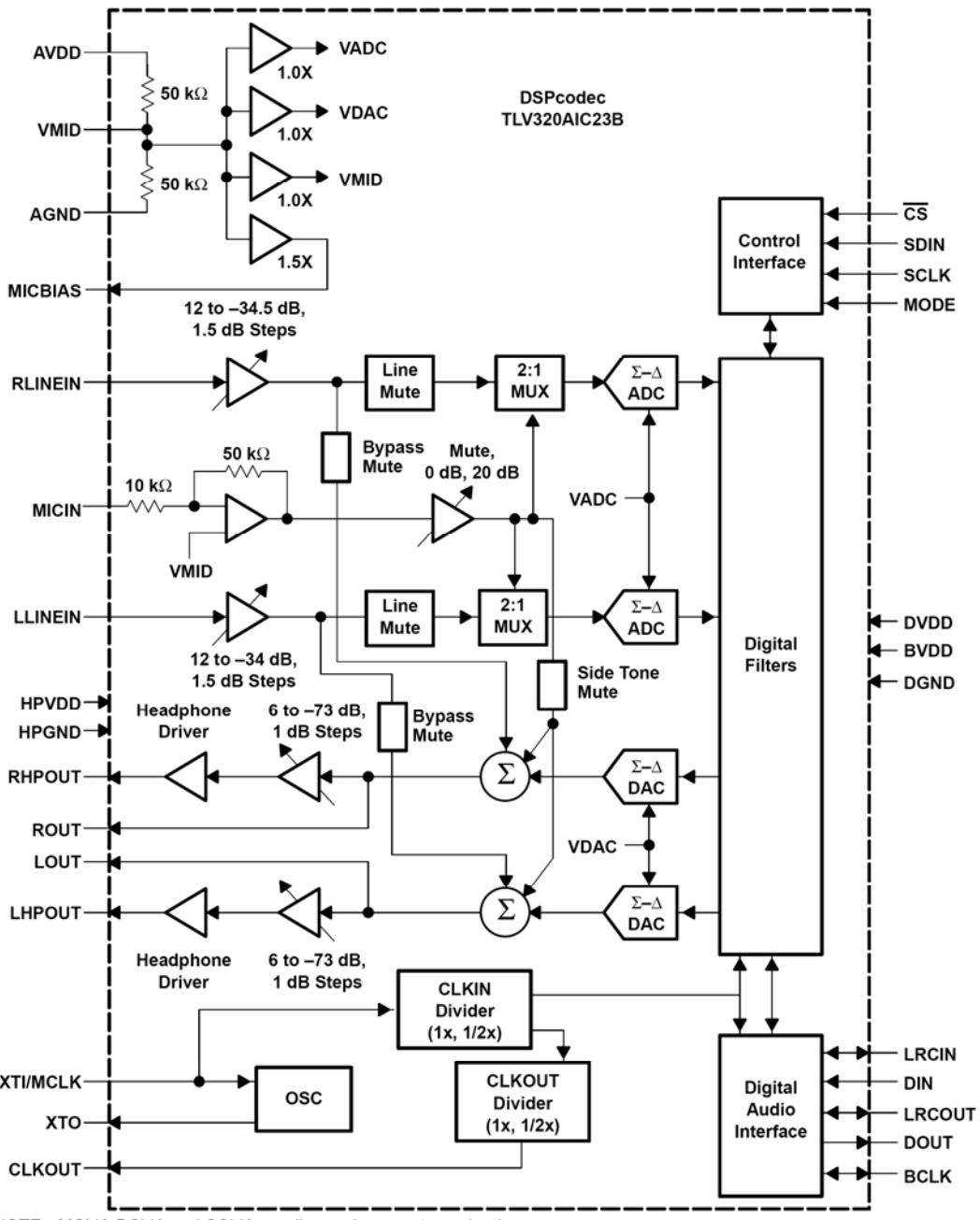

TLV320AIC23B（以下简称 AIC23B）是 TI 推出的一款高性能的立体声音频 Codec 芯片，内置耳机输出放大器，支持 MIC 和 LINE IN 两种输入方式（二选一），并且输入和输出都具有可编程增益调节。AIC23B 的模数转换（ADC）和数模转换（DAC）部件高度集成在芯片内部，采用了先进的 Sigma-delta 过采样技术，可以在 8K 到 96K 采样率范围内提供 16-位、20-位、24-位和 32-位采样，ADC 和 DAC 的信噪比分别可以达到 90dB 和 100dB。同时，AIC23B 还具有很低的能耗，回放模式下功率仅为 23mW，省电模式下更是小于 15uW。AIC23B 的管脚和内部结构框图如下：

## 4.3 TLV320AIC23B与'DM642 的接口

TLV320AIC23B 与微处理器的接口有二个，一个是控制口，用于设置 TLV320AIC23B 的工作参数，另一个是数据口，用于传输 TLV320AIC23B 的 A/D、D/A 数据。SEED-VPM642 模板上将 TMS320DM642 的 McASP 配置成 Burst Frame Sync Mode 方式，与 4 片的 TLV320AIC23B 的数据口接口；使用 IIC 总线与 TLV320AIC23B 的控制口接口。

### 4.3.1 AIC23B的数据口

TLV320AIC23B 的数据口有四种工作方式，分别为：

- Right justified

- Left justified

- IIS Mode

- DSP Mode

其中后两种可以很方便的与 DSP 的 McBSP 串口相连接。下面我们以 DSP Mode 模式来说明数据口的连接。其硬件上的管脚说明如下：

- BCLK: 数据口位-时钟信号，当 AIC23B 为从模式时（通常情况），该时钟由 DSP 产生；AIC23B 为主模式时，该时钟由 AIC23B 产生；

- LRCIN: 数据口 DAC 输出的帧同步信号（IIS 模式下左 / 右声道时钟）

- LRCOUT: 数据口 ADC 输入的帧同步信号

- DIN: 数据口 DAC 输出的串行数据输入

- DOUT: 数据口 ADC 输入的串行数据输出

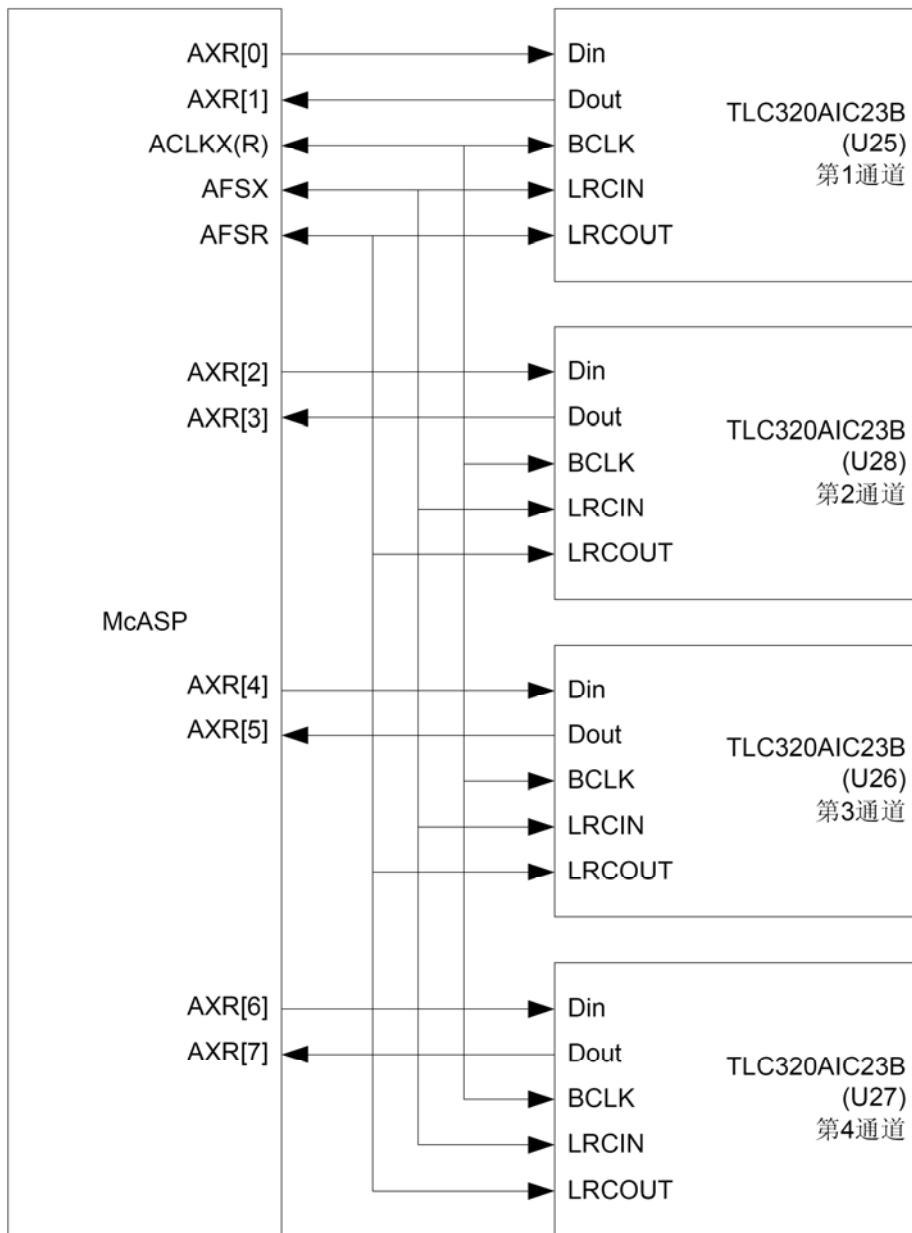

这部分可以和'DM642 的 McASP 接口无缝连接，可以方便的实现主模式与从模式两种工作方式。当 McASP 为从模式时，McASP 的接收时钟与帧同频信号都由 AIC23B 来提供；当 McSP 为主模式时，McASP 产生所有的信号。连接示意图如下：

## TMS320DM642

从上图可以看出，McASP 是如何与四片 TLC320AIC23B 进行连接的。描述如下：

- 第一通路 (U25) 的输入与输出与 McASP 的 AXR[1:0]连接，其中 AXR1 为数据输入，AXR0 为数据输出；

- 第二通路 (U28) 的输入与输出与 McASP 的 AXR[3:2]连接，其中 AXR3 为数据输入，AXR2 为数据输出；

- 第三通路 (U26) 的输入与输出与 McASP 的 AXR[5:4]连接，其中 AXR5 为数据输入，AXR4 为数据输出；

- 第四通路 (U27) 的输入与输出与 McASP 的 AXR[7:6]连接，其中 AXR7 为数据输入，AXR6 为数据输出；

- 四个通路的帧同步信号、发送与接收时钟均是共用的。因而，当 **McASP** 工作在从模式时，只能有且只能有一片 **AIC23B** 工作在主模式，其它三片工作在从模式。

当 **McASP** 工作在主模式时，其发送与接收模块的时钟中，须有一个选择为外部方式，一般选择发送时钟为 **McASP** 产生，接收时钟为外部（即 **ACLKX**）。

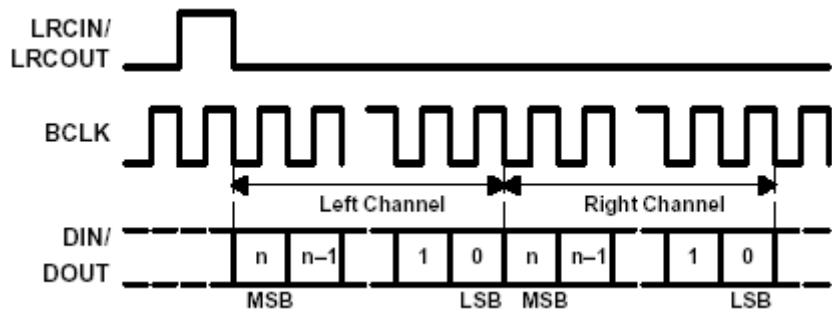

‘DM642 与 AIC23B 的数据交换的协议可以采用 DSP 模式与 IIS 模式，区别仅在于 DSP 的 McBSP 帧同步信号的宽度。后者的帧同步信号宽度必须为一个字（16 位）长，而前者的帧宽度可以为一个位长，比如在字长 16 位（即左右声道的采样各为 16 位），帧长为 32 位的情况下，如果采用 IIS，帧同步信号宽度应为 16 位；而采用 DSP Mode 帧信号宽度 1 位即可。在 SEED-VPM642 系统中采用 DSP 模式与 McASP 相连接。其时序如下图：

#### 4.3.2 AIC23B的控制口

TLV320AIC23B 的控制接口有两种工作方式，分别为：

- 2 线制的 IIC 方式（MODE 为低）；

- 3 线制的 SPI 方式（MODE 为高）。

在 SEED-VPM642 模板上采用 IIC 方式控制 TLV320AIC23B。其硬件管脚的说明如下：

- SDIN: AIC23B 控制口串行数据输入；

- SCLK: AIC23B 控制口的位-时钟；

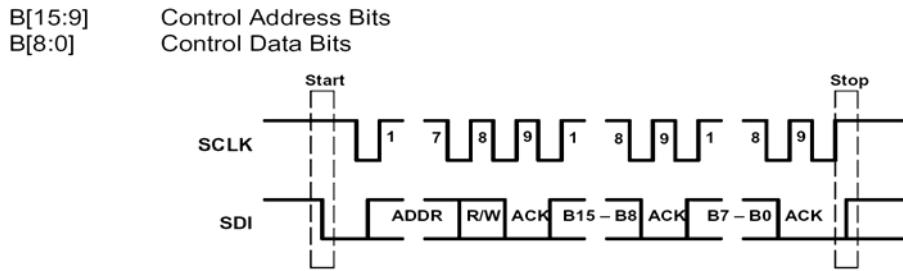

当使用 IIC 总线对 AIC23B 进行配置时，IIC 总线选择 7 位地址的寻址方式，并由于 AIC23B 的寄存器只有写操作无读操作，因而，其通讯协议为每个 WORD 的前 7-Bit 为寄存器地址，后 9-Bit 为寄存器内容。其时序如下图所示：

每个 AIC23B 只有两个不同的 IIC 总线从设备地址 0x1A (CS 为低) 与 0x1B (CS 为高) 可供选择。因而一个 IIC 总线只能配置 2 个 AIC23B。在 SEED-VPM642 中，我们采用将 DM642 的 IIC 总线切换成两路 IIC 总线 (IIC0 与 IIC1) 的方法实现对四片 AIC23B 的配置，每一路 IIC 总线上可以连接 2 个 AIC23B。其硬件连接原理如下图：

AIC23B 的控制寄存器见下表：

| 地址      | 需要初始化的寄存器     |

|---------|---------------|

| 0000000 | 左声道的音量控制寄存器   |

| 0000001 | 右声道的音量控制寄存器   |

| 0000010 | 左声道耳机的音量控制寄存器 |

| 0000011 | 右声道耳机的音量控制寄存器 |

| 0000100 | 模拟音频的路径控制寄存器  |

| 0000101 | 数字音频的路径控制寄存器  |

| 0000110 | 省电方式控制寄存器     |

| 0000111 | 数字音频的接口格式寄存器  |

| 0001000 | 采样率的设置寄存器     |

| 0001001 | 数字接口设置寄存器     |

| 0001111 | 复位寄存器         |

### 4.3.3 TLC320AIC23B的位时钟实现

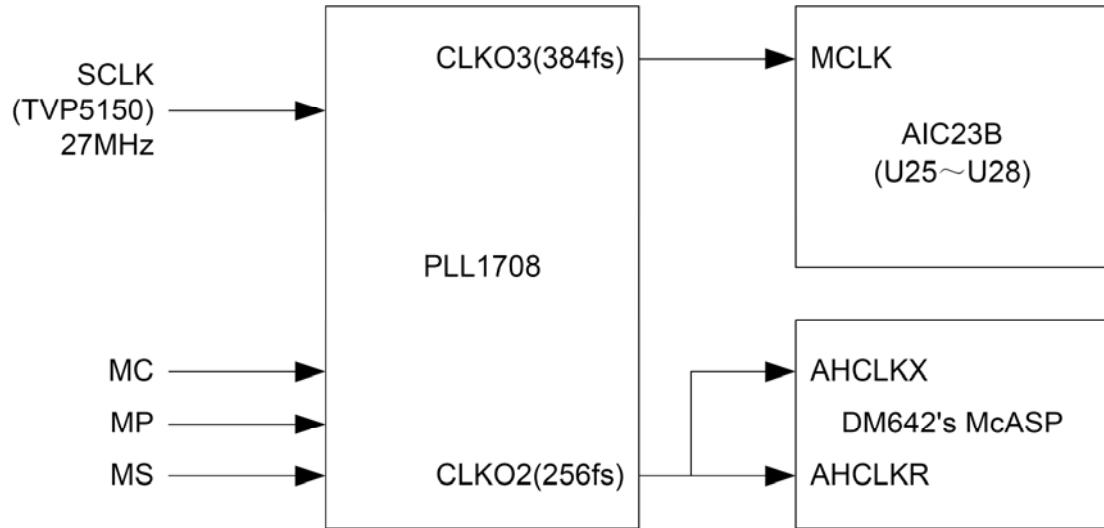

在 SEED-VPM642 系统中，音频的采集与图像的采集、音频的播放与图像的播放必须保持同步。因而 4 片 AIC23B 的时钟输入是由第一片视频解码器 TVP5150 的 SCLK 经过 PLL1708 经过适当分频后的 SCKO3 (384fs) 提供。另外为了保证获得合适的位时钟与帧同步信号配合，AHCLKx 与 AHCLKr 分别与 PLL1708 的 SCKO2 (256fs) 连接。其原理图如下所示：

从图中可以看出，PLL1708 是一可编程的锁相环，将 TVP5150 的 27MHz 的时钟输出做为输入，从而保证了图像与音频的同步；其可以分频出：

- SCKO1 输出可编程的 768fs、512fs、384fs、256fs ( $fs = 48\text{KHz}$ , 倍频系数可编程) 时钟，SEED-VPM642 系统未用；

- SCKO2 输出可编程的 256fs ( $fs = 16, 22.05, 24, 32, 44.1, 48, 64, 88.2, 96\text{KHz}$ , 音频采样率  $fs$  可编程) 时钟，**提供给 AIC23 的 MCLK**；

- SCKO3 输出可编程的 384fs ( $fs = 16, 22.05, 24, 32, 44.1, 48, 64, 88.2, 96\text{KHz}$ , 音频采样率  $fs$  可编程) 时钟，**提供给 AHCLKX(R)**；

- PLL1708 其它的时钟输出在 SEED-VPM642 系统中未使用。

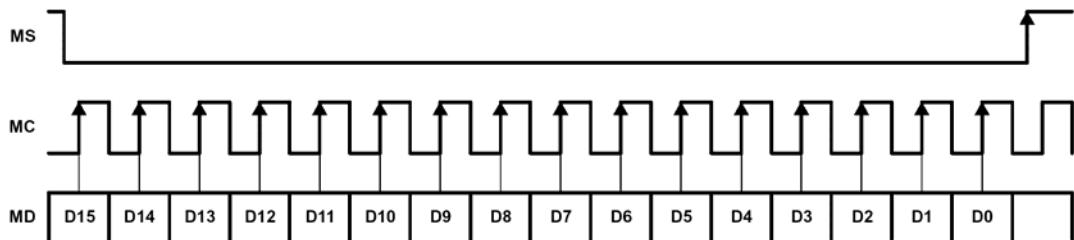

PLL1708 输出时钟的可编程特性由串口和引脚设置，用于编程的串口有 3 个信号，MC（位-时钟）、MD（数据位）和 MS（片选信号），这 3 个信号在 VPM642 中由 CPLD 产生，PLL1708 还有一个编程引脚 CSEL，其与串行控制数据中的 CFG1 位一起来选择 SCKO1 的输出频率。下图说明 MC/MP/MS 控制由 CPLD 的寄存器 AUDIOPLL (地址为 0x9008 0013) 产生，其说明如下：

地址：0x9008 0013 (只写)

| D07 | D06 | D05 | D04 | D03 | D02 | D01 | D00 |

|-----|-----|-----|-----|-----|-----|-----|-----|

| ×   | ×   | ×   | ×   | ×   | MD  | MC  | MS  |

- MD:** PLL1708 串行配置的数据位;

**MC:** PLL1708 串行配置的位-时钟;

**MS:** PLL1708 串行配置的片选信号。

在进行 PLL1708 编程时，用户可在 TMS320DM642 定时器的驱动下使 MC/MP/MS 产生如下的逻辑即可完成对 PLL1708 的编程（注意数据是在上升沿保持有效）：

在 PLL1708 中总其有两个寄存器：

- **Mode Register:** 用于控制各个时钟的使能及采样率的设置；

**MD** 每位代表的含义如下：

| D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| 0   | 1   | 1   | 1   | 0   | 0   | CE6 | CE5 | CE4 | CE3 | CE2 | CE1 | SR2 | SR1 | FS2 | FS1 |

- CE6:** MCKO2 输出使能 / 禁止控制

0: MCKO2 输出禁止

1: MCKO2 输出使能（缺省）

- CE5:** MCKO1 输出使能 / 禁止控制

0: MCKO1 输出禁止

1: MCKO1 输出使能（缺省）

- CE4:** SCKO1 输出使能 / 禁止控制

0: SCKO1 输出禁止

1: SCKO1 输出使能（缺省）

- CE3:** SCKO3 输出使能 / 禁止控制

0: SCKO3 输出禁止

1: SCKO3 输出使能（缺省）

- CE2:** SCKO2 输出使能 / 禁止控制

0: SCKO2 输出禁止

1: SCKO2 输出使能（缺省）

- CE1:** SCKO0 输出使能 / 禁止控制

0: SCKO0 输出禁止

|          |                 |

|----------|-----------------|

| 1:       | SCKO0 输出使能 (缺省) |

| SR[2:1]: | 音频采样率分频选择       |

| 00:      | $\times 1$ (缺省) |

| 01:      | $\times 2$      |

| 10:      | $\times 1/2$    |

| 11:      | 保留              |

| FS[2:1]: | 音频采样率 $f_s$ 的选择 |

| 00:      | 48KHz (缺省)      |

| 01:      | 44.1KHz         |

| 10:      | 32KHz           |

| 11:      | 保留              |

Configuration Register: 与 CSEL 组合, 选择 SCKO1 的输出。每位代表的含义如下:

| D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4   | D3  | D2  | D1  | D0  |

|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|-----|-----|-----|

| 0   | 1   | 1   | 0   | 1   | 1   | RSV | RSV | RSV | RSV | RSV | CFG1 | RSV | RSV | RSV | RSV |

CFG1: SCKO1 配置

0: SCKO1 输出频率为 768fs 或 512fs ( $f_s = 48\text{KHz}$ ) (缺省)

1: SCKO1 输出频率为 384fs 或 256fs ( $f_s = 48\text{KHz}$ )

CFG1、CSEL: SCKO1 配置

00: 768fs

01: 512fs

10: 384fs

11: 256fs

在 SEED-VPM642 中 SCKO1 未用。

#### 4.4 TLV320AIC23B的模拟接口

TLV320AIC23B 的模拟接口主要包括以下两个部分:

- 立体声输入与 MIC 输入;

- 立体声输出。

#### 4.4.1 立体声输入与麦克风输入

立体声输入口包括左右声道的输入，其管脚为：

- LLINEIN: 左声道 LINE IN 输入；

- RLINEIN: 右声道 LINE IN 输入。

麦克风输入主要是用来通过无源的麦克进行现场声音的采集。其中由于麦克是无源元器件，所以要为其提供偏置电源。其主要管脚如下：

- MICBIAS: 提供麦克风偏压，通常是 3/4 AVDD；

- MICIN: 麦克风输入，由 AIC 结构框图可以看出放大器默认是 5 倍增益

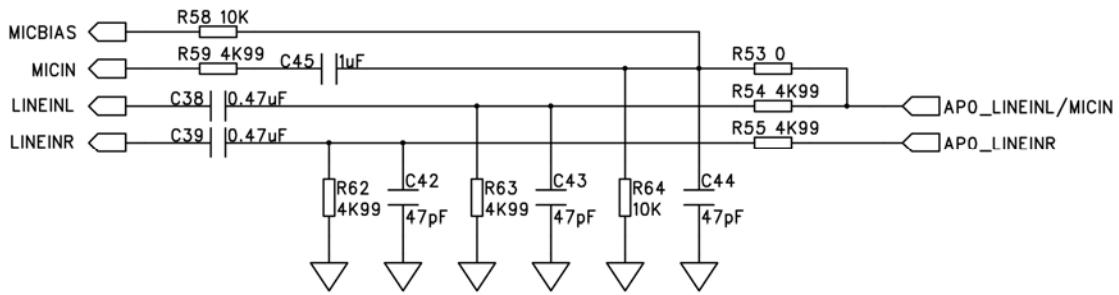

SEED-VPM642 中的音频输入的连接示意图如下：

从上图可以看出在 SEED-VPM642 中 LINE\_IN 与 MIC\_IN 是不能同时使用的，每次只能使用其中的一种功能。其切换是由两个电阻完成的。以上图为为例：

- 当 R53 焊接，R54 不焊时，使用 MIC\_IN 功能，此时 LINEINR 未用，也没有连接。

- 当 R53 不焊，R54 焊接时，使用 LINE\_IN 功能。

在 SEED-VPM642 上共有四路电路完全相同的音频输入前端，它们的配置如下所示：

- 第一通路 (U25)：

- 当 R53 焊接，R54 不焊时，使用 MIC\_IN 功能；

- 当 R53 不焊，R54 焊接时，使用 LINE\_IN 功能。

- 第二通路 (U28)：

- 当 R65 焊接，R66 不焊时，使用 MIC\_IN 功能；

- 当 R65 不焊，R66 焊接时，使用 LINE\_IN 功能。

- 第三通路 (U26)：

- 当 R78 焊接，R79 不焊时，使用 MIC\_IN 功能；

- 当 R78 不焊，R79 焊接时，使用 LINE\_IN 功能。

- 第四通路 (U27)：

- 当 R91 焊接，R92 不焊时，使用 MIC\_IN 功能；

- 当 R91 不焊，R92 焊接时，使用 LINE\_IN 功能。

在 SEED-VPM642 中，默认情况下音频的输入将配置成为 LINE\_IN 功能。

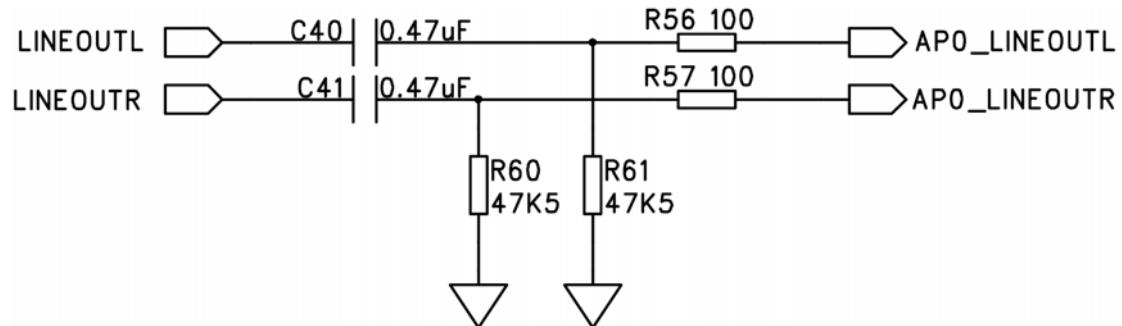

#### 4.4.2 立体声与耳机输出

AIC23B 总共有两种输出方式：

- 立体声输出，其管脚为：

- LOUT：左声道输出；

- ROUT：右声道输出。

- 耳机输出，可以直接驱动  $32\Omega$  的耳机，不需要外部再进行功率驱动了。其输出管脚为：

- LHPOUT：左声道耳机放大输出；

- RHPOUT：右声道耳机放大输出。

在 SEED-VPM642 中采用标准的立体声输出，从 AIC23B 框图可以看出，LOUT 和 ROUT 没有经过内部放大器，是标准的 AC97 的接口，其连接示意图如下：

## 第 5 章

# UART & 数字I / O接口

---

在 SEED-VPM642 上配置有二个通用异步串口，接口标准可由软件配置为 RS232 / RS422 / RS485，它可用于控制云台或与其它设备通讯。

在 SEED-VPM642 上还配置有一定数量的数字 I / O 口线，用于系统报警和状态指示。

## 5.1 数字I / O

在 SEED-VPM642 模板上配置有 8-位数字量输入，8-位数字量输出，对应的输入 / 输出如下所示：

□ 数字量输入口：

SEED-VPM642 模板上数字量输入口映射到 DM642 存贮空间的 0x9008 0010，是一个 8-位只读寄存器 DINR，该寄存器位域定义如下：

地址：0x9008 0010（只读）

| D07  | D06  | D05  | D04  | D03  | D02  | D01  | D00  |

|------|------|------|------|------|------|------|------|

| DIN7 | DIN6 | DIN5 | DIN4 | DIN3 | DIN2 | DIN1 | DIN0 |

DIN[i]：连接器 J1 上的 DI[i] ( $i = 0、1、\dots、7$ ) 信号的当前状态

0：DI[i]当前状态为低电平；

1：DI[i]当前状态为高电平。

□ 数字量输出口：

SEED-VPM642 模板上数字量输入口映射到 DM642 存贮空间的 0x9008 0010，是一个 8-位只写寄存器 DOUTR，该寄存器位域定义如下：

地址：0x9008 0010（只写）

| D07   | D06   | D05   | D04   | D03   | D02   | D01   | D00   |

|-------|-------|-------|-------|-------|-------|-------|-------|

| DOUT7 | DOUT6 | DOUT5 | DOUT4 | DOUT3 | DOUT2 | DOUT1 | DOUT0 |

DOUT[i]: 直接输出给连接器 J1 上的 DO[i] ( $i = 0, 1, \dots, 7$ ) 信号;

0: DO[i]当前输出为低电平;

1: DO[i]当前输出为高电平。

## 5.2 TL16C752B

SEED-VPM642 采用 TL16C752B 通用异步收发器 UART，其上包含二路相互独立的异步收发器，接收和发送各带 64-字节 FIFO，并各自带有 Modem 接口信号。对于 RS232，SEED-VPM642 板卡最高传输率可达 1Mbaud；对于 RS422/RS485，SEED-VPM642 板卡最高传输率可达 1.92Mbaud。

### 5.2.1 TL16C752BPT与DSP的连接

TL16C752B 采用 8-位异步并行存储器接口，并采用 +3.3V 电源供电，可以与 TMS320DM642 的外部存储器接口 (EMIFA) 直接连接。TL16C752B 每个通道包含 18 个寄存器，通过地址 A2~A0 及寄存器位对它们进行寻址，A、B 二通道分别由片选信号选通。SEED-VPM642 将 TL16C752B 配置在 TMS320DM642 的  $\overline{CE1}$  空间，A、B 二个通道所占的地址范围如下：

|        |  | 地址                      |

|--------|--|-------------------------|

| UART A |  | 0x9008 0000~0x9008 0007 |

| UART B |  | 0x9008 0008~0x9008 000F |

另外，TL16C752B 还提供二个中断请求信号 INTA、INTB 分别用于通道 A 和 B 申请 TMS320DM642 的中断。在 SEED-VPM642 中，INTA 和 INTB 相与，复用 TMS320DM642 的 INT5。

### 5.2.2 UART的寄存器说明

TL16C752B 每个通道均有 18 个寄存器，用于控制串行异步通信的工作方式，以及反馈相应的状态，这些寄存器总结如下：

| A2 | A1 | A0 | 读方式           | 写方式              |

|----|----|----|---------------|------------------|

| 0  | 0  | 0  | 接收保持寄存器 (RHR) | 发送保持寄存器 (THR)    |

| 0  | 0  | 1  | 中断使能寄存器 (IER) | 中断使能寄存器 (IER)    |

| 0  | 1  | 0  | 中断标志寄存器 (IIR) | FIFO 控制寄存器 (FCR) |

| 0  | 1  | 1  | 线路控制寄存器 (LCR) | 线路控制寄存器 (LCR)    |

|   |   |   |                   |                   |

|---|---|---|-------------------|-------------------|

| 1 | 0 | 0 | MODEM 控制寄存器 (MCR) | MODEM 控制寄存器 (MCR) |

| 1 | 0 | 1 | 线路状态寄存器 (LSR)     |                   |

| 1 | 1 | 0 | MODEM 状态寄存器 (MSR) |                   |

| 1 | 1 | 1 | 暂存寄存器 (SRP)       | 暂存寄存器 (SRP)       |

| 0 | 0 | 0 | 低位除数寄存器 (DLL)     | 低位除数寄存器 (DLL)     |

| 0 | 0 | 1 | 高位除数寄存器 (DLH)     | 高位除数寄存器 (DLH)     |

| 0 | 1 | 0 | 增强功能寄存器 (EFR)     | 增强功能寄存器 (EFR)     |

| 1 | 0 | 0 | Xon-1 word        | Xon-1 word        |

| 1 | 0 | 1 | Xon-2 word        | Xon-2 word        |

| 1 | 1 | 0 | Xoff-1 word       | Xoff-1 word       |

| 1 | 1 | 1 | Xoff-2 word       | Xoff-2 word       |

| 1 | 1 | 0 | 发送控制寄存器 (TCR)     | 发送控制寄存器 (TCR)     |

| 1 | 1 | 1 | 触发等级寄存器 (TLR)     | 触发等级寄存器 (TLR)     |

| 1 | 1 | 1 | FIFO 就绪寄存器        |                   |

黑体的部分的寄存器为二次寻址的寄存器。

### 线路控制寄存器

| D7   | D6    | D5  | D4  | D3  | D2  | D1  | D0  |

|------|-------|-----|-----|-----|-----|-----|-----|

| DLAB | BREAK | SPB | EPS | PEN | STB | WL1 | WL0 |

WL1 WL0: 设置数据长度

- 00 5 位

- 01 6 位

- 10 7 位

- 11 8 位

STB: 设置停止位个数

- 0 1 个停止位

- 1 1.5 个停止位 (5 位数据长度时) , 2 个停止位 (6、7、8 位数据长度时)

PEN: 奇偶校验使能

- 0 奇偶校验无效

- 1 奇偶校验有效

EPS: 奇偶校验选择

- 0 奇校验

- 1 偶校验

SPB: 选择强制校验功能 (如果 PEN=1)

- 0 非强制校验

|               |                                                                          |

|---------------|--------------------------------------------------------------------------|

| 1             | 强制校验<br>如果此位置 1，并且 EPS=0；在发送与接收的数据后置 1<br>如果此位置 1，并且 EPS=1；在发送与接收的数据后置 0 |

| <b>BREAK:</b> | 间隔控制位<br>0 正常操作；<br>1 强迫输出为低，以警告通讯中止                                     |

| <b>DLAB:</b>  | 寄存器访问选择<br>0 访问其余寄存器<br>1 访问除数和功能切换寄存器与 EFR 寄存器                          |

### MODEM 控制寄存器

| D7                   | D6                | D5           | D4   | D3   | D2  | D1  | D0  |

|----------------------|-------------------|--------------|------|------|-----|-----|-----|

| x1 or<br>x1/4<br>CLK | TCR<br>&TLR<br>EN | 0\Xon<br>Any | LOOP | IRQE | FRE | RTS | DTR |

|                        |                                                                                 |

|------------------------|---------------------------------------------------------------------------------|

| <b>DTR:</b>            | 数据终端准备好信号<br>0 管脚 DTR 输出为低<br>1 管脚 DTR 输出为高                                     |

| <b>RTS:</b>            | 发送请求信号<br>0 管脚 RTS 输出为低<br>1 管脚 RTS 输出为高：                                       |

| <b>FRE:</b>            | FIFO 的 Rdy 使能信号<br>0 禁止 FIFO 的 Rdy<br>1 使能 FIFO 的 Rdy                           |

| <b>IRQE:</b>           | 中断管脚使能及 OP 脚管的输出<br>0 中断管脚 INTA、INTB 为三态，OP 输出为低<br>1 中断管脚 INTA、INTB 使能，OP 输出为高 |

| <b>LOOP:</b>           | 自闭环<br>0 正常工作方式<br>1 自闭环工作方式，用于串口自检                                             |

| <b>0\Xon any:</b>      | 此位仅在 EFR[4]置 1 时有效<br>0 禁止 Xon any 功能<br>1 使能 Xon any 功能                        |

| <b>TCR&amp;TLR EN:</b> | 此位仅在 EFR[4]置 1 时有效；使能 TCR 和 TLR 寄存器                                             |

|   |                  |

|---|------------------|

| 0 | 无操作              |

| 1 | 使能 TCR 和 TLR 寄存器 |

|                 |                     |

|-----------------|---------------------|

| x1 or x1/4 CLK: | 此位仅在 EFR[4]置 1 时有效; |

| 0               | 时钟输入除 1             |

| 1               | 时钟输入除 4             |

复位时， MODEM 控制寄存器清零。

### 中断使能寄存器

| D7              | D6              | D5           | D4        | D3   | D2   | D1     | D0    |

|-----------------|-----------------|--------------|-----------|------|------|--------|-------|

| 0\CTS interrupt | 0\RTS interrupt | 0\Xoff sleep | 0\X Sleep | EMSI | ELSI | ETHREI | ERDAI |

|        |        |

|--------|--------|

| ERDAI: | 接收中断使能 |

| 1      | 接收中断使能 |

| 0      | 接收中断禁止 |

|         |        |

|---------|--------|

| ETHREI: | 发送中断使能 |

| 1       | 发送中断使能 |

| 0       | 发送中断禁止 |

|       |          |

|-------|----------|

| ELSI: | 接收错误中断使能 |

| 1     | 接收错误中断使能 |

| 0     | 接收错误中断禁止 |

|       |            |

|-------|------------|

| EMSI: | MODEM 中断使能 |

| 1     | MODEM 中断使能 |

| 0     | MODEM 中断禁止 |

|            |                    |

|------------|--------------------|

| 0\X Sleep: | 此位仅在 EFR[4]置 1 时有效 |

| 1          | 使能省电模式             |

| 0          | 禁止省电模式             |

|               |                    |

|---------------|--------------------|

| 0\Xoff sleep: | 此位仅在 EFR[4]置 1 时有效 |

| 1             | 使能 Xoff 中断         |

| 0             | 禁止 Xoff 中断         |

|                  |                    |

|------------------|--------------------|

| 0\RTS interrupt: | 此位仅在 EFR[4]置 1 时有效 |

| 1                | 使能 RTS 中断          |

| 0                | 禁止 RTS 中断          |

|                  |                    |

|------------------|--------------------|

| 0\CTS interrupt: | 此位仅在 EFR[4]置 1 时有效 |

| 1                | 使能 CTS 中断          |

## 中断标志寄存器

| D7     | D6     | D5        | D4     | D3    | D2    | D1    | D0   |

|--------|--------|-----------|--------|-------|-------|-------|------|

| FCR(0) | FCR(0) | 0\CTS,RTS | 0\Xoff | INTC2 | INTC1 | INTC0 | INTS |

INTS: 中断状态位

0 有中断

1 无中断

INTC[2:0]: 中断编码, 见下表

0\Xoff: Xoff 或特殊字符被检测到的中断状态

0\CTS,RTS: CTS 与 RTS 从低变高的状态。

FCR(0): FCR[0]的内容的镜像。

TL16C752B 中有 7 个中断源, 它们分别是: 接收错误中断; 接收中断; FFIO 超时中断; 发送中断; MODEM 中断; Xoff 或特殊字符被检测到的中断; CTS 与 RTS 从低变高的状态中断; 这 7 个中断有相应的优先级。中断标志寄存器功能如下表:

| 中断标志寄存器 |    |    |    |    |    | 中 断 设 置 与 清 除 |         |                       |                           |

|---------|----|----|----|----|----|---------------|---------|-----------------------|---------------------------|

| D5      | D4 | D3 | D2 | D1 | D0 | 中断优先级         | 中断类型    | 中断源                   | 中断清除                      |

| 0       | 0  | 0  | 0  | 0  | 1  | —             | 无中断     | 无中断                   |                           |

| 0       | 0  | 0  | 1  | 1  | 0  | 最高            | 接收错误    | 溢出、奇偶、帧错误、间断          | 溢出中断读线路状态寄存器, 其它的读接收 FIFO |

| 0       | 0  | 1  | 1  | 0  | 0  | 第二            | 接收超时    | 接收 FIFO 中有无效数据        | 读接收缓冲器                    |

| 0       | 0  | 0  | 1  | 0  | 0  | 第二            | RHR 中断  | 接收缓冲器有数据              | 读接收缓冲器                    |

| 0       | 0  | 0  | 0  | 1  | 0  | 第三            | 发送      | 发送寄存器空/发送 FIFO 超过触发设定 | 读 IIR 或写发送保持寄存器           |

| 0       | 0  | 0  | 0  | 0  | 0  | 第四            | MODEM   | MODEM 状态              | 读 MODEM 状态寄存器             |

| 0       | 1  | 0  | 0  | 0  | 0  | 第五            | Xoff 中断 | 接收到 Xoff 或特殊字符        | 接收 Xon 字符/读 IIR           |

| 1       | 0  | 0  | 0  | 0  | 0  | 第六            | CTS,RTS | CTS 与 RTS 管脚从低变高      | 读 IIR                     |

### 5.2.3 波特率的设置

TL16C752B 包含一个可编程的波特率寄存器，它可以在输入时钟的基础上进行分频(最大分频数为  $2^{16} - 1$ )，其计算公式如下：

$$\text{分频数} = \text{当前时钟输入 (30.72MHz)} / (\text{比例系数} \times 16 \times \text{期望的波特率})$$

其中比例系数为：

当复位后，寄存器 MCR 的第 7 位设为 0 时，比例系数为 1 (默认值)

当复位后，寄存器 MCR 的第 7 位设为 1 时，比例系数为 4

当时钟为 30.72MHz 时，常用波特率的设置如下：

| 波特率   | 高位除数寄存器 DLM | 低位除数寄存器 DLL |

|-------|-------------|-------------|

| 1200  | 06H         | 40H         |

| 2400  | 03H         | 20H         |

| 4800  | 01H         | 90H         |

| 9600  | 00H         | C8H         |

| 19200 | 00H         | 64H         |

| 38400 | 00H         | 32H         |

### 5.3 异步串口接口电平

采用 MAX3160 多协议收发器，使得异步串口接口电平可配置为 RS232 / RS422 / RS485 多种接口电平标准。TL16C752B 的 Modem 信号没有完全引至串行接口上，只是在 RS232 接口标准时，采用 4 线制 (RXD、TXD、RTS、CTS)，而在 RS422 / RS485 接口标准时，采用 2 线制 (RXD、TXD)。

MAX3160 上的引脚 **RS485/RS-232** 用于选择工作在 RS422/RS485 还是 RS232 接口标准，引脚 HDPLX 则用于选择是 RS422 还是 RS485。它们受系统控制寄存器 0 (SYSCNTL0) 的控制，其各位的定义如下：

串口配置寄存器 (UARTSET)

地址：0x9008 0012，只写

| D07 | D06 | D05 | D04 | D03   | D02   | D01                  | D00                  |

|-----|-----|-----|-----|-------|-------|----------------------|----------------------|

| ×   | ×   | ×   | ×   | FASTB | FASTA | <b>RS485/RS-232B</b> | <b>RS485/RS-232A</b> |

| ×   | ×   | ×   | ×   | W-0   | W-0   | W-0                  | W-0                  |

**RS485/RS-232A:** 异步串口 0 (COM 0) 配置为 RS232 方式还是 RS422/RS485 方式

- 0 选择 RS232 方式

- 1 选择 RS422/RS485 方式

**RS485/RS-232B:** 异步串口 1 (COM 1) 配置为 RS232 方式还是 RS422/RS485 方式

- 0 选择 RS232 方式

- 1 选择 RS422/RS485 方式

**FASTA:** 异步串口 1 (COM 1) 配置为全速还是慢速运行方式

- 0 慢速运行方式

- 1 快速运行方式

**FASTB:** 异步串口 2 (COM 2) 配置为全速还是慢速运行方式

- 0 慢速运行方式

- 1 快速运行方式

MAX3160 上的引脚 HDPLX 用于控制是否采用全双工模式，异步串口 COM 0 和 COM 1 的 2 个 HDPLXA 和 HDPLXB 信号分别由 TL16C752B 的引脚 DTRA 和 DTRB 配置为输出来控制，当 FAST 为 0 时，选用全双工模式；当 FAST 为 1 时，选用半双工模式。

**注 1：** MAX3160 上的引脚 FAST 用于控制信号转换率。当 FAST 为 0 时，选用较低的信号转换率，有利于 EMI 抑制；当 FAST 为 1 时，选用较高的信号转换率。

**注 2：** 在使用 RS485 方式时，一定注意，串行通讯是半双工的，发送与接收共用一对绞线，发送时，亦同时在已方可接收到，所以发送时一定禁止接收操作。

**注 3：** 在使用 RS485/RS422 方式时，电阻 R155~R158 焊接 120 欧姆。

## 第 6 章

# PCI、HPI与以太网接口

---

在 SEED-VPM642 系统中可以实现 PCI、HPI(16-位或 32-位)、以太网(EMAC+MDIO)等三种接口。由于在 TMS320DM642 片上这三种外设复用同一组引脚，所以这三种功能除了 HPI16 与以太网接口可以同时使用外，其它的配置不能同时使用的。SEED-VPM642 将这三种接口设计成根据模板的安装情况自动进行配置。

### 6.1 自动配置的实现

SEED-VPM642 有下列三种可能的接口形式：

- 32-位 PCI 接口；

- 32-位 HPI 接口；

- 16-位 HPI + 以太网接口。

SEED-VPM642 模板上采用自动检测来进行自动配置，利用 PCI 总线上 B3 (GND) 和 B10 (保留) 分别作为 EMAC\_DETECT (上拉) 和 HPI\_DETECT (下拉) 自动检测信号，检测信号与接口之间的关系如下表所示：

| EMAC_DETECT<br>(B3) | HPI_DETECT<br>(B10) | 接口            |

|---------------------|---------------------|---------------|

| 1                   | 0                   | HPI16 + 以太网接口 |

| 0                   | 0                   | 32-位 PCI      |

| 0                   | 1                   | 32-位 HPI      |

| 1                   | 1                   | ×             |

### 6.2 PCI总线接口

当用户将 SEED-VPM642 模板插入计算机的 PCI 插槽中时，检测信号 EMAC\_DETECT 接地为低电平，HPI\_DETECT 下拉为低电平，自动配置成 32-位 PCI 总线，此时 DM642 的配置引脚状态如下：

- PCI\_EN 为高, MAC\_EN 为低, 使能 DM642 的 PCI 功能;

- PCIEAI 为高, 使能 EEPROM 的自动初始化功能;

- PCI66 为高, 使 DM642 的 PCI 总线工作在 33MHz。

在上电复位后, TMS320DM642 将 PCI 端口按以上的初始条件使能, 完成与计算机的配置。

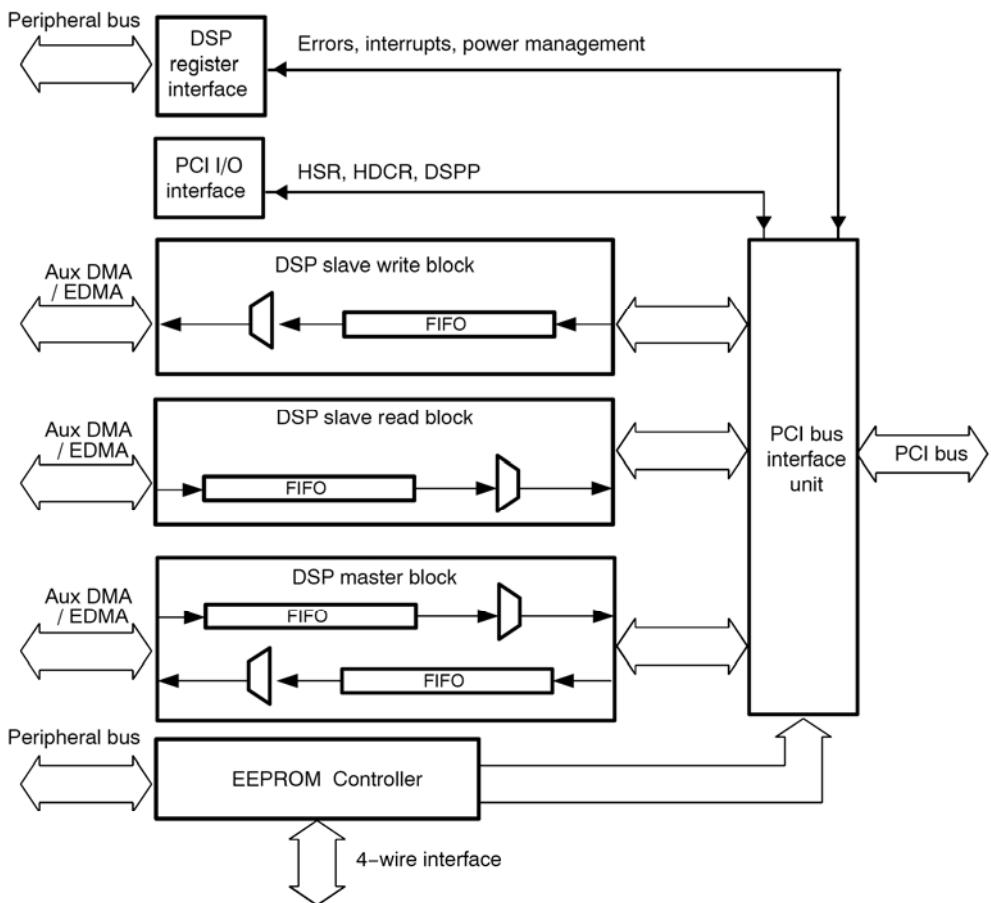

### 6.2.1 PCI简介

TMS320DM642 的 PCI 总线由以下几个部分组成:

- PCI 总线接口单元;

- EEPROM 控制器;

- DSP 作为 PCI 从设备时的写传输 (PC→'DM642) 单元;

- DSP 作为 PCI 从设备时的读传输 (PC←'DM642) 单元;

- DSP 作为 PCI 主设备时的数据传输单元;

- PCI 的 I/O 接口;

- DSP 寄存器接口。

其原理框图如下所示:

PCI 的主要功能如下：

- 支持 PCI2.2 的协议；

- 支持 4 线的 EEPROM 自动初始化功能；

- 支持 PCI 的主、从两种模式的总线传输，通过 EDMA 总线能完成以下四种读 / 写方式：

- 从模式写传输，PC 机通过 PCI 总线写数据到'DM642 存储空间中；

- 从模式读传输，PC 机通过 PCI 总线从'DM642 存储空间中读数据；

- 主模式写传输，'DM642 通过 PCI 总线写数据到 PC 机存储空间；

- 主模式读传输，'DM642 通过 PCI 总线从 PC 机存储空间中读数据。

关于 PCI 的详细的说明参看文档：**TMS320C6000 DSP Ethernet Media Access Controller (EMAC)/ Management Data Input/Output (MDIO)Module Reference Guide**（文献号 SPRU628）。

### 6.2.2 PCI 的寄存器

PCI 总线接口总共有三种寄存器：

- PCI 配置寄存器，只能被外部的主 PCI 设备访问；

- PCI I/O 寄存器，只能被外部的主 PCI 设备访问；

- PCI 存贮器映射的外设寄存器，可以被 DSP 与 PCI 的主机访问。

### 6.2.2.1 配置寄存器

配置寄存器包含了标准的 PCI 配置信息，包括 vendor ID、device ID、class code、revision number 等等。这些寄存器的设置可以在上电时从 EEPROM 中被初始化。配置寄存器的列表如下图：

| Address | Access     | Byte 3                                   | Byte 2      | Byte 1                          | Byte 0               |

|---------|------------|------------------------------------------|-------------|---------------------------------|----------------------|

| 00h     | read only  | Device ID                                |             | Vendor ID                       |                      |

| 04h     | read/write | Status                                   |             | Command                         |                      |

| 08h     | read only  | Class Code                               |             |                                 | Revision ID          |

| 0Ch     | read/write | Reserved                                 | Header Type | Latency Timer                   | Cache Line Size      |

| 10h     | read/write | Base 0 Address (4M-byte prefetchable)    |             |                                 |                      |

| 14h     | read/write | Base 1 Address (8M-byte nonprefetchable) |             |                                 |                      |

| 18h     | read/write | Base 2 Address (4 words I/O)             |             |                                 |                      |

| 24h     | read only  | Reserved                                 |             |                                 |                      |

| 2Ch     | read only  | Subsystem ID                             |             | Subsystem Vendor ID             |                      |

| 30h     | read only  | Reserved                                 |             |                                 |                      |

| 34h     | read only  | Reserved                                 |             |                                 | Capabilities Pointer |

| 38h     | read only  | Reserved                                 |             |                                 |                      |

| 3Ch     | read/write | Max_Latency                              | Min_Grant   | Interrupt Pin                   | Interrupt Line       |

| 40h     | read only  | Power Management Capabilities            |             | Next Item Pointer               | Capability ID        |

| 44h     | read/write | Power Data                               | Reserved    | Power Management Control/Status |                      |

| 48h FFh | read only  | Reserved                                 |             |                                 |                      |

Note: Shaded registers can be autoloaded from EEPROM at autoinitialization.

### 6.2.2.2 PCI I/O 寄存器

PCI 的 I/O 寄存器位于 PCI 主机端的 I/O 空间。它只能由主机端通过对 I/O 的基址 1 或基址 2 访问。所有的 I/O 寄存器均为字节寻址的。当处理器不支持 I/O 寻址模式时，对内存映射的基址 1 进行读写 PCI 的 I/O 寄存器。I/O 寄存器列表如下：

| <b>Acronym</b> | <b>Register Name</b>         |

|----------------|------------------------------|

| HSR            | Host status register         |

| HDCR           | Host-to-DSP control register |

| DSPP           | DSP page register            |

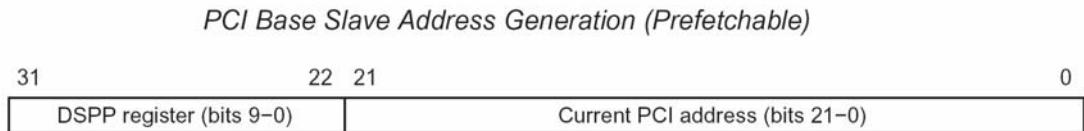

#### 6.2.2.3 PCI存贮器映射的外设寄存器

这些寄存器被映射到了 DSP 的空间内，使 DSP 可以控制与观察 PCI 接口的状态。这些寄存器均可被 DSP 与 PCI 的主机端访问。列表如下：

| Acronym             | Register Name                                |

|---------------------|----------------------------------------------|

| RSTSRC              | DSP reset source/status register             |

| PMDCSR <sup>†</sup> | Power management DSP control/status register |

| PCIIS               | PCI interrupt source register                |

| PCIIEN              | PCI interrupt enable register                |

| DSPMA               | DSP master address register                  |

| PCIMA               | PCI master address register                  |

| PCIMC               | PCI master control register                  |

| CDSPA               | Current DSP address register                 |

| CPCIA               | Current PCI address register                 |

| CCNT                | Current byte count register                  |

| EEADD               | EEPROM address register                      |

| EEDAT               | EEPROM data register                         |

| EECTL               | EEPROM control register                      |

| HALT <sup>†</sup>   | PCI transfer halt register                   |

| TRCTL <sup>‡</sup>  | PCI transfer request control register        |

<sup>†</sup> This register only applies to C62x DSP.

<sup>‡</sup> TRCTL register only applies to C64x DSP.

### 6.2.3 PCI的初始化

PCI 的初始化可以由两种方式完成，一为 TMS320DM642 按默认值完成初始化，另一为通 EEPROM 完成 PCI 接口的初始化。在 SEED-VPM642 系统中是选用后者。

在 SEED-VPM642 系统中，采用的是 93LC66B 做为自动初始化的 EERPOM，其接口形式为 4 线的 SPI 方式，详细说明见下表：

| Pin     | Input/Output | Description               |

|---------|--------------|---------------------------|

| XSP_CLK | O            | Serial EEPROM Clock       |

| XSP_CS  | O            | Serial EEPROM Chip Select |

| XSP_DI† | I            | Serial EEPROM Data In     |

| XSP_DO  | O            | Serial EEPROM Data Out    |

† The XSP\_DI pin should be pulled down.

PCI 的初始化的配置值在 EEPROM 内部位置的映射如下表：

| EEPROM Memory Map |                                       |

|-------------------|---------------------------------------|

| Address           | Contents (msb ... lsb)                |

| 0h                | Vendor ID                             |

| 1h                | Device ID                             |

| 2h                | Class Code [7–0]/Revision ID          |

| 3h                | Class Code [23–8]                     |

| 4h                | Subsystem Vendor ID                   |

| 5h                | Subsystem ID                          |

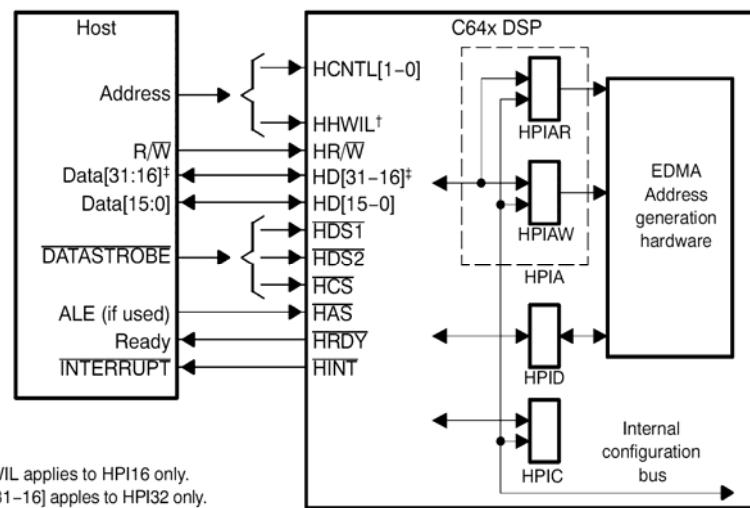

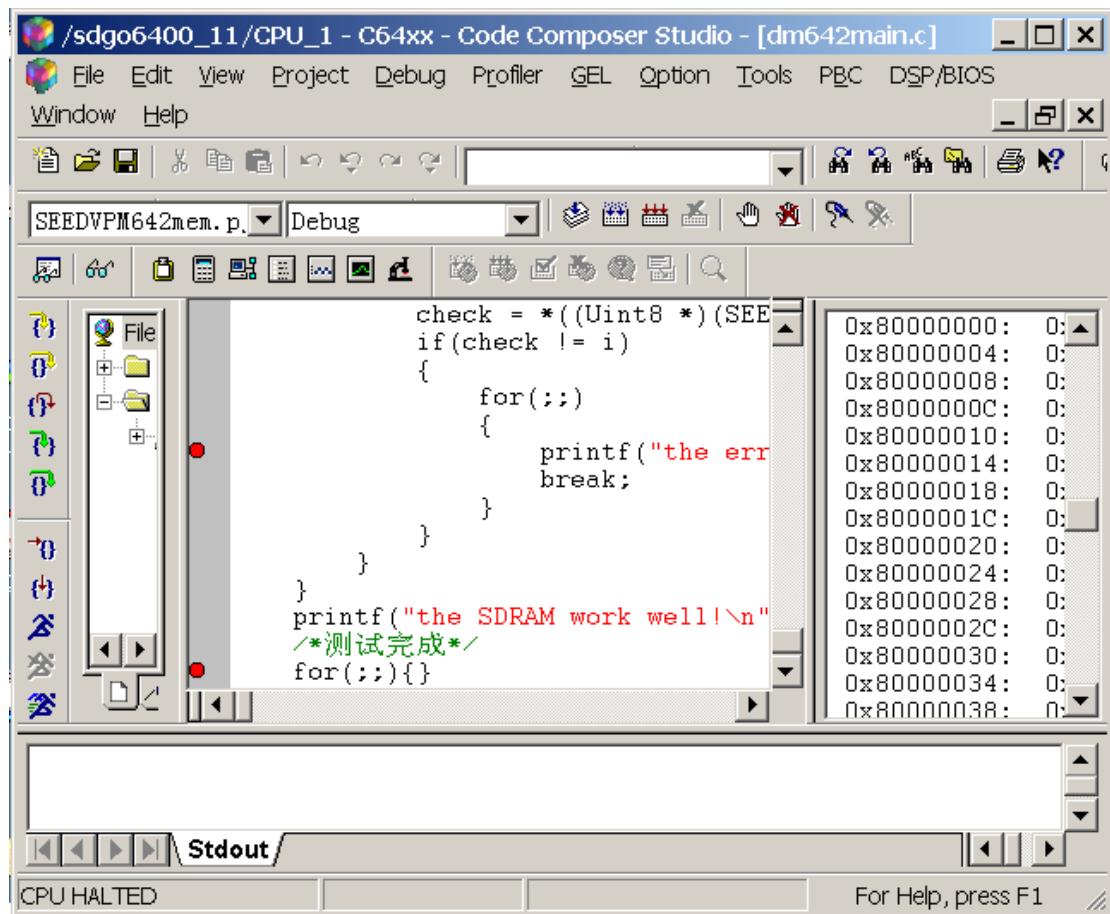

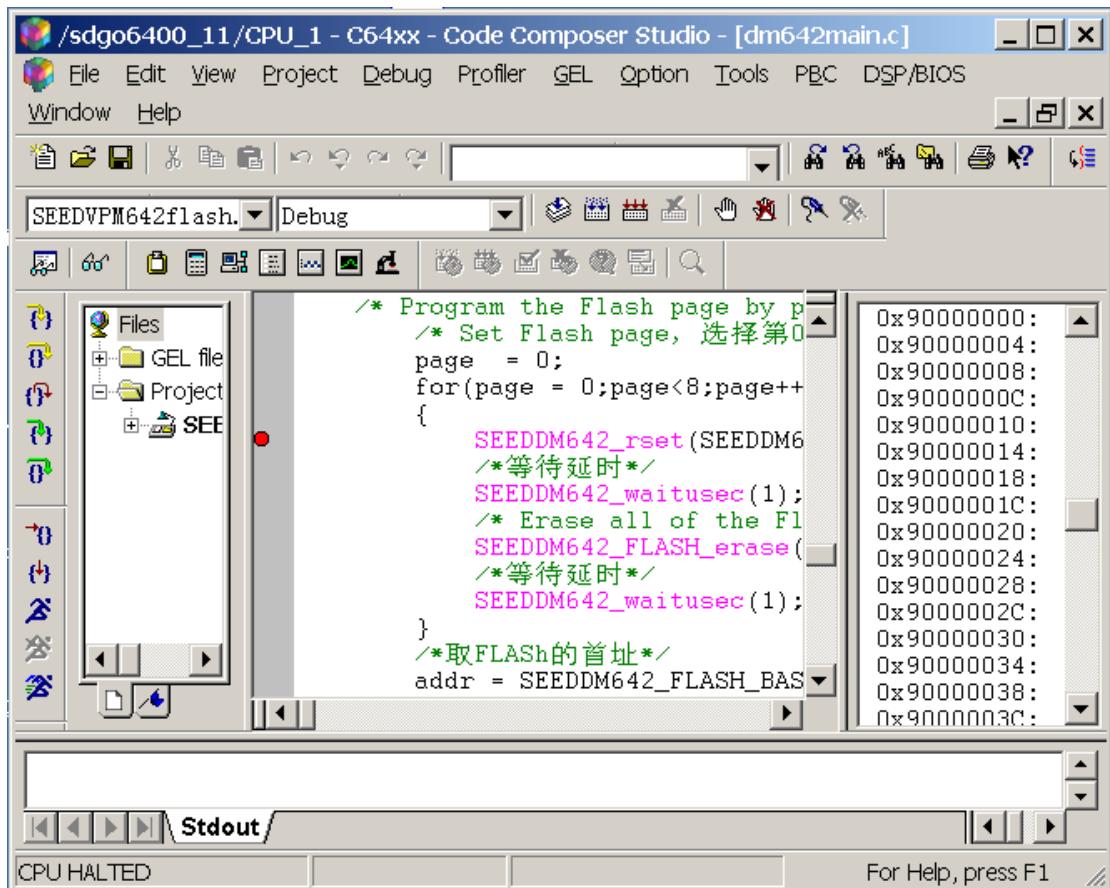

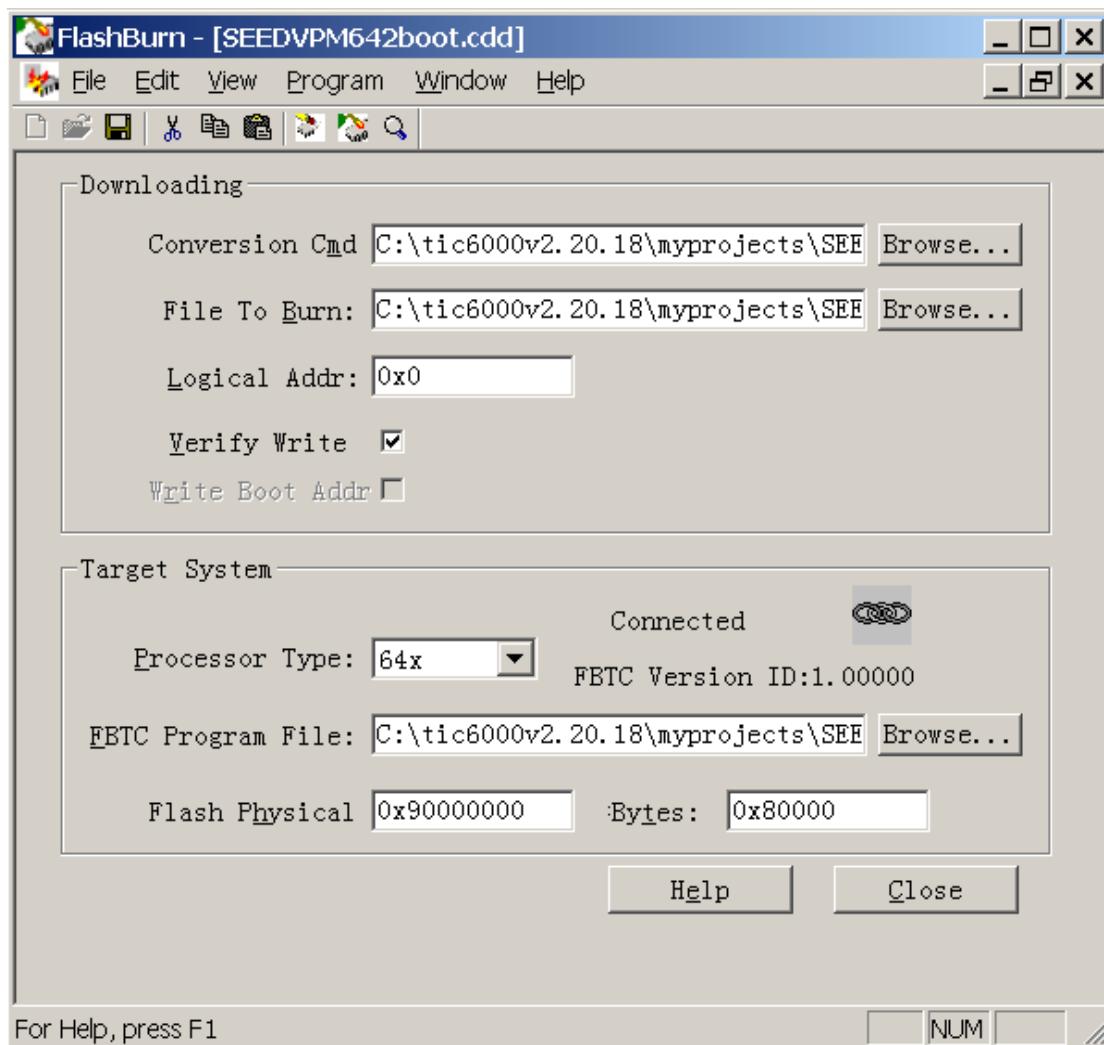

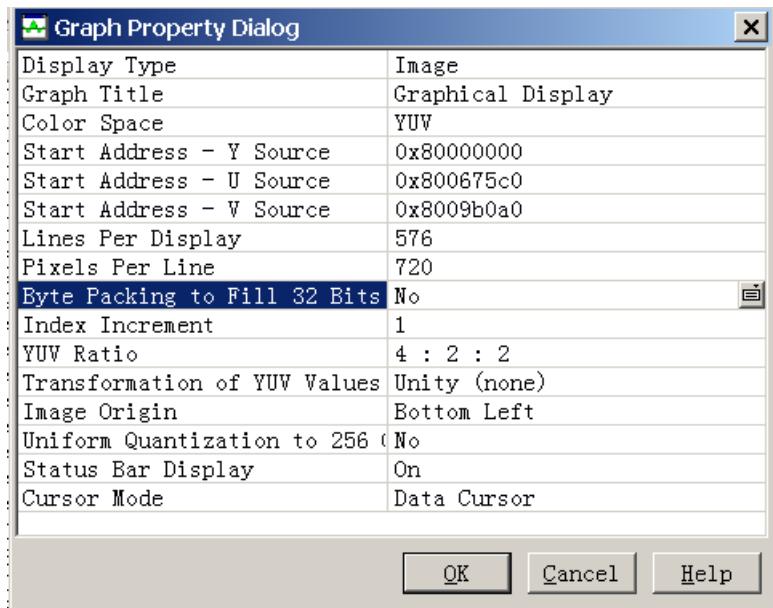

| 6h                | Max_Latency/Min_Grant                 |