# Gigabit Ethernet Switch Subsystem

1

# **Agenda**

- GbE Switch

- SGMII

- MDIO

- Example Code

- SGMII Loopback

- PC-EMAC Communication

### **GbE Switch**

- Overview

- ALE Operational mode

- Normal Mode

- Direct Packet

- Bypass Mode

- MAC Flow Control

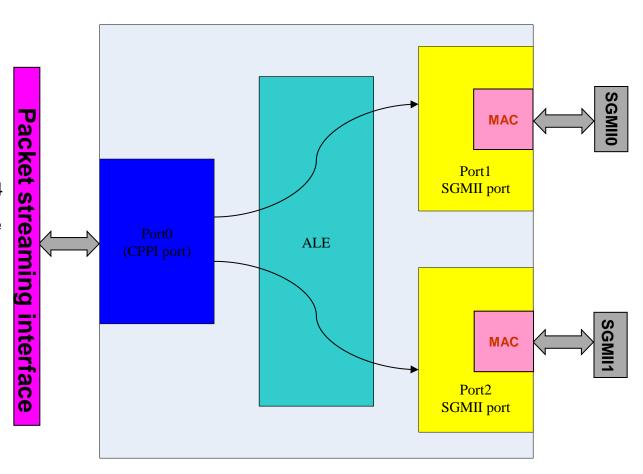

#### **GbE Switch - Overview**

- One CPPI port

- Two SGMII ports

- One MAC per SGMII port

- Address Lookup Engine (ALE)

- Determine which port to forward the frame

- A lookup table with 1024 entries shared for three ports. Entry table can be updated by ALE through learning and semiautomatic age-out mechanism or maintained by host.

- Learn based on source MAC address

- Forward based on destination MAC address

# **GbE Switch – ALE Operational Mode**

- Normal Mode

- Direct Packet

- Bypass Mode

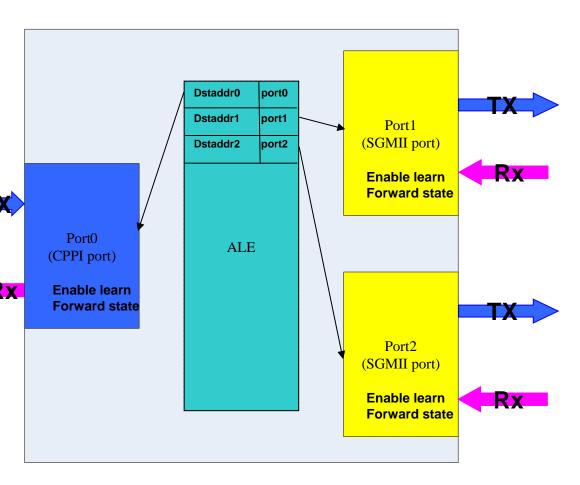

### **GbE Switch – ALE Normal Mode**

- Configure all the three ports as forward state, and enable learn for src addr learning to update the ALE table in time.

- Entered frame with dstaddr0 is forwarded to port0, with dstaddr1 is forwarded to port1, and with dstaddr2 is forwarded to port2. While the frame without the matched dstaddr will be broadcasted.

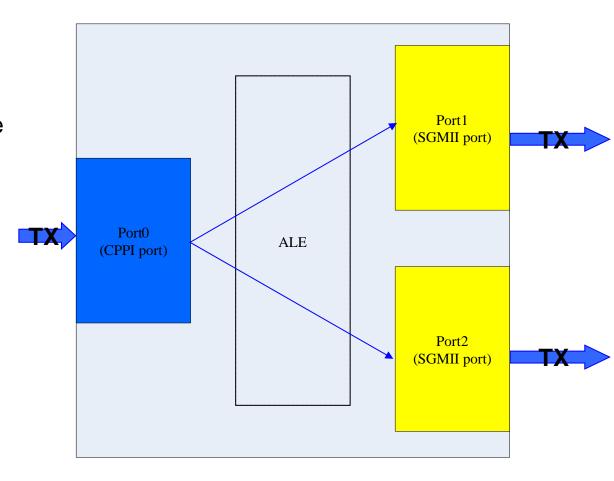

### **GbE Switch – Direct Packet**

Only for transmit packet output from port0, the packet can be sent to the specified port1 or port2 directly through setting the ps\_flag in the descriptor.

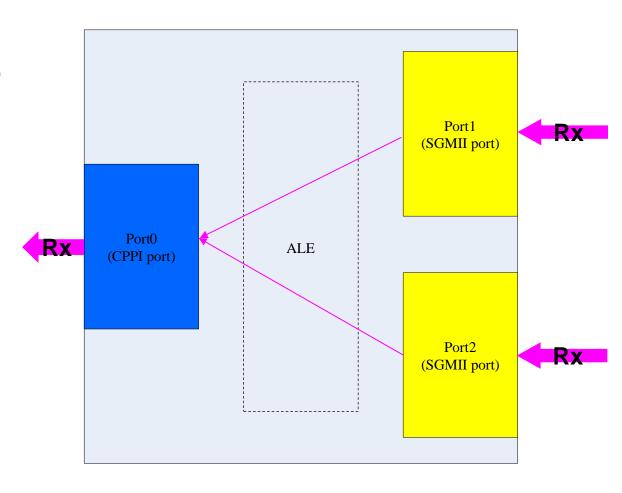

# **GbE Switch – ALE Bypass Mode**

Only for received packet from port1 or port2, the received packet is sent to port0 directly

### **GbE Switch – MAC**

Flow control is enabled by setting the RX\_FLOW\_EN or the TX\_FLOW\_EN bit in the MAC\_CONTROL register, and the flow control event is triggered by configure the MAC receive FIFO by host

#### Receive flow control

- For half-duplex mode, generate a collision sequence for received frames to prevent frame reception.

- For full-duplex mode, send a pause frame with multicast destination address and set the source address with the MAC address to make all the station stop sending frame to the received port within the indicated period.

#### Transmit flow control

Only support for full-duplex mode, incoming pause frame with destination address equal to multicast address or the MAC address of the switch port to be controlled, and set the source address equal to the transmit device to make the source MAC port stop transmitting frame.

## **SGMII**

- Support Operation Modes

- Digital Loopback Mode

- SGMII to PHY

- SGMII to SGMII with auto-negotiation

- SGMII to SGMII with forced link

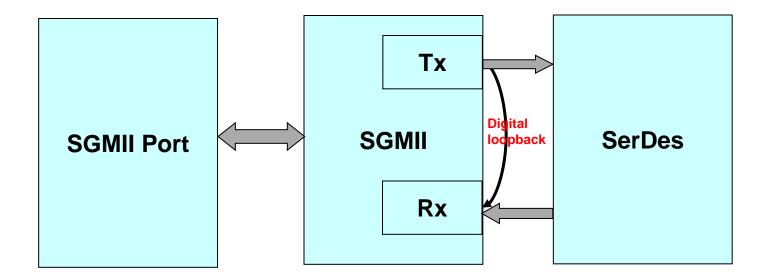

# **SGMII** – Digital loopback

Transmit and receive signals are connected before reaching SerDes module.

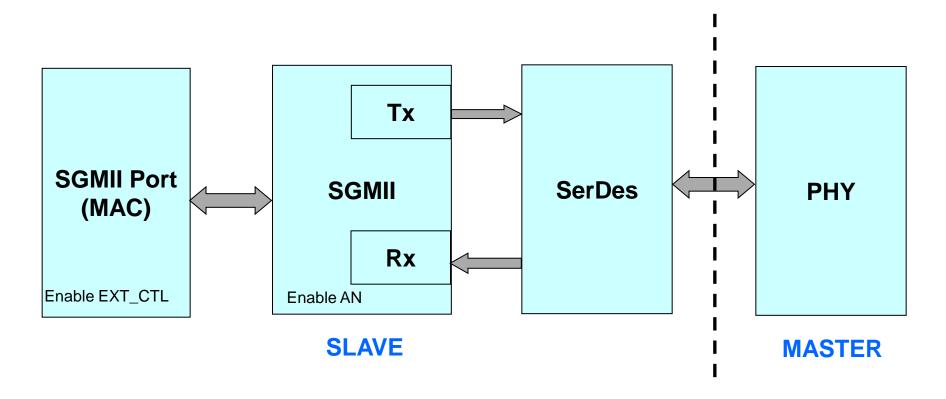

### SGMII – SGMII to PHY

Configure external PHY device as master, while SGMII as the slave.

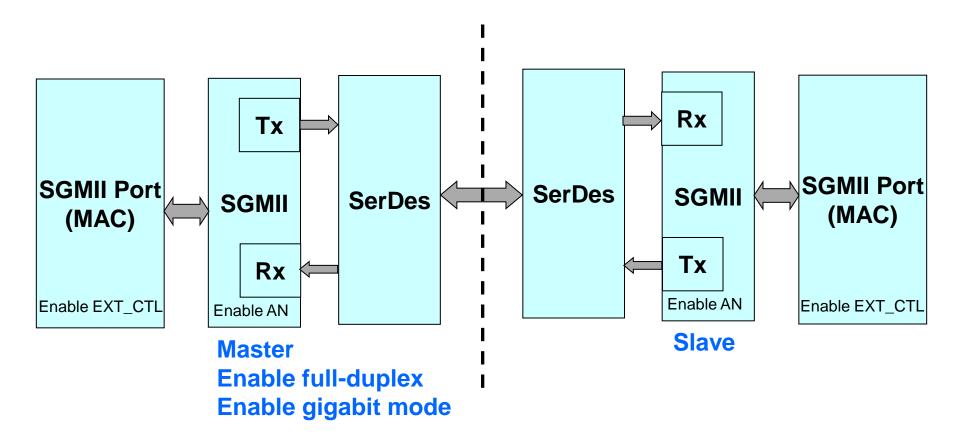

## SGMII – SGMII to SGMII with auto-negotiation

Configure one SGMII as the master, while the other as the slave.

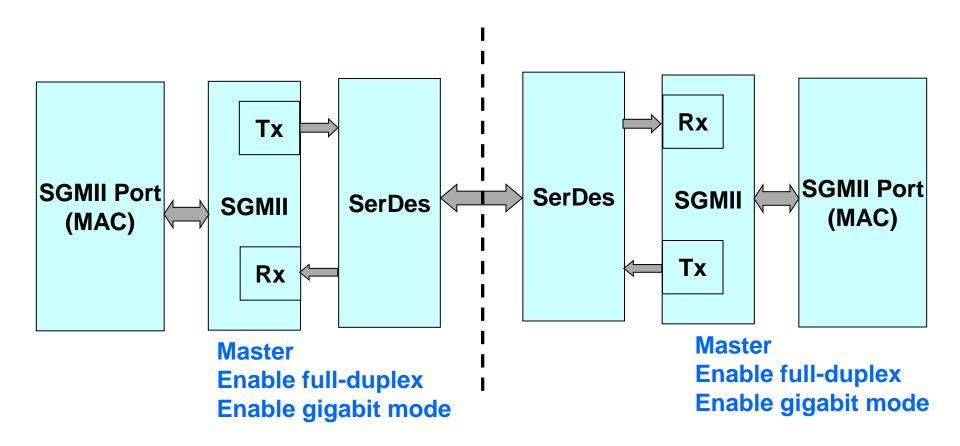

### SGMII – SGMII to SGMII with forced link

Configure both SGMII as master.

#### **MDIO**

- Connect up to 32 PHY devices

- Store the connected PHY devices' link state in the ALIVE and LINK register

- Monitor Process

- Set two PHY devices to be monitored simultaneously, enable interrupt for link status change

- When generate link status change interrupt, the host can read or write the related PHY device's link status register

- Set another two PHY devices to be monitored.

#### **GbE Switch Initialization Procedure**

- Configure the SerDes PLL, TX/RX registers

- Configure the SGMII\_CONTROL and MR\_ADV\_ABILITY register to establish a link and autonegotiation

- Configure the MAC1\_SA and MAC2\_SA source address hi and lo registers for flow control

- Configure the MAC\_CONTROL, and MAC\_RX\_MAXLEN register to enable GMII, Gigabit, and flow control and set the receive maximum length

- Enable the desired statistics ports by programming the CPSW\_STAT\_PORT\_EN register

- Configure the CPSW\_CONTORL register to enable the switch port

- Configure the ALE, can be set as bypass mode for simple test

### **GbE Switch Tx/Rx**

- Transmit data through EMAC, push the descriptor with linked buffer to TXQ648

- Receive data from external devices through EMAC

- The packet can be routed to PA according to the below CPSW\_CFG\_REG. At reset the PA is set as bypass mode, and the received packet is routed out to the CPU through the PA CPPI channel22(flow 22) for TXTA, and channel23(flow 23) for TXTB.

| Bit   | Name     | Туре | Reset | Description                                                                                                                                                                             |

|-------|----------|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31-11 | Reserved | R    | 0     | Reserved.                                                                                                                                                                               |

| 10-8  | TXSTB    | RW   | 6     | This field maps the CPSW TXSTB port to a packet DMA channel.  Register default value is 6.  0 = PDSP0  1 = PDSP1  2 = PDSP2  3 = PDSP3  4 = PDSP4  5 = PDSP5  6 = Packet DMA channel 23 |

| 7-3   | Reserved | R    | 0     | Reserved.                                                                                                                                                                               |

| 2-0   | TXSTA    | RW   | 6     | This field maps the CPSW TXSTA port to a packet DMA channel.  Register default value is 6.  0 = PDSP0  1 = PDSP1  2 = PDSP2  3 = PDSP3  4 = PDSP4  5 = PDSP5  6 = Packet DMA channel 22 |

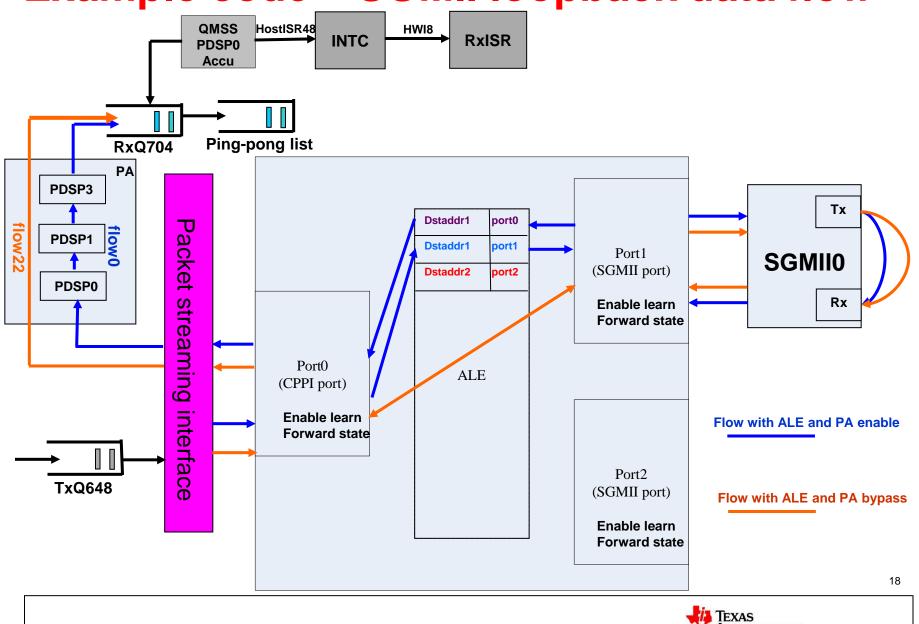

# Example code – SGMII loopback data flow

INSTRUMENTS

# PC-EMAC communication example based on TN EVM (C5)

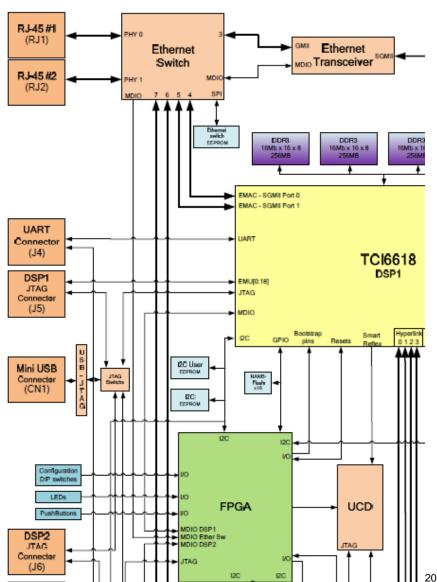

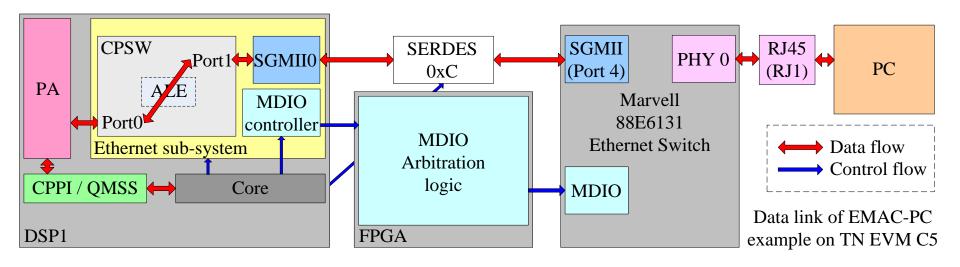

## Hardware diagram and data link

- Hardware diagram

- Ethernet sub-system SGMII port connect with Marvell switch SGMII port through SERDES

- Marvell switch PHY port configured by DSP1 through MDIO in Marvell switch and MDIO arbitration logic in FPGA

- MDIO arbitration logic in FPGA guaranteed only one DSP can be the MDIO controller at any given time

# Hardware diagram and data link

Data link

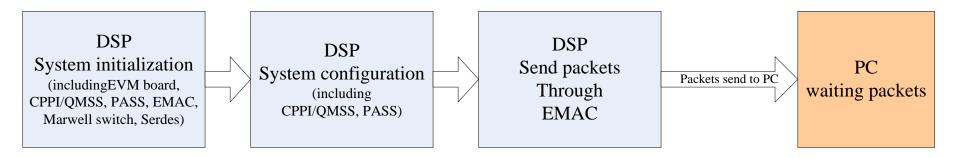

# Example code processing flow (TX)

#### **Transimt**

- Set ALE bypass mode (data from SGMII fort of EMAC can only be received by PKTDMA port)

- Configure link between EMAC SGMII port and Marvell switch SGMII port as Force Link without Auto Negotiation

- Send packets from PKTDMA to SGMII with specified port (set TO\_PORT bit of PS flag in descriptor) instead of using ALE

- Enable ALE Self-learning function and print ALE's entry to see the record

- Use Ethernet sniffer software (WireShark) to parser received packets

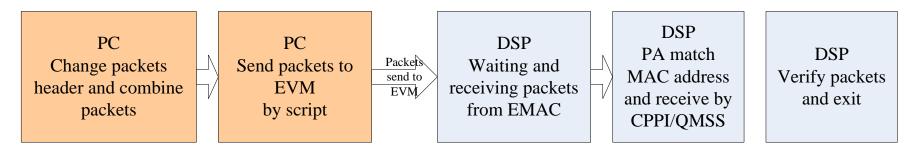

# Example code processing flow (RX)

#### Receive

- PA only match MAC destination address to decide whether receive the packet or not in this example

- Use Ethernet sniffer software (WireShark) to check whether the script sent on the right device or not

- Example code provide ALE entry print function, which can be used for checking EMAC routing information