**TPS92070** ZHCS457 – AUGUST 2011

# 高性能集成调光LED照明控制器 查询样品: TP\$92070

## 特性

- 高级集成调光接口

- 非耗散 TRIAC 调光器管理

- 在调光时保持光源的一致性

- 没有低频光照度波动

- 指数调光特性

- 创新型次面反馈消除光耦合器设备

- LED 电流调节优于 5%

- 可编程最小LED电流

- 用于减少的EMI和改进的效能的DCM操作

- 前沿调光器检测

- 功率因子 > 0.8

- 逐周期电流限制

- 低启动电流及工作电流

- 集成 PWM MOSFET 驱动器

- 热关断

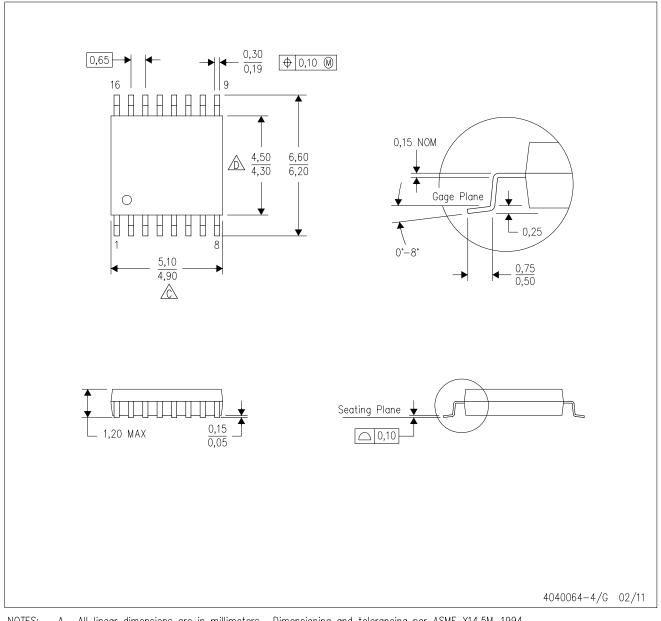

- 16-引脚, TSSOP 封装

#### 应用范围

- **LED** 照明灯

- LED 光源

- **LED** 聚光灯

- LED 投光灯

#### 说明

TPS92070 是一款高级PWM控制器,非常适合在低功率、离线、LED照明应用中使用。TPS92070 的集成调光接口电路特有一个非耗散的调光器触发控制电路。TPS92070 控制器提供没有光照度波动效应的 DC LED 电流。DC 电流也会使LED的效能更高。TPS92070 根据外部调光器的位置提供指数控制光照输出。高功率因子经由填谷式电路实现。一旦检测到前沿调光器,TPS92070 就设定一个输出以关闭PFC电路并由此优化驱动器运行。LED 电流感应精度错误放大器实现深度调光。TPS92070 电流感应结构提供紧密电流调节并消除对光耦合器的需要。紧密电流调节在单个照明或光源间允许强大的颜色和强度匹配节允许。

**TPS92070** 也含有多种保护特性,包括逐周期峰值电流限制、过载电流保护、开放式-LED(输出过压)保护、低压闭锁和热关断。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

**TPS92070** ZHCS457 – AUGUST 2011

www.ti.com.cn

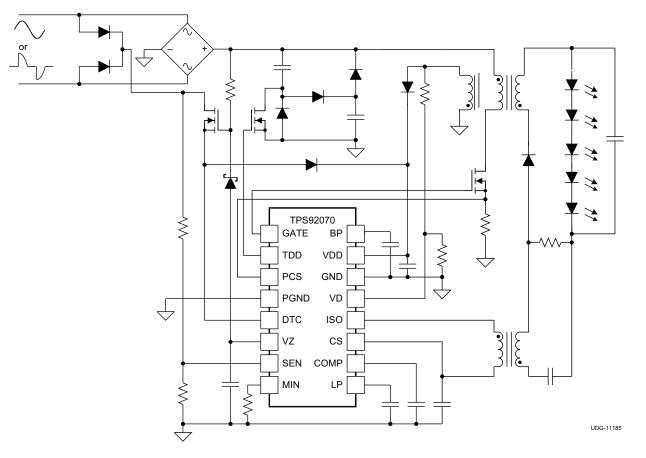

# **APPLICATION DIAGRAM**

# RUMENTS

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

|  | TEMPERATURE<br>RANGE (T <sub>J</sub> ) | PACKAGE       | PINS | TRANSPORT<br>MATERIAL | UNITS | ORDERABLE<br>NUMBER |  |  |  |  |

|--|----------------------------------------|---------------|------|-----------------------|-------|---------------------|--|--|--|--|

|  | –40°C to 140°C                         | Plastic TSSOP | 16   | Tube                  | 70    | TPS92070PW          |  |  |  |  |

|  |                                        | Plastic 1550P | 16   | Tape and Reel         | 2000  | TPS92070PWR         |  |  |  |  |

### ODDEDING INFORMATION(1)(2)

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI (1)website at www.ti.com.

Package drawings, thermal data, and symbolization are available at www.ti.com/packaging (2)

### ABSOLUTE MAXIMUM RATINGS<sup>(1)(2)(3)</sup>

All voltages are with respect to GND, -40°C < T<sub>J</sub> = T<sub>A</sub> < 125°C, all currents are positive into and negative out of the specified terminal (unless otherwise noted)

|                                               |                                |                   | VALU | E     |    |

|-----------------------------------------------|--------------------------------|-------------------|------|-------|----|

|                                               |                                | -                 | MIN  | UNITS |    |

| Supply voltage                                | VDD <sup>(4)</sup>             |                   | -0.3 | 25.0  |    |

|                                               | ISO, CS, COMP, LP, MIN, SEN, F | PCS               | -0.3 | 7.0   |    |

| lanut valta est                               | BP, GATE, TDD                  |                   | -0.3 | 7.2   |    |

| Input voltages                                | VD                             |                   | -1.4 | 7.0   |    |

|                                               | VZ, DTC <sup>(5)</sup>         | -0.3              | 20.0 |       |    |

|                                               | VZ (pulse < 1 ms)              | VZ (pulse < 1 ms) |      |       |    |

|                                               | BP                             |                   | -0.5 | 0     |    |

| Input current                                 | DTC                            | Peak              |      | 30    | mA |

|                                               | DTC                            | Average           |      | 16    |    |

|                                               | VDD                            |                   | 5    |       |    |

| Operating junction temperature <sup>(6)</sup> |                                |                   | -40  | 140   | °C |

| Storage temperature <sup>(6)</sup>            |                                |                   | -65  | 150   | °C |

| Lead temperature (10 seconds)                 |                                |                   |      | 260   | °C |

(1) These are stress ratings only. Stress beyond these limits may cause permanent damage to the device. Functional operation of the device at these or any conditions beyond those indicated under Recommended Operating Conditions is not implied. Exposure to absolute maximum rated conditions for extended periods of time may affect device reliability

All voltages are with respect to GND.

All currents are positive into the terminal, negative out of the terminal. (3)

VDD clamped at approximately 23 V. See ELECTRICAL CHARACTERISTICS table. VZ clamped at approximately 12.5 V. See ELECTRICAL CHARACTERISTICS table. (4)

(5)

(6) Higher temperature may be applied during board soldering process according to the current JEDEC J-STD-020 specification with peak reflow temperatures not higher than classified on the device label on the shipping boxes or reels.

ZHCS457-AUGUST 2011

www.ti.com.cn

# **RECOMMENDED OPERATING CONDITIONS**

Unless otherwise noted, all voltages are with respect to GND,  $-40^{\circ}C < T_J = T_A < 125^{\circ}C$ .

|                  |                                                   | MIN                 | TYP | MAX  | UNIT |

|------------------|---------------------------------------------------|---------------------|-----|------|------|

| VDD              | Input Voltage                                     | 9                   |     | 21.5 | V    |

| VZ               | Current                                           | 1                   |     | 100  | μA   |

| R <sub>MIN</sub> | Resistor from MIN to GND <sup>(1)</sup>           | 25                  |     | 75   | kΩ   |

| $R_{VD1}$        | Valley detect resistor from AUX winding to VD pin | 50                  |     | 200  | kΩ   |

| C <sub>VZ</sub>  | VZ bypass capacitor                               | 1                   |     | 4.7  | nF   |

| C <sub>BP</sub>  | BP capacitor                                      | 0.47                | 1   |      | μF   |

| $C_{VDD}$        | VDD capacitor                                     | 10×C <sub>BP7</sub> | 4.7 |      | μF   |

| $C_{VDD,BP}$     | VDD bypass capacitor, ceramic <sup>(2)</sup>      | 0.1                 |     |      | μF   |

(1) R<sub>MIN</sub> values greater than 75K will produce lower minimum current values. However accuracy of the minimum current will degrade, and there may be flickering at very low values of Imin.

(2) If a ceramic capacitor is used for  $C_{VDD}$  then this capacitor is not needed.

# **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

|                                        | MAX | UNIT |

|----------------------------------------|-----|------|

| ESD Rating, Human Body Model (HBM)     | 1.5 | kV   |

| ESD Rating, Charged Device Model (CDM) | 500 | V    |

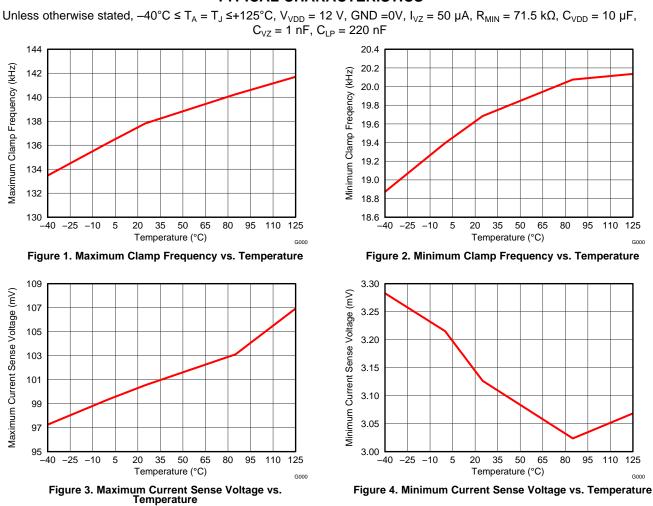

# **ELECTRICAL CHARACTERISTICS**

Unless otherwise stated, -40°C <  $T_A$  < 125°C,  $T_J$  =  $T_A$ ,  $V_{VDD}$  = 12 V, GND =0 V,  $I_{VZ}$  = 50 µA,  $R_{MIN}$  = 71.5 k $\Omega$ ,  $C_{VDD}$  = 4.7µF,  $C_{BP}$  = 1 µF,  $C_{LP}$  = 220nF

|                         | PARAMETER                                   | TEST CONDITIONS                                                                                                    | MIN        | TYP  | MAX   | UNITS |

|-------------------------|---------------------------------------------|--------------------------------------------------------------------------------------------------------------------|------------|------|-------|-------|

| BIAS and S              | TARTUP                                      |                                                                                                                    |            |      |       |       |

| I <sub>START</sub>      | VZ startup current                          | $V_{VDD}$ = 7 V, Measured I <sub>VZ</sub>                                                                          |            | 1.0  | 10    | μA    |

| V <sub>VZ</sub>         | VZ voltage                                  | $V_{VDD}$ = 7 V, 15 µA < I <sub>VZ</sub> < 100 µA                                                                  | 11.5       | 12.5 | 13.5  | V     |

|                         | VDD startup current                         | V <sub>VDD</sub> = 7.5 V                                                                                           |            | 134  | 240   |       |

| I <sub>VDD</sub>        | Standby current                             | $V_{LP} = 0 V, V_{SEN} = 0 V$                                                                                      |            | 750  | 1500  | μA    |

|                         | Switching current                           | fG <sub>ATE</sub> = 138 kHz, GATE – unloaded                                                                       |            | 1880 | 2500  |       |

| V <sub>VDD(uvlo)</sub>  | VDD UVLO threshold                          | Measured at VDD (falling)                                                                                          | 7          | 7.88 | 8.4   | V     |

| V <sub>VDD(ovp)</sub>   | VDD clamp and OVP                           | Measured at VDD (rising)                                                                                           | 21.5       | 23.5 | 25    | V     |

| R <sub>VZ(ovp)</sub>    | OVP VZ discharge resistance                 | $V_{VDD} = V_{VDD(ovp)}, VZ = 3 V$                                                                                 |            | 4.8  |       | kΩ    |

| V <sub>BP</sub>         | BP Regulation voltage                       | $9 V < V_{VDD} < 19V, I_{BP} = -0 \mu A$                                                                           | 6.7        | 7    | 7.2   | V     |

| DIMMER TR               |                                             | •                                                                                                                  |            |      |       |       |

| V <sub>SEN(hi)</sub>    | D'arrest threads ald                        | Measured at SEN (rising)                                                                                           | 4.75       | 5    | 5.25  |       |

| V <sub>SEN(lo)</sub>    | <ul> <li>Dimmer sense thresholds</li> </ul> | Measured at SEN (falling)                                                                                          | 0.9        | 1    | 1.10  | V     |

| V <sub>SEN(clamp)</sub> | SEN Clamp voltage                           | I <sub>SEN</sub> = 100 μA                                                                                          | 5.75       | 6    | 6.25  | V     |

| I <sub>DTC(lkg)</sub>   | DTC to PGND leakage current                 | $V_{\text{DTC}}$ = 12 V, $V_{\text{SEN}}$ > $V_{\text{SEN}(hi)}$                                                   |            | 40   | 100   | nA    |

|                         |                                             | V <sub>DTC</sub> = 3 V, V <sub>SEN</sub> (falling), V <sub>SEN(lo)</sub> < V <sub>SEN</sub> < V <sub>SEN(hi)</sub> | 16         | 20   | 25    | kΩ    |

| R <sub>DTC(pgnd)</sub>  | DTC to PGND resistance                      | V <sub>DTC</sub> = 3 V, V <sub>SEN</sub> (rising), V <sub>SEN</sub> < V <sub>SEN(hi)</sub>                         | 100        | 156  | 300   | Ω     |

|                         |                                             | V <sub>SEN</sub> < V <sub>SEN(lo)</sub>                                                                            | 100        | 156  | 300   | Ω     |

| CURRENT                 | SETPOINT                                    |                                                                                                                    |            |      |       |       |

| V <sub>MIN</sub>        | MIN regulation voltage                      |                                                                                                                    |            | 2.5  |       |       |

| R <sub>OUT(lp)</sub>    | LP output resistance                        |                                                                                                                    |            | 500  |       | kΩ    |

| V <sub>OH(lp)</sub>     | LP Maximum voltage level                    | $V_{SEN} = 6 V, I_{LP} = 0 \mu A$                                                                                  | 2.9        | 3    | 3.1   | V     |

| V <sub>OL(Ip)</sub>     | LP Minimum voltage level                    | $V_{SEN} = 0 V, I_{LP} = 0 \mu A$                                                                                  | -0.02<br>5 | 0    | 0.025 | V     |

# **ELECTRICAL CHARACTERISTICS (continued)**

Unless otherwise stated, -40°C <  $T_A$  < 125°C,  $T_J$  =  $T_A$ ,  $V_{VDD}$  = 12 V, GND =0 V,  $I_{VZ}$  = 50 µA,  $R_{MIN}$  = 71.5 k $\Omega$ ,  $C_{VDD}$  = 4.7µF,  $C_{BP}$  = 1 µF,  $C_{LP}$  = 220nF

|                         | PARAMETER                                                                        | TEST CONDITIONS                                                                                         | MIN   | TYP  | MAX   | UNITS |

|-------------------------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|------|-------|-------|

| ERROR AM                | PLIFIER                                                                          |                                                                                                         |       |      |       |       |

| V <sub>IOS</sub>        | Input offset voltage                                                             | $5 \text{ mV} < \text{V}_{\text{CS}} < 100 \text{ mV}, \text{V}_{\text{COMP}} = 3 \text{ V}$            |       | ±500 |       | μV    |

| V <sub>COMP(min)</sub>  | Minimum COMP clamp voltage                                                       | $V_{CS}$ = 150 mV, $V_{LP}$ < 3 V                                                                       | 1.45  | 1.53 | 1.60  | V     |

| V <sub>COMP(max)</sub>  | Maximum COMP clamp voltage                                                       | $V_{CS}$ < 100 mV, $V_{LP}$ > 2.1 V                                                                     | 3.6   | 3.7  | 3.8   | V     |

| V <sub>CS(min)</sub>    | Minimum CS reference voltage                                                     | $V_{LP} = 0, R_{MIN} = 71.5 \text{ k}\Omega, T_A = 25^{\circ}\text{C}$                                  | 2.835 | 3.15 | 3.465 | mV    |

| V <sub>CS(max)</sub>    | Maximum CS reference voltage                                                     | $V_{LP} > 2.1 \text{ V}, \text{ T}_{A} = 25^{\circ}\text{C}$                                            | 97    | 100  | 103   | mV    |

| MODULATI                | ON                                                                               |                                                                                                         |       |      |       |       |

| f <sub>CLAMP(max)</sub> | Maximum frequency clamp                                                          | Measured at GATE, $V_{COMP}$ = 3.5 V, $T_A$ = 25°C                                                      | 132   | 138  | 146   |       |

| f <sub>CLAMP(min)</sub> | Minimum frequency clamp                                                          | Measure at GATE, $V_{COMP}$ = 1.53 V, $V_{VD}$ = 0 V, $T_A$ = 25°C                                      | 10    | 20   | 30    | kHz   |

| VALLEY DE               | TECT                                                                             |                                                                                                         |       |      |       | 1     |

|                         |                                                                                  | Measured when GATE is high, $I_{VD} = -15 \ \mu A$                                                      |       | -560 |       |       |

| VD <sub>CLAMP</sub>     | VD clamp                                                                         | Measured when GATE is low and VD is falling                                                             |       | -125 |       | mV    |

| V <sub>VD(en)</sub>     | VD enable threshold                                                              | Minimum peak of resonant valley, $V_{COMP}$ = 1.8 V                                                     | 600   |      |       | mV    |

| V <sub>VD(zc)</sub>     | Zero-crossing detect threshold                                                   | Measured at VD (falling)                                                                                | 80    | 100  | 135   | mV    |

| t <sub>VD(vw)</sub>     | Valley wait timer                                                                | $V_{COMP} > V_{MINF_DET}$ , $V_{VD} = 0$ V, wait time for next<br>PWM pulse with zero-crossing detected | 10    | 12.7 | 14    | μs    |

| I <sub>VD(min)</sub>    | Current required for valley detection                                            |                                                                                                         | -50   |      |       | μA    |

|                         | RENT PROTECTION                                                                  |                                                                                                         |       |      |       | 1     |

| V <sub>PCS(oc)</sub>    | Over current limit                                                               | Measure at PCS (rising), V <sub>COMP</sub> = 4 V                                                        | 670   | 700  | 750   | mV    |

| t <sub>PCS_G1(oc)</sub> | Propagation delay                                                                | Measured between PCS and GATE falling                                                                   | 10    | 64   | 190   | ns    |

| PWM COMP                | PARATOR                                                                          | •                                                                                                       |       |      |       |       |

| t <sub>LEB</sub>        | Leading edge blanking                                                            | Measured at GATE, $V_{COMP}$ = 3.5 V                                                                    | 180   | 220  | 300   | ns    |

| V <sub>PWM(max)</sub>   |                                                                                  | $V_{COMP} = V_{COMP(max)}$                                                                              |       | 600  | 650   |       |

| V <sub>PWM</sub>        | PWM thresholds                                                                   | V <sub>COMP</sub> = 3.5 V                                                                               | 460   | 500  | 550   |       |

| V <sub>PWM(min)</sub>   | _                                                                                | Measured at PCS rising, COMP ≤ 2 V                                                                      | 40    | 65   | 80    | mV    |

| t <sub>PCS_G1(cl)</sub> | Propagation delay                                                                | Measured between PCS and GATE falling                                                                   | 10    | 54   | 120   | ns    |

| LED ISOLA               | TED CURRENT SENSE                                                                |                                                                                                         |       |      |       |       |

| R <sub>ISO(pd)</sub>    | Pull down resistance                                                             | GATE is high                                                                                            | 240   | 270  | 350   | Ω     |

| PWM OUTP                | PUTS                                                                             |                                                                                                         |       |      |       |       |

| V <sub>GATE(oh)</sub>   | Output voltage high                                                              | Manageral at OATE                                                                                       | 6.7   | 7    | 7.2   |       |

| V <sub>GATE(ol)</sub>   | Output voltage low                                                               | Measured at GATE                                                                                        | -0.01 | 0    | 0.01  | V     |

| t <sub>FALL(pwm)</sub>  | Fall time                                                                        | $C_{GATE} = 1 \text{ nF}, T_A = 25^{\circ}C$                                                            |       | 43   | 70    |       |

| t <sub>RISE(pwm)</sub>  | Rise time                                                                        | $CG_{ATE} = 1 \text{ nF}, T_A = 25^{\circ}C$                                                            |       | 105  | 155   | ns    |

| TRIAC DIM               | MER DETECTION                                                                    |                                                                                                         |       |      |       |       |

| V <sub>TDD(oh)</sub>    | Output voltage high                                                              | Measured at TDD                                                                                         | 6.7   | 7    | 7.2   |       |

| V <sub>TDD(ol)</sub>    | Output voltage low                                                               |                                                                                                         | -0.01 | 0    | 0.01  | V     |

| t <sub>FALL(tdd)</sub>  | Fall time                                                                        | C <sub>TDD</sub> = 1 nF                                                                                 |       | 120  | 190   |       |

| t <sub>RISE(tdd)</sub>  | Rise time                                                                        | C <sub>TDD</sub> = 1 nF                                                                                 |       | 130  | 220   | ns    |

| t <sub>DLY_1V_5V</sub>  | Minimum delay from 1V to 5V SEN<br>signal transitions for no dimmer<br>detection |                                                                                                         | 105   | 135  | 170   | μs    |

|                         |                                                                                  | -                                                                                                       | 1     |      |       |       |

**TPS92070** ZHCS457 – AUGUST 2011

TEXAS INSTRUMENTS

www.ti.com.cn

#### **DEVICE INFORMATION**

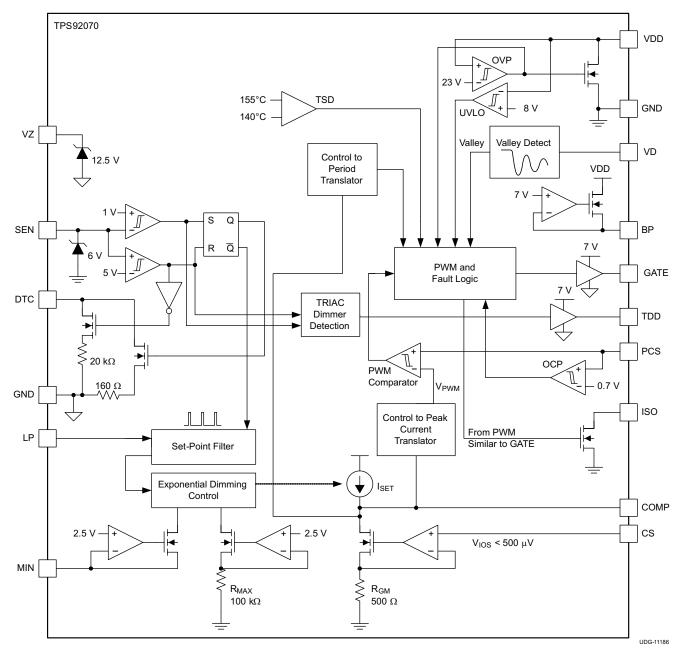

#### FUNCTIONAL BLOCK DIAGRAM

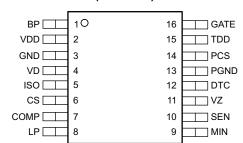

#### TPS92070 PW (TSSOP) PACKAGE (TOP VIEW)

#### **PIN DESCRIPTIONS**

| PIN  |     | DESCRIPTION                                                                                                                                |  |  |  |  |  |  |

|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| NAME | NO. | DESCRIPTION                                                                                                                                |  |  |  |  |  |  |

| BP   | 1   | Connect a 1-uF ceramic capacitor to GND to bypass the internal voltage regulator.                                                          |  |  |  |  |  |  |

| COMP | 7   | Loop compensation output. Connect the loop compensation components between this pin and GND                                                |  |  |  |  |  |  |

| CS   | 6   | LED current sense feedback and positive input terminal of the error amplifier.                                                             |  |  |  |  |  |  |

| DTC  | 12  | Dimmer trigger control input. Connect this pin to thesource of the HV N-channel MOSFET cascode device of the DTC circuit.                  |  |  |  |  |  |  |

| GATE | 16  | PWM drive signal output. Connect to flyback power MOSFET.                                                                                  |  |  |  |  |  |  |

| GND  | 3   | Ground for internal circuitry                                                                                                              |  |  |  |  |  |  |

| ISO  | 5   | Inverting input of secondary side current sense comparator and isolation transformer buffer. Connect to GND for non-isolated applications. |  |  |  |  |  |  |

| LP   | 8   | Pole for DTC low pass filter. Connect a capacitor to GND to set the response time of the dimming level detection circuit.                  |  |  |  |  |  |  |

| MIN  | 9   | Minimum current programming input. Connect a resistor to GND to set the minimum LED current.                                               |  |  |  |  |  |  |

| PCS  | 14  | Primary current sense input. Connected to shunt resistor for primary side current sense.                                                   |  |  |  |  |  |  |

| PGND | 13  | Power ground for GATE Driver. Connected to GND <sup>(1)</sup>                                                                              |  |  |  |  |  |  |

| SEN  | 10  | Dimmer sense input. An internal window comparator continuously monitors this pin to determine the dimmer setting.                          |  |  |  |  |  |  |

| TDD  | 15  | TRIAC dimmer detect. Drives bypass FET in Valley Fill PFC when dimmer is detected. For non PFC applications, leave this pin open           |  |  |  |  |  |  |

| VD   | 4   | Valley detect input. Connect to the Aux winding through a resistor divider.                                                                |  |  |  |  |  |  |

| VDD  | 2   | Provides power to the device. Connect a bypass capacitor directly to GND. See RECOMMENDED OPERATING CONDITIONS for suggested values.       |  |  |  |  |  |  |

| VZ   | 11  | Voltage clamp. This pin clamps the maximum voltage on the gate of the external HV DTC N-channel MOSFET.                                    |  |  |  |  |  |  |

(1) See Application Section for layout recommendations

**TPS92070** ZHCS457-AUGUST 2011 ISTRUMENTS

EXAS

www.ti.com.cn

#### **TYPICAL CHARACTERISTICS**

#### APPLICATIONS

#### STARTUP BIAS AND UVLO

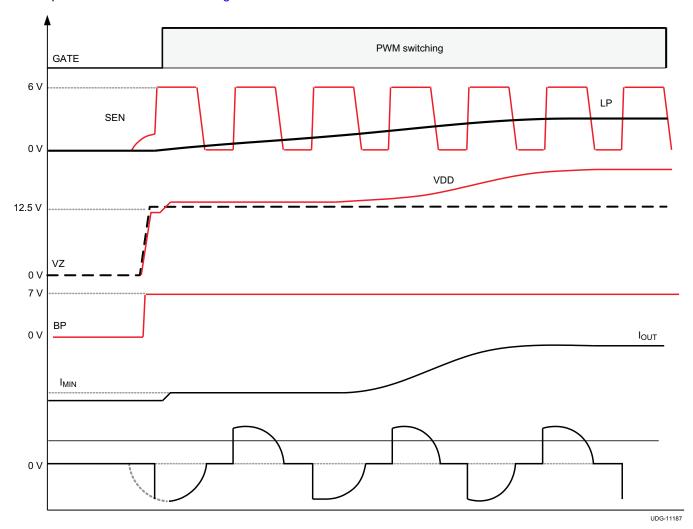

During powerup when VDD is less than the UVLO threshold of 8 V, the VZ pin is trickle charged with  $I_{VZ(start)}$  of approximately 10 µA through the startup-resistor connected to the bulk rectified voltage. As VZ is being charged, VDD tracks VZ (less  $V_{GSTH}$ ) through the external cascode HV MOSFET (Q1) supplying a VDD startup current of 135 µA. Once VZ reaches the TPS92070 zener clamp regulation level of 12.5 V, the device enters into a stand-by mode during which the dimmer trigger circuit (DTC), set-point filter, 7-V bias regulator, and a minimal amount of housekeeping circuitry is active. The TPS92070 remains in this state until the SEN pin exceeds 5 V indicating that adequate line voltage is present, either through TRIAC firing, or line voltage presence. The typical start-up waveforms are shown in Figure 5.

Figure 5. Typical Startup Waveforms for a TRIAC Triggered VIN(ac) Input

#### **DTC and PHASE DETECTION**

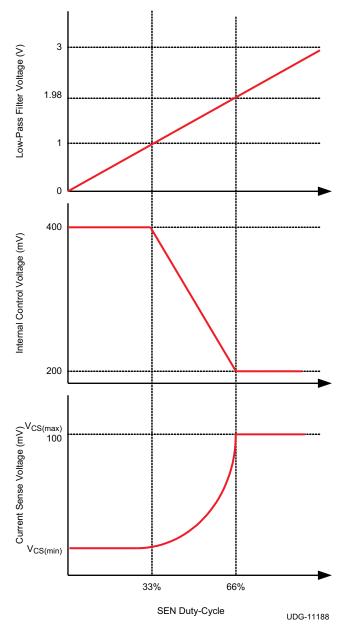

The DTC pin is a current sink which loads the dimmer with approximately 20 mA during the zero-crossing of the AC line to ensure that the TRIAC is reliably triggered. This current sink is switched on when the voltage on the SEN pin is below 5 V. The setpoint filter in conjunction with the SEN and LP pins is used to determine the firing angle of the TRIAC dimmer (if any) connected to the input of the LED driver. An internal window comparator monitors the SEN (dimmer sense input) pin and the resulting duty-cycle is transformed into a voltage at the LP pin using the LP filter. The relation between the TRIAC firing angle and the LP voltage is shown in Figure 6. It illllustrates the conversion of the TRIAC firing angle to LP voltage and exponential dimming control of I<sub>SET</sub> based on internal control voltage. As the voltage on the LP varies from 0 V to 3 V based on the mapping of 0% to 100% SEN duty-cycle, an internal control voltage is linearly modulated by TPS92070 from 400 mV to 200 mV.

Figure 6. TRIAC Firing Angle vs. Low-Pass Filter Voltage

The internal control voltage, V<sub>CTRL</sub> is clamped to 0.4 V for LP < 1 V and clamped to 0.2 V for LP > 1.98V. As the control voltage is linearly modulated between 0.4 V and 0.2 V, the current sense reference voltage V<sub>CS</sub> is exponentially controlled between the pre-set maximum of 100 mV and the externally programmed minimum limit of V<sub>CS MiN</sub>. The current setpoint level, V<sub>CS MiN</sub> is programmed by R<sub>MIN</sub>.

$$V_{CS(min)} = \frac{225}{R_{MIN}}$$

(1)

The exponential control of the set-point current extends the dimming control range and enables up to two decades of LED current-programming between the  $V_{CS(min)}$  and  $V_{CS(max)}$  = 100 mV levels.

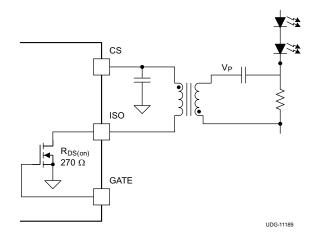

#### LED CURRENT SENSE

The secondary-side LED current is sensed using the CS pin and tightly regulated using the low-offset (500  $\mu$ V) transconductance amplifier. The transconductance (g<sub>M</sub>) of the amplifier is internally set to approximately g<sub>M</sub> = 1/500 S. In the direct current-sense mode (non-isolated), the ISO pin is connected to GND. In the isolated-mode, the secondary-side LED current is sensed using a small transformer with the secondary of the transformer connected between CS and ISO pins as shown in Figure 7. The ISO pin has a switched pull-down resistance of 270  $\Omega$ .

Figure 7. Isolated Current Sense

#### MODULATION

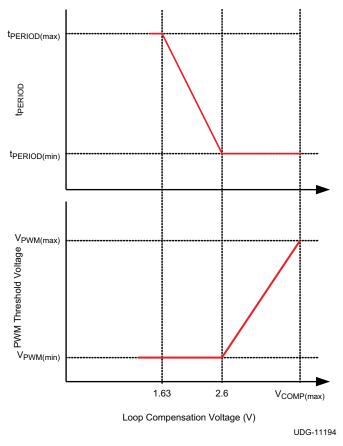

The internal I<sub>SET</sub> current and RGM sets a reference input for the transconductance current sense amplifier which controls the voltage on the COMP pin. The COMP pin is used for loop compensation. The voltage on the COMP pin modulates the peak of the primary current and the switching frequency (frequency modulation) of the flyback converter. The modulation on the primary current and the switching frequency are shown in Figure 8. The peak of the primary current is modulated by varying the threshold on the PWM comparator. The threshold is modulated from 0.6 V to 0.065 V while the switching frequency varies between 20 kHz and 138 kHz as COMP pin varies from 3.7 V to 2.6 V. The maximum COMP pin voltage is clamped at 3.7 V allowing the maximum cycle-by-cycle peak current limit PWM threshold to be 0.6 V. The switching frequency is linearly modulated from 138 kHz to 20 kHz with the PWM threshold clamped at 0.065 V as the COMP pin varies from 2.6 V to 1.63 V. The minimum frequency is clamped at 20 kHz and TPS92070 enters the minimum frequency detect state for COMP <1.6 V. The minimum voltage on the COMP is clamped at 1.53 V. The PWM threshold is related to the COMP pin voltage as shown in Equation 2 and Equation 3.

For  $2.6 \leq V_{COMP} \leq 3.7$ ,

$$V_{PWM} = \frac{V_{COMP} - 2.5}{2}$$

For  $V_{COMP} < 2.6 V$ ,  $V_{PWM} = 0.065$  (2)

(3)

Figure 8. Switching Period and PWM Threshold Modulation Based on COMP pin Voltage

## PRIMARY CURRENT SENSE

The primary current is sensed by monitoring the voltage developed across an external current-sense resistor connected between the source of the external HV MOSFET and PGND. The PCS pin is used for monitoring the voltage and it is then compared with the PWM threshold ( $V_{PWM}$ ). The PWM comparator has a leading-edge blanking time of 220 ns to avoid any false-tripping of the comparator due to capacitive charge spikes on the PCS pin. The GATE output is pulled low once the PCS pin reaches the PWM threshold.

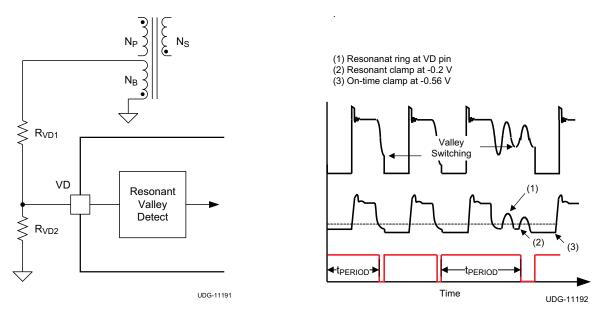

#### VALLEY DETECT

TPS92070 ensures that the flyback converter always operates in either DCM or QR mode of operation and initiates a new PWM switching cycle only after the energy in the flyback transformer is completely reset to zero. This is accomplished by monitoring the auxiliary winding waveform using a resistive divider connected to the VD pin. The TPS92070 initiates a new switching cycle based on the following conditions:

- For normal operation with 1.63 V ≤ V<sub>COMP</sub> ≤ 3.7 V, a new PWM switching cycle is initiated when the internal timer t<sub>PERIOD</sub> has expired and the next valley is detected. The VD pin must go below 100 mV (V<sub>VD(zc)</sub>) prior to valley detection to enable the valley detector circuit.

- In the minimum frequency clamp state when  $V_{COMP} < 1.63$  V, the switching period is fixed at  $t_{PERIOD(max)}$  (corresponding to  $f_{CLAMP(min)}$ ) and the valley detector is disabled.

- The relationship of t<sub>PERIOD</sub> to the switching frequency is shown in Equation 4 and Equation 5.

$$f_{\text{CLAMP}(\text{max})} = \frac{1}{t_{\text{PERIOD}(\text{min})}}$$

$$f_{\text{CLAMP}(\text{min})} = \frac{1}{t_{\text{PERIOD}(\text{max})}}$$

(5)

By turning on the flyback power switch at the resonant valley, the switching losses are reduced thereby enabling higher efficiency. The voltage at the VD pin is clamped at –0.56 V during the negative excursions on the AUX winding when GATE is high. When GATE is low and during the resonant valley detection, the VD pin is clamped at –0.2 V. The interface to the VD pin to the AUX winding is shown in Figure 9. The TPS92070 requires that the positive peak of the resonant ring at the VD pin is higher than 0.6 V ( $V_{VD(en)}$ ) to ensure that the valley-detect circuit is enabled for detection on the falling edge when  $V_{COMP} > 1.63$  V. Hence,  $R_{VD2}$  need to be selected in such a way that this condition is met for all AUX voltages when  $V_{COMP} > 1.63$  V. A current  $I_{VD(min)}$  of at least 50 µA must be drawn from the VD pin when the GATE is high to ensure proper valley detection. This requirement determines the value of  $R_{VD1}$ . The waveforms associated with the valley detect are shown in Figure 10. If the voltage at the AUX winding is not sufficient for valley detection when  $V_{COMP} > 1.63$  V, an internal valley wait timer of 12.7 µs ( $t_{VD(vw)}$ ) expires after the  $t_{PERIOD}$  times out. The time out of the valley wait timer would initiate a new PWM switching pulse following the 100 mV threshold crossing on the VD pin.

Figure 9. Auxiliary Winding Interface to VD

Figure 10. HV MOSFET Drain and VD Waveforms

ZHCS457 - AUGUST 2011

## TRIAC DIMMER DETECT

The TDD pin is used to drive an external by-pass FET that disables valley-fill PFC when a dimmer is detected by TPS92070. The TDD pin is set to logic high state ( $V_{TDD(oh)} = 7$  V) as the part is powered up and if no dimmer is detected by continuously sensing the SEN pin, the TDD pin is then reset to logic low ( $V_{TDD(ol)} = 0$  V). The presence of a dimmer is detected by monitoring the time delay in a window between 1 V and 5 V comparators that are monitoring the SEN pin. If the rise time from 1 V to 5 V is greater than 135 µs for four consecutive half-line cycles, direct connection to the AC line without dimmer is assumed, and the TDD output goes low. Otherwise the TDD pin remains high. If the TDD pin is low and the delay time ( $t_{DLY_1V_5V}$ ) is detected to be less than 135 µs, for four consecutive half-line cycles, the TDD pin goes high once the SEN pin falls below 1 V indicating dimmer detection.

#### **PROTECTION FEATURES**

#### **Output Over Voltage Protection (OVP)**

Output (secondary-side) overvoltage protection / open LED detection is achieved by disabling the controller whenever the VDD voltage rises enough to trigger its internal 23 V clamp. Upon OVP detection, GATE is pulled low and the TDD pin is reset to logic-high state. The TPS92070 is disabled and an internal pull-down resistor ( $R_{VZ(ovp)}$ ) discharges the VZ pin, until the VDD voltage drops below the UVLO threshold when a restart is triggered.

#### **Overcurrent Protection (OCP)**

Overcurrent faults are detected when the PCS pin exceeds the internal 700-mV threshold. Upon the detection of an OCP condition, the GATE signal is pulled low, and the LP pin voltage is reset to 0 V corresponding to the minimum LED output condition. GATE switching and current regulation resumes from the minimum LED light setting once the SEN pin crosses the 5 V.

#### Thermal Shutdown (TSD)

TPS92070 is disabled if the junction temperature of the part exceeds approximately 155°C and enters into the restart mode where the VZ pin is discharged until VDD falls below the UVLO threshold. The device stays in this restart mode until the junction temperature falls below approximately 140°C when it resumes normal operation with the light output preset to the minimum setting.

#### **PCB** Layout

Use good layout practices when constructing the PCB. Maintain the location of bypass components close to the pins being bypassed. Route power ground (PGND) separate from signal ground (GND) to keep the high current paths and the small signal paths separate. Connect PGND to GND at a single point, preferably under the device.

www.ti.com

### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|-----------------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-----------------------------|

| TPS92070PW       | ACTIVE                | TSSOP        | PW                 | 16   | 90          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

| TPS92070PWR      | ACTIVE                | TSSOP        | PW                 | 16   | 2000        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND**: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

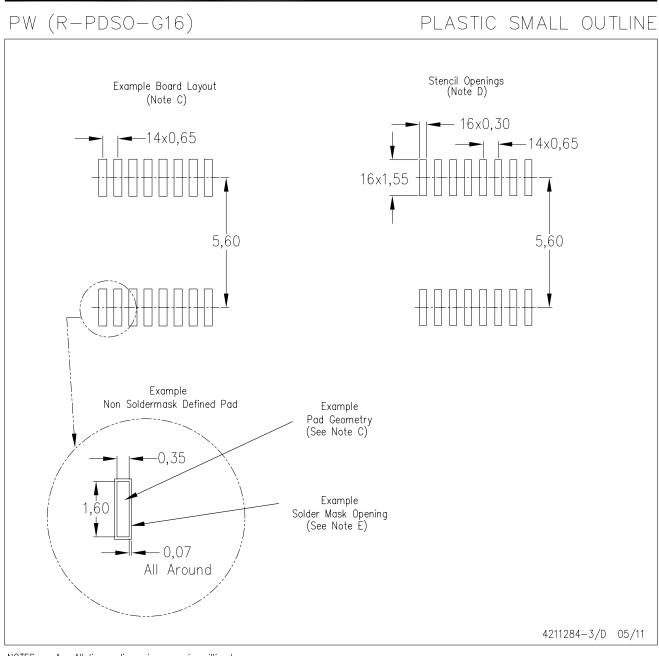

PW (R-PDSO-G16)

PLASTIC SMALL OUTLINE

NOTES:

A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.  $\beta$ . This drawing is subject to change without notice.

Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0,15 each side.

Body width does not include interlead flash. Interlead flash shall not exceed 0,25 each side.

E. Falls within JEDEC MO-153

# LAND PATTERN DATA

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC-7525 for other stencil recommendations.

- E. Customers should contact their board fabrication site for solder mask tolerances between and around signal pads.

#### 重要声明

德州仪器(TI)及其下属子公司有权在不事先通知的情况下,随时对所提供的产品和服务进行更正、修改、增强、改进或其它更改, 并有权随时中止提供任何产品和服务。客户在下订单前应获取最新的相关信息,并验证这些信息是否完整且是最新的。所有产品的 销售都遵循在订单确认时所提供的TI 销售条款与条件。

TI保证其所销售的硬件产品的性能符合TI标准保修的适用规范。仅在TI保证的范围内,且TI认为有必要时才会使用测试或其它质量控制技术。除非政府做出了硬性规定,否则没有必要对每种产品的所有参数进行测试。

TI 对应用帮助或客户产品设计不承担任何义务。客户应对其使用TI 组件的产品和应用自行负责。为尽量减小与客户产品和应用相关的风险,客户应提供充分的设计与操作安全措施。

TI不对任何TI专利权、版权、屏蔽作品权或其它与使用了TI产品或服务的组合设备、机器、流程相关的TI知识产权中授予的直接 或隐含权限作出任何保证或解释。TI所发布的与第三方产品或服务有关的信息,不能构成从TI获得使用这些产品或服务的许可、授 权、或认可。使用此类信息可能需要获得第三方的专利权或其它知识产权方面的许可,或是TI的专利权或其它知识产权方面的许可。

对于TI的产品手册或数据表,仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况下才允许进行复制。在复制信息的过程中对内容的篡改属于非法的、欺诈性商业行为。TI对此类篡改过的文件不承担任何责任。

在转售TI产品或服务时,如果存在对产品或服务参数的虚假陈述,则会失去相关TI产品或服务的明示或暗示授权,且这是非法的、 欺诈性商业行为。TI对此类虚假陈述不承担任何责任。

TI 产品未获得用于关键的安全应用中的授权,例如生命支持应用(在该类应用中一旦TI产品故障将预计造成重大的人员伤亡),除 非各方官员已经达成了专门管控此类使用的协议。购买者的购买行为即表示,他们具备有关其应用安全以及规章衍生所需的所有专业 技术和知识,并且认可和同意,尽管任何应用相关信息或支持仍可能由TI 提供,但他们将独力负责满足在关键安全应用中使用其产品及TI 产品所需的所有法律、法规和安全相关要求。此外,购买者必须全额赔偿因在此类关键安全应用中使用TI产品而对TI 及其代表造成的损失。

TI 产品并非设计或专门用于军事/航空应用,以及环境方面的产品,除非TI 特别注明该产品属于"军用"或"增强型塑料"产品。只有TI 指定的军用产品才满足军用规格。购买者认可并同意,对TI 未指定军用的产品进行军事方面的应用,风险由购买者单独承担, 并且独力负责在此类相关使用中满足所有法律和法规要求。

TI 产品并非设计或专门用于汽车应用以及环境方面的产品,除非TI 特别注明该产品符合ISO/TS 16949 要求。购买者认可并同意,如果他们在汽车应用中使用任何未被指定的产品,TI 对未能满足应用所需要求不承担任何责任。

可访问以下URL 地址以获取有关其它TI 产品和应用解决方案的信息:

| Ī                    | 立品                                        | J                     | 应用                       |

|----------------------|-------------------------------------------|-----------------------|--------------------------|

| 数字音频                 | www.ti.com.cn/audio                       | 通信与电信                 | www.ti.com.cn/telecom    |

| 放大器和线性器件             | http://www.ti.com.cn/amplifiers           | 计算机及周边                | www.ti.com.cn/computer   |

| 数据转换器                | http://www.ti.com.cn/dataconvert<br>ers   | 消费电子                  | www.ti.com/consumer-apps |

| <b>DLP®</b> 产品       | www.dlp.com                               | 能源                    | www.ti.com/energy        |

| DSP - 数字信号处理器        | http://www.ti.com.cn/dsp                  | 工业应用                  | www.ti.com.cn/industrial |

| 时钟和计时器               | http://www.ti.com.cn/clockandtim<br>ers   | 医疗电子                  | www.ti.com.cn/medical    |

| 接口                   | http://www.ti.com.cn/interface            | 安防应用                  | www.ti.com.cn/security   |

| 逻辑                   | http://www.ti.com.cn/logic                | 汽车电子                  | www.ti.com.cn/automotive |

| 电源管理                 | http:///www.ti.com.cn/power               | 视频和影像                 | www.ti.com.cn/video      |

| 微控制器 (MCU)           | http://www.ti.com.cn/microcontroll<br>ers | 无线通信                  | www.ti.com.cn/wireless   |

| RFID 系统              | http://www.ti.com.cn/rfidsys              |                       |                          |

| RF/IF 和 ZigBee® 解决方案 | www.ti.com.cn/radiofre                    |                       |                          |

|                      | TI E2E 工程师社区                              | http://e2e.ti.com/cn/ |                          |

邮寄地址: 上海市浦东新区世纪大道 1568 号,中建大厦 32 楼 邮政编码: 200122 Copyright © 2011 德州仪器 半导体技术(上海)有限公司