# AN-1484 Designing A SEPIC Converter

Dongbing Zhang

#### **ABSTRACT**

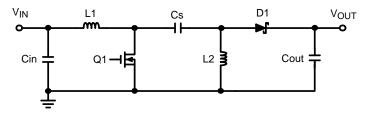

In a single ended primary inductance converter (SEPIC) design, the output voltage can be higher or lower than the input voltage. The SEPIC converter shown in Figure 1 uses two inductors: L1 and L2. The two inductors can be wound on the same core since the same voltages are applied to them throughout the switching cycle.

#### Contents Introduction \_\_\_\_\_\_\_2 2 3 8 9 10 **List of Figures** 1 2 3 4 5

All trademarks are the property of their respective owners.

Introduction www.ti.com

# 1 Introduction

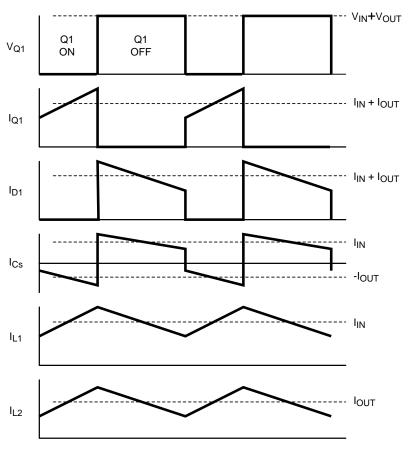

Using a coupled inductor takes up less space on the PCB and tends to be lower cost than two separate inductors. The capacitor Cs isolates the input from the output and provides protection against a shorted load. Figure 2 and Figure 3 show the SEPIC converter current flow and switching waveforms.

Figure 1. SEPIC Topology

Figure 2. SEPIC Converter Current Flow Top: During Q1 On-Time, Bottom: During Q1 Off-Time

Figure 3. SEPIC Converter Switching Waveforms ( $V_{Q1}$ : Q1 Drain to Source Voltage)

# 2 Duty Cycle Consideration

For a SEPIC converter operating in a continuous conduction mode (CCM), the duty cycle is given by:

$$D = \frac{V_{OUT} + V_D}{V_{IN} + V_{OUT} + V_D}$$

(1)

$V_D$  is the forward voltage drop of the diode D1. The maximum duty cycle is:

$$D_{\text{max}} = \frac{V_{\text{OUT}} + V_{\text{D}}}{V_{\text{IN (min)}} + V_{\text{OUT}} + V_{\text{D}}}$$

(2)

## 3 Inductor Selection

A good rule for determining the inductance is to allow the peak-to-peak ripple current to be approximately 40% of the maximum input current at the minimum input voltage. The ripple current flowing in equal value inductors L1 and L2 is given by:

$$\Delta I_{L} = I_{IN} \times 40\% = I_{OUT} \times \frac{V_{OUT}}{V_{IN \text{ (min)}}} \times 40\%$$

(3)

The inductor value is calculated by:

$$L1 = L2 = L = \frac{V_{IN (min)}}{\Delta I_L x f_{sw}} x D_{max}$$

(4)

Power MOSFET Selection www.ti.com

$f_{sw}$  is the switching frequency and  $D_{max}$  is the duty cycle at the minimum  $V_{in}$ . The peak current in the inductor, to ensure the inductor does not saturate, is given by:

$$I_{L1 \text{ (peak)}} = I_{OUT} \times \frac{V_{OUT} + V_{D}}{V_{IN \text{ (min)}}} \times \left(1 + \frac{40\%}{2}\right)$$

(5)

$$I_{L2 \text{ (peak)}} = I_{OUT} \times \left(1 + \frac{40\%}{2}\right)$$

(6)

If L1 and L2 are wound on the same core, the value of inductance in the equation above is replaced by 2L due to mutual inductance. The inductor value is calculated by:

$$L1' = L2' = \frac{L}{2} = \frac{V_{IN (min)}}{2 \times \Delta I_L \times f_{sw}} \times D_{max}$$

(7)

#### 4 Power MOSFET Selection

The parameters governing the selection of the MOSFET are the minimum threshold voltage  $V_{th(min)}$ , the onresistance  $R_{DS(ON)}$ , gate-drain charge  $Q_{GD}$ , and the maximum drain to source voltage,  $V_{DS(max)}$ . Logic level or sublogic-level threshold MOSFETs should be used based on the gate drive voltage. The peak switch voltage is equal to Vin + Vout. The peak switch current is given by:

$$I_{Q1 (peak)} = I_{L1 (peak)} + I_{L2 (peak)}$$

(8)

The RMS current through the switch is given by:

$$I_{Q1 (rms)} = I_{OUT} \sqrt{\frac{(V_{OUT} + V_{IN (min)} + V_D) \times (V_{OUT} + V_D)}{V_{IN (min)}^2}}$$

(9)

The MOSFET power dissipation PQ1 is approximately:

$$P_{Q1} = I_{Q1 \text{ (rms)}}^{2} \times R_{DS \text{ (ON)}} \times D_{max} + (V_{IN \text{ (min)}} + V_{OUT}) \times I_{Q1 \text{ (peak)}} \times \frac{Q_{GD} \times f_{sW}}{I_{G}}$$

(10)

$P_{Q1}$ , the total power dissipation for MOSFETs includes conduction loss (as shown in the first term of the above equation) and switching loss as shown in the second term.  $I_G$  is the gate drive current. The  $R_{DS(ON)}$  value should be selected at maximum operating junction temperature and is typically given in the MOSFET data sheet. Ensure that the conduction losses plus the switching losses do not exceed the package ratings or exceed the overall thermal budget.

# 5 Output Diode Selection

The output diode must be selected to handle the peak current and the reverse voltage. In a SEPIC, the diode peak current is the same as the switch peak current  $I_{Q1(peak)}$ . The minimum peak reverse voltage the diode must withstand is:

$$V_{RD1} = V_{IN (max)} + V_{OUT (max)}$$

(11)

Similar to the boost converter, the average diode current is equal to the output current. The power dissipation of the diode is equal to the output current multiplied by the forward voltage drop of the diode. Schottky diodes are recommended in order to minimize the efficiency loss.

# 6 SEPIC Coupling Capacitor Selection

The selection of SEPIC capacitor, Cs, depends on the RMS current, which is given by:

$$I_{Cs (rms)} = I_{OUT} \times \sqrt{\frac{V_{OUT} + V_{D}}{V_{IN (min)}}}$$

(12)

The SEPIC capacitor must be rated for a large RMS current relative to the output power. This property makes the SEPIC much better suited to lower power applications where the RMS current through the capacitor is relatively small (relative to capacitor technology). The voltage rating of the SEPIC capacitor must be greater than the maximum input voltage. Tantalum and ceramic capacitors are the best choice for SMT, having high RMS current ratings relative to size. Electrolytic capacitors work well for through-hole applications where the size is not limited and they can accommodate the required RMS current rating.

The peak-to-peak ripple voltage on Cs (assuming no ESR):

$$\Delta V_{Cs} = \frac{I_{OUT} \times D_{max}}{Cs \times f_{sw}}$$

(13)

A capacitor that meets the RMS current requirement would mostly produce small ripple voltage on Cs. Hence, the peak voltage is typically close to the input voltage.

# 7 Output Capacitor Selection

In a SEPIC converter, when the power switch Q1 is turned on, the inductor is charging and the output current is supplied by the output capacitor. As a result, the output capacitor sees large ripple currents. Thus the selected output capacitor must be capable of handling the maximum RMS current. The RMS current in the output capacitor is:

$$I_{Cout (rms)} = I_{OUT} \times \sqrt{\frac{V_{OUT} + V_{D}}{V_{IN (min)}}}$$

(14)

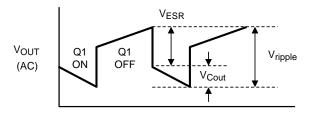

Figure 4. Output Ripple Voltage

The ESR, ESL, and the bulk capacitance of the output capacitor directly control the output ripple. As shown in Figure 4, assume half of the ripple is caused by the ESR and the other half is caused by the amount of capacitance. Hence,

$$ESR \le \frac{V_{\text{ripple}} \times 0.5}{I_{\text{L1 (peak)}} + I_{\text{L2 (peak)}}}$$

(15)

$$Cout \ge \frac{I_{OUT} \times D}{V_{ripple} \times 0.5 \times f_{sw}}$$

(16)

The output cap must meet the RMS current, ESR and capacitance requirements. In surface mount applications, tantalum, polymer electrolytic, and polymer tantalum, or multi-layer ceramic capacitors are recommended at the output.

## 8 Input Capacitor Selection

Similar to a boost converter, the SEPIC has an inductor at the input. Hence, the input current waveform is continuous and triangular. The inductor ensures that the input capacitor sees fairly low ripple currents. The RMS current in the input capacitor is given by:

$$I_{\text{Cin (rms)}} = \frac{\Delta I_{\text{L}}}{\sqrt{12}} \tag{17}$$

The input capacitor should be capable of handling the RMS current. Although the input capacitor is not so critical in a SEPIC application, a 10  $\mu$ F or higher value, good quality capacitor would prevent impedance interactions with the input supply.

# 9 SEPIC Converter Design Example

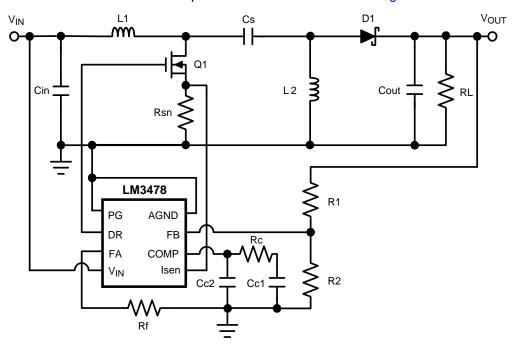

Input voltage ( $V_{IN}$ ): 3.0 V-5.7 V LM3478 controller is used in this example. The schematic is shown in Figure 5.

Output voltage (V<sub>OUT</sub>): 3.3 V

Output current (I<sub>OUT</sub>): 2.5A

Switching frequency f<sub>sw</sub>: 330 kHz

LM3478 controller is used in this example. The schematic is shown in Figure 5.

Figure 5. Schematic

# Step 1: Duty cycle calculation

Assume that the  $V_D$  is 0.5 V,

$$D_{max} = \frac{V_{OUT} + V_{D}}{V_{IN (min)} + V_{OUT} + V_{D}}$$

$$= \frac{3.3 + 0.5}{3.0 + 3.3 + 0.5} = 0.56$$

(18)

$$D_{min} = \frac{V_{OUT} + V_{D}}{V_{IN (max)} + V_{OUT} + V_{D}}$$

$$= \frac{3.3 + 0.5}{5.7 + 3.3 + 0.5} = 0.40$$

(19)

#### Step 2: Inductor selection

The input inductor L1 ripple current is:

$$\Delta I_{L} = I_{OUT} \times \frac{V_{OUT}}{V_{IN (min)}} \times 40\%$$

$$= 2.5 \times \frac{3.3}{3.0} \times 0.4 = 1.1A$$

(20)

and the inductance for L1 and L2 is:

L1 = L2 = L =

$$\frac{V_{IN (min)}}{\Delta I_L \times f_{sw}} \times D_{max}$$

=  $\frac{3.0}{1.1 \times 330k} \times 0.56 = 4.6 \ \mu H$  (21)

The closest standard value of an off-the-shelf inductor is 4.7 µH. The peak input inductor current is:

$$I_{L1 \text{ (peak)}} = I_{OUT} \times \frac{V_{OUT} + V_D}{V_{IN \text{ (min)}}} \times \left(1 + \frac{40\%}{2}\right)$$

$$= 2.5 \times \frac{3.3 + 0.5}{3.0} \times 1.2 = 3.8A$$

(22)

The peak current for L2 is:

$$I_{L2 \text{ (peak)}} = I_{OUT} \times \left(1 + \frac{40\%}{2}\right) = 2.5 \times 1.2 = 3A$$

(23)

#### Step 3: Power MOSFET selection

The MOSFET peak current is:

$$I_{Q1 \text{ (peak)}} = I_{L1 \text{ (peak)}} + I_{L2 \text{ (peak)}}$$

= 3.8 + 3 = 6.8A (24)

and the RMS current is:

$$I_{Q1(rms)} = I_{OUT} \sqrt{\frac{(V_{OUT} + V_{IN(min)} + V_D) \times (V_{OUT} + V_D)}{V_{IN(min)}^2}}$$

$$= 2.5 \times \sqrt{\frac{(3.3 + 3.0 + 0.5) \times (3.3 + 0.5)}{3.0^2}} = 4.2A$$

(25)

The rated drain voltage for the MOSFET must be higher than  $V_{IN}+V_{OUT}$ . Si4442DY ( $R_{DS(ON)}=8~m\Omega$  and  $Q_{GD}=10~nC$ ) is selected in this design. The gate drive current  $I_G$  of the LM3478 is 0.3A. The estimated power loss is:

$$P_{Q1} = I_{Q1 \text{ (rms)}}^{2} \times R_{DS \text{ (ON)}} \times D_{max} + (V_{IN \text{ (min)}})$$

$$+ V_{OUT}) \times I_{Q1 \text{ (peak)}} \times \frac{Q_{GD} \times f_{SW}}{I_{G}}$$

$$= 4.2^{2} \times 8m \times 0.56 + (3 + 3.3) \times 6.8$$

$$\times \frac{10n \times 330k}{0.3} = 0.55W$$

(26)

### Step 4: Output diode selection

The rated reverse voltage of the diode must be higher than V<sub>IN</sub>+V<sub>OUT</sub> and the average diode current is equal to the output current at full load.

#### Step 5: SEPIC coupling capacitor selection

The RMS current of the Cs is:

$$I_{CS (rms)} = I_{OUT} \times \sqrt{\frac{V_{OUT} + V_D}{V_{IN (min)}}}$$

$$= 2.5 \times \sqrt{\frac{3.3 + 0.5}{3.0}} = 2.8A$$

(27)

and the ripple voltage is

$$\Delta V_{Cs} = \frac{I_{OUT} \times D_{max}}{Cs \times f_{sw}} = \frac{2.5 \times 0.56}{10 \mu \times 330 k} = 0.42 V$$

(28)

A 10 µF ceramic cap is selected.

# Step 6: Output capacitor selection

The RMS current of the output capacitor is:

$$I_{\text{Cout}(\text{rms})} = I_{\text{Cs}(\text{rms})} = 2.8A \tag{29}$$

Assuming the peak-to-peak ripple is 2% of the 3.3V output voltage, the ESR of the output capacitor is:

ESR

$$\leq \frac{V_{\text{ripple x }0.5}}{I_{\text{L1(peak)}} + I_{\text{L2(peak)}}} = \frac{0.02 \times 3.3 \times 0.5}{3.8 + 3}$$

= 4.8 m $\Omega$  (30)

and the capacitance is:

$$Cout \ge \frac{I_{OUT} \times D_{max}}{V_{ripple} \times 0.5 \times f_{sw}} = \frac{2.5 \times 0.56}{0.02 \times 3.3 \times 0.5 \times 300k}$$

$$= 141 \ \mu F \tag{31}$$

Two pieces of 100  $\mu$ F (6m $\Omega$  ESR) ceramic caps are used. For cost-sensitive applications, an electrolytic capacitor and a ceramic capacitor can be used together. Noise sensitive applications can include a second stage filter.

## Step 7: Input capacitor selection

The RMS current of the input capacitor is:

$$I_{\text{Cin(rms)}} = \frac{\Delta I_L}{\sqrt{12}} = \frac{1.1}{\sqrt{12}} = 0.32A \tag{32}$$

#### Step 8: Feedback resistors, current sensing resistor calculation and frequency set resistor

R1 is the top resistor and R2 is the bottom resistor of the voltage divider. The feedback reference voltage is 1.26V.

If R1 = 20 k $\Omega$ , then:

$$R2 = \frac{V_{REF}}{V_{OUT} - V_{REF}} \times R1 = \frac{1.26}{3.3 - 1.26} \times 20k$$

$$= 12.4 \text{ k}\Omega$$

(33)

For the LM3478, the threshold voltage to trigger the current protection varies with duty cycle. The threshold is a ramp which is defined by Vsense at 0% duty cycle and Vsense – Vsl at 100% duty cycle. The values for Vsense and Vsl can be taken from the *Electrical Characteristics* section of the *LM3478*, *LM3478-Q1High-Efficiency Low-Side N-Channel Controller for Switching Regulator Data Sheet* (SNVS085). There is also a plot in the data sheet showing the typical current sense voltage vs duty cycle. In our example the duty cycle was calculated to be about 50% and so we use the current limit threshold of 130mV for the following calculation to keep things simple. Thus the sensing resistor value is:

$$Rsn = \frac{130 \text{ mV}}{I_{Q1(peak)}} = \frac{130m}{6.8} = 19 \text{ m}\Omega$$

(34)

Rf is approximately 50 k $\Omega$  for 330 kHz operation.

#### Step 9: Compensation Design

In the control to output transfer function of a peak current mode controlled SEPIC converter, the load pole can be estimated as  $1/(2\pi RL^*Cout)$ ; The ESR zero of the output capacitor is  $1/(2\pi ESR^*Cout)$ , where RL is the load resistant, Cout is the output capacitor and ESR is the Equivalent Series Resistance of the output capacitor. There is also a right-half-plane zero ( $f_{RHPZ}$ ), given by:

$$f_{RHPZ} = \frac{(1 - D_{max})^2 \times V_{OUT}}{2\pi \times D_{max} \times L2 \times 0.5 \times I_{OUT}}$$

$$= \frac{(1 - 0.56)^2 \times 3.3}{2\pi \times 0.56 \times 4.7\mu \times 0.5 \times 2.5} = 31 \text{ kHz}$$

(35)

We can also see a "glitch" in the magnitude plot at the resonant frequency of the network formed by the SEPIC capacitor Cs and the inductor L2:

$$f_{R} = \frac{1}{2\pi \, x \, \sqrt{\text{L2} \, x \, \text{Cs}}} = \frac{1}{2\pi \, x \, \sqrt{4.7 \mu \text{H} \, x \, 10 \mu \text{F}}}$$

$$= 23 \, \text{kHz}$$

(36)

The crossover frequency is set at one sixth of the  $f_{RHPZ}$  or  $f_{R}$ , whichever is lower:

$$f_c = \frac{f_R}{6} = \frac{23k}{6} = 3.8 \text{ kHz}$$

(37)

Parts Cc1, Cc2 and Rc form a compensation network, which has one zero at  $1/(2\pi Rc^*Cc1)$ , one pole at the origin, and another pole at  $1/(2\pi Rc^*Cc2)$ .

Where,  $V_{REF}$  is the reference voltage of 1.26 V,  $V_{OUT}$  is the output voltage,  $G_{cs}$  is the current sense gain (roughly 1/Rsn) 100A/V, and  $G_{ma}$  is the error amplifier transconductance (800 µmho).

Rc is chosen to set the desired crossover frequency.

$$Rc = \frac{2\pi \times f_c \times C_{OUT} \times V_{OUT}^2 \times (1 + D_{max})}{G_{cs} \times G_{ma} \times V_{REF} \times V_{IN (min)} \times D_{max}}$$

$$= \frac{2\pi \times 3.8k \times 200\mu \times 3.3^2 \times (1 + 0.56)}{91 \times 800\mu \times 1.26 \times 3.0 \times 0.56}$$

$$= 523\Omega$$

(38)

References www.ti.com

Cc1 is chosen to set the compensator zero to 1/4 of the crossover frequency:

$$Cc1 = \frac{4}{2\pi \times f_c \times Rc} = \frac{4}{2\pi \times 3.8k \times 523} = 330 \text{ nF}$$

(39)

The pole at  $1/(2\pi Rc^*Cc2)$  is to cancel the ESR zero  $1/(2\pi ESR^*Cout)$ ,

$$Cc2 = \frac{C_{OUT} \times ESR}{Rc} = \frac{200\mu \times 3m}{523} = 1.2 \text{ nF}$$

(40)

# 10 References

LM3478, LM3478-Q1High-Efficiency Low-Side N-Channel Controller for Switching Regulator Data Sheet (SNVS085)

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

Products Applications

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers <u>microcontroller.ti.com</u> Video and Imaging <u>www.ti.com/video</u>

RFID www.ti-rfid.com

OMAP Applications Processors <a href="www.ti.com/omap">www.ti.com/omap</a> TI E2E Community <a href="e2e.ti.com">e2e.ti.com</a>

Wireless Connectivity <u>www.ti.com/wirelessconnectivity</u>