# UCD3138 Digital Power Peripherals Programmer's Manual

**SLUU995 - July 2012**

#### **Table of Contents** 2 2.1 2.2 2.3 2.4 2.5 2.6 2.7 2.8 2.9 2.10 2.10.1 2.11 2.12 2.13 2.14 2.15 2.15.1 2.15.2 2.15.3 2.15.4 2.15.5 2.15.6 2.15.7 2.15.8 2.15.9 2.15.10 2.15.11 2.15.12 2.15.13 2.15.14 2.15.15 2.16.1 2.16.2 2.16.3 2.16.4 2.16.5 2.16.6 External Sync Enable .......40 2.16.7 2.16.8 Auto Mode Switching Enable......40 2.16.9 2.16.10

|   | 2.16. | 6.11 Check Override                             | 40 |

|---|-------|-------------------------------------------------|----|

|   | 2.16. | 6.12 Global Period Enable                       | 40 |

|   | 2.16. | 6.13 Using DPWM Pins as General Purpose I/O     | 41 |

|   | 2.16. |                                                 |    |

|   | 2.16. |                                                 |    |

|   | 2.16. |                                                 |    |

| 2 | .17 I | DPWM Control Register 2                         | 42 |

|   | 2.17. | 7.1 External Synchronization Input Divide Ratio | 42 |

|   | 2.17. |                                                 |    |

|   | 2.17. |                                                 |    |

|   | 2.17. | 7.4 Ideal Diode Emulation (IDE) Enable for PWMB | 42 |

|   | 2.17. |                                                 |    |

|   | 2.17. |                                                 |    |

|   | 2.17. | 7.7 Sample Trigger Enable bits                  | 43 |

| 2 | .18 I | Period and Event Registers                      |    |

| 2 |       | Phase Trigger Register                          |    |

| 2 |       | Cycle Adjust Registers                          |    |

| 2 |       | Resonant Duty Register                          |    |

| 2 |       | DPWM Fault Control Register                     |    |

| 2 |       | DPWM Overflow Register                          |    |

| 2 |       | DPWM Interrupt Register                         |    |

|   | 2.24. | 4.1 DPWM Period Interrupt Bits                  | 45 |

|   | 2.24. |                                                 |    |

|   | 2.24. |                                                 |    |

| 2 | .25 I | DPWM Counter Preset Register                    | 45 |

| 2 |       | Blanking Registers                              |    |

| 2 |       | DPWM Adaptive Sample Register                   |    |

| 2 |       | DPWM Fault Status Register                      |    |

| 2 |       | DPWM Auto Switch Registers                      |    |

| 2 | .30 I | DPWM Edge PWM Generation Register               | 47 |

| 3 |       | nt End                                          |    |

| 3 | .1 I  | Error ADC and Front End Gain                    | 48 |

|   | 3.1.1 | .1 Front End Gain                               | 48 |

|   | 3.1.2 | .2 EADC Error Output                            | 49 |

|   | 3.1.3 | .3 EADC Triggering, EADC Output to Filter       | 50 |

|   | 3.1.4 |                                                 |    |

|   | 3.1.5 | .5 EADC Averaging                               | 52 |

|   | 3.1.6 | .6 Enabling the EADC and Front End              | 53 |

| 3 | .2 I  | Front End DAC                                   | 54 |

| 3 | .3 I  | Ramp Module                                     | 56 |

|   | 3.3.1 | •                                               |    |

|   | 3.3.2 |                                                 |    |

|   | 3.3.3 | ·                                               |    |

|   | 3.3.4 | · ·                                             |    |

|   | 3.3.5 |                                                 |    |

|   | 3.3.6 | •                                               |    |

|   | 3.3.7   | Using Ramp Module for Peak Current Mode                     |    |

|---|---------|-------------------------------------------------------------|----|

|   | 3.3.8   | Sync FET Soft On/Off using Ramp Module                      | 59 |

|   | 3.4 St  | uccessive Approximation Mode                                |    |

|   | 3.4.1   | SAR Control Parameters                                      | 60 |

|   | 3.4.2   | SAR Algorithm Overview                                      | 61 |

|   | 3.4.3   | Non-Continuous SAR Mode                                     |    |

|   | 3.4.4   | Continuous SAR Mode                                         |    |

|   |         | bsolute Value Without SAR                                   |    |

|   |         | ADC Modes                                                   |    |

| 4 |         |                                                             |    |

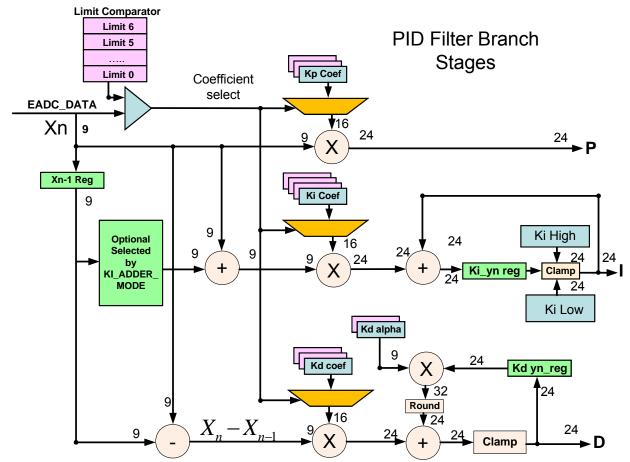

| • |         | Iter Math Details                                           |    |

|   | 4.1.1   | Filter Input and Branch Calculations                        |    |

|   | 4.1.2   | Proportional Branch                                         |    |

|   | 4.1.3   | Integral Branch                                             |    |

|   | 4.1.3   | Differential Branch                                         |    |

|   | 4.1.4   |                                                             |    |

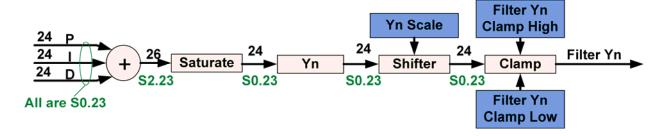

|   | 4.1.5   | Add, Saturate, Scale and Clamp                              |    |

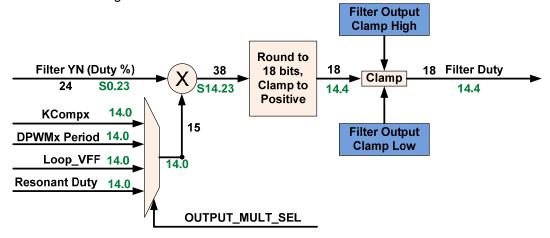

|   |         | Filter Output Stage                                         |    |

|   |         | Iter Status Register                                        |    |

|   |         | Iter Control Register                                       |    |

|   | 4.3.1   | Filter Enable                                               |    |

|   | 4.3.2   | Use CPU Sample                                              |    |

|   | 4.3.3   | Force Start                                                 |    |

|   | 4.3.4   | Kp Off, Kd Off, Ki Off                                      |    |

|   | 4.3.5   | Kd Stall, Ki Stall                                          |    |

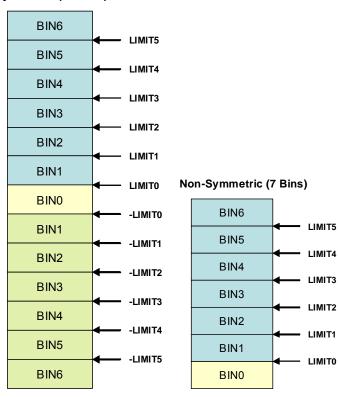

|   | 4.3.6   | Nonlinear Mode                                              |    |

|   | 4.3.7   | Output Scaling                                              |    |

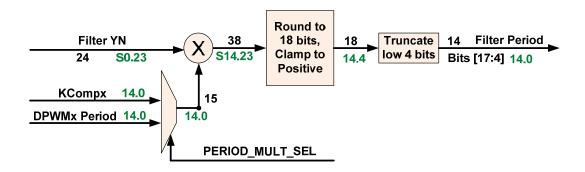

|   | 4.3.8   | Output Multiplier Select                                    |    |

|   | 4.3.9   | Switching Period as Output multiplier                       |    |

|   | 4.3.10  |                                                             |    |

|   | 4.3.11  | Feed Forward as Output Multiplier                           |    |

|   | 4.3.12  | ·                                                           |    |

|   | 4.3.13  |                                                             |    |

|   | 4.4 X   | N, YN Read and Write Registers                              |    |

|   | 4.4.1   | CPU Xn Register                                             |    |

|   | 4.4.2   | Filter XN Read Register                                     | 70 |

|   | 4.4.3   | Filter YN Read Registers                                    |    |

|   | 4.5 C   | oefficient Configuration Register                           | 71 |

|   | 4.6 K   | o, Ki, and Kd Registers                                     | 72 |

|   |         | pha Register                                                |    |

|   |         | Iter Nonlinear Limit Registers                              |    |

|   | 4.9 C   | lamp Registers                                              | 73 |

|   | 4.10 Fi | Iter Preset Register                                        | 73 |

| 5 |         | Иux                                                         |    |

|   |         | ont End Control Muxes (FECTRL0MUX, FECTRL1MUX, FECTRL2MUX). |    |

|   |         | ample Trigger Control (SAMPTRIGCTRL)                        |    |

|   |         | xternal DAC Control (EXTDACCTRL)                            | 76 |

|   | 5.4   | Filter Mux Register (FILTERMUX)                 |      |

|---|-------|-------------------------------------------------|------|

|   | 5.5   | Filter KComp Registers (FILTERKCOMPx)           | . 77 |

|   | 5.6   | DPWM Mux Register (DPWMMUX)                     | . 77 |

|   | 5.7   | Global Enable Register (GLBEN)                  | . 77 |

|   | 5.8   | PWM Global Period Register (PWMGLBPRD)          | . 78 |

|   | 5.9   | Sync Control (SYNCCTRL)                         |      |

|   | 5.10  | Light Load (Burst) Mode                         |      |

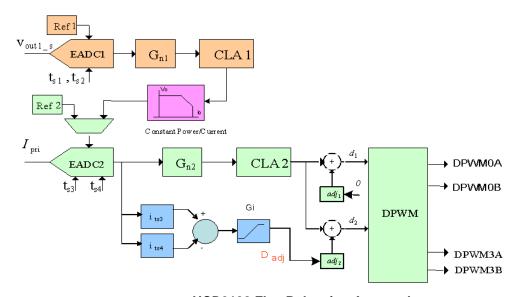

|   | 5.11  | Constant Current / Constant Power               |      |

|   |       | Analog Peak Current Mode                        |      |

|   |       | Automatic Cycle Adjustment                      |      |

|   | 5.13  |                                                 |      |

|   | 5.13  |                                                 |      |

|   | 5.13  |                                                 |      |

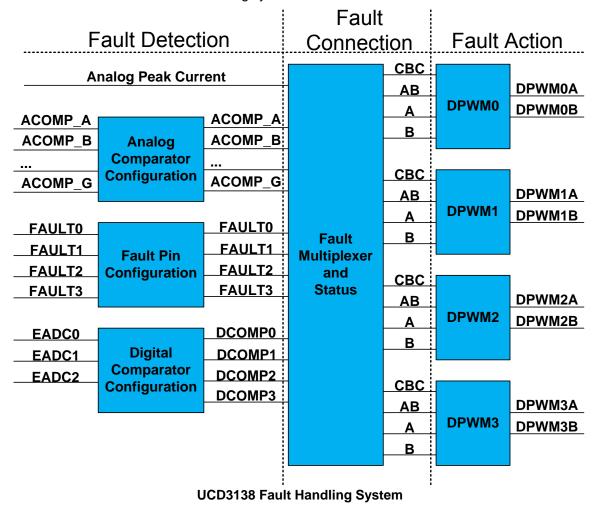

| 6 |       | t Mux                                           |      |

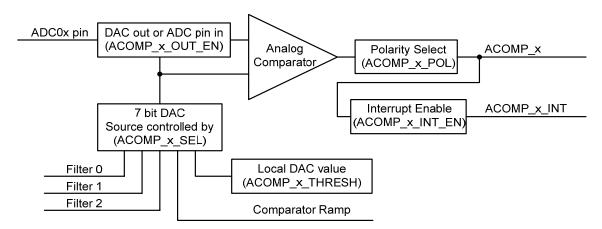

| U |       | Analog Comparator Configuration                 |      |

|   | 6.1.  |                                                 |      |

|   | 6.1.2 |                                                 |      |

|   | 6.1.3 |                                                 | _    |

|   | 6.1.4 |                                                 |      |

|   | 6.1.  | <b></b>                                         |      |

|   | 6.1.6 |                                                 |      |

|   | 6.1.  | <b></b>                                         |      |

|   | 6.1.8 |                                                 |      |

|   |       | Analog Comparator Ramp                          |      |

|   | 6.3   | Digital Comparator Configuration                | . OJ |

|   | 6.4   |                                                 |      |

|   | 6.5   | Fault Pin Configuration                         |      |

|   |       |                                                 |      |

|   |       | Fault Status Registers                          |      |

|   | 6.7   | Fault Mux Control Registers                     |      |

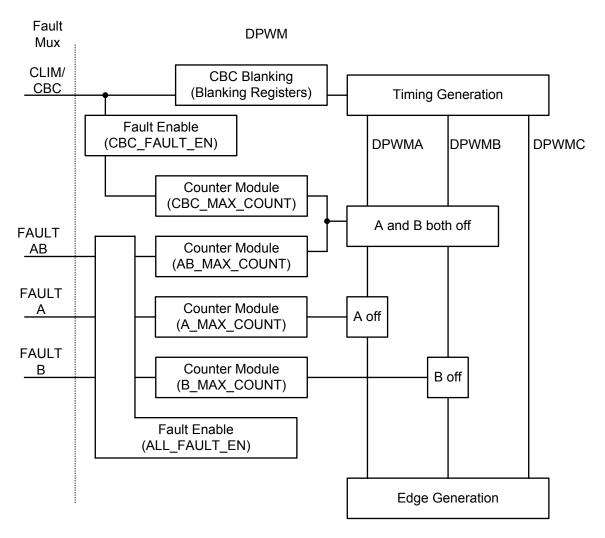

|   | 6.8   | DPWM Fault Action                               |      |

|   | 6.9   | IDE /DCM Detection Control                      |      |

|   |       | Oscillator Failure Detection                    |      |

|   |       | 1.1 High Frequency Oscillator Failure Detection |      |

| _ |       | .2 Low Frequency Oscillator Failure Detection   |      |

| 7 | GIO   | Module                                          | . 90 |

| 8 |       | VM 0-3 Registers Reference                      |      |

|   |       | DPWM Control Register 0 (DPWMCTRL0)             |      |

|   | 8.2   | DPWM Control Register 1 (DPWMCTRL1)             |      |

|   | 8.3   | DPWM Control Register 2 (DPWMCTRL2)             |      |

|   |       | DPWM Period Register (DPWMPRD)                  |      |

|   | 8.5   | DPWM Event 1 Register (DPWMEV1)                 |      |

|   | 8.6   | DPWM Event 2 Register (DPWMEV2)                 |      |

|   |       | DPWM Event 3 Register (DPWMEV3)                 |      |

|   | 8.8   | DPWM Event 4 Register (DPWMEV4)                 | . 99 |

|   |       | DPWM Sample Trigger 1 Register (DPWMSAMPTRIG1)  |      |

|   | 8.10  | DPWM Sample Trigger 2 Register (DPWMSAMPTRIG2)  | 100  |

|   | 8.11 | DPWM Phase Trigger Register (DPWMPHASETRIG)                 |     |

|---|------|-------------------------------------------------------------|-----|

|   | 8.12 | DPWM Cycle Adjust A Register (DPWMCYCADJA)                  | 101 |

|   | 8.13 | DPWM Cycle Adjust B Register (DPWMCYCADJB)                  |     |

|   | 8.14 | DPWM Resonant Duty Register (DPWMRESDUTY)                   | 101 |

|   | 8.15 | DPWM Fault Control Register (DPWMFLTCTRL)                   | 101 |

|   | 8.16 | DPWM Overflow Register (DPWMOVERFLOW)                       |     |

|   | 8.17 | DPWM Interrupt Register (DPWMINT)                           | 104 |

|   | 8.18 | DPWM Counter Preset Register (DPWMCNTPRE)                   | 106 |

|   | 8.19 | DPWM Blanking A Begin Register (DPWMBLKABEG)                | 106 |

|   | 8.20 | DPWM Blanking A End Register (DPWMBLKAEND)                  | 106 |

|   | 8.21 | DPWM Blanking B Begin Register (DPWMBLKBBEG)                | 107 |

|   | 8.22 | DPWM Blanking B End Register (DPWMBLKBEND)                  |     |

|   | 8.23 | DPWM Minimum Duty Cycle High Register (DPWMMINDUTYHI)       | 107 |

|   | 8.24 | DPWM Minimum Duty Cycle Low Register (DPWMMINDUTYLO)        |     |

|   | 8.25 | DPWM Adaptive Sample Register (DPWMADAPTIVE)                |     |

|   | 8.26 | DPWM Fault Status (DPWMFLTSTAT)                             |     |

|   | 8.27 | DPWM Auto Switch High Upper Thresh Register                 |     |

|   | (DPW | MAUTOSWHIUPTHRESH)                                          | 109 |

|   | 8.28 | DPWM Auto Switch High Lower Thresh Register                 |     |

|   | (DPW | MAUTOSWHILOWTHRESH)                                         | 110 |

|   | 8.29 | DPWM Auto Switch Low Upper Thresh Register                  |     |

|   | (DPW | MAUTOSWLOUPTHRESH)                                          | 110 |

|   | 8.30 | DPWM Auto Switch Low Lower Thresh Register                  |     |

|   | (DPW | MAUTOSWLOLOWTHRESH)                                         |     |

|   | 8.31 | DPWM Auto Config Max Register (DPWMAUTOMAX)                 | 112 |

|   | 8.32 | DPWM Auto Config Mid Register (DPWMAUTOMID)                 | 113 |

|   | 8.33 | DPWM Edge PWM Generation Control Register (DPWMEDGEGEN)     | 115 |

|   | 8.34 | DPWM Filter Duty Read Register (DPWMFILTERDUTYREAD)         |     |

|   | 8.35 | DPWM BIST Status Register (DPWMBISTSTAT)                    |     |

| 9 |      | nt End Control Registers                                    |     |

|   | 9.1  | Ramp Control Register (RAMPCTRL)                            |     |

|   | 9.2  | Ramp Status Register (RAMPSTAT)                             |     |

|   | 9.3  | Ramp Cycle Register (RAMPCYCLE)                             |     |

|   | 9.4  | EADC DAC Value Register (EADCDAC)                           | 122 |

|   | 9.5  | Ramp DAC Ending Value Register (RAMPDACEND)                 | 122 |

|   | 9.6  | DAC Step Register (DACSTEP)                                 | 122 |

|   | 9.7  | DAC Saturation Step Register (DACSATSTEP)                   |     |

|   | 9.8  | EADC Trim Register (EADCTRIM) – (For Factory Test Use Only) |     |

|   | 9.9  | EADC Control Register (EADCCTRL)                            |     |

|   | 9.10 | Analog Control Register (ACTRL) (For Test Use Only)         |     |

|   | 9.11 | Pre-Bias Control Register 0 (PREBIASCTRL0)                  |     |

|   | 9.12 | Pre-Bias Control Register 1 (PREBIASCTRL1)                  |     |

|   | 9.13 | SAR Control Register (SARCTRL)                              |     |

|   | 9.14 | SAR Timing Register (SARTIMING)                             |     |

|   | 9.15 | EADC Value Register (EADCVALUE)                             |     |

|   | 9 16 | FADC Raw Value Register (FADCRAWVALUE)                      | 131 |

| 9.17  | DAC Status Register (DACSTAT)                         | 131 |

|-------|-------------------------------------------------------|-----|

| 10 F  | ilter Registers Reference                             | 131 |

| 10.1  | Filter Status Register (FILTERSTATUS)                 | 131 |

| 10.2  | Filter Control Register (FILTERCTRL)                  |     |

| 10.3  | CPU XN Register (CPUXN)                               | 134 |

| 10.4  | Filter XN Read Register (FILTERXNREAD)                | 135 |

| 10.5  | Filter KI_YN Read Register (FILTERKIYNREAD)           |     |

| 10.6  | Filter KD_YN Read Register (FILTERKDYNREAD)           | 135 |

| 10.7  | Filter YN Read Register (FILTERYNREAD)                |     |

| 10.8  | Coefficient Configuration Register (COEFCONFIG)       | 136 |

| 10.9  | Filter KP Coefficient 0 Register (FILTERKPCOEF0)      | 138 |

| 10.10 | Filter KP Coefficient 1 Register (FILTERKPCOEF1)      | 138 |

| 10.11 | Filter KI Coefficient 0 Register (FILTERKICOEF0)      |     |

| 10.12 | Filter KI Coefficient 1 Register (FILTERKICOEF1)      | 140 |

| 10.13 |                                                       |     |

| 10.14 | Filter KD Coefficient 1 Register (FILTERKDCOEF1)      | 140 |

| 10.15 | ,                                                     |     |

| 10.16 |                                                       | 141 |

| 10.17 |                                                       | 141 |

| 10.18 | Filter Nonlinear Limit Register 2 (FILTERNL2)         | 141 |

| 10.19 |                                                       | 142 |

| 10.20 | Filter KI Feedback Clamp Low Register (FILTERKICLPLO) | 142 |

| 10.21 | Filter YN Clamp High Register (FILTERYNCLPHI)         |     |

| 10.22 | ,                                                     |     |

| 10.23 |                                                       |     |

| 10.24 |                                                       | 144 |

| 10.25 | <b>6</b> \                                            |     |

| 11 L  | oop Mux Registers Reference                           |     |

| 11.1  |                                                       | 144 |

| 11.2  | Front End Control 1 Mux Register (FECTRL1MUX)         |     |

| 11.3  | Front End Control 2 Mux Register (FECTRL2MUX)         | 149 |

| 11.4  | Sample Trigger Control Register (SAMPTRIGCTRL)        |     |

| 11.5  | External DAC Control Register (EXTDACCTRL)            | 152 |

| 11.6  | Filter Mux Register (FILTERMUX)                       |     |

| 11.7  | Filter KComp A Register (FILTERKCOMPA)                | 156 |

| 11.8  | Filter KComp B Register (FILTERKCOMPB)                | 156 |

| 11.9  | DPWM Mux Register (DPWMMUX)                           | 157 |

| 11.10 |                                                       | 158 |

| 11.11 | Constant Power Nominal Threshold Register (CPNOM)     |     |

| 11.12 | <b>5</b> \ ,                                          |     |

| 11.13 | 3                                                     |     |

| 11.14 |                                                       |     |

| 11.15 | <b>5</b> , , , , , , , , , , , , , , , , , , ,        |     |

| 11.16 | <b>5</b> \                                            |     |

| 11.17 | <b>O</b> ( )                                          | 163 |

| 11.18 | Cycle Adjustment Control Register (CYCADJCTRL)        | 164 |

| 11.19 | Cycle Adjustment Limit Register (CYCADJLIM)               |     |

|-------|-----------------------------------------------------------|-----|

| 11.20 | Cycle Adjustment Status Register (CYCADJSTAT)             | 165 |

| 11.21 | Global Enable Register (GLBEN)                            |     |

| 11.22 | PWM Global Period Register (PWMGLBPRD)                    | 167 |

| 11.23 | Sync Control Register (SYNCCTRL)                          |     |

| 11.24 | Light Load Control Register (LLCTRL)                      | 168 |

| 11.25 | Light Load Enable Threshold Register (LLENTHRESH)         | 168 |

| 11.26 | Light Load Disable Threshold Register (LLDISTHRESH)       |     |

| 11.27 |                                                           |     |

| 11.28 |                                                           |     |

| 11.29 |                                                           |     |

| 12 F  | ault Mux Registers Reference                              | 171 |

| 12.1  | Analog Comparator Control 0 Register (ACOMPCTRL0)         | 171 |

| 12.2  | Analog Comparator Control 1 Register (ACOMPCTRL1)         |     |

| 12.3  | Analog Comparator Control 2 Register (ACOMPCTRL2)         |     |

| 12.4  | Analog Comparator Control 3 Register (ACOMPCTRL3)         | 175 |

| 12.5  | External Fault Control Register (EXTFAULTCTRL)            |     |

| 12.6  | Fault Mux Interrupt Status Register (FAULTMUXINTSTAT)     |     |

| 12.7  | Fault Mux Raw Status Register (FAULTMUXRAWSTAT)           | 178 |

| 12.8  | Comparator Ramp Control 0 Register (COMPRAMP0)            |     |

| 12.9  | Digital Comparator Control 0 Register (DCOMPCTRL0)        |     |

| 12.10 | Digital Comparator Control 1 Register (DCOMPCTRL1)        |     |

| 12.11 | Digital Comparator Control 2 Register (DCOMPCTRL2)        | 182 |

| 12.12 | Digital Comparator Control 3 Register (DCOMPCTRL3)        |     |

| 12.13 | Digital Comparator Counter Status Register (DCOMPCNTSTAT) |     |

| 12.14 | DPWM 0 Current Limit Control Register (DPWM0CLIM)         |     |

| 12.15 | DPWM 0 Fault AB Detection Register (DPWM0FLTABDET)        | 186 |

| 12.16 | DPWM 0 Fault Detection Register (DPWM0FAULTDET)           |     |

| 12.17 |                                                           |     |

| 12.17 | · · · · · · · · · · · · · · · · · · ·                     |     |

| 12.18 | DPWM 1 Fault AB Detection Register (DPWM1FLTABDET)        |     |

| 12.19 | DPWM 1 Fault Detection Register (DPWM1FAULTDET)           |     |

| 12.20 | DPWM 2 Current Limit Control Register (DPWM2CLIM)         |     |

| 12.21 | DPWM 2 Fault AB Detection Register (DPWM2FLTABDET)        | 202 |

| 12.22 | DPWM 2 Fault Detection Register (DPWM2FAULTDET)           |     |

| 12.23 | DPWM 3 Current Limit Control Register (DPWM3CLIM)         | 208 |

| 12.24 | DPWM 3 Fault AB Detection Register (DPWM3FLTABDET)        |     |

| 12.25 | DPWM 3 Fault Detection Register (DPWM3FAULTDET)           |     |

| 12.26 | HFO Fail Detect Register (HFOFAILDET)                     |     |

| 12.27 |                                                           |     |

| 12.28 |                                                           |     |

|       | IIO – General Purpose Input/Output Module                 |     |

| 13.1  | Fault IO Direction Register (FAULTDIR)                    |     |

| 13.2  | Fault Input Register (FAULTIN)                            |     |

| 13.3  | Fault Output Register (FAULTOUT)                          |     |

| 13.4  |                                                           | 219 |

| 13.5  | Fault Interrupt Polarity Register (FAULTINTPOL)   | 219 |

|-------|---------------------------------------------------|-----|

| 13.6  | Fault Interrupt Pending Register (FAULTINTPEND)   | 221 |

| 13.7  | External Interrupt Direction Register (EXTINTDIR) | 222 |

| 13.8  | External Interrupt Input Register (EXTINTIN)      | 222 |

| 13.9  | External Interrupt Output Register (EXTINTOUT)    | 222 |

| 13.10 | External Interrupt Enable Register (EXTINTENA)    | 222 |

| 13.11 |                                                   |     |

| 13.12 | External Interrupt Pending Register (EXTINTPEND)  | 223 |

# **Scope of this Document**

The following topics are covered in the UCD3138 Digital Power Peripheral Programmer's Manual

- Digital Pulse Width Modulator (DPWM)

- Modes of Operation (Normal/Multi/Phase-shift/Resonant etc)

- Automatic Mode Switching

- DPWMC, Edge Generation & Intra-Mux

- Front End

- Analog Front End

- Error ADC or EADC

- Front End DAC

- Ramp Module

- Successive Approximation Register Module

- Filter

- Filter Math

- Loop Mux

- Analog Peak Current Mode

- Constant Current/Constant Power (CCCP)

- Automatic Cycle Adjustment

- Fault Mux

- Analog Comparators

- Digital Comparators

- Fault Pin functions

- DPWM Fault Action

- Ideal Diode Emulation (IDE), DCM Detection

- Oscillator Failure Detection

- Register Map for all of the above peripherals in UCD3138

Other topics related to UCD3138 are covered in the additional documents listed below:

#### **UCD3138 ARM and Digital System Programmer's Manual**

- Boot ROM & Boot Flash

- BootROM Function

- o Memory Read/Write Functions

- o Checksum Functions

- o Flash Functions

- Avoiding Program Flash Lock-Up

- ARM7 Architecture

- Modes of Operation

- Hardware/Software Interrupts

- o Instruction Set

- o Dual State Inter-working (Thumb 16-bit Mode/ARM 32-bit Mode)

- Memory & System Module

- Address Decoder, DEC (Memory Mapping)

- Memory Controller (MMC)

- Central Interrupt Module

- Register Map for all of the above peripherals in UCD3138

#### **UCD3138 Monitoring and Communications Programmer's Manual**

- ADC12

- Control, Conversion, Sequencing & Averaging

- Digital Comparators

- Temperature Sensor

- PMBUS Addressing

- Dual Sample & Hold

- Miscellaneous Analog Controls (Current Sharing, Brown-Out, Clock-Gating)

- PMBUS Interface

- General Purpose Input Output (GPIO)

- Timer Modules

- PMBus

- Register Map for all of the above peripherals in UCD3138

For the most up to date product specifications please consult the UCD3138 Device datasheet (Lit # SLUSAP2) available at www.ti.com.

# 1 Introduction

UCD3138 is a digital power supply controller from Texas Instruments offering superior levels of integration and performance in a single chip solution targeting high-performance isolated power supply applications. At its core are the digital control loop peripherals, also known as Digital Power Peripherals (DPP) that are used for controlling the high-speed voltage/current loops in the power supply and an ARM7TDMI-S microcontroller/processor that performs real-time monitoring, configures peripherals and manages communications. The device also contains a 12-bit, 265ksps general purpose ADC with up to 14 channels, timers, interrupt control, JTAG debug and PMBus and UART communications ports. In terms of memory, UCD3138 offers 32kB of program flash, 2kB of data flash, 4kB RAM and 4kB of ROM.

The Digital Power Peripherals (DPPs) are elemental blocks in the UCD3138 controller which are specifically architected for digital power supply control. They are designed to replace the analog compensation network and PWM generation system that are employed in power supplies based on analog power management controller ICs, and add enhanced digital features to the system. In many cases, after initialization by firmware, the DPPs can control a power supply completely autonomously, with no firmware intervention. This leaves processor resources for improved monitoring, communication, and other functions.

The simplest configuration of the Digital Power Peripherals highlighting the key blocks involved in loop control is shown below:

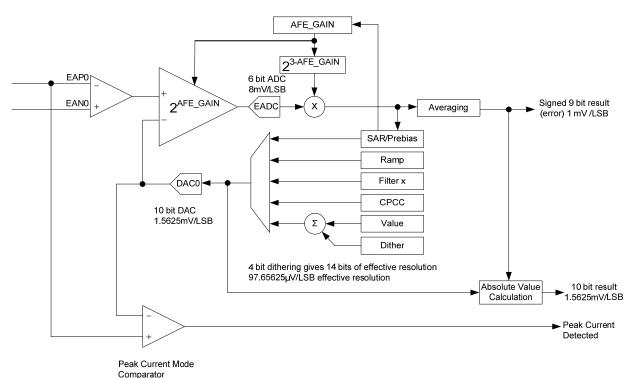

The Error ADC (in the Front End) accepts a differential voltage signal as an input. It measures the difference between this input and a digitally controlled reference voltage and generates a digital error output. It passes this digital error information to the Filter. The Error ADC (or EADC) is a specialized high speed, high resolution ADC with a small dynamic range, optimized for power supply error measurement.

The Filter takes the error signal and passes it through a PID based digital filter which compensates for the characteristics of the external loop. This filter can be dynamically reprogrammed for changing power load source, and circuit characteristics. It also offers non-linear response capability for better handling of transients.

The output of the compensator is passed to a Digital PWM (DPWM) generator. The DPWM has two outputs, which can be used in many different ways. There are modes for synchronous rectification, multiple phases, various bridge topologies, and LLC configurations. In addition to the 2 DPWM outputs, the DPWM has other signals which are used externally and internally. These include:

- o Frame start start of a switching cycle

- Sample Trigger signals Front end to take a sample

- Sync out signals another DPWM to start a frame

- Sync in a signal to this DPWM to start a frame

- o Fault signals signal the DPWM to take various fault actions

These signals will be covered in much more detail in the DPWM section of this document.

The peripherals can be run tied together as shown above, or they can be used in different groupings and interconnections, not shown in the picture above. For example, the DPWM can be used to trigger the Error ADC, which will trigger the Filter at the end of its conversion.

The UCD3138 device supports multiple sets of the Digital Power Peripherals affording the ability to control upto 3 feedback loops (voltage or current) and drive 8 outputs simultaneously. To inter-connect all the DPPs, there is a large module called the Loop Mux. This permits a high degree of flexibility in DPP

configuration. Any Front End can be connected to any Filter, and any Filter output can be connected to any DPWM. Additionally, information can be passed between the peripherals. For example, the output of one Filter (eg. controlling a slow Voltage loop), can contribute to the reference of another Front End (eg. monitoring a fast current loop) and enable implementation of nested loops (such as in Average Current mode control).

In addition, the DPPs in UCD3138 provide other modules and functions for power supply and control. These include:

- Fault Handling

- Cycle by Cycle Current Limit

- Constant Power/Constant Current

- Ramp up/Ramp Down

- Peak Current Mode control and so on.

There is also a module called Fault Mux which connects fault detection circuitry outputs to control inputs, primarily on the DPWMs, to customize fault handling and recovery.

This documentation provides information about the DPP modules in UCD3138, starting with a detailed description, continuing with some configuration examples, and ending with a reference section which lists each bit field in each DPP module.

# 2 Digital Pulse Width Modulator (DPWM)

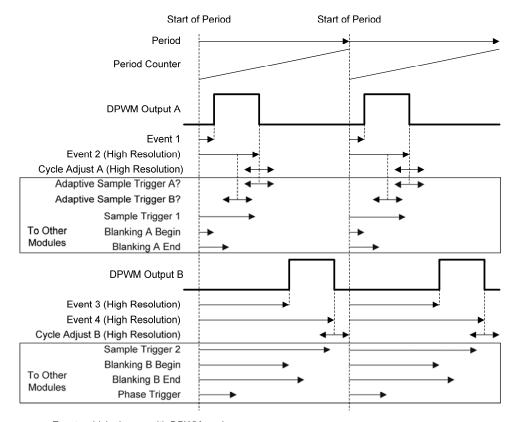

The DPWM Module is probably the most complex and central of the DPPs. It takes the output of the Filter and converts it into the correct PWM output for many power supply topologies. Each DPWM module has two output pins – DPWMxA and DPWMxB (x=0, 1, 2 & 3). The DPWM provides for programmable dead times and cycle adjustments for current balancing between phases. It controls the triggering of the EADC. It can synchronize to other DPWMs or to external sources. Alternately, it can provide synchronization information to other DPWMs or to external recipients. The DPWM can also be synchronized to external devices using the SYNC pin as either an input or an output. In addition, it interfaces to several fault detection circuits. The response to these faults is part of the DPWM function.

# 2.1 DPWM Block Diagram

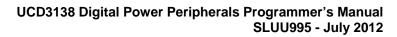

The picture below illustrates an overall view of a single DPWM block, which is composed of many different individual modules, through which the signals propagate:

**Block Diagram of a DPWM module**

- The Timing Generation Module outputs 3 DPWM signals (DPWMx\_T, x=A, B, C), as well as many other signals for other modules. It is the section where the filter output is translated into pulse widths and sometimes into the period.

- The Fault Handling Module is next. It shuts off the DPWM signals if a fault occurs. After the DPWM signals come from the Fault Module (DPWMx\_F, x=A, B, C), they are sent to other DPWM Modules.

- The Edge Generation and Intra Mux modules can combine signals from several DPWMs to generate new signals (DWMx E, DPWMx I, x=A, B, C).

The notation of DPWMx\_T, DPWMx\_F (where x=A, B, C) etc is very useful here to understand the origin and relationship between the signals. For example DPWM2A\_F may have no relationship at all to DPWM2A\_I.

Many topologies use neither the DPWMC signal nor Edge Generation and Intra Mux modules. The default is for these modules to just pass signals through unchanged. However certain topologies such as Phase Shifted Full Bridge (PSFB) use both modules as well as DPWMC signal.

These diagrams merely illustrate the signal propagation through the various modules in the DPWM and do not show the configuration logic which controls how each module works and which can dynamically reconfigure the DPWM between switching cycles.

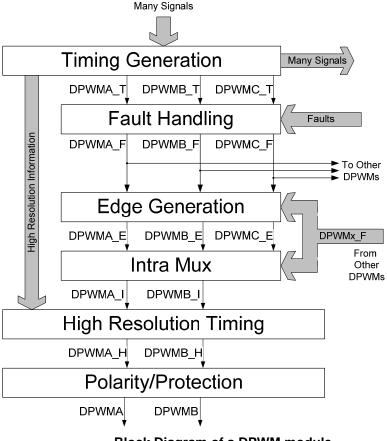

The next figure shows a block diagram of just the Timing Module illustrating the data, signals and main elements involved (once again, the real logic of the Timing Module is not illustrated here).

**Block Diagram of Timing Module in the DPWM module**

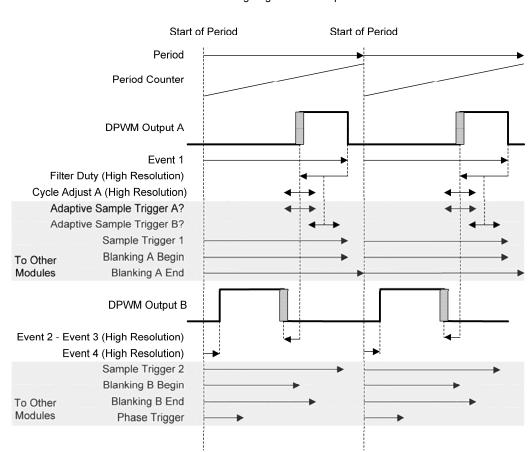

# 2.2 Introduction to DPWM (DPWM Multi-Mode, Open Loop)

The DPWM is based on a DPWM counter, which counts up from 0 to a period value, and then is reset and starts over again. The counter can also be reset by a sync signal, either from the SYNC pin, or from another DPWM.

The DPWM logic causes transitions in many digital signals when the period counter hits the target value for that signal. In the Timing Module block diagram shown above, this is functionality is represented by a digital comparator.

The DPWM has a basic 250 MHz clock, giving a resolution of 4 nanoseconds. 15 other 250 MHz clocks are generated spaced 250 picoseconds apart. Output pulse widths and pulse spacing are controlled by these clocks, giving a resolution of 250 picoseconds. The edges generated by these clocks are hence referred to as "High Resolution" in the illustrations throughout this section.

Most of the signals out of the DPWM are fairly simple. The only complex signals are DPWMA and DPWMB. These vary depending upon the power supply topology and are the most important signals coming out of the DPWM.

The DPWM has many modes to support different topologies. These are selected by a mode bit field in a DPWM control register. The "Multi mode, Open loop" mode is used to introduce the DPWM here, while the other DPWM modes are described in subsequent sections.

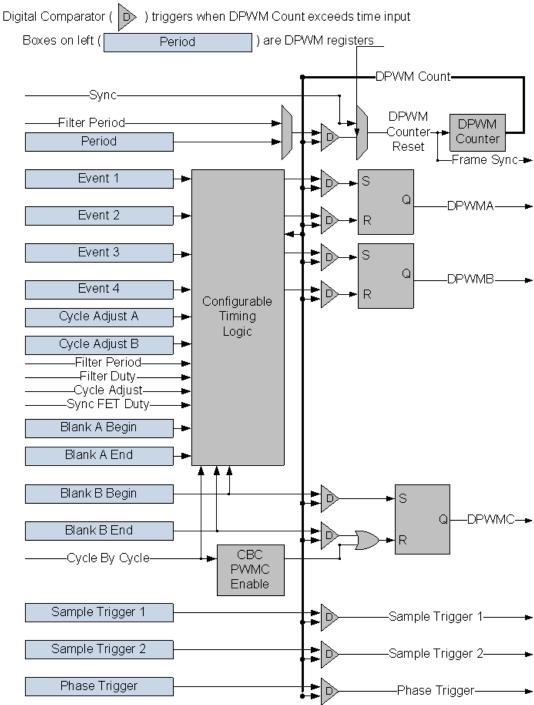

The following figure illustrates most of the signals involved in the DPWM in a mode known as "Multi mode, Open loop". Open loop means that the DPWM is controlled entirely by its own registers, not by the filter output. In other words, the power supply control loop is not closed. This mode is used for introducing the DPWM because there is a very simple correlation between DPWM register values and signal timing.

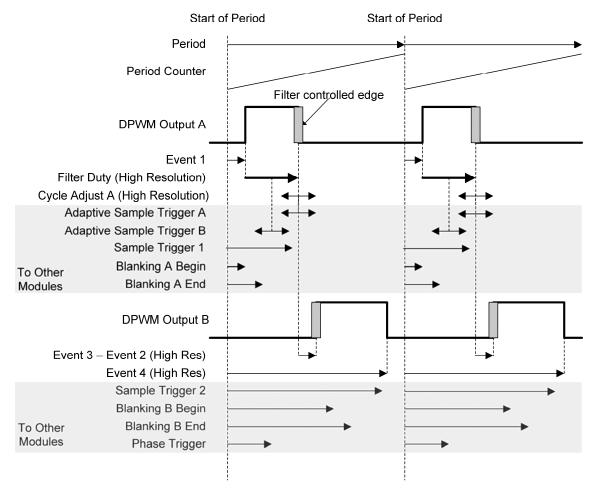

Multi Mode Open Loop

Events which change with DPWM mode:

DPWM A Rising Edge = Event 1

DPWM A Falling Edge = Event 2 + Cycle Adjust A

Adaptive Sample Trigger A = Event 1 + Filter Duty + Adaptive Sample Register

Adaptive Sample Trigger B = Event 1 + Filter Duty/2 + Adaptive Sample Register

DPWM B Rising Edge = Event 3

DPWM B Falling Edge = Event 4 + Cycle Adjust B

Phase Trigger = Phase Trigger Register value

Events always set by their registers, regardless of mode:

Sample Trigger 1, Sample Trigger 2, Blanking A Begin, Blanking A End, Blanking B Begin, Blanking B End

#### **DPWM Mode - Multi-mode, Open Loop**

The Sample Trigger signals are used to trigger the Front End to sample input signals. The Blanking signals are used to blank fault measurements during noisy events, such as FET turn on and turn off. This prevents false detection of faults caused by noise. They only affect the Cycle By Cycle (CBC) module. Other faults are not blanked.

Note that Sample Trigger 1 and 2, Blanking A and B, and Phase Trigger are shown at logical locations for this specific mode, but they can be placed anywhere within the period.

#### 2.3 DPWM Normal Mode

In Normal mode, the Filter output determines the pulse width on DPWM A. DPWM B fits into the rest of the switching period, with a dead time separating it from the DPWM A on-time. It is useful in topologies

that use D and 1-D type waveforms. For example, buck and boost derived topologies can be driven using Normal mode. Here is a drawing of the Normal Mode waveform:

#### Normal Mode Closed Loop

Events which change with DPWM mode:

DPWM A Rising Edge = Event 1

DPWM A Falling Edge = Event 1 + Filter Duty + Cycle Adjust A

Adaptive Sample Trigger A = Event 1 + Filter Duty + Adaptive Sample Register or

Adaptive Sample Trigger B = Event 1 + Filter Duty/2 + Adaptive Sample Register

DPWM B Rising Edge = Event 1 + Filter Duty + Cycle Adjust A + (Event 3 – Event 2)

DPWM B Falling Edge = Event 4

Phase Trigger = Phase Trigger Register value or Filter Duty

Events always set by their registers, regardless of mode:

Sample Trigger 1, Sample Trigger 2, Blanking A Begin, Blanking A End, Blanking B Begin, Blanking B End

#### **DPWM - Normal Mode**

Cycle Adjust A can be used to adjust pulse widths on individual phases of a multi-phase system. This can be used if current balancing is necessary, for example. The Adaptive Sample Triggers can be used to sample in the middle of the on-time (Adaptive Sample Trigger B - for an average output during on-

time), or at the end of the on-time (Adaptive Sample Trigger A - to minimize phase delay). The Adaptive Sample Register provides an offset from the center or end of the on-time for DPWM signal from the chip. This can compensate for external delays, such as FET and gate driver turn-on times.

The Blanking signals are used to disable the CBC fault signal during noise. Generally the noise is caused by DPWM edges. The Blanking registers hold fixed values, so they are easiest to use with fixed edges, rather than with edges that change dynamically. So in this case, the rising edge of DPWM A and the falling edge of DPWM B are easy to provide blanking for. In this mode, both blanking times act on the falling edge of A, since this is what the Cycle By Cycle logic works on.

Cycle Adjust B has no effect in Normal Mode.

CAUTION – In Normal Mode, the DPWM calculated rising edge of DPWMB must not be permitted to exceed DPWM Event 4. This can be done either with a clamp on the filter output, or by using an appropriate KCOMP value in the filter output multiply operation. If this is not done, the DPWMB on time may overlap the DPWMA on time, causing shoot through.

#### 2.4 DPWM Phase Shift Mode

In most modes, it is possible to synchronize multiple DPWM modules using the phase shift signal. The phase shift signal has two possible sources. It can come from the Phase Shift Register or from the Filter Duty value.

The Phase Shift Register provides a fixed value, which is useful in simple multiphase systems such as interleaved PFC.

When the Filter Duty is the source, the changes in the filter output cause changes in the phase relationship of two DPWM modules. This is useful for phase shifted full bridge topologies if voltage mode control is desired rather than peak current mode.

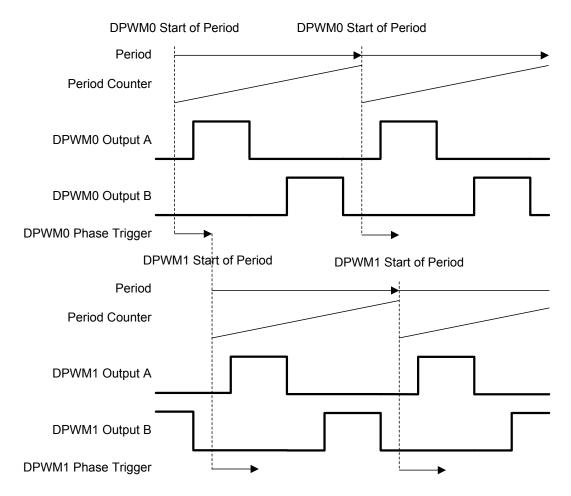

The following figure shows the mechanism of phase shift:

Phase Trigger = Phase Trigger Register value or Filter Duty

**DPWM - Phase Shift Mode**

# 2.5 DPWM Multiple Output Mode (Multi Mode)

Multi Mode is used for systems where each phase has only one driver signal requirement. In this mode, each DPWM peripheral can drive two phases with the same pulse width, but with a time offset between the phases, and with different cycle adjusts for each phase.

Here is a diagram for Multi mode:

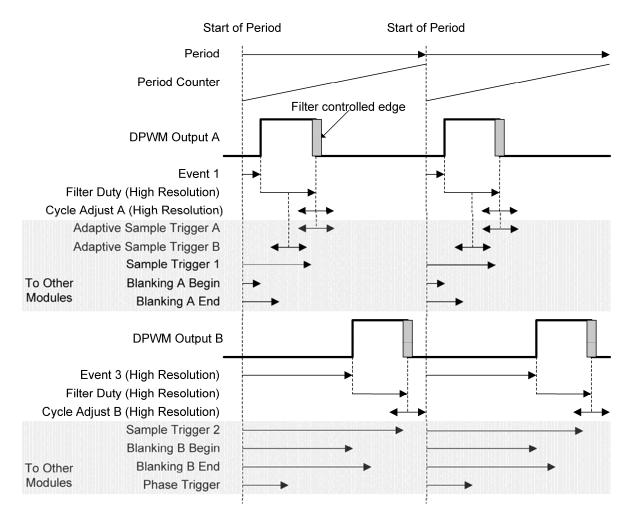

#### Multi Mode Closed Loop

Events which change with DPWM mode:

DPWM A Rising Edge = Event 1

DPWM A Falling Edge = Event 1 + Filter Duty + Cycle Adjust A

Adaptive Sample Trigger A = Event 1 + Filter Duty + Adaptive Sample Register or

Adaptive Sample Trigger B = Event 1 + Filter Duty/2 + Adaptive Sample Register

DPWM B Rising Edge = Event 3

DPWM B Falling Edge = Event 3 + Filter Duty + Cycle Adjust B

Phase Trigger = Phase Trigger Register value or Filter Duty

Events always set by their registers, regardless of mode:

Sample Trigger 1, Sample Trigger 2, Blanking A Begin, Blanking A End, Blanking B Begin, Blanking B End

**DPWM - Multiple Output Mode (Multi Mode)**

Event 2 and Event 4 are not relevant in Multi mode.

As shown in the illustration, DPWMA is designed to turn on close to the start of the period. It can turn off any time until the end of the period, achieving essentially 100% on-time. DPWMB is designed to start later in the period to support a multi-phase system. Therefore DPWMB is designed to cross over the

period boundary safely, so long as it does not ever move into or out of an event update window. This makes 100% pulse width operation possible for DPWMB as well.

Since the rising edge on DPWMB is also fixed, Blanking B Begin and End can be used for blanking this rising edge. In this mode, Blanking A works only on the falling edge of A, and Blanking B works only on the falling edge of B.

And, of course, Cycle Adjust B is usable on DPWM B.

There is no restriction preventing the two signals from overlapping each other. The diagram shows the two signals 180 degrees out of phase, but this is not required. They could be 90 degrees, 60 degrees or whatever offset is desired.

### 2.6 DPWM Resonant Mode

The resonant mode operation depends on the status of the RESON\_DEADTIME\_COMP\_EN bit. Setting the RESON\_DEADTIME\_COMP\_EN bit provides for a symmetrical waveform where DPWMA and DPWMB have the same pulse width. As the switching frequency changes, the dead times between the pulses remain the same. This mode is ideal for the LLC topology.

Clearing the RESON\_DEADTIME\_COMP\_EN bit provides a mode where the pulse widths are the same and the duty cycle percentage is constant as the period changes. This means that as the frequency increases, the dead times shrink proportionally.

The equations for this mode are designed for a smooth transition from PWM mode to Resonant mode, as described in Section 2.10.1 Resonant LLC Example on page 27. Here is a diagram of this mode:

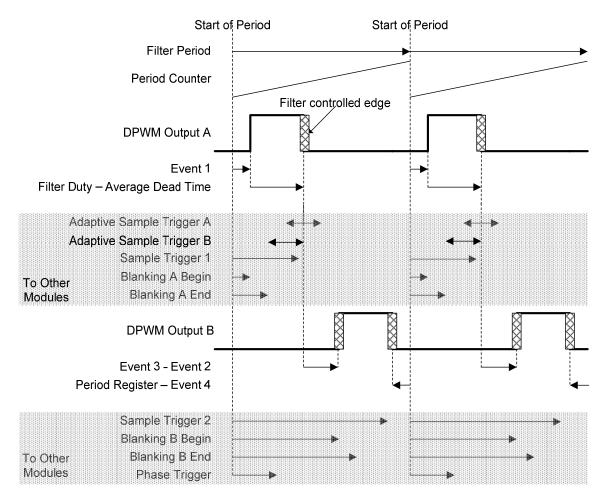

#### Resonant Symmetrical Closed Loop

Events which change with DPWM mode:

Dead Time 1 = Event 3 – Event 2

Dead Time 2 = Event 1 + Period Register – Event 4)

Average Dead Time = (Dead Time 1 + Dead Time 2)/2

DPWM A Rising Edge = Event 1

DPWM A Falling Edge = Event 1 + Filter Duty – Average Dead Time

Adaptive Sample Trigger A = Event 1 + Filter Duty + Adaptive Sample Register

Adaptive Sample Trigger B = Event 1 + Filter Duty/2 + Adaptive Sample Register

DPWM B Rising Edge = Event 1 + Filter Duty – Average Dead Time + (Event 3 – Event 2)

DPWM B Falling Edge = Filter Period – (Period Register – Event 4)

Phase Trigger = Phase Trigger Register value or Filter Duty

Events always set by their registers, regardless of mode:

Sample Trigger 1, Sample Trigger 2, Blanking A Begin, Blanking A End, Blanking B Begin, Blanking B End

#### **DPWM - Resonant Mode**

As seen later, the Filter module has two outputs, Filter Duty and Filter Period. In the Resonant mode, the Filter is configured so that the Filter Period is twice the Filter Duty. With zero dead times, each DPWM pin would be On for half of the period. For dead time handling, the average of the two dead times is

subtracted from the Filter Duty for both DPWM pins. Therefore both pins will have the same on-time, and the dead times will be fixed regardless of the period. The only edge which is fixed relative to the start of the period is the rising edge of DPWM A. Blanking A and Blanking B both work only on DPWMA.

# 2.7 Triangular Mode

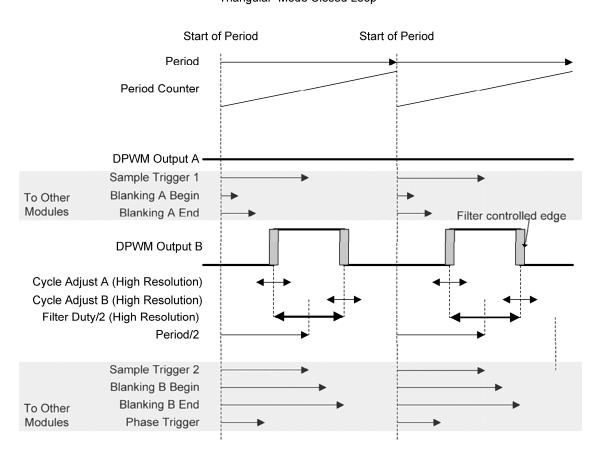

Triangular mode provides a very stable phase shift in interleaved PFC and similar topologies. In this case, the PWM pulse is centered in the middle of the period, rather than starting at one end or the other. In Triangular Mode, only DPWM B is available. Here is a diagram for Triangular Mode:

Triangular Mode Closed Loop

Events which change with DPWM mode:

DPWM A Rising Edge = None

DPWM A Falling Edge = None

Adaptive Sample Trigger = None?

DPWM B Rising Edge = Period/2 - Filter Duty/2 + Cycle Adjust A

DPWM B Falling Edge = Period/2 + Filter Duty/2 + Cycle Adjust B

Phase Trigger = Phase Trigger Register value or Filter Duty

Events always set by their registers, regardless of mode:

Sample Trigger 1, Sample Trigger 2, Blanking A Begin, Blanking A End, Blanking B Begin, Blanking B End

**DPWM - Triangular Mode**

All edges are dynamic in triangular mode, so fixed blanking is not that useful. The adaptive sample trigger is not needed. It is very easy to put a fixed sample trigger exactly in the center of the On-time, because the center of the on-time does not move in this mode. Both Blanking A and Blanking B are applied to DPWMB.

# 2.8 DPWM Leading Edge Mode

Leading edge mode is very similar to Normal mode, reversed in time. The DPWM A falling edge is fixed, and the rising edge moves to the left, or backwards in time, as the filter output increases. The DPWMB falling edge stays ahead of the DPWMA rising edge by a fixed dead time. Here is a diagram of the Leading Edge Mode:

Leading Edge Closed Loop

Events which change with DPWM mode:

DPWM A Falling Edge = Event 1

DPWM A Rising Edge = Event 1 - Filter Duty + Cycle Adjust A

Adaptive Sample Trigger A = Event 1 - Filter Duty + Adaptive Sample Register or

Adaptive Sample Trigger B = Event 1 - Filter Duty/2 + Adaptive Sample Register

DPWM B Rising Edge = Event 4

DPWM B Falling Edge = Event 1 - Filter Duty + Cycle Adjust A -(Event 2 - Event 3)

Phase Trigger = Phase Trigger Register value or Filter Duty

Events always set by their registers, regardless of mode:

Sample Trigger 1, Sample Trigger 2, Blanking A Begin, Blanking A End, Blanking B Begin, Blanking B End

**DPWM – Leading Edge Mode**

As in the Normal mode, the two edges in the middle of the period are dynamic, so the fixed blanking intervals are mainly useful for the edges at the beginning and end of the period.

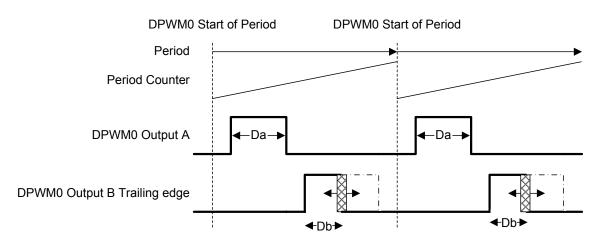

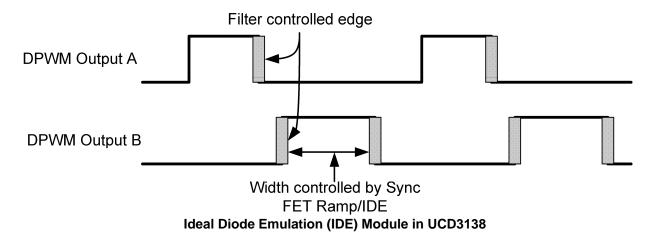

# 2.9 Sync FET Ramp and IDE Calculation

For many topologies, it is useful to replace diodes with synchronous rectification (SR), a concept also known as Ideal Diode Emulation (IDE). In continuous conduction mode, the SR FET control is simple, because it can be turned on for the entire off time of the primary FET, minus a dead time. This is handled perfectly by Normal mode. The Sync FET Ramp and IDE calculation are only available in Normal mode. They are not compatible with the Cycle by Cycle Fault module.

However, in discontinuous mode, the SR FET needs to be turned off before the end of the period. The UCD3138 hardware provides an automatic function to make this easier. In this case, the falling edge of DPWMB is adjusted, as shown below:

Normal Mode with Sync FET IDE and/or Ramp

Sync FET edge on DPWM B controlled by Ramp logic and/or Integrated Diode equation Stays within dead time limits for Normal Mode

#### **SyncFET IDE (Normal Mode)**

The digital hardware implements the equation  $D_b = D_a * K_d$ . The firmware measures Vin and Vout and calculates Kd. For example, for a Buck topology,  $K_d = (V_{in} - V_{out})/V_{out}$ , where  $D_a$  is duty cycle of the control FET,  $D_b$  is duty cycle of SR FET,  $V_{in}$  is input voltage and  $V_{out}$  is output voltage. The firmware periodically measures the slowly changing  $V_{in}$  and  $V_{out}$ , and puts the calculated result into the Kd register. The DPWM hardware adjusts  $D_b$  every switching cycle, maintaining proper IDE even during transients which cause rapid changes in  $D_a$ .

When starting up in prebias mode i.e. with a voltage already present on the outputs, it is difficult to accomplish precise diode emulation (IDE). One solution to this issue is to ramp the voltage up to the target without synchronous rectification (SR), and then to activate SR after the voltage is regulated. When activating or de-activating SR, in order to avoid glitches in the regulated voltage, it is best to gradually increase/decrease the Sync FET on-time. The UCD3138 provides what is termed as Sync FET Soft-On/Soft-Off (ramp) logic to accomplish this. This is documented in Section 3.3.8 Sync FET Soft On/Off using Ramp Module. The Ramp module in the Front End is used for this function. It will ramp up to either the limits imposed by normal mode, or to the limits imposed by the IDE logic.

With digital IDE enabled, as the system transitions from discontinuous mode into continuous conduction Mode (sync FET is on until end of the period) the IDE will stop reducing the Sync FET pulse width. This

is because the reverse conduction through the Sync FET will keep Da and Db the same. It is necessary to detect DCM (Discontinuous Conduction Mode) current levels in the IDE approach. Once these levels are detected, the Sync FET should be ramped down, and then ramped back up with IDE enabled.

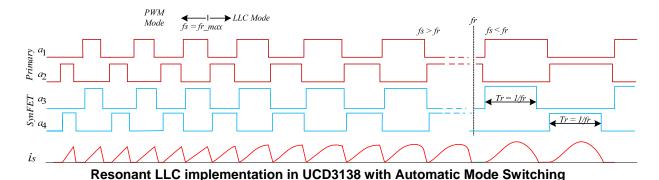

# 2.10 Automatic Mode Switching

Automatic Mode switching enables the DPWM module to switch between modes automatically, with no firmware intervention. This is useful to increase efficiency and power range and also to achieve smooth system performance (such as monotonic start-up) in certain topologies. An example of mode switching in LLC topology is provided next.

# 2.10.1 Resonant LLC Example

In Resonant LLC topology, three modes are used. At the lowest power, a pulse width modulated mode (Multi Mode) is used. As power increases and frequency decreases, Resonant mode is used. As the frequency gets still lower, resonant mode is still used, however the Sync FET driver changes so that the on-time is fixed and does not increase (SR Pulse Width is clamped). Here are the waveforms for the LLC:

2.10.2 Mechanism for Automatic Mode Switching

Many of the configuration parameters for the DPWM, including the mode, are in DPWM Control Register 1. For automatic mode switching, some of these parameters are duplicated in the Auto Config Mid and Auto Config High registers.

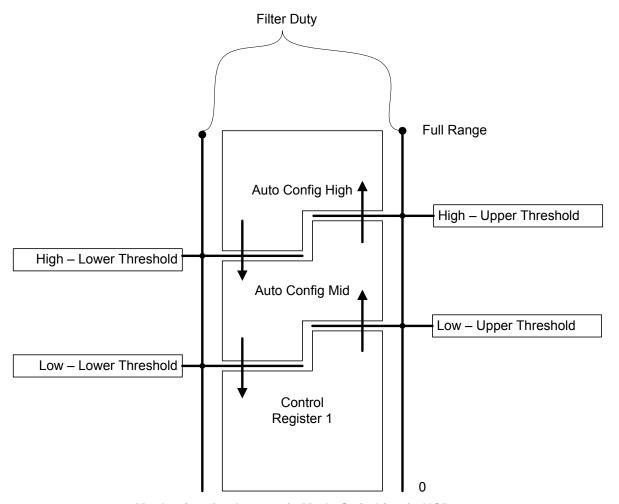

If automatic mode switching is enabled, the Filter Duty signal is used to select which of these three registers is used. There are 4 registers which are used to select the points at which the mode switching takes place. They are used as shown below:

# Automatic Mode Switching With Hysteresis

Mechanism for Automatic Mode Switching in UCD3138

As shown, the registers are used in pairs for hysteresis. The transition from Control Register 1 to Auto Config Mid only takes place when the Filter Duty goes above the Low Upper threshold. It does not go back to Control Register 1 until the Low Lower Threshold is passed. This prevents oscillation between modes if the filter duty is close to a mode switching point. In some applications it is necessary to make the values the same, disabling hysteresis. This has to be done to make the DPWM signals from the two modes match properly at the mode switching point.

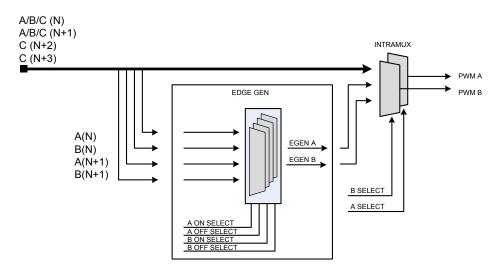

# 2.11 DPWMC, Edge Generation, IntraMux

The UCD3138 has sophisticated hardware for generating complex waveforms beyond the simple DPWMA and DPWMB waveforms already discussed. The DPWMC, the Edge Generation Module, and the IntraMux play a key role in delivering this capability

DPWMC is a signal inside the DPWM logic. It goes high at the Blanking B begin time, and low at the Blanking B end time.

The Edge Gen module takes DPWMA and DPWMB from its own DPWM module, and the next one, and uses them to generate edges for two outputs. For DPWM3, the DPWM0 is considered to be the next DPWM. Each edge (rising and falling for DPWMA and DPWMB) has 8 options which can cause it. The options are:

0 = DPWM(n) A Rising edge 1 = DPWM(n) A Falling edge 2 = DPWM(n) B Rising edge 3 = DPWM(n) B Falling edge 4 = DPWM(n+1) A Rising edge 5 = DPWM(n+1) A Falling edge 6 = DPWM(n+1) B Rising edge 7 = DPWM(n+1) B Falling edge

The Edge Gen is controlled by the DPWMEDGEGEN register. It also has an enable/disable bit.

The IntraMux is controlled by the Auto Config registers. The IntraMux takes signals from multiple DPWMs and from the Edge Gen. It can be programmed to route these signals to the DPWMA and DPWMB outputs. This is useful for complex topologies like Phase Shifted Full Bridge, especially when they are controlled with automatic mode switching. It is disabled by setting the Intramux to Pass Through mode for each of the DPWM signals, A and B. If the Intra Mux is enabled, high resolution must be disabled.

Here is a drawing of the Edge Gen/Intra Mux:

UCD3138 Edge-Gen & Intra-Mux

Here is a list of the IntraMux modes for DPWMA:

0 = DPWMA(n) pass through (default)

1 = Edge-gen output, DPWMA(n)

2 = DPWNC(n)

3 = DPWMB(n) (Crossover)

4 = DPWMA(n+1)

5 = DPWMB(n+1)

6 = DPWMC(n+1)

7 = DPWMC(n+2)

8 = DPWMC(n+3)

Here is a list of the IntraMux modes for DPWMB:

- 0 = DPWMB(n) pass through (default)

- 1 = Edge-gen output, DPWMB(n)

- 2 = DPWNC(n)

- 3 = DPWMA(n) (Crossover)

- 4 = DPWMA(n+1)

- 5 = DPWMB(n+1)

- 6 = DPWMC(n+1)

- 7 = DPWMC(n+2)

- 8 = DPWMC(n+3)

The DPWM number wraps around just like the Edge Gen unit. For DPWM4, DPWM(n+1) is DPWM0, DPWM(n+2) is DPWM1, and so on.

Note that the Fault logic affects the Fault module, which is before the Edge Gen and IntraMux units (refer to DPWM Block diagram in section 2.1). The effect of a fault must be calculated taking into account the impact of the Edge Gen and IntraMux units.

# 2.12 Time Resolution of Various DPWM registers

Different registers in the DPWM block have different time resolutions. Pulse widths are generally adjustable in nominal 250 picosecond steps, while period and phase shift are adjustable in 4 nanosecond steps. The sample trigger is adjustable in 16 nanosecond steps.

| Register                | Resolution | Number of bits | Bit Alignment |

|-------------------------|------------|----------------|---------------|

| Phase Trigger,          | 4 ns.      | 14             | Standard      |

| Period,                 |            |                |               |

| Event1,                 |            |                |               |

| Blanking A and B Begin  |            |                |               |

| Blanking A and B End    |            |                |               |

| Minimum Duty Cycle Low  |            |                |               |

| Minimum Duty Cycle High |            |                |               |

| Counter Preset          |            |                |               |

| Sample Trigger 1 and 2  | 16 ns      | 12             | Standard      |

| Event2,3,4              | 250 ps     | 18             | Standard      |

| Cycle Adjust A and B    | 250 ps     | 16 (signed)    | Standard      |

| Adaptive Sample         | 16 ns      | 12 (signed)    | 16 ns LSbit   |

| Resonant Duty           | 4 ns.      | 16 (signed) or | 4 ns LSbit    |

| _                       |            | 14 (unsigned)  |               |

#### **DPWM Register Time Resolutions in UCD3138**

On the UCD3138, all these registers are aligned so that their bit fields match the scaling, except for the Resonant Duty and Adaptive Sample register. All the registers are unsigned, except for the 2 adjust registers, Resonant Duty and Adaptive Sample register, which are signed to permit positive or negative adjustment.

The Resonant Duty register is used in the UCD3138 LLC reference firmware (implemented in UCD3138LLCEVM-028 EVM) as a 14 bit unsigned register. It can also be used as a 16 bit signed register. See Section 2.21 Resonant Duty Register, page 44.

This means that the Phase Trigger, Period, and Event1 registers ignore the 4 least significant bits, as shown below:

DPWM Period Register (DPWMPRD) – All other 4 ns registers with standard alignment are the same.

| Bit Number | 17:4              | 3:0      |  |  |

|------------|-------------------|----------|--|--|

| Bit Name   | PRD               | RESERVED |  |  |

| Access     | R/W               | -        |  |  |

| Default    | 00_0011_0100_0001 | 0000     |  |  |

The Sample Trigger registers ignore the 6 least significant bits, as shown here:

DPWM Sample Trigger 1 Register (DPWMSAMPTRIG1)

| Bit Number | 17:6           | 5:0      |

|------------|----------------|----------|

| Bit Name   | SAMPLE_TRIGGER | RESERVED |

| Access     | R/W            | -        |

| Default    | 0000_0010_0000 | 00_0000  |

Only the Event 2, 3, and 4 registers use all 18 bits of the field, as shown below.

DPWM Event 2 Register (DPWMEV2) – Event 3 and 4 are the same, Cycle Adjust registers only go to bit 15.

| Bit Number | 17:0                   |  |  |

|------------|------------------------|--|--|

| Bit Name   | EVENT2                 |  |  |

| Access     | R/W                    |  |  |

| Default    | 00_0000_0001_0110_0011 |  |  |

This means that in all these registers, each bit has the same weight in terms of time. This makes configuration simpler, since all register loads can use the same time base.

To use this feature, use the .all extension on the register structure. The bit fields do not include the ignored bits.

All of these C statements put 100 microseconds into the respective registers. Note that the "Low" resolution clock is at 4 nanoseconds, and "High" resolution is at 250 picoseconds. So the corresponding numbers for the registers are 2,500 and 40,000 respectively.

Dpwm0Regs.DPWMPRD.all = 40000; //includes 4 unused least significant bits

Dpwm0Regs.DPWMPRD.bit.PRD = 2500; //only puts in PRD bit field = 40000/16

Dpwm0Regs.DPWMEV1.all = 40000; //includes 4 unused bits

Dpwm0Regs.DPWMEV1.bit.EVENT1 = 2500; //EV1 is the only low resolution event register

Dpwm0Regs.DPWMEV2.all = 40000; //EV2 is high resolution, so

Dpwm0Regs.DPWMEV2.bit.EVENT2 = 40000; //both forms are the same

Dpwm0Regs.DPWMSAMPTRIG1.all = 40000; //includes 6 unused lsbs

Dpwm0Regs.DPWMSAMPTRIG1.bit.SAMPLE\_TRIGGER = 625;

//needs to be divided by 64 for 6 bits

The adaptive sample and resonant duty registers do not follow the standard bit alignment. Their least significant bits are worth 16 nanoseconds and 4 nanoseconds respectively.

#### 2.13 PWM Counter and Clocks

The PWM counter is the center of the DPWM logic. There is no register that can be read to give the value of the PWM counter, but most events are triggered by it. In all modes it is allowed to count up to the period value, and then restarted at zero. Since it restarts at zero, the period is technically equal to PERIOD + 1. So in the example above, the number should really be 2499. Generally the error is unimportant. In all modes but the resonant modes, the period is a fixed value. In the resonant modes, the period comes from the output of a Filter.

The PWM counter is also restarted by the receipt of a sync signal (if sync is enabled), as shown above in Section 2.4, DPWM Phase Shift Mode on page 19.

Sync signals received exactly at the end of the period run very smoothly. Sync signals received at other times during the period will restart the counter and the period. The effects of this should be taken into consideration for each application.

Even though the period register has only 14 bits, the PWM counter effectively has 18 bits. Each 4 nanosecond period is subdivided into 16 intervals, nominally 250 picoseconds long. The extra 4 bits representing these intervals are called "high resolution bits".

# 2.14 DPWM Registers - Overview

This section discusses each DPWM register, with examples of their use where appropriate. In addition, it interacts with many other peripherals, parts of which are also described below.

# 2.15 DPWM Control Register 0 (DPWMCTRL0)

The DPWM Control Register 0 is one of 3 DPWM control registers which configure the DPWM. All 3 registers control a variety of DPWM functions. It is not possible to draw a clear dividing line between the 3 registers.

# 2.15.1 DPWM Auto Config Mid and Max Registers

There are two other registers – DPWMAUTOMAX and DPWMAUTOMID, which have many of the same bits as control register 0.

These two Auto Mode Switching (AMS) registers are used in topologies where the DPWM mode changes automatically as the filter output changes, such as resonant and phase shifted full bridge. See the section 2.10.2Mechanism for Automatic Mode Switching in page 27 on the auto switch level registers for more information on mode switching.

Not all bits in DPWMCTRL0 are duplicated in the auto registers. The bits that occur only in DPWMCTRL0 are used for all modes. Bits were selected based on mode switching needs for LLC and PSFB topologies. The following bitfield descriptions tell whether each field occurs in the auto mode switching registers.

#### 2.15.2 Intra Mux

The Intra Mux bit fields, PWM\_A\_INTRA\_MUX, and PWM\_B\_INTRA\_MUX, enable signals from different sources to be multiplexed into the 2 DPWM outputs, A and B. This functionality is used in full and half bridge topologies. The default value for this bit field, 0, causes normal functionality, with the standard DPWM waveforms as described in the mode descriptions above section to appear on the DPWMA and DPWMB pins. For details of the Intra Mux, see section 2.11 DPWMC, Edge Generation, IntraMux, page 28.

These fields also occur in the AMS registers.

## 2.15.3 Cycle by Cycle Current Limit Enable

There are several enable bits related to cycle by cycle current limit:

DPWMCTRL0 contains:

CBC\_PWM\_C\_EN

CBC\_PWM\_AB\_EN

CBC\_ADV\_CNT\_EN

CBC\_SYNC\_CUR\_LIMIT\_EN

CBC\_BSIDE\_ACTIVE\_EN

All of these bits, except for CBC BSIDE ACTIVE EN also occur in the AMS registers.

The first two, CBC\_PWM\_C\_EN and CBC\_PWM\_AB\_EN simply enable cycle by cycle current limit for their respective signals.

The other three bits have different effects in different modes. Here are the effects:

#### **Normal Mode**

In normal mode, a CBC event will cause DPWMA to go low before the time dictated by the CLA. The dead time for DPWMB will be preserved, so the rising edge of DPWMB will be moved forward by the same amount as the falling edge of DPWMA.

There are only two options for setting the CBC bits in normal mode:

- 1. All cleared, no CBC.

- 2. Set both CBC\_PWM\_AB\_EN and CBC\_ADV\_CNT\_EN to get CBC.

CBC BSIDE ACTIVE EN has no effect.

#### Resonant/multi Mode

In resonant/multi mode, the systems are often symmetrical. In this case, DPWMB may need to be controlled by the Cycle by Cycle Fault logic as well. Sometimes a short pulse on one DPWM pin needs to be followed by an equal length pulse on the other DPWM pin to prevent an offset from building up in a capacitor or inductor. In this case, it is possible to enable *phase matching* in these two modes. If DPWMA or DPWMB is cut short by a CBC event, the next pulse, on the other DPWM pin, will also be shortened to the same length.

Here are the states for resonant and multi modes:

- o All cleared no CBC

- Only CBC PWM AB EN set CBC on A only, no phase matching

- CBC\_PWM\_AB\_EN and CBC\_BSIDE\_ACTIVE\_EN only set CBC on A and B, no phase matching

- o All three set CBC on A and B, phase matching

- CBC\_PWM\_AB\_EN and CBC\_ADV\_CNT\_EN set, CBC\_BSIDE\_ACTIVE\_EN not set CBC on A only and B phase matches to A

#### Truth table:

| CBC_PWM_AB_EN | CBC_ADV_CNT_EN | CBC_BSIDE_ACTIVE_EN | CBC A | CBC B | phase match |

|---------------|----------------|---------------------|-------|-------|-------------|

| 0             | x              | x                   | 0     | 0     | 0           |

| 1             | 0              | 0                   | 1     | 0     | 0           |

| 1             | 1              | 0                   | 1     | 0     | B matches A |

| 1             | 1              | 1                   | 1     | 1     | 1           |

CBC\_SYNC\_CUR\_LIM\_EN is used to control the slave sync. If this bit is set, the slave sync is advanced during current limit. This is not used in any topology configuration at this time. If this bit is set, the sync out pulse from the DPWM will occur if the CBC fault occurs. If the CBC fault does not occur during a period, the sync pulse will occur according to the normal setting of the sync control bit fields.

For more information on cycle by cycle current limit, refer to the section 6 Fault Mux in page 80.

#### 2.15.4 Multi Mode on/off

The MULTI\_MODE\_CLA\_A\_OFF and MULTI\_MODE\_CLA\_B\_OFF bits dictate which calculation is used for each DPWM pin in multi mode only. In other modes they should not be set. If the bit is cleared, the on-time of the DPWM pin is controlled by the Filter output. If the bit is set, then the on-time is controlled by the Event registers.

The AMS registers only have MULTI\_MODE\_CLA\_B\_OFF, they do not have MULTI\_MODE\_CLA\_A\_OFF.

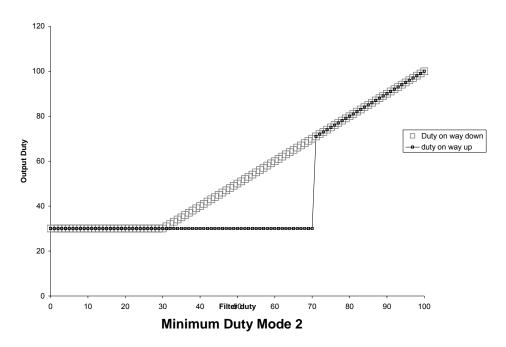

# 2.15.5 Minimum Duty Mode

The MIN DUTY MODE bits select how the DPWM handles minimum duty cycle limits.

- o 0 Default Filter output is passed directly through to the DPWM

- o 1 Filter value passed through if above minimum. If below minimum, no pulse from DPWM

- 2 Filter value passed through if above minimum. If below minimum, DPWM pulse width = minimum value

There are two registers setting minimum duty and hysteresis:

DPWMMINDUTYLOW DPWMMINDUTYHI

The Low register sets the point at which the minimum duty mode will take effect as the duty drops. In mode 2, it also sets the minimum duty.

The High register sets the point at which minimum duty mode is exited as the duty goes up.

These bits are not duplicated in the AMS registers.

10

20

30

40

50

Filter Duty

These two graphs show modes 1 and 2 with PMMINDUTYLOW at 30, and DPWMMINDUTYHI at 70.

Min duty mode 1 with hysteresis

# 100 80 80 40 20 -

**Minimum Duty Mode 1**

60

100

# 2.15.6 Master Sync Control Select

The MASTER SYNC CNTL SEL bit selects where the sync output of the DPWM channel comes from.

The default value, 0, causes the sync delay to come from the Phase Trigger register. This is useful for systems that have fixed intervals between phases, such as interleaved PFC and hard switching full bridge. See Section 2.4, DPWM Phase Shift Mode, on page 19.

Putting a 1 into this bit causes the master sync output to be controlled by the Filter output.

This bit is duplicated in the AMS registers.

# 2.15.7 Master Sync Slave Enable

Setting the MSYNC\_SLAVE\_EN bit enables the DPWM channel to be slaved to the sync output of another DPWM channel. This bit works together with the DPWMx\_SYNC\_SEL bits in the DPWMMUX register in the Loop Mux section. The sample code below makes DPWM1 a slave to DPWM0:

LoopMuxRegs.DPWMMUX.bit.DPWM1\_SYNC\_SEL = 0; //DPWM1 is slave to DPWM0 Dpwm1Regs.DPWMCTRL0.bit.MSYNC\_SLAVE\_EN = 1; //enable slave mode for DPWM1

This bit is not duplicated in the AMS registers.

#### 2.15.8 D Enable

Normally, the Filter Duty (D) is used to set the on-time of DPWM pins directly. In other words, OnTime = D. The D\_ENABLE bit can be used to make the OnTime = 1-D instead.

A default value (0) causes the output of the Filter to be used directly for DPWM output calculations. So in multi mode, for example, the DPWMA and B on-times would increase as the Filter Duty increases.

If the D\_ENABLE bit is set, however, the Filter Duty is subtracted from the period register. In this case, as the Filter Duty increases from zero to full range, the on-time will decrease from 100% of the period to 0% of the period.

This bit is not duplicated in the AMS registers.

## 2.15.9 Resonant Mode Fixed Duty Enable

The RESON\_MODE\_FIXED\_DUTY\_EN bit only controls the duty cycle width in the resonant modes. With the default (0) value, the duty cycle comes from the filter directly. This is for use above the lower resonant frequency, Fmin, and provides a duty cycle that fills half the period minus a fixed dead time.

Setting this bit causes the pulse width to be derived from the Auto Switch High Upper Threshold Register.

This bit is generally only set for LLC for the Sync FETs in the mode where the output frequency is below the lowest resonant frequency of the circuit. At this point any increases in pulse width are not beneficial, so they are stopped. There is also a waveform showing the modes in Section 2.10.1, Resonant LLC Example on page 27.

This bit is duplicated in the AMS registers.

## 2.15.10 DPWM A and B Fault Polarity

The PWM\_A\_FLT\_POL and PWM\_B\_FLT\_POL bits increase the flexibility of the DPWM by permitting arbitrary output states for the DPWM pins in case of a fault. The values in these bits will also appear on these pins when the DPWM is disabled. These values actually appear on the output of the Fault Module in the DPWM. Therefore, if the IntraMux or Edge Generation units are used, the same value may not appear on the output of the DPWM.

These bits do not affect the DPWM status after device reset. After reset, all DPWM pins are configured as outputs and actively driven low.

These bits are not duplicated in the AMS registers.

#### 2.15.11 Blank Enable

The BLANK\_A\_EN and BLANK\_B\_EN bits are used for fault detection. They work with the blanking registers – See Section 2.26 Blanking Registers on page 46 – to enable blanking for current limit detection. Without blanking, noise may cause false Cycle By Cycle (CBC) fault detection.

These bits are not duplicated in the AMS registers.

#### 2.15.12 **DPWM Mode**

The PWM\_MODE bits select the mode for the DPWM. See the DPWM reference section for the mode numbers, and sections above for the descriptions of the various modes.

These bits are duplicated in the AMS registers.

#### 2.15.13 **DPWM Invert**

The PWM A INV and PWM B INV bits invert the output of the DPWMA and DPWMB pins.

These bits do not affect the DPWM status after device reset however. After reset, all DPWM pins configured as outputs which are actively driving low.

These bits are not duplicated in the AMS registers.

## 2.15.14 Filter Enable (CLA\_EN)

In the past, the filter was called a Control Law Accelerator, so for historical reasons, the Filter Enable bit is called CLA\_EN. This bit, when set, causes the DPWM to take its input from a Filter. Otherwise, the DPWM output comes from the DPWM registers only.

This bit is duplicated in the AMS registers.

The filter which controls each DPWM is selected by the DPWMx\_FILTER\_SEL bit in the DPWMMUX register in the Loop Mux.

#### **2.15.15 DPWM Enable**

The PWM\_EN bit, when set enables the DPWM channel. If it is 0 (default), the DPWM outputs are set to the value in the DPWM Fault Polarity bits (Section 2.15.10 DPWM A and B Fault Polarity on page 37.

This bit occurs only in the Control 0 register, not in the AMS registers.

# 2.16 DPWM Control Register 1

Like DPWMCRTL0, the DPWMCTRL1 register contains a wide assortment of control bits for the DPWM.

#### 2.16.1 Period Counter Preset Enable

The PRESET\_EN bit adds flexibility for systems with multiple DPWM modules that have different period starting times. It can be used to start up all DPWMs simultaneously, even if their periods do not start at the same times. It can also be used for synchronizing these DPWMs.

Normally, the period counter is reset to zero by three events

- 1. DPWM ENABLE

- 2. Sync Received (slave mode enabled)

- 3. Counter reaches Period Register value

If PRESET\_EN is enabled, this changes:

- 1. DPWM\_ENABL:E Period Counter set to preset value

- 2. Sync Sync Received (slave mode enabled) Period Counter set to preset value

- 3. Counter reaches Period Register value Period counter set to zero

## 2.16.2 Sync FET Ramp Enable

The SYNC\_FET\_EN bit enables the Sync FET Ramp logic to take control of DPWM B. For more on the Ramp logic, see Section 3.3.8 Sync FET Soft On/Off using Ramp, on page 59. The Front End which provides the Ramp data is selected in the DPWMMUX register in the Loop Mux. The following code enables Sync FET Ramp for DPWM0, and sets up Front End 0's Ramp Engine to provide the ramp source.

LoopMuxRegs.DPWMMUX.bit.DPWM0\_SYNC\_FET\_SEL = 0;

//use ramp engine on Front End 0

Dpwm0Regs.DPWMCTRL1.bit.SYNC\_FET\_EN = 1; //enable sync FET ramp

The Sync FET Ramp logic ramps the pulse width of DPWMB up from a starting point to a width controlled by Normal mode, or by the IDE function, if enabled. It only works in Normal mode.

#### 2.16.3 Burst Mode Enable

Setting the BURST\_EN bit enables burst (light load) mode for this DPWM. For more information on Light load mode, see the light load section.

## 2.16.4 Current/Flux Balancing Duty Adjust

Setting the CLA\_DUTY\_ADJ\_EN bit enables the Current Balancing logic to modify the input to the DPWM so that current controlled by this DPWM can be balanced with the current controlled by another DPWM in the same UCD3138. For more information, see the Current Balancing section.

# 2.16.5 Sync Out Divisor Selection

The SYNC\_OUT\_DIV\_SEL bit field selects a divisor generating the sync out pulse on the external sync out pin. It is only effective on the sync out, not on internal chip sync signals sent to other DPWMs.

The divisor has 4 bits, and a range from 1 to 16 for the divisor. The divisor = SYNC OUT DIV SEL + 1.

So 0 in the bit field would give a divisor of 1, 1 gives a divisor of 2, and so on.

#### 2.16.6 Filter Scale

The CLA\_SCALE bits control shifting of the Filter Duty output before it is used by the DPWM. Shifts available range from a 3 bit right shift to a 3 bit left shift. The Filter Period is not scaled by these bits.

The default value, 0, causes no shift. For the shift table, see the DPWM reference section 8.2, DPWM Control Register 1 (DPWMCTRL1)on page 94.

This can be used in complex topologies where the same filter output is needed for different circuits at different frequencies. It can also be used to change the overall gain of the Filter.

## 2.16.7 External Sync Enable

Setting the EXT SYNC EN bit causes the DPWM to use the Sync In pin as a source for Sync.

## 2.16.8 Cycle By Cycle B Side Active Enable

For more on the CBC\_BSIDE\_ACTIVE\_EN bit, see Section 2.15.3 above Cycle by Cycle Current Limit Enable on page 33.

## 2.16.9 Auto Mode Switching Enable

The AUTO\_MODE\_SEL bit, when set, enables auto mode switching.

## 2.16.10 Event Update Select

The EVENT\_UP\_SEL enables 4 different modes of DPWM Event Updating. The DPWM needs a period of 72 nanoseconds (nominal) to update its timing for the next period. During this period, it takes the latest Filter outputs and any firmware changes to register values and recalculates the timing of the DPWM signals. The time selected for update should NOT have any DPWM edges moving in or out of the window.

**CAUTION:** If DPWM edges move in or out of the Event Update Window, those transitions may be missed, leading to DPWM pulses longer or shorter than expected.

The modes are:

- o 0 As soon as Filter calculation is done

- o 1 At end of period (starts at end of period, and extends 72 nsec into start of new period)

- o 2 At time set by sample trigger 2

- o 3 At both End of Period and at time set by sample trigger 2

Note that all modes except for mode 1 make the Event Update timing dependent on the position of the sample trigger. For most topologies, mode 1 is used, and dead times or minimum pulse widths are used to keep moving edges out of the first 72nsec of the DPWM period. Please refer to the reference firmware code provided with UCD3138 EVMs for specific guidance regarding each topology.

#### 2.16.11 Check Override

The CHECK\_OVERRIDE bit, when set, overrides the internal DPWM checking. The DPWM checking will prevent invalid placement of Event settings/period settings or invalid configurations.

Setting this bit may be necessary for some topologies.

#### 2.16.12 Global Period Enable

The GLOBAL\_PERIOD\_EN bit, if set, enables the use of the Global Period register to provide the period for this DPWM. It is intended for use with systems which use multiple DPWMs and have need for frequency dithering. This makes it possible to change the frequency of multiple DPWMs at one location.

For more information, see 5.8 PWM Global Period Register (PWMGLBPRD), page 78.

# 2.16.13 Using DPWM Pins as General Purpose I/O

There are 6 bits in DPWMCTRL1 which can be used to make the DPWM pins into general purpose I/O pins:

These bits take effect immediately.

- PWM\_A\_OE 1 makes DPWMA into an output if enabled as a GPIO, 0 makes it an input

- o PWM B OE 1 makes DPWMB into an output if enabled as a GPIO, 0 makes it an input

- o GPIO A VAL Value put on DPWMA if it is an output

- o GPIO\_B\_VAL Value put on DPWMA if it is an output

```

GPIO_A_EN - 1 enables DPWMA as a GPIO GPIO_B_EN - 1 enables DPWMB as a GPIO

```

In addition, there are 2 bits in the DPWMOVERFLOW register which are also used for GPIO:

- o GPIO A IN reports level on DPWM A pin if used as input

- GPIO\_B\_IN reports level on DPWM\_B pin if used as input

# 2.16.14 High Resolution enable/disable

There are 5 bits which all enable/disable High Resolution Mode in some way or another

- PWM\_HR\_MULT\_OUT\_EN Set only for multi mode

- o HIRES SCALE (2 bits) Sets resolution of DPWM high res block

- o ALL PHASE CLK ENA enables all phases or only needed phases