# Digital Amplifier TAS57xx Family Deep Dive

Ryan Wang (王凡)

<u>ryan-wang@ti.com</u> Ver. 2009/10/1

### **About This Slides**

- This slide gives detail and advanced descriptions for TAS57xx devices, some examples are also provided to help customer to do programming.

- The method and function provided in this slides are mostly based on TAS5706. However, most of functions for the device in TAS57xx family are the same, take this slides for your reference.

- This slide is suitable for experienced FAE and customer engineer.

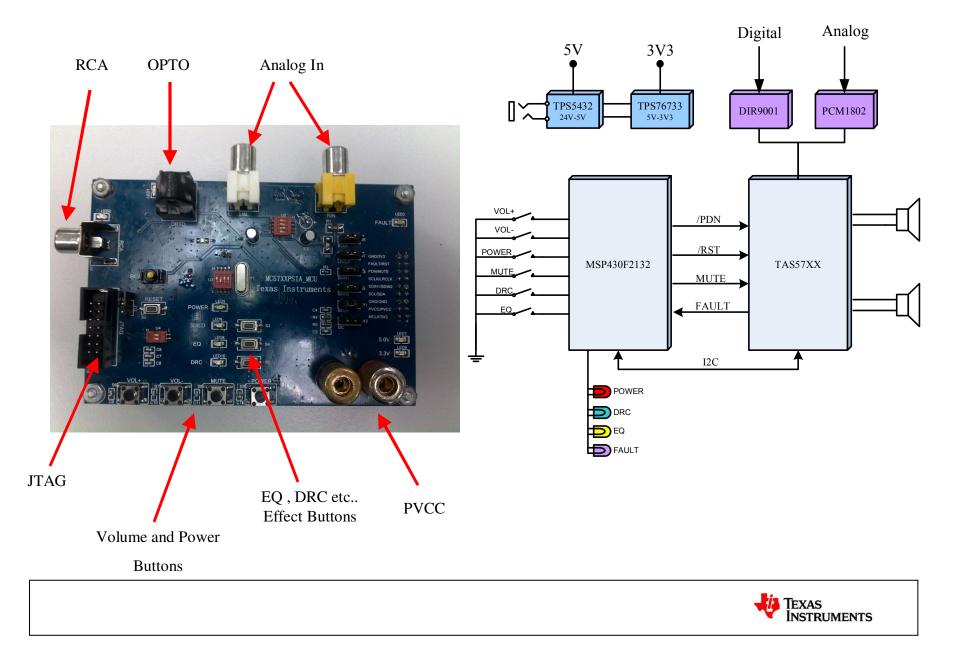

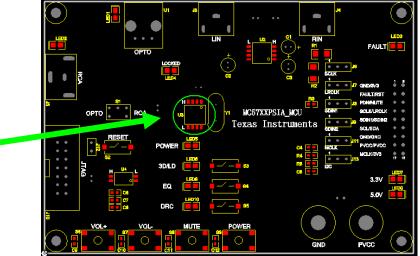

### **TAS57XX MCU EVM Design Review**

### **TAS57XX MCU EVM Project Overview**

### What's the diff. between GDE and MCU Ver.

| GDE Version                                                                                                                                                                                                                                                                                                                                                                                                   | MCU Version                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Advantages                                                                                                                                                                                                                                                                                                                                                                                                    | Advantages                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| <ol> <li>Integrated EQ, DRC parameters generator GUI.</li> <li>Can modify register parameters by User.</li> <li>Graphic User Interface is preferred by some customers.</li> </ol>                                                                                                                                                                                                                             | <ol> <li>Stand alone demo board running without PC.</li> <li>TI can provide sample code for customer now.</li> <li>Demo EQ, DRC, Loudness by press only one button.</li> <li>Support All standard TAS57XX EVM daughter board.</li> <li>Integrated swift DC/DC controller, only one PVCC is required.</li> <li>ADC is replaced by PCM1802 with better performance for test.</li> <li>TI FAE can evaluate different timing sequence on this EVM.</li> </ol> |  |  |  |  |  |

| Disadvantages                                                                                                                                                                                                                                                                                                                                                                                                 | Disadvantages                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| <ol> <li>Must have PC to demo our device to customer.</li> <li>Take more time when adjust EQ, DRC during demo.</li> <li>Can't provide coding guidance to customer</li> <li>Can't test exactly startup/shut down sequence</li> <li>AVCC and PVCC two power rails are needed.</li> </ol>                                                                                                                        | <ol> <li>Must need GDE to generate EQ, DRC etc parameters.</li> <li>Only engineer familiar with coding can modify register setting.</li> <li>Can't support GDE software.</li> </ol>                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| <ul> <li>Next Version combined all advantages: TAS57XX MCU EVM with TAS1020B</li> <li>1. Integrate TAS1020B in TAS57XX MCU EVM to support GDE software control from USB.</li> <li>2. I2C Jumpers are provided to select control source, from GDE USB control or MCU stand alone control.</li> <li>Nice to have:</li> <li>1. TAS1020B support USB I2S converting, provide USB audio input function.</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

1. TAS1020B support USB I2S converting, provide USB audio input function.

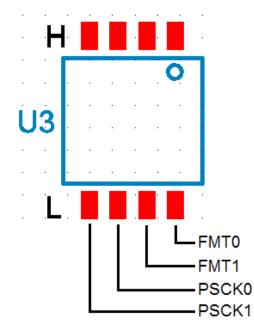

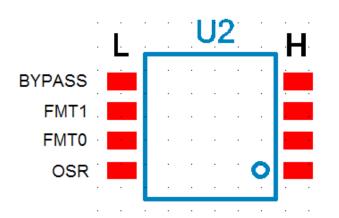

## **I2S Format Select Switch**

| FMT1      | FMT0              | S/PDIF DOUT FORMAT     |                              |      |  |  |  |

|-----------|-------------------|------------------------|------------------------------|------|--|--|--|

| L         | L                 | 16-bit, MSB-first, r   | right-justified              |      |  |  |  |

| L         | Н                 | 24-bit, MSB-first, 1   | right-justified              |      |  |  |  |

| Н         | L                 | 24-bit MSB-first, le   | eft-justified                |      |  |  |  |

| Н         | Н                 | 24-bit, MSB-first, I2S |                              |      |  |  |  |

| PSCK[1:0] | PSCK[1:0] SETTING |                        | OUTPUT CLOCK FROM PLL SOURCE |      |  |  |  |

| PSCK0     | PSCK1             | SCKO                   | ВСКО                         | LRCK |  |  |  |

| L         | L                 | 128fs                  | 64fs                         | fs   |  |  |  |

| L         | Н                 | 256fs                  | 64fs                         | fs   |  |  |  |

| Н         | L                 | 384fs 64fs fs          |                              |      |  |  |  |

| Н         | Н                 | 512fs 64fs fs          |                              |      |  |  |  |

### **ADC I2S Format Select Switch**

| FMT1 | FMT0 | ADC DOUT FORMAT                       |  |  |

|------|------|---------------------------------------|--|--|

| L    | L    | Left-justified, 24-bit                |  |  |

| L    | Н    | I2S, 24-bit                           |  |  |

| Н    | L    | Right-justified, 24-bit               |  |  |

| Н    | Н    | Right-justified, 20-bit               |  |  |

| BYP  | PASS | HPF(HIGH-PASS FILTER) MODE            |  |  |

| I    |      | Normal (no dc component on DOUT) mode |  |  |

| H    | ł    | Bypass (dc component on DOUT) mode    |  |  |

| OSR  |      | OVERSAMPLING RATIO                    |  |  |

| L    |      | 64fs                                  |  |  |

| Н    |      | 128fs (fs<50kHz)                      |  |  |

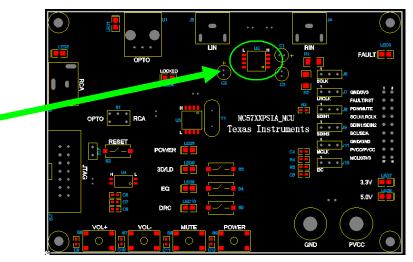

| P3.4 | P3.5 | OUTPUT TYPE                   |

|------|------|-------------------------------|

| L    | L    | 2.0 Channel Output            |

| L    | Н    | 2.1 Channel Output            |

| Н    | L    | 2.1 (external) Channel Output |

| Н    | Н    | 4.0 Channel Output            |

# **Firmware 1.0 function list**

- All function is based on TAS5706 now.

- 2.0 / 2.1 output has been supported.

- EQ, DRC demo for 2.0/2.1 is ok now.

- All Volume and Power control key function is OK.

- Already demo to customer successfully.

# **Device ID Version Check**

- All devices in TAS57xx family have Device ID, stored in 0x01 register.

- Same Device ID means basic functions provided are the same. (Unless disabled on purpose)

| Firmware Ver. | Device P/N                |

|---------------|---------------------------|

| 0x23          | TAS5705                   |

| 0x28          | TAS5706                   |

| 0x2A          | TAS5706A/TAS5706B/TAS5716 |

| 0x68          | TAS5708                   |

| 0x70          | TAS5707/TAS5709 /TAS5710  |

| ???           | TAS5711                   |

• Where I can find firmware version information?

---- Check this register in datasheet: "Device ID register"

|  |  | 0x01 | Device ID register | 1 | Description shown in subsequent section | 0x28 |

|--|--|------|--------------------|---|-----------------------------------------|------|

|--|--|------|--------------------|---|-----------------------------------------|------|

### **I2S-Input Family Comparison Matrix**

| Device                        | Closed<br>Loop | PVDD      | BQs | DRC              | SE 2.1 | PWM<br>Outs | Robust DC<br>Protection | 3D/Bass<br>Boost       | Audio Input<br>Ports | Package              |

|-------------------------------|----------------|-----------|-----|------------------|--------|-------------|-------------------------|------------------------|----------------------|----------------------|

| TAS5704 (H/W Ctrl)<br>(20W)   | Yes            | 10 to 26V | -   | -                | -      | 1x          | -                       | -                      | 2x<br>(32–192kHz)    | 10x10mm<br>64- HTQFP |

| TAS5705 (20W)                 | -              | 8 to 23V  | 18  | 2x               | -      | 2x          | -                       | -                      | 2x<br>(32–192kHz)    | 10x10mm<br>64- HTQFP |

| TAS5706A/B (20W)              | Yes            | 10 to 26V | 18  | 2x               | Yes    | 2x          | -                       | -                      | 2x<br>(32–192kHz)    | 10x10mm<br>64- HTQFP |

| TAS5716 (20W)                 | Yes            | 10 to26V  | 18  | 2x               | Yes    | 2x          | -                       | Yes                    | 2x<br>(32–192kHz)    | 10x10mm<br>64- HTQFP |

| TAS5707 (20W)                 | -              | 8 to 26V  | 14  | 1x               | _      | -           | -                       | -                      | 1x<br>(8–48kHz)      | 7x7mm<br>48- HTQFP   |

| TAS5708 (20W)                 | Yes            | 10 to 26V | 14  | 1x               | -      | -           | -                       | -                      | 1x<br>(8–48kHz)      | 7x7mm<br>48- HTQFP   |

| TAS5709 (20W)                 | -              | 8 to 24V  | 22  | 2-band           | _      | -           | -                       | Yes (Best)             | 1x<br>(8–48kHz)      | 7x7mm<br>48- HTQFP   |

| TAS5710 (20W)                 | Yes            | 10 to 26V | 22  | 2-band           | -      | -           | -                       | Yes (Best)             | 1x<br>(8–48kHz)      | 7x7mm<br>48- HTQFP   |

| TAS5711 (20W)                 | -              | 8 to 26V  | 21  | 2-band           | Yes    | -           | -                       | Yes (Best)             | 1x<br>(8–48kHz)      | 7x7mm<br>48- HTQFP   |

| TAS5713 (25W)<br>(110mΩ FETS) | -              | 8 to 26V  | 18  | 2-band<br>(Best) | -      | -           | -                       | Improved<br>Bass Boost | 1x<br>(8–48kHz)      | 7x7mm<br>48- HTQFP   |

| TAS5715 (25W)<br>(110mΩ FETS) | -              | 8 to 26V  | 16  | 2-band<br>(Best) | -      | 1x          | Yes                     | Improved<br>Bass Boost | 1x<br>(8–48kHz)      | 7x7mm<br>48- HTQFP   |

**P2P/Footprint Compatible**

P2P/Footprint Compatible

P2P/Footprint Compatible

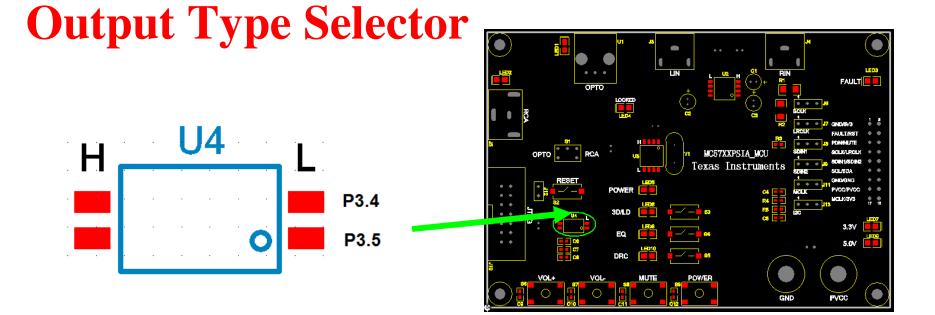

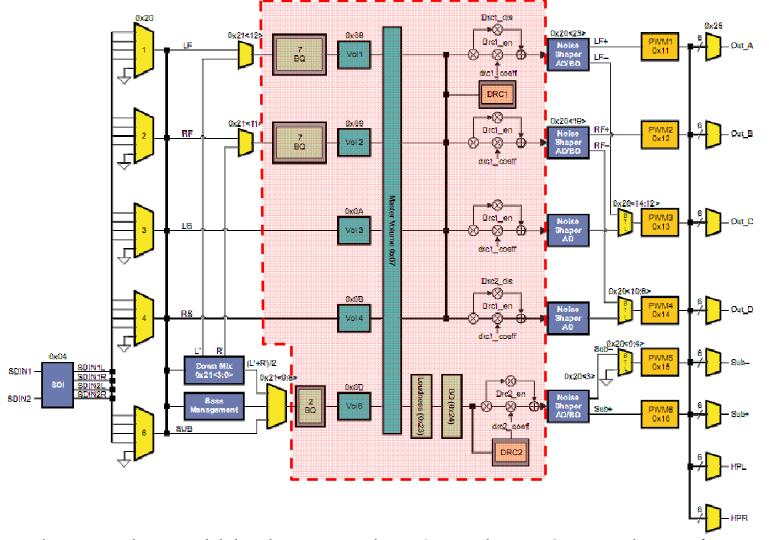

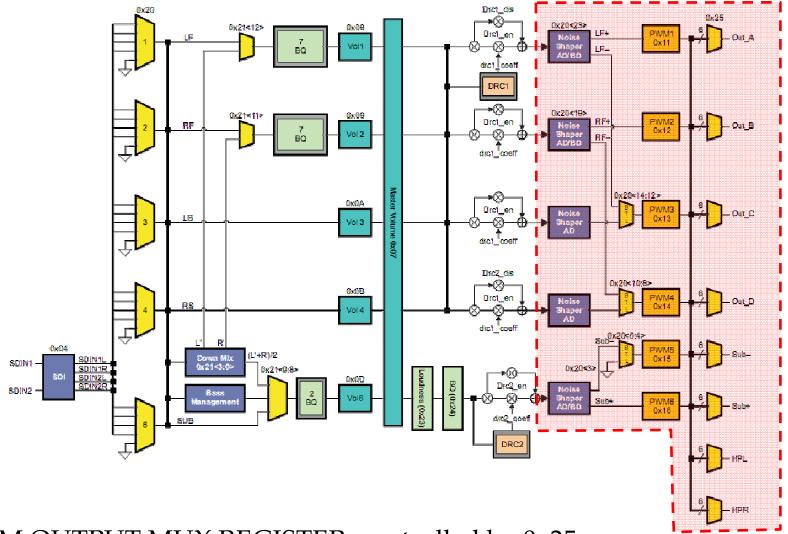

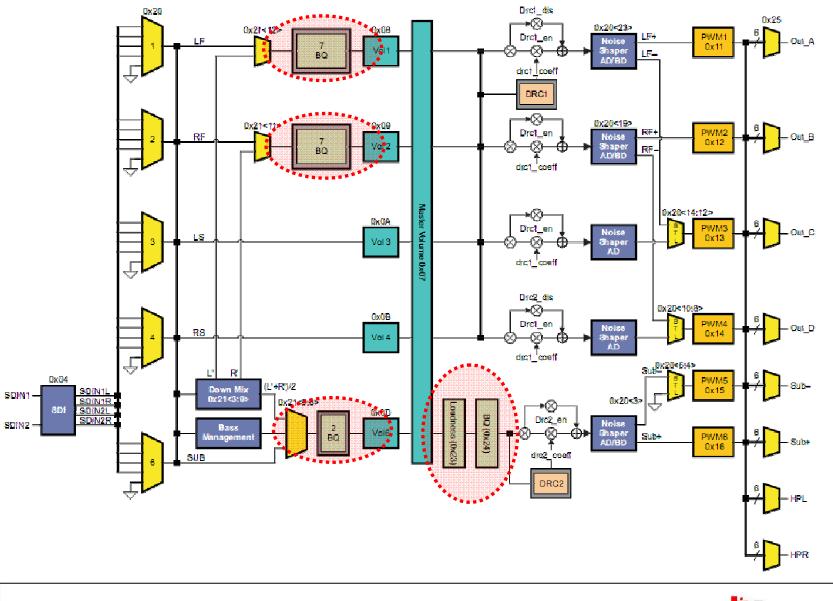

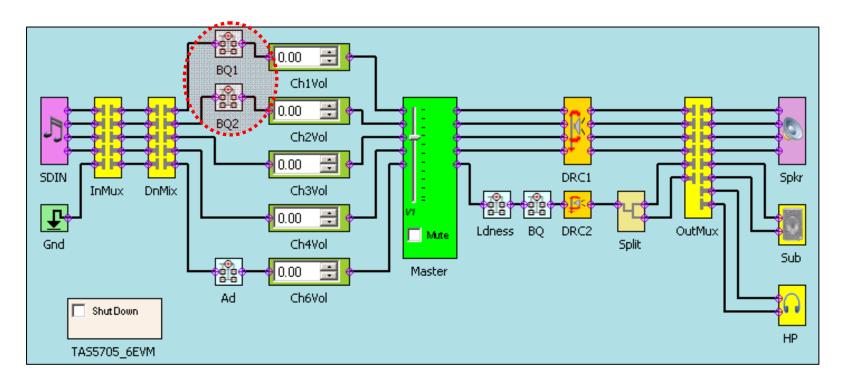

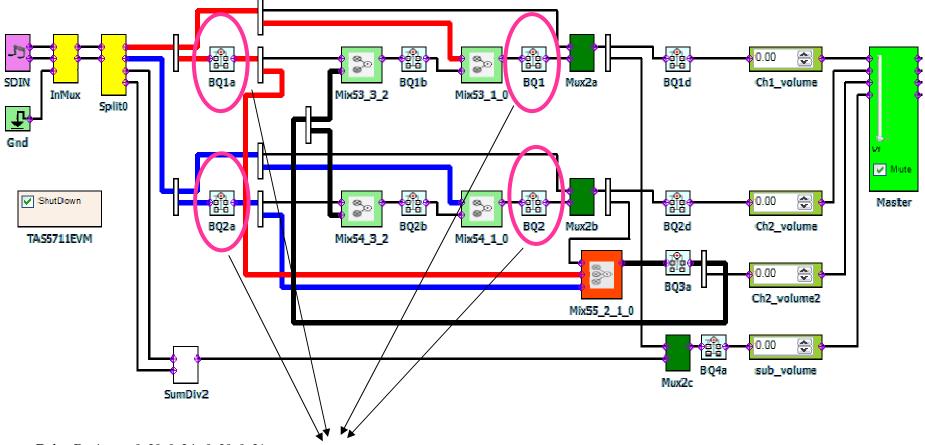

### **Typical Signal Flow of TAS57XX**

### **Get Started with Typical Signal Flow of TAS57xx**

### Get Started with Typical Signal Flow of TAS57XX

Internal DAP channel blocks provide EQ, Vol, DRC, Loudness functions.

### Get Started with Typical Signal Flow of TAS57XX

PWM OUTPUT MUX REGISTER, controlled by 0x25.

# **Critical Registers Setting**

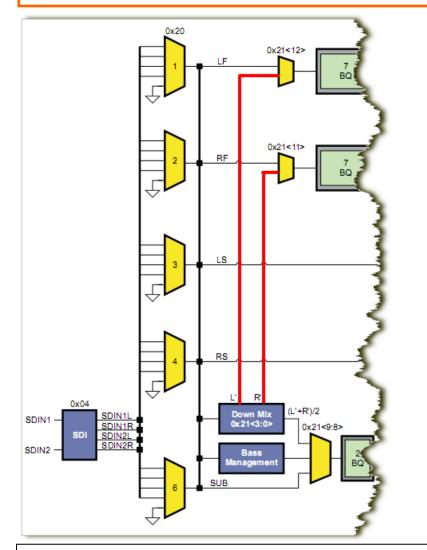

### **INPUT MUX and DOWN MIX REGISTERS**

*Register: 0x20 Register: 0x21*

### 0x20, INPUT MULTIPLEXER REGISTER

Invert Output Phase

| Table 19. Input Multiplexer Register (0x20) |                     |       |                       |     |            |       |        |                                          |

|---------------------------------------------|---------------------|-------|-----------------------|-----|------------|-------|--------|------------------------------------------|

| D31                                         | D30                 | D29   | D28                   | D27 | D26        | D25   | D24    | FUNCTION                                 |

| 0                                           | 0                   | -     | -                     |     | -          | _     | -      | Reserved = 0x00                          |

|                                             |                     | 0     |                       |     |            |       |        | Do not negate Ch6 volume in speaker mode |

|                                             |                     | 1     |                       |     |            |       |        | Negate Ch6 volume in speaker mode (1)    |

|                                             |                     |       | 0                     |     |            |       |        | Do not negate Ch5 volume in speaker mode |

|                                             |                     |       | 1                     |     |            | l I   |        | Negate Ch5 volume in speaker mode (1)    |

| the total                                   | Transferrer and the | n-min | and the second second | 0.  | ANNIA ROAD | hanne | JANNA. | Do not negate Ch4 volume in speaker mode |

#### [D31:D24] Output Phase Negative Function On/Off

Set these bits to 1 means that channel output phase is inverted by 180degree. This function is used in Single Ended output, to avoid supply pumping effect. Remember speaker wire connection MUST be inverted to make sure outputs keep in phase.

#### Example:

CH1 and CH2 are configured to SE output, CH6 is Bass channel.

Set [D31:D24] to 0x01 to inverter CH1 output. CH1 and CH2 are now 180degree reversed. CH1 negative and positive speaker wires must be exchanged.

### 0x20, INPUT MULTIPLEXER REGISTER

Input Signal Routing

| D23 | D22 | D21 | D20 | D19              | D18 | D17 | D16 | FUNCTION                         |

|-----|-----|-----|-----|------------------|-----|-----|-----|----------------------------------|

| 0   | -   | -   | -   | -                | -   | -   | -   | Channel-1 AD mode                |

| 1   | —   | -   | -   | -                | —   | —   | -   | Channel-1 BD mode <sup>(2)</sup> |

| -   | 0   | 0   | 0   | -                | _   | —   | -   | SDIN1-L to channel 1 (2)         |

| -   | 0   | 0   | 1   | -                | -   | -   | T   | SDIN1-R to channel 1             |

| -   | 0   | 1   | 0   | —                | —   | _   | _   | SDIN2-L to channel 1             |

| _   | 0   | 1   | 1   | -                | —   | —   | I   | SDIN2-R to channel 1             |

| -   | 1   | 0   | 0   | -                | -   | -   | -   | Reserved                         |

| -   | 1   | 0   | 1   | -                | -   | -   | -   | Reserved                         |

| -   | 1   | 1   | 0   | _<br><sup></sup> |     |     |     | Ground (0) to channel 1          |

#### [D23:D00] Input Signal Routing Configuration

#### For CH1, CH2, CH6

These bits are used to set which I2S input data is connected to which internal channel, and also switching mode selection, AD or BD mode.

For Single-ended channel, AD mode MUST be selected.

For BTL or PBTL channel, AD or BD mode both works.

### 0x20, INPUT MULTIPLEXER REGISTER

BTL Configuration

|               | Table 19. Input Multiplexer Register (0x20) (continued) |     |                        |               |               |    |    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |

|---------------|---------------------------------------------------------|-----|------------------------|---------------|---------------|----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| D15           | D14                                                     | D13 | D12                    | D11           | D10           | D9 | D8 | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 0             | 0 <b>—</b> 1                                            | -   | -                      | —             | -             | -  | -  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| 1 <del></del> | 0                                                       | 0   | 0                      | -             | -             | -  | -  | SDIN1-L to channel 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|               | 0                                                       | 0   | 1                      | -             | -             | -  | -  | SDIN1-R to channel 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| -             | 0                                                       | 1   | 0                      | —             | -             | -  | I  | SDIN2-L to channel 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| -             | 0                                                       | 1   | 1                      | -             | -             | -  | -  | SDIN2-R to channel 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

|               | 1                                                       | 0   | 0                      | 122           |               |    |    | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| —             | 1                                                       | 0   | 1                      | -             | _             | _  | -  | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| -             | 1                                                       | 1   | 0                      | -             | -             | -  | Е  | Ground (0) to channel 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| —             | 1                                                       | 1   | 1                      | -             | -             | -  | Н  | Ch1 (BTL-) to channel 3—BTL pair for channel 1 (3)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|               | AL AND AL                                               |     | and a start of the set | A Contraction | iteration and |    |    | Fridded (3) and the second sec |  |

[D23:D00] Input Signal Routing Configuration

#### For CH3, CH4, CH5

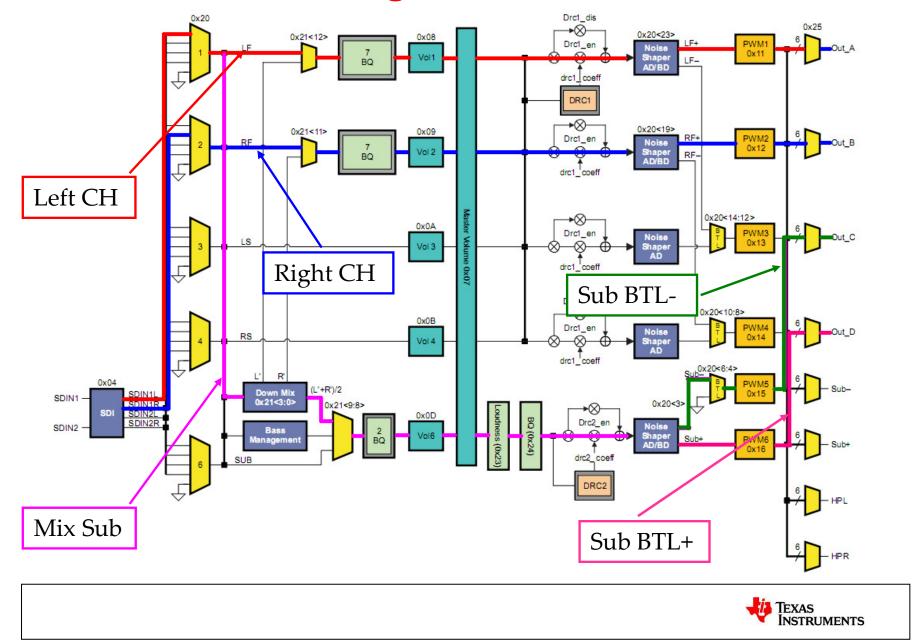

Beside I2S data can be routed to CH3, CH4, CH5. The BTL- signal of CH1, CH2, CH6 are also can be routed to them, to form a BTL output.

### 0x20, INPUT MULTIPLEXER REGISTER

BTL Configuration

BTL Pair Channels Setting:

| Source PWM CHs | BTL Pair PWM CHs |

|----------------|------------------|

| PWM1           | PWM3             |

| PWM2           | PWM4             |

| PWM6           | PWM5             |

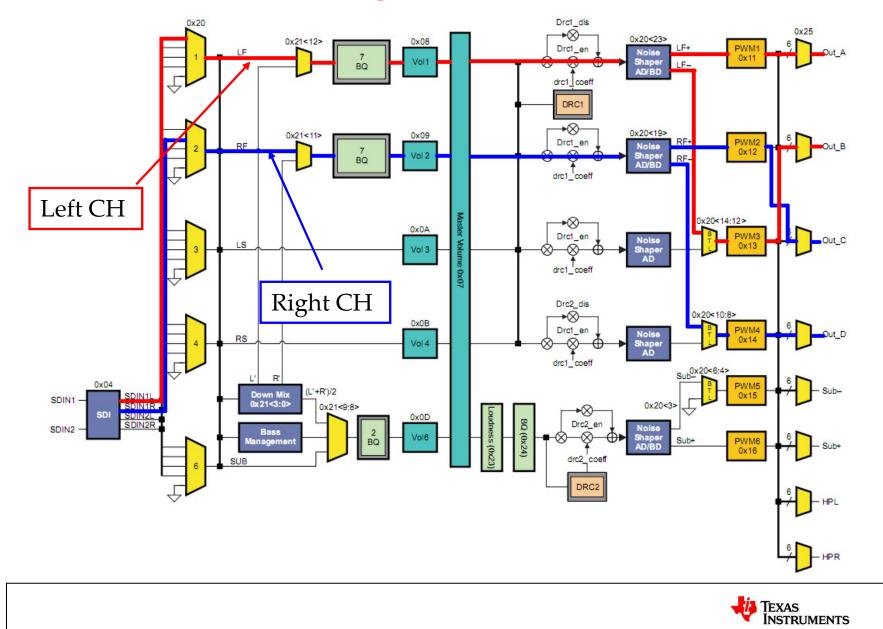

- BTL Channel signal flow are marked in left picture.

- PWM Channels can be routed to OUTA,B,C,D at random.

Example:

• Select option in red box to make PWM1 and PWM3 as BTL Pair.

Ground (0) to channel 3 Ch1 (BTL-) to channel 3—BTL pair for channel 1 <sup>(3)</sup> Reserved <sup>(3)</sup> SDIN1-L to channel 4

#### 0x21, DOWNMIX INPUT MUX REGISTER

What's Downmix

L' and R' are downmix from input CH1 ~ CH4. Below table shows formula for each configure.

Usually, no. 2 and 6 are often used in normal condition.

That's

L'=L=CH1 input

R'=R=CH2 input

| NO. | Bits 3:0 | Definition                                        |

|-----|----------|---------------------------------------------------|

| 1   | X0X0     | $L' = (0.000 \times Ls + 0.000 \times L) / 1.000$ |

| 2   | X0X1     | $L' = (0.000 \times Ls + 1.000 \times L) / 1.000$ |

| 3   | X1X0     | $L' = (1.000 \times Ls + 0.000 \times L) / 1.000$ |

| 4   | X1X1     | $L' = (0.707 \times Ls + 1.000 \times L) / 1.707$ |

| 5   | 0X0X     | $R' = (0.000 \times Rs + 0.000 \times R) / 1.000$ |

| 6   | 0X1X     | $R' = (0.000 \times Rs + 1.000 \times R) / 1.000$ |

| 7   | 1X0X     | $R' = (1.000 \times Rs + 0.000 \times R) / 1.000$ |

| 8   | 1X1X     | $R' = (0.707 \times Rs + 1.000 \times R) / 1.707$ |

### 0x21, DOWNMIX INPUT MUX REGISTER

Downmix Setting

| D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8  | FUNCTION                                          |

|-----|-----|-----|-----|-----|-----|----|-----|---------------------------------------------------|

| 0   | 1   | 0   | -   | -   | -   | -  | -   | Reserved <sup>(1)</sup>                           |

| -   | -   | Ι   | 1   | -   | -   | -  | -   | Enable downmix data L' to channel 1               |

| -   | _   |     | 0   | -   | -   | -  |     | Enable channel 1 data to channel 1 <sup>(1)</sup> |

| -   | -   | -   | -   | 1   | -   | -  | -   | Enable downmix data R' to channel 2               |

| -   | _   | _   |     | 0   | -   | _  | -   | Enable channel 2 data to channel 2 <sup>(1)</sup> |

| -   | _   |     | 1   | -   | 0   | _  | 670 | Reserved                                          |

| -   | -   | -   | -   | -   | -   | 0  | 0   | Enable channel 6 data to channel 6                |

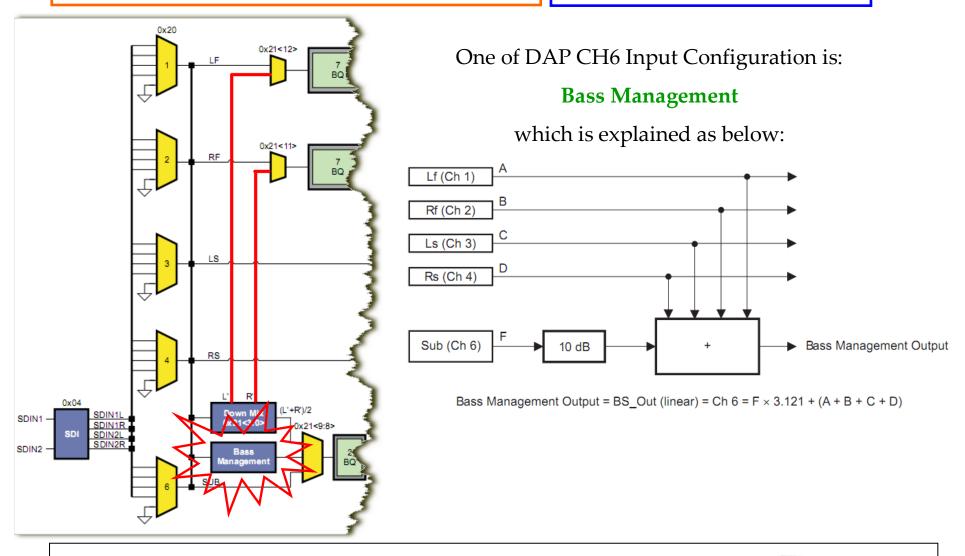

| -   | -   | _   | _   | -   | -   | 0  | 1   | Enable bass management on channel 6               |

| -   | -   | -   | -   | -   | -   | 1  | 0   | Enable (L'+R')/2 downmix data on channel 6 (1)    |

|     |     |     |     |     |     |    |     |                                                   |

#### [D15:D8] Select internal CH1, CH2, CH6 input source

These bits are used to choose input source for internal DAP channel 1, 2 and 6.

- DAP CH1 has two options: L' or Mux CH1

- DAP CH2 has two options: R' or Mux CH2

- DAP CH6 has three options: Mux CH6 or Bass management or (L'+R')/2

#### Usually:

- DAP CH1 = Mux CH1 for left channel

- DAP CH2 = Mux CH2 for right channel

- DAP CH6 = (L' + R')/2 for subwoofer channel. \* Note: Usually used in 2.1CH configuration.

### 0x21, DOWNMIX INPUT MUX REGISTER

Bass Management for CH6

Texas Instruments

# **Critical Registers Setting**

*Register: 0x25*

PWM OUTPUT MUX REGISTER

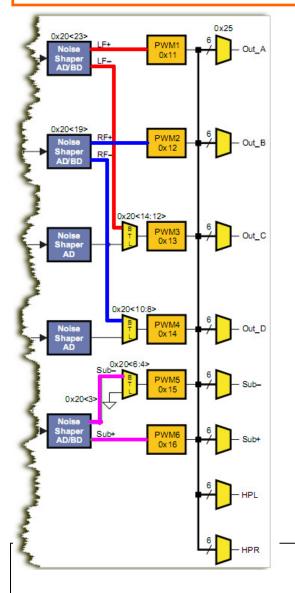

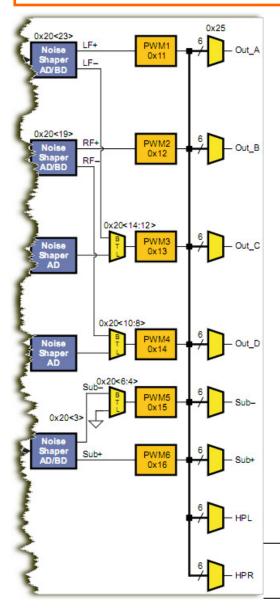

### 0x25, PWM OUTPUT MUX REGISTER

PWM Out Routing

Definition:

Internal Digital PWM: PWM 1 to PWM6

Half – Bridge Output: OUT\_A to OUT\_D

Logic PWM Output : Sub-, Sub+, HPL, HPR

PWM1 to PWM6 can be routed to any one of eight outputs.

Output A to D is Half-Bridge high power output, can drive speaker.

Sub-, Sub+, HPL, HPR are PWM signal outputs which used to drive external power stage or just for line out.

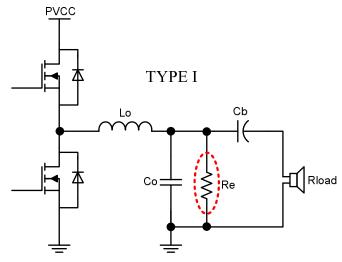

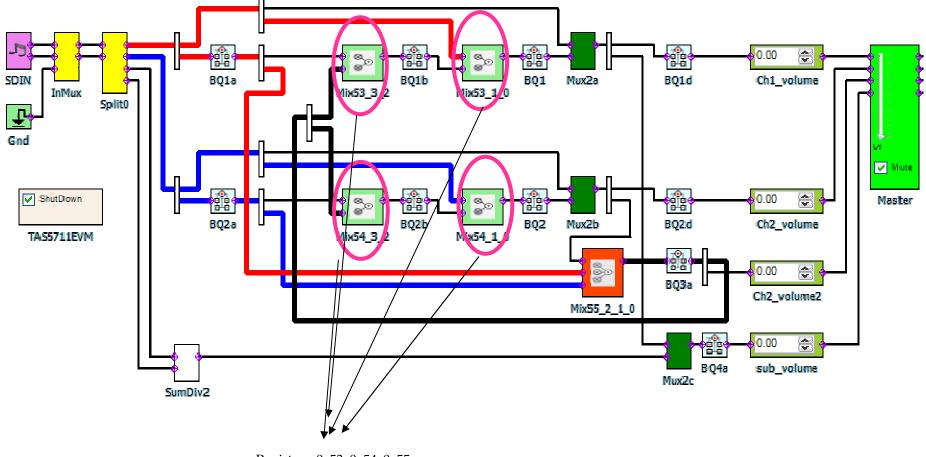

# 2.0 and 2.1 Output Default Configuration Signal Flow

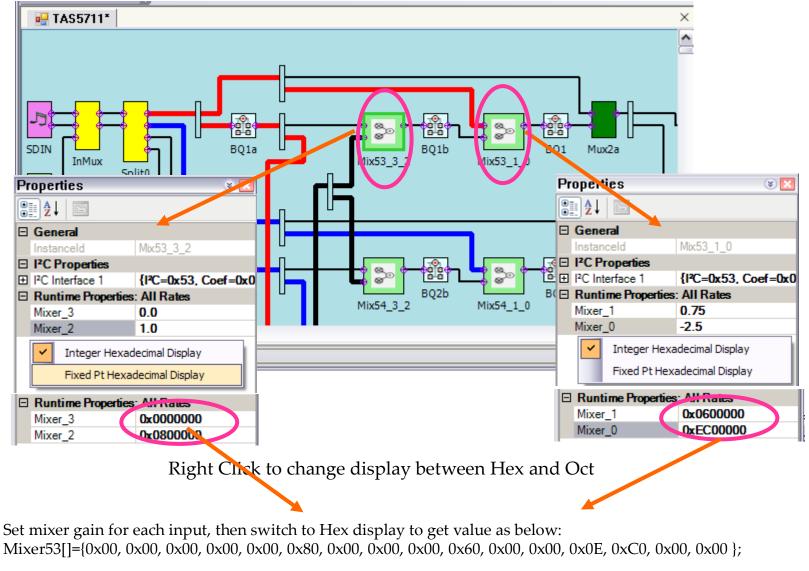

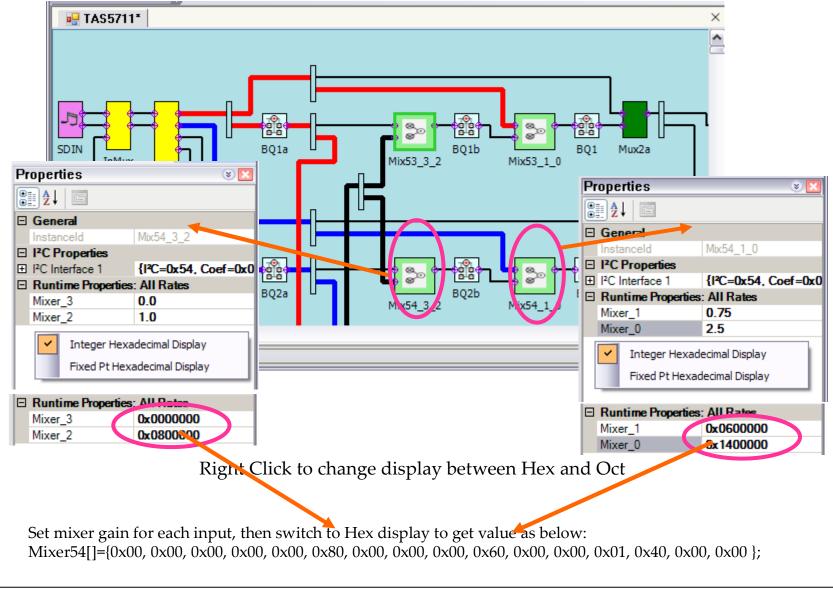

### **Default 2.0 CH Signal Flow Chart**

### **Default 2.1 CH Signal Flow Chart**

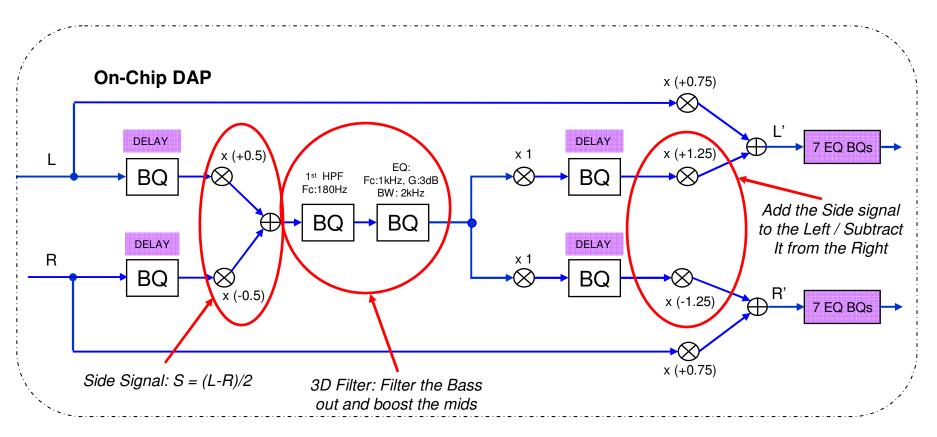

### **Digital Audio Processor Application**

### Signal Flow of TAS57xx --- EQ Channels

TEXAS INSTRUMENTS

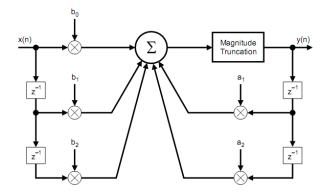

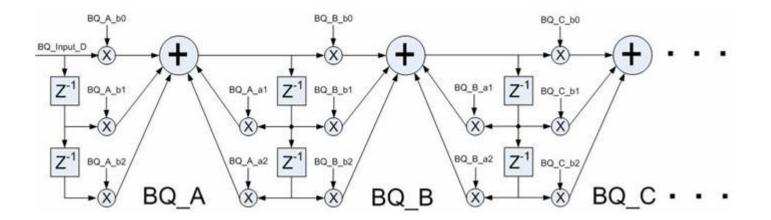

# How EQ works?

Single BQ filter provide Single filter, such as one HPF, LPF....

BQ filter can be linked in series to do several times filtering on input signal.

# **High Pass Filter Collection**

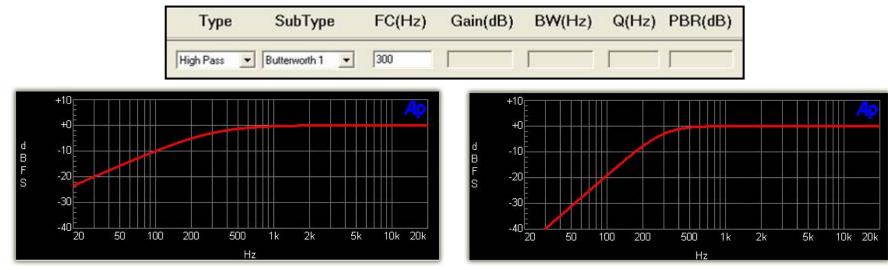

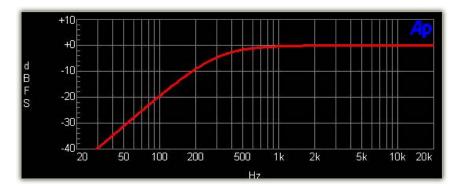

Butterworth HPF (1st order)

Bessel HPF (2nd order)

Butterworth HPF (2nd order)

Linkwitz-Riley HPF (2nd order)

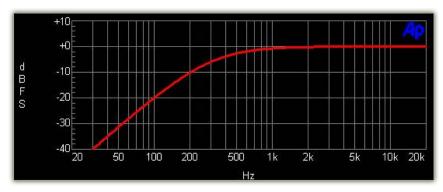

# Variable Q High Pass Filter (2nd order)

The Variable Q High Pass Filter allows the user to specify the Filter Q which is defined as Fc / BW.

#### Properties

- Fc = -3dB Filter cutoff frequency in Hertz.

- Q = Peaking amplitude at Fc.

Variable Q High Pass Filter (2nd order)

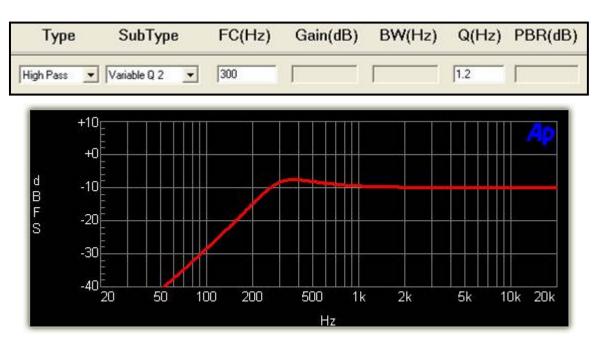

### **Low Pass Filters Collection**

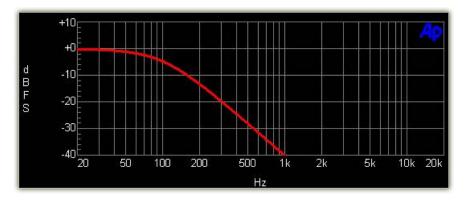

Butterworth LPF (1st order)

### Bessel LPF(2nd order)

### Butterworth LPF(2nd order)

Linkwitz-Riley LPF(2nd order)

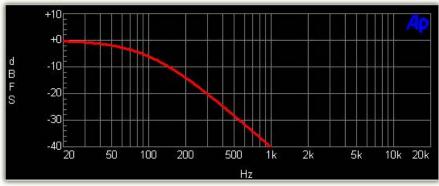

# Variable Q Low Pass Filter (2nd order)

The Variable Q Low Pass Filter allows the user to specify the Filter Q, which is defined as Fc / BW.

#### Properties

- •Fc = -3dB Filter cutoff frequency in Hertz.

- $\bullet Q = Fc / BW$

Variable Q Low Pass Filter (2nd order)

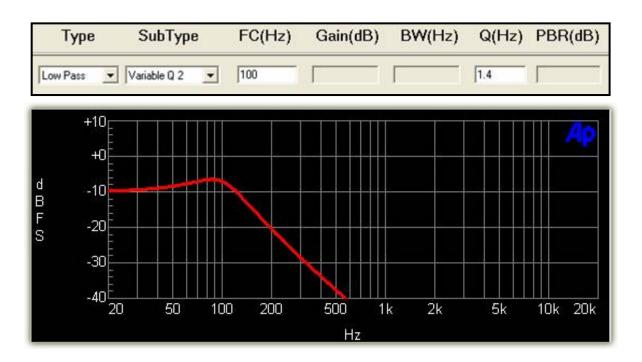

# **EQ** Filters

One of the most common 2nd-order IIR filters is the bell-shaped parametric equalization (EQ) filter. This powerful filter is specified by Fc, Gain, and BW. Two examples are shown: one with a -10 dB cut and one with a +10 dB boost.

#### Properties

Fc = -3dB Filter cutoff frequency in Hertz. Gain = Filter gain in dB BW = Filter bandwidth

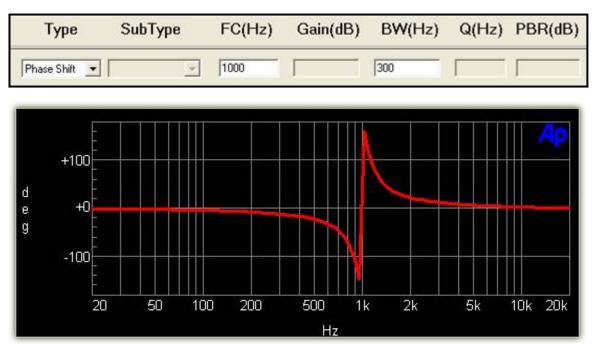

## **Phase Shift**

The Phase Shift Filter allows you to produce a phase shift in the audio, as can be seen in the example. Note that the gain plot for this filter is the same as an All Pass filter. That is, it produces a flat response throughout the audio band.

Properties

- Fc = Frequency of Maximum Phase deviation (Hertz).

- BW = Specifies the slope of the phase deviation

Note: This is Phase vs Frequency Curve

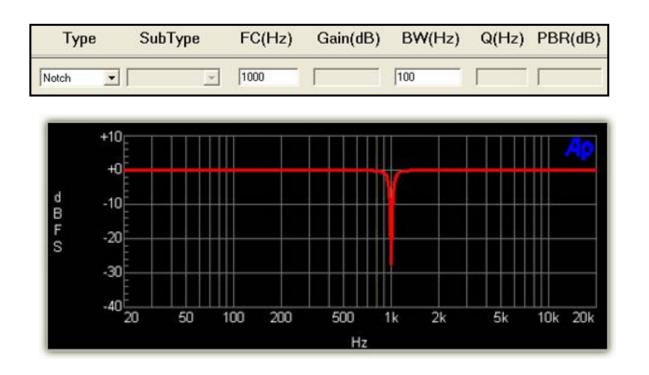

## **Notch Filter**

The Notch Filter is also known as a band reject filter. This filter produces a deep cut at the center frequency (Fc).

#### Properties

- Fc = Notch center frequency in Hertz.

- BW = Bandwidth of notch

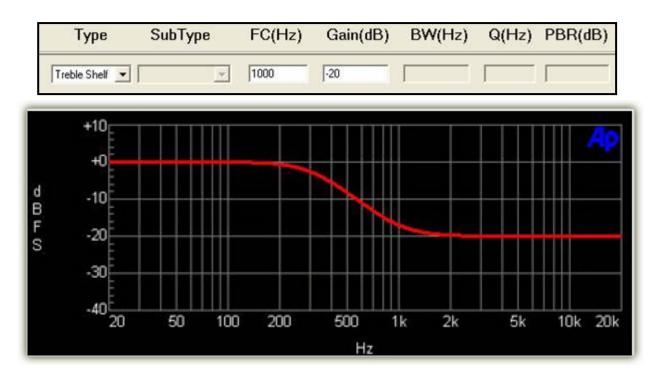

#### **Treble Shelf Filter**

The Treble Shelf Filter is shown below. In this example, the treble is cut by -20 dB at -3 dB point from Fc = 1,000 Hz.

#### Properties

- Fc = Notch center frequency in Hertz.

- Gain (dB) = Filter Gain in DB

Note:

Treble and Bass Shelf filter also can do positive gain shelf, but it recommend to use negative gain shelf to prevent digital overflow.

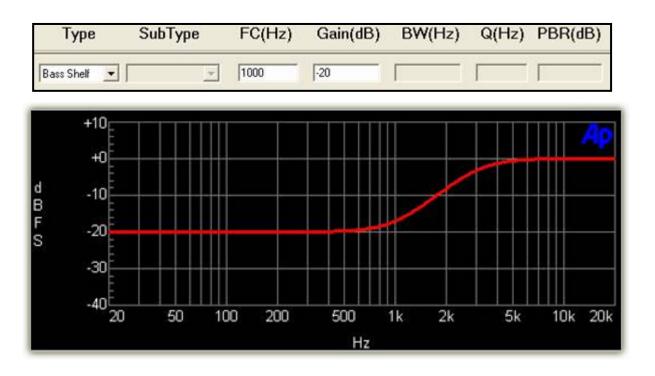

## **Bass Shelf Filter**

The Bass Shelf Filter is shown below. In this example, the bass is cut by -20 dB at -3 dB point from Fc = 1,000 Hz.

#### Properties

Fc = Notch center frequency in Hertz.Gain (dB)

Note:

Treble and Bass Shelf filter also can do positive gain shelf, but it recommend to use negative gain shelf to prevent digital overflow.

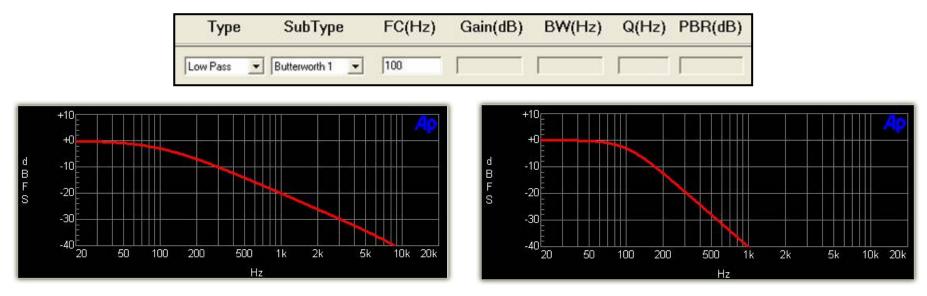

### **EQ Design Example**

Design Spec:

- 2.0 Channel Output, following EQ applied to both L/R channel

- Cut off audio signal below 35Hz by using two band Butterworth 2 filter

- Boost 5dB at 80Hz, band width is 100Hz

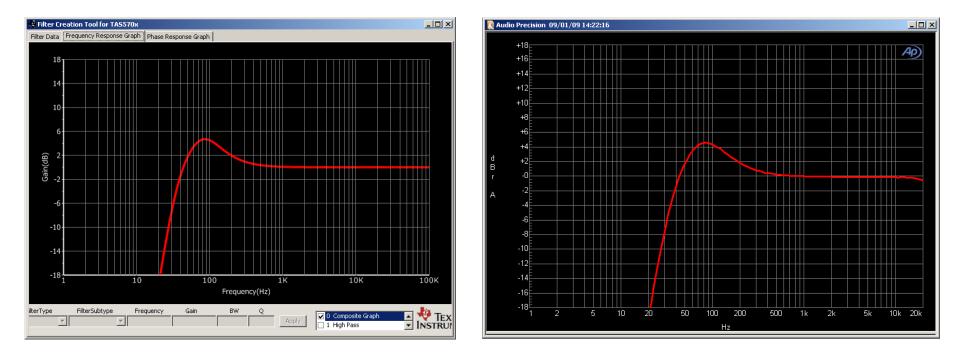

Curve in GDE

# EQ Design Example

Step 1:

Generate EQ coefficient In GDE;

BQ1 is for Left channel, BQ2 is for Right channel.

Select BQ1 and BQ2 to modify EQ parameters.

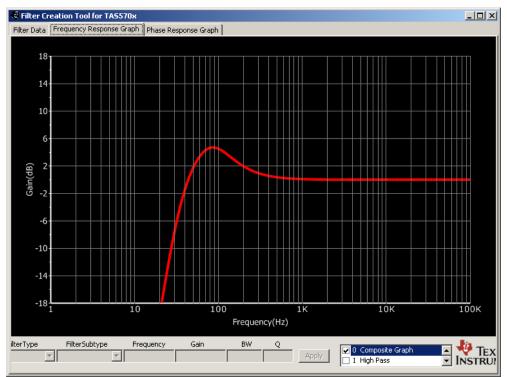

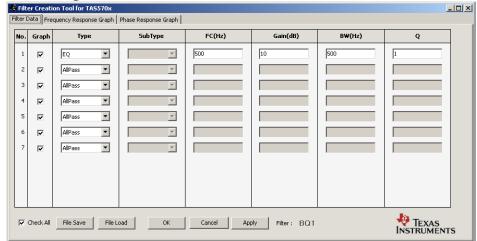

# EQ Design Example ---- Setting Guide

- 1. Add **Two High Pass filters** for bq1 and bq2, cut off frequency is set to 35Hz.

- 2. Add EQ filter for bq3, center frequency is 80Hz, Gain is 5dB, Band width is 100Hz.

- 3. Final table should looks like following picture:

|                                                            | Filter Creation Tool for TA5570x         Filter Data         Frequency Response Graph         Phase Response Graph |                       |                      |        |          |        |       |  |  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|--------|----------|--------|-------|--|--|

| Filter I                                                   | Data Fre                                                                                                           | quency Response Graph | Phase Response Graph |        |          |        |       |  |  |

| No.                                                        | Graph                                                                                                              | Туре                  | SubType              | FC(Hz) | Gain(dB) | B₩(Hz) | Q     |  |  |

| 1                                                          | N                                                                                                                  | High Pass 💌           | Butterworth 2 💌      | 35     |          |        | 0.707 |  |  |

| 2                                                          |                                                                                                                    | High Pass 💌           | Butterworth 2 💌      | 35     |          |        | 0.707 |  |  |

| 3                                                          |                                                                                                                    | EQ                    | <b>*</b>             | 80     | 5        | 100    | 0.8   |  |  |

| 4                                                          |                                                                                                                    | AllPass               | <b>v</b>             |        |          |        |       |  |  |

| 5                                                          |                                                                                                                    | AllPass 💌             | <b>v</b>             |        |          |        |       |  |  |

| 6                                                          |                                                                                                                    | AllPass 💌             | V                    |        |          |        |       |  |  |

| 7                                                          |                                                                                                                    | AllPass 💌             | <b>_</b>             |        |          |        |       |  |  |

|                                                            |                                                                                                                    |                       |                      |        |          |        |       |  |  |

|                                                            |                                                                                                                    |                       |                      |        |          |        |       |  |  |

|                                                            |                                                                                                                    |                       |                      |        |          |        |       |  |  |

| Check All File Save File Load OK Cancel Apply Filter : BQ2 |                                                                                                                    |                       |                      |        |          |        |       |  |  |

- 4. Click OK or Apply to send coefficient to devices for BQ1.

- 5. Do the same thing for BQ2, make sure Left and Right channels EQ are the same.

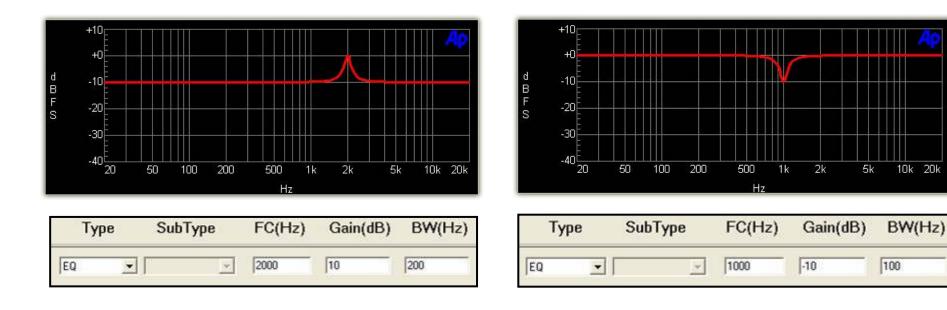

# **EQ Design Example ---- Test Results**

Test Results are shown blow:

GDE Generated Curve

AP Test Curve

# EQ Design Example ---- Register Map

Example EQ is programmed to device registers, here is register map for reference:

| 1.cfg - Notepad File Edit Format View                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | w Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                          |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| <pre>! I2C Configurat<br/>X1B 00<br/>X06 00<br/>X19 30<br/>X21 00 00 42<br/>X20 00 89 77<br/>X11 B8<br/>X12 60<br/>X13 A0<br/>X14 48<br/>X15 F4<br/>X16 0C<br/>X04 05<br/>X25 00 02 13<br/>! Biquads<br/>X50 00 00 00<br/>X29 00 7F 96<br/>X2A 00 7F 96<br/>X2D 00 80 00<br/>X2P 00 80 00<br/>X2P 00 80 00<br/>X2P 00 80 00<br/>X2P 00 80 00<br/>X2F 00 80 00<br/>X2F 00 80 00<br/>X31 00 7F 96<br/>X31 00 7F 96<br/>X32 00 80 00<br/>X35 00 80 00<br/>X35 00 80 00<br/>X36 00 80 00<br/>X37 00 80 00<br/>X37 00 80 00<br/>X38 00 80 00<br/>X38 00 80 00<br/>X38 00 80 00<br/>X38 00 7F FF<br/>X3A 00 7F FF<br/>X3B 00 7F FF</pre> | W         Thep           tion file for TAS570;           03           7A           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00           00 | 00 00 00 00 00 00 00<br>00 7F 96 00 00 FF 2<br>00 7F 96 00 00 FF 2<br>00 7D 80 04 00 FE 5<br>00 00 00 00 00 00 00<br>00 00 00 00 00 00 | B       A8       OF       80       D3       A8         B       A8       OF       80       D3       A8         2       47       OF       81       AA       27         00       00       00       00       00       00       00         00       00       00       00       00       00       00         00       00       00       00       00       00       00         00       00       00       00       00       00       00         00       00       00       00       00       00       00         00       00       00       00       00       00       00         00       00       00       00       00       00       00         00       00       00       00       00       00       00         00       00       00       00       00       00       00         00       00       00       00       00       00       00         00       00       00       00       00       00       00         00       00       00 <th>CH1-bq1-HighPass<br/>CH1-bq2-HighPass<br/>CH1-bq3-EQ<br/>CH2-bq1-HighPass<br/>CH2-bq2-HighPass<br/>CH2-bq3-EQ</th> | CH1-bq1-HighPass<br>CH1-bq2-HighPass<br>CH1-bq3-EQ<br>CH2-bq1-HighPass<br>CH2-bq2-HighPass<br>CH2-bq3-EQ |

TEXAS INSTRUMENTS

#### **Digital Audio Processor Application**

### **Fundamental of Dynamic Range Control**

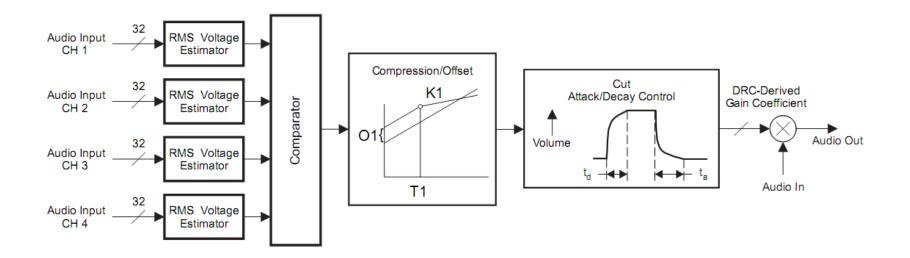

Dynamic Range Control (DRC) is an automatic signal amplitude control mechanism that can be used to contain or control the dynamic range of an audio signal to within specified limits.

DRC Signal Chart for TAS5706 (One – band DRC)

### **Fundamental of Dynamic Range Control**

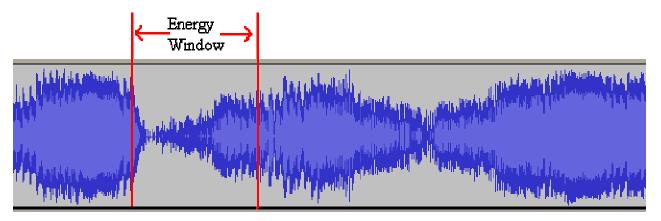

**AAV estimator**—This DRC element derives an estimate of the average absolute value (AAV) of the audio data stream into the DRC. A time constant, *t\_energy*, is used to control the effective time window over which the AAV estimate is made.

**Compression coefficient computation**—This DRC element converts the output of the AAV estimator to a logarithmic number, determines the region where the input resides, and then computes and outputs the appropriate gain coefficient to the attack/decay element. Parameters K define the slopes of the gain curve for these three regions. T specify the boundaries of the regions, in terms of input level. O specify offsets of the gain curve relative to a 1:1 transfer function at the thresholds.

Attack/decay control—This DRC element controls the transition time of changes in the coefficient computed in the compression/expansion coefficient computation element. User-specified parameters  $t_a$  and  $t_d$  are used to set the attack and decay time constants used in the gain adjustment.

### **DRC** Timing Parameter --- Energy Time

Energy Time: DRC element derives an estimate of the average absolute value (AAV) of the audio data stream into the DRC. A time constant, t\_energy, is used to control the effective time window over which the AAV estimate is made.

A reasonable minimum value for the energy time constant that would be used where **fast response is desired** is 10 times the period of the **lowest frequency** that is passed through the system.

For example if the lowest frequency 40 Hz, the period of this is 25 ms.

The minimum energy time constant should be (10 \* 25 ms = 250 ms).

Less than this time constant will produce a DRC control signal with significant ripple in it. We want to avoid ripple in the control signal because it produces modulation distortion in the output.

- 1. Larger Energy time will result slow action of DRC.

- 2. Smaller Energy time will make DRC act too often.

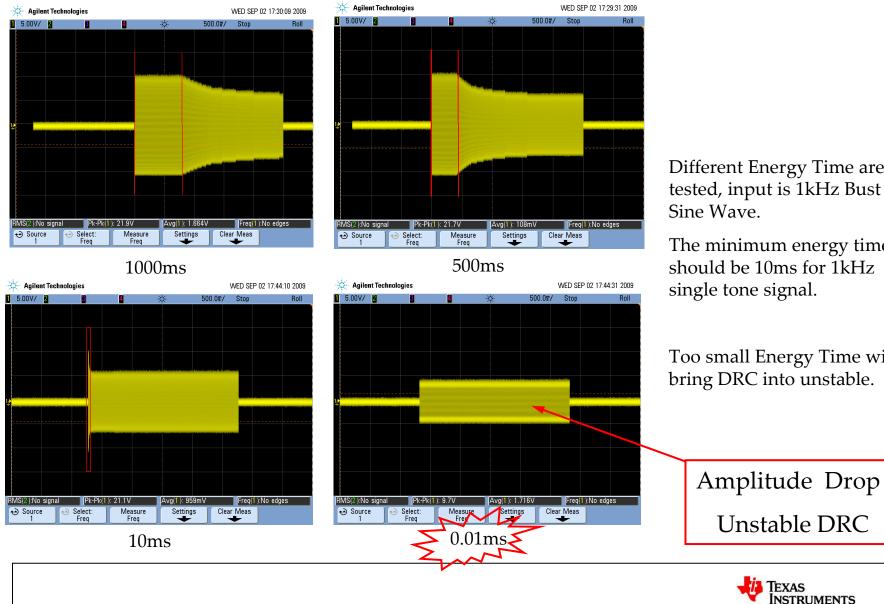

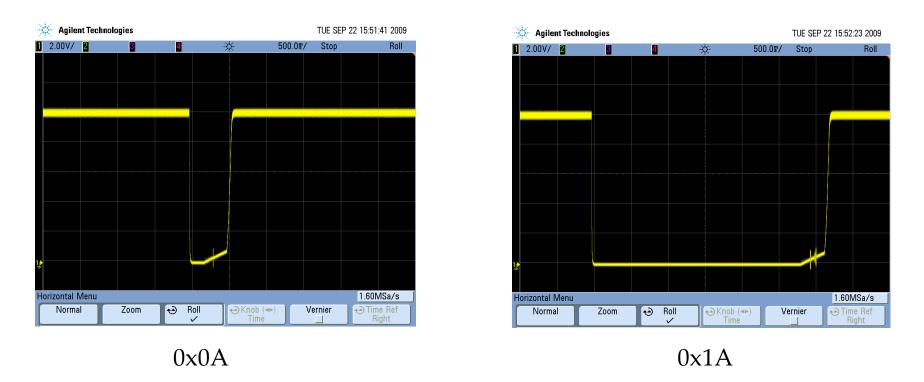

## **Energy Time Timing Example**

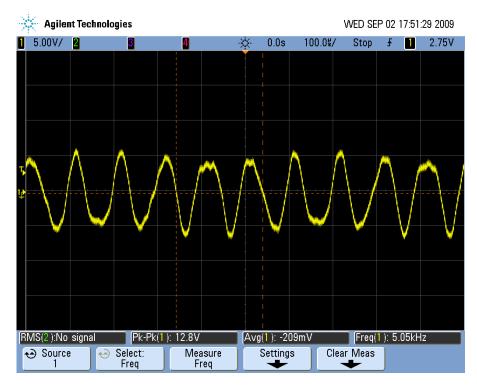

Different Energy Time are tested, input is 1kHz Bust

The minimum energy time should be 10ms for 1kHz single tone signal.

Too small Energy Time will bring DRC into unstable.

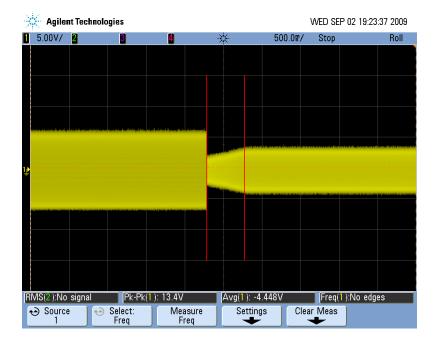

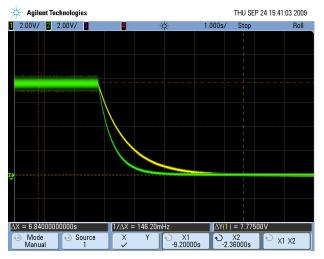

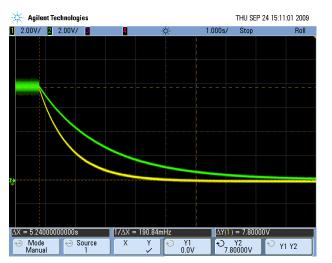

# **Error Energy Timing**

Minimum value for the energy time constant is: 10 times the period of the **lowest frequency** Otherwise, signal will have distortion after applied DRC.

Distortion Wave after DRC

Input Sine 10kHz, Energy time 0.1ms.

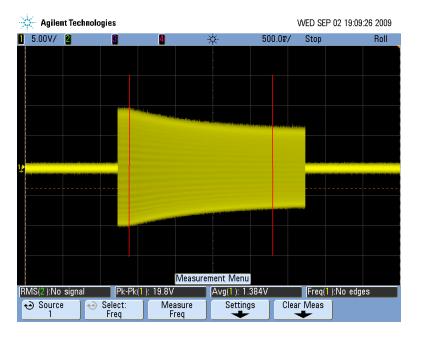

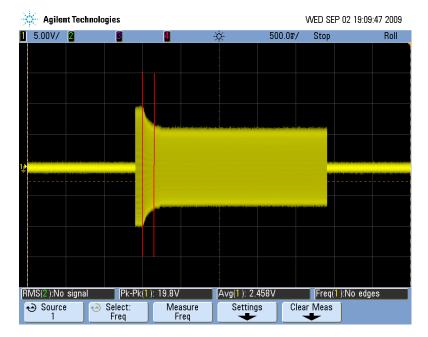

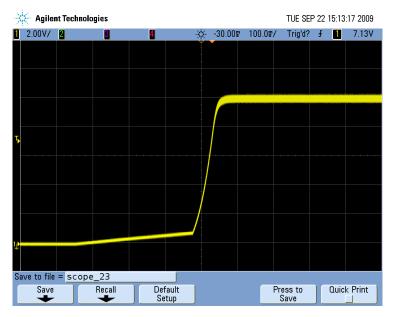

# **Attack Time Example**

Attack time is 1000ms

Attack time is 10ms

- Attack is defined as the application time of compression

- Typically set the minimum Attack time constant to between 3 and 5 times the period of the lowest frequency signal

- Longer attack time make sound volume change slowly

- Shorter attack time increase fast response when sound level changes

- Too short attack time will reduce Bass (Low frequency) content performance

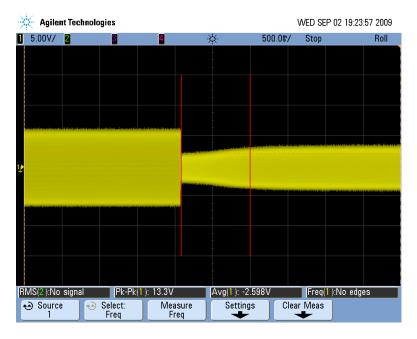

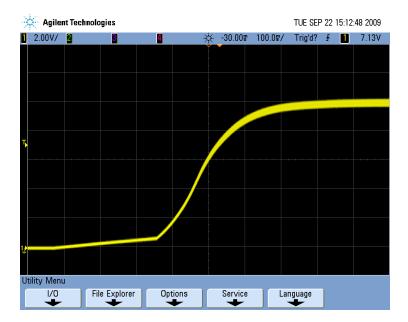

# **Decay Time Example**

Decay time is 500ms

Decay time is 10ms

- Decay is defined as the release time of compression.

- Typically set the minimum Decay time constant to between 10 and 20 times the period of the lowest signal.

- Longer Decay time make sound volume change slowly.

- Shorter Decay time increase response speed when input sound level changes.

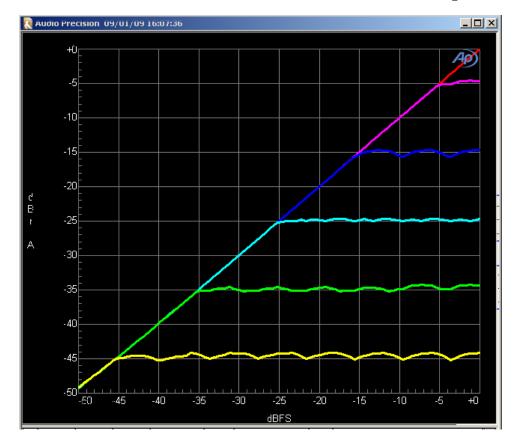

## **Use DRC as Power Limiter**

DRC functions are mostly used as Power Limiter, in this kind of application, compression rate is set to more than 30 to reduce Gain to almost zero when input exceeds threshold.

Output vs Input Vol = -10, input = 0db, 20/30/40/50db threshold

## **Time Constant Time Example**

If the Lowest Frequency is Fs, the period is Ts. Suitable timing for DRC act as **Power Limiter** are list as blow:

| Items       | x Ts       | Timing<br>For 40Hz |

|-------------|------------|--------------------|

| Energy time | 10x ~ 20x  | 250ms ~ 500ms      |

| Attack time | 3x ~ 5x    | 75ms ~ 125ms       |

| Decay time  | 10x ~ 100x | 250ms ~ 2500ms     |

Note : Customer may need to optimize above timing according to subjective listening test. Different music type, such as POP, Classic etc.. require different timing.

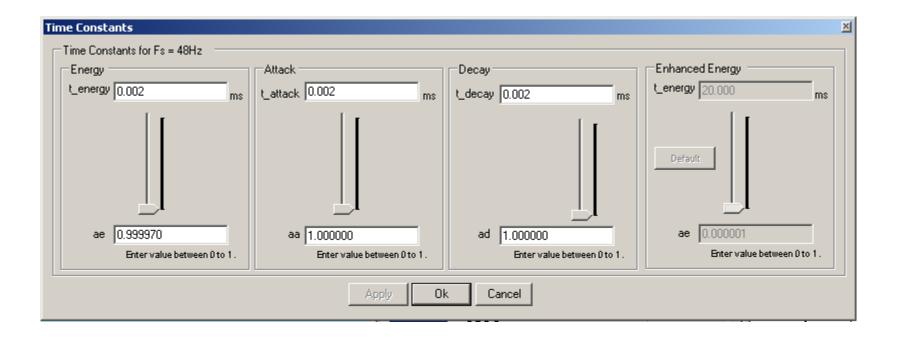

#### **DRC Panel of TAS57XX GDE**

GDE provide a panel for user to program special timing for DRC

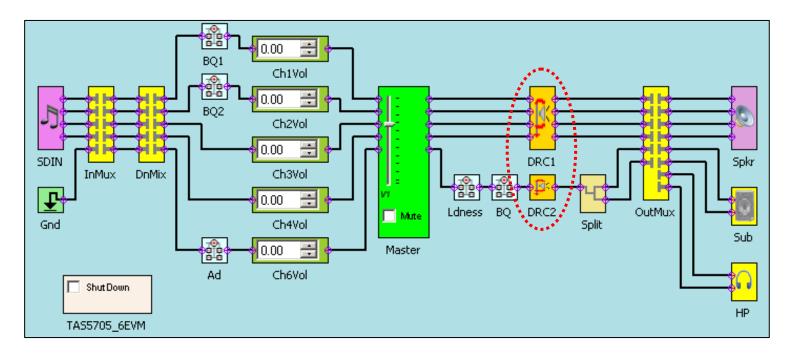

## **DRC Setting Example**

Step 1. Generate coefficient in DRC panel:

- DRC1 is for CH1 CH2 CH3 CH4 -----in charge of Left and Right channels DRC function

- DRC2 is for CH5 CH6 ------used only in 2.1 channels output. In charge of woofer DRC function

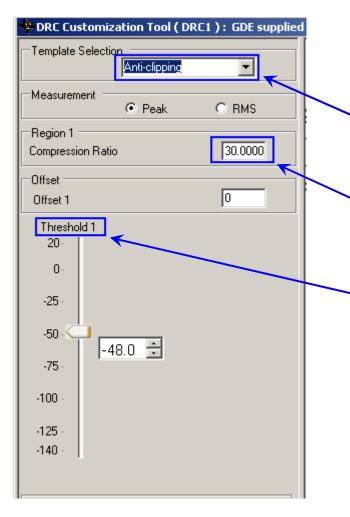

## **DRC Setting Panel**

*Note: This setting example is suitable for Power Limiter function, named Anti-Clipping in DRC Panel.*

- 1. Select "Anti-clipping" Template, this helps to set correct time constants for "Attach time" "Decay time" "Energy time" automatically.

- 2. Compression Ratio has been set to 30 automatically. That's enough for Power limiting.

- 3. The only thing customer need to adjust is "Threshold"

value. It depends on how much power after limitaion they want.

Note: Please select suitable value for "Threshold" according to experiment results. That's a "Try and Error" method.

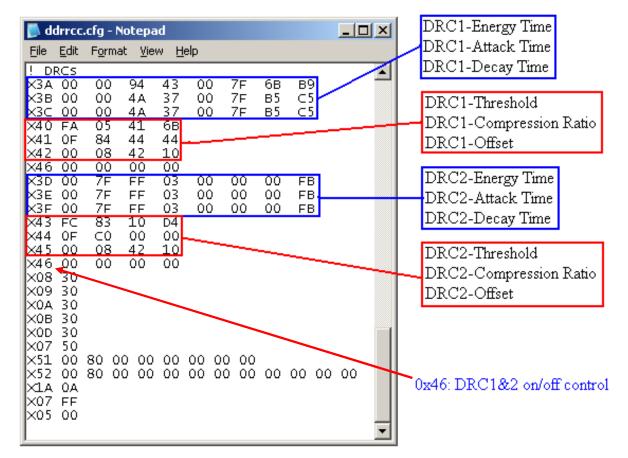

## **DRC Register Map**

- 1. Program DRC1 and DRC2 parameters at initiation.

- 2. 0x46 can be used to control DRC on/off

- 3. DRC adjustment is a "try and error" process, please try different Threshold value (0x40 and 0x43) to find what you want.

#### **Digital Audio Processor Application**

#### ----- Auto Bank for EQ and DRC

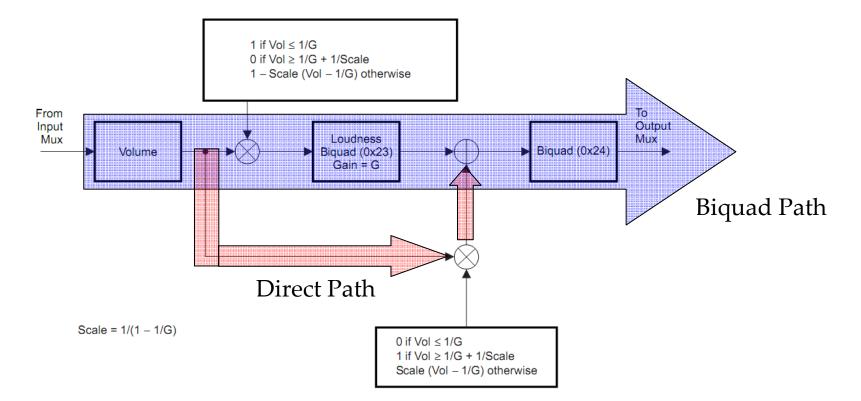

## **EQ Auto Bank Switching**

Bank switching allows the TAS57xx to detect automatically a change in the input sample rate and switch to the appropriate bank without any MCU intervention.

- TAS57xx has three banks to handle differential sampling frequency.

- For device ID is 0x28/0x2A parts: TAS5705/6/16:

- Bank1 is for 32kHz

- Bank2 is for 44.1/48kHz

- Bank3 is for 96Hz and above

- For device ID is 0x68/0x70 parts: TAS5707/8/9/10/11:

- More flexible setting provided to handle different sample-rate.

- 0x50 can set which bank is for which sampling rate

- EQ can be turn on/off by one bit change

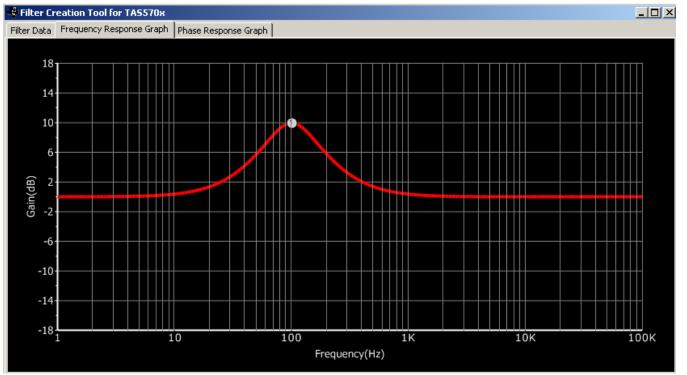

# Why we need EQ Auto Bank Switching?

#### Example Without Auto bank:

- 1. Adding one EQ at 500Hz, 10dB boost, width is 200Hz.

- 2. Calculate 48kHz coefficient.

| Ξ | Configuration |          |

|---|---------------|----------|

|   | CurrentDevice | TAS5706B |

|   | CurrentRate   | Rate48   |

|   | CoefBanking   | Disabled |

|   | Use441K       | Disabled |

|   | Int21Mode     | Off      |

#### Set GDE Sample-Rate to Rate48

| Filter Creation Tool for TA5570x |                                                                                    |           |          |        |          |        |   |  |  |

|----------------------------------|------------------------------------------------------------------------------------|-----------|----------|--------|----------|--------|---|--|--|

| No.                              | Graph                                                                              | Туре      | SubType  | FC(Hz) | Gain(dB) | BW(Hz) | Q |  |  |

| 1                                | শ                                                                                  | EQ        | Y        | 500    | 10       | 500    | 1 |  |  |

| 2                                | •                                                                                  | AllPass   | <b>*</b> |        |          |        |   |  |  |

| 3                                | <b>N</b>                                                                           | AllPass 💌 | <b>V</b> |        |          |        |   |  |  |

| 4                                | N                                                                                  | AllPass   | V        |        |          |        |   |  |  |

| 5                                | •                                                                                  | AllPass 💌 | V        |        |          |        |   |  |  |

| 6                                | •                                                                                  | AllPass 💌 | V        |        |          |        |   |  |  |

| 7                                | N                                                                                  | AllPass 💌 | V        |        |          |        |   |  |  |

|                                  |                                                                                    |           |          |        |          |        |   |  |  |

|                                  |                                                                                    |           |          |        |          |        |   |  |  |

|                                  |                                                                                    |           |          |        |          |        |   |  |  |

| <b>N</b>                         | Check All     File Save     File Load     OK     Cancel     Apply     Filter : BQ1 |           |          |        |          |        |   |  |  |

Set EQ

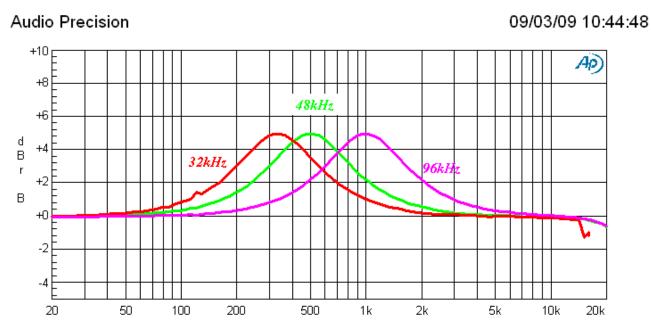

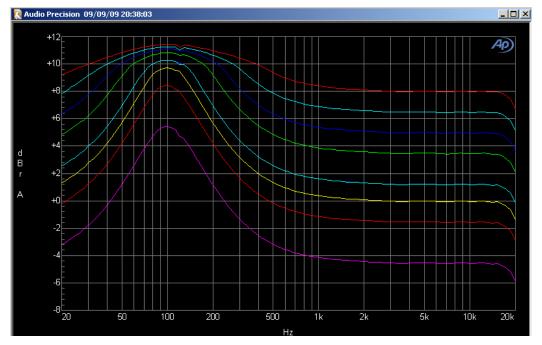

## **EQ Curve Without Auto Bank Switching**

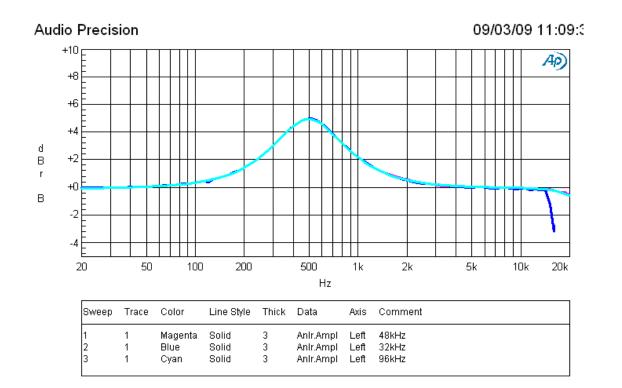

Frequency Response Curve without Auto Bank Switching

Without Bank switching, when input sampling frequency change to 32kHz or 96kHz, EQ curve shift.

So we need Auto-Bank Switching to make sure correct EQ curve under different sample rate.

## **Enable Auto Bank Switching**

Follow these steps to turn on Auto Bank Switching Function

**Step1**: Calculate all coefficient under different sampling frequency.

Enable **Coefbank** in GDE, this enabled GDE to store all coefficients for different sample frequency in Configure File.

| 🗆 Configuration |          |

|-----------------|----------|

| CurrentDevice   | TAS5706B |

| CurrentRate     | Rate48   |

| CoefBanking     | Enabled  |

| Use441K         | Disabled |

| Int21Mode       | Off      |

Step: Go to EQ Panel, regenerate EQ coefficient.

Regenerate EQ in EQ panel

#### EQ Register Map with Auto Bank Switching

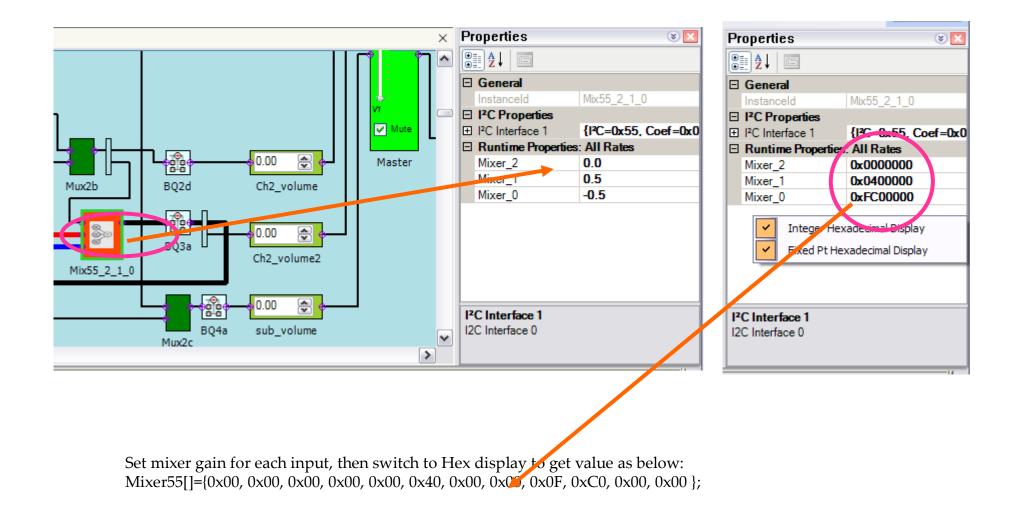

#### Configure file with Auto Bank On