# Four Voltage References, an ADC and MSP430

Tadija Janjic

HPL – Tucson

Michael Ashton

#### **Motivation**

- u Total Solution Concept

- u Application section of datasheets

- u New REF products from TI

- u Greed

- n Product Recognition

- n Increased Revenue

# **Experiment**

- u Verify setup/measurements

- u Evaluate TI REFs with ADS1256

- u Compare different TI REF results

- u Suggest the optimal circuitry

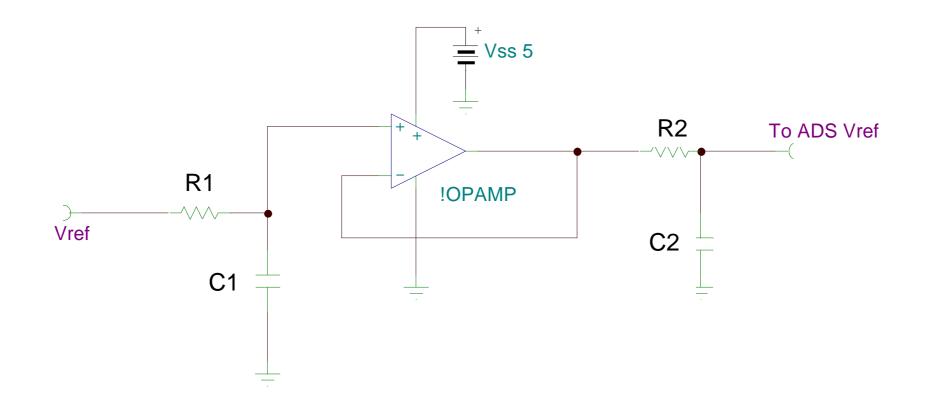

# Basic Setup

ADS1256, PGA=1, Vref=2.5V

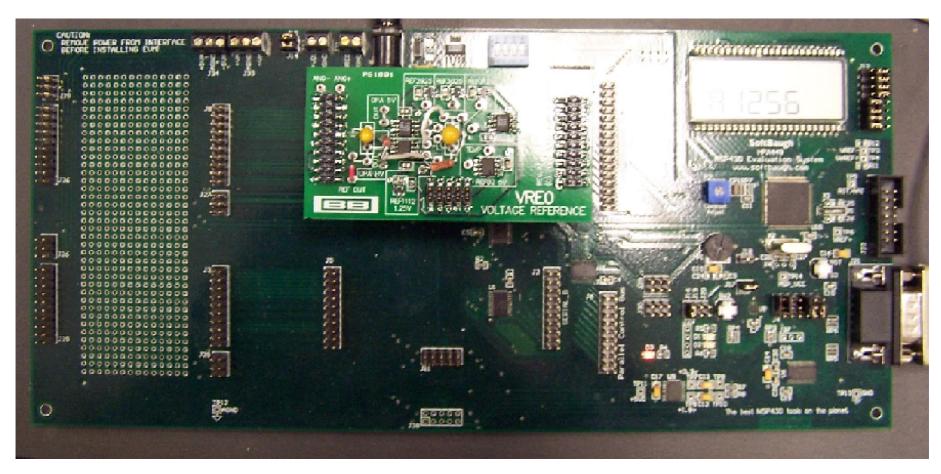

#### **Board**

# Board (side view)

### **Considerations**

- u Low Noise

- u Long term stability

- n *Time*

- n Temperature

# **Experiment Design**

| R1 | C1 | OPA | R2  | C2  | RMS noise free bits |

|----|----|-----|-----|-----|---------------------|

|    |    | 335 | 100 | 10u |                     |

|    |    |     |     |     |                     |

|    |    | 227 | 100 | 10u |                     |

|    |    |     |     |     |                     |

Additional considerations:

Vin amplitude, f<sub>s</sub> (data output rate)

# Confirm the Setup

#### Table 2. Effective Number of Bits (ENOB, rms) with Buffer On

| DATA<br>RATE |      |      |      | PGA  |      |      |      |

|--------------|------|------|------|------|------|------|------|

| (SPS)        | 1    | 2    | 4    | 8    | 16   | 32   | 64   |

| 50           | 23.9 | 23.6 | 23.0 | 22.5 | 21.8 | 21.1 | 20.3 |

| 60           | 23.8 | 23.4 | 22.9 | 22.4 | 21.7 | 21.0 | 20.2 |

| REF  | R1  | C1  | OPA | R2  | C2  | RMSnfb |

|------|-----|-----|-----|-----|-----|--------|

| 1004 | 10k | 47u | 227 | 100 | 10u | 23.8   |

VIn=0V, shorted inputs,

#### Results

| REF   | R1   | C1   | OPA    | R2   | C2   | RMSnfb |

|-------|------|------|--------|------|------|--------|

| 1004  |      |      | OPA335 | 100  | 10u  | 20.7   |

| 1004  | 10k  | 220u | same   | same | same | 22.3   |

| 1004  | 10k  | 47u  | same   | same | same | 22.4   |

| 3025  | same | same | same   | same | same | 20.8   |

| 3125  | same | same | same   | same | same | 20     |

| 1112* | same | same | same   | same | same | 22.1   |

| 1004  | same | same | OPA227 | same | same | 22.4   |

\* OPA in a gain of 2

Vin=2.5V, data output rate = 60Hz,

#### **Conclusions**

- u On ADS1256 one needs external buffer

- n Input impedance 18k

- u Noise-wise OPA227 and OPA335 equal

- n However, we tried at T=25 °C

- u REF1004 and REF1112 similar results

- u REF3xxx family good for lower precision

- u RC (settling time vs. noise) trade off

### **MSP430**

- u Has 12 bit ADC (ADC12)

- u Has Vref (2.5V or 1.5V)

- n 800uA max

- n *100ppm/°C max*

- n 4% initial accuracy

#### •TI REFs:

- •8uA -110 uA max current

- •15 -100ppm/ ° C

- •2.048/2.5/3.0V/3.3V

0.2%

#### Results

| REF             | R1   | C1   | Noise RMS bits |

|-----------------|------|------|----------------|

| Internal (2.5V) |      |      | ~3.1           |

| 1004 – 2.5V     | 100  | 47u  | ~3.0           |

| 3025            | 10k  | 47u  | ~2.7           |

| 3125            | same | same | ~2.7           |

| 1004            | same | same | ~2.7           |

| 3125            | 100  | same | ~3.0           |

| 3025            | same | same | ~3.0           |

| 1112            | same | same | 5.5            |

### Conclusions - Part II

- u External REFs improve performance

- n Lower noise

- n Lower supply current

- u REF1112 can not be used with MSP430

- n VeRef is 1.4V min!!!!!

# Summary

- Built tools for evaluations

- u Got preliminary results

- u Will work on other ADCs and MSP430

- n SARs, Delta-Sigma

- u Will improve datasheets

- u **Support customers** with optimal solution

Thank You

# Amplifier to A/D Interface Study

Or...that short task that will not go away

Bill Klein

Senior Applications

Engineer

Miro Oljaca

<a href="Strategic Marketing: Motor Control">Strategic Marketing: Motor Control</a>

With major contributions from: Tom Hendrick, Tim Green, Rick Downs, Rod Burt, Bob Benjamin, Bernd Rundel, Bruce Trump, Dennis Goeke, Pat Highton

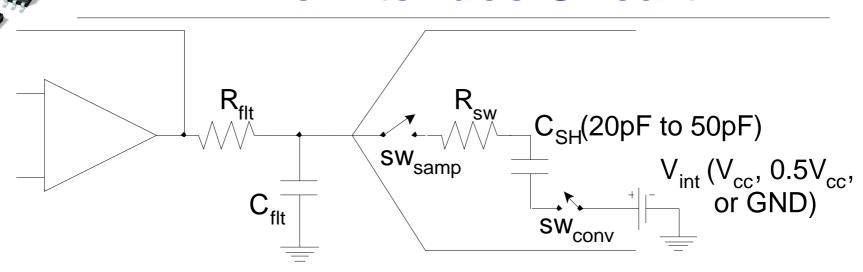

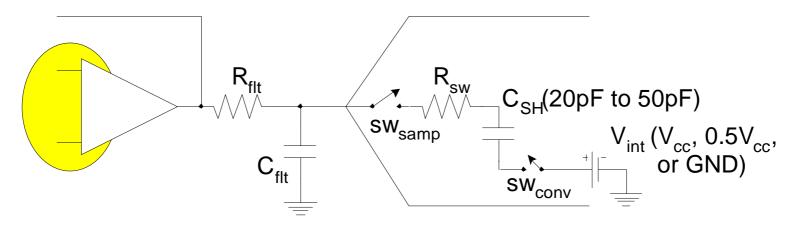

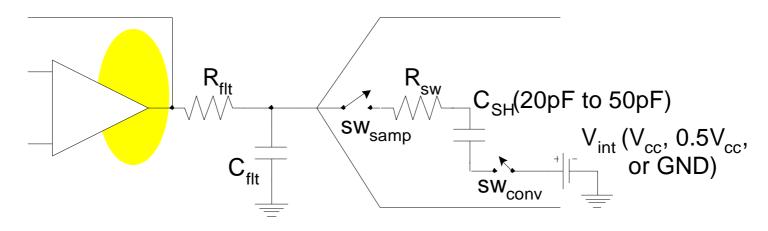

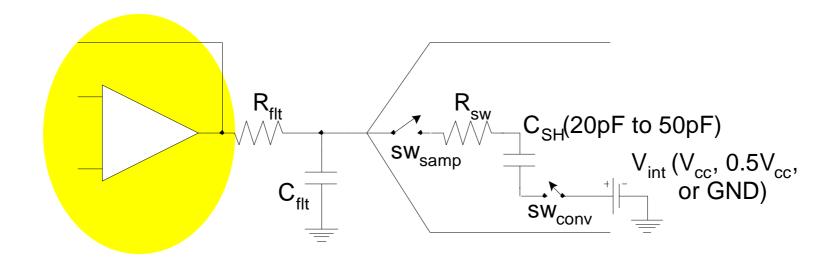

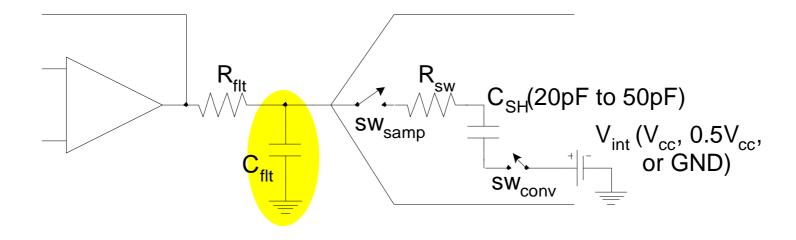

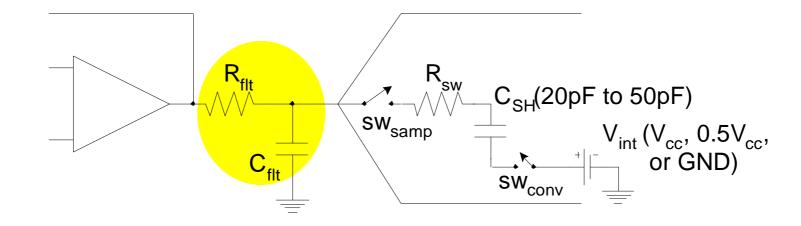

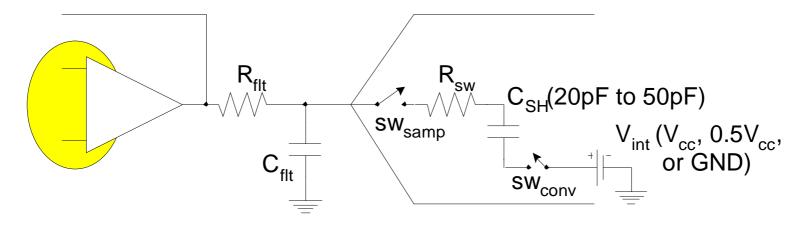

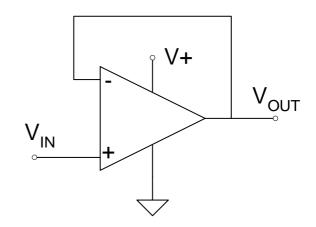

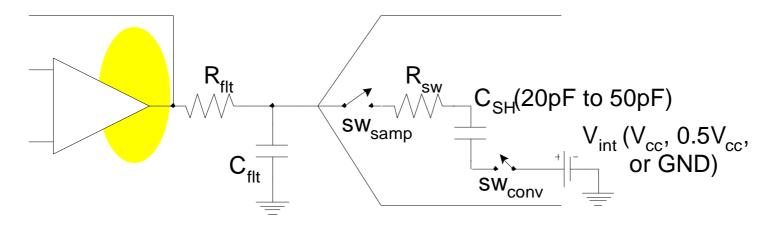

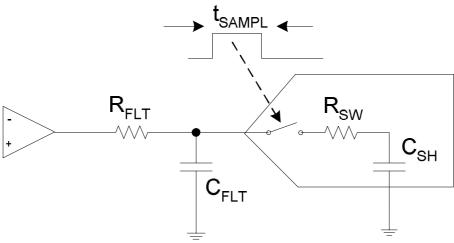

### The Interface Circuit

#### Op Amp

CMV Range, V<sub>OS</sub> vs CMV

RR Out-Swing to the rail

Slew Rate, Signal BW,

Load Transient, Settling Time,

Output Impedance,

#### **Filter**

Charge Bucket

Filtering,

C<sub>load</sub> Isolation,

#### A/D

**Acquisition Time**

**Input Circuit Parameters**

Initial Voltage on C<sub>SH</sub>

### LSB Size

#### u Signal range:

```

n +/-10V is a 20V range

```

w 12 bits: 20V/4,096 = 4.88mV per LSB

w 16 bits: 20V/65,536 = 305µV per LSB

n +5V range

w 12 bits: 5V/4,096 = 1.22mV per LSB

w 16 bits:  $5V/65,536 = 76.2\mu V per LSB$

w 24 bits: 5V/16,777,216 = 298nV per LSB

n +3.3V range

w 12 bits:  $3.3V/4,096 = 806\mu V per LSB$

w 16 bits:  $3.3V/65,536 = 50.4\mu V per LSB$

w 24 bits: 3.3V/16,777,216 = 196nV per LSB

## **Op Amp Input Concerns**

#### See Appendix

Rail-to-Rail Input

## **Output Stage Concerns**

#### See Appendix

Rail-to-Rail Output

# How Fast does that Op Amp Settle

# What Settling Time?

- u Think of a linear voltage regulator, there are TWO Settling Times.

- n Line Transient

- n Load Transient

- u Same applies here.

- u Data sheets report settling time to 0.01% at best.

## **OPA300**

## **OPA340**

## **OPA350**

## Line Transient Becomes

- u Response to change in input signal

- u Includes Slew Rate.

- u Op Amp data sheets MAY address Settling Time to 0.01%

- u But we need 0.0007629% for a 16 bit system

# Required Settling Time

| Number of bits | 0.5LSB     |

|----------------|------------|

| 10             | 0.0488281% |

| 12             | 0.0122070% |

| 14             | 0.0030518% |

| 16             | 0.0007629% |

| 18             | 0.0001907% |

| 20             | 0.0000477% |

| 22             | 0.0000119% |

| 24             | 0.0000030% |

See appendix for calculations

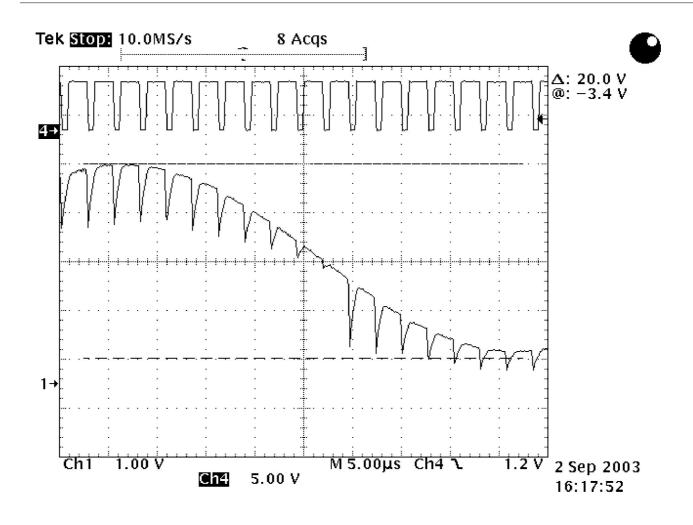

### Load Transient is UNKNOWN

- u We know the load is the input capacitance of the A/D

- u We do NOT know the starting voltage.

- n Possible voltages: GND, Mid-Rail, Random

- n Not given in data sheet

- u The Op Amp data sheet does NOT even mention this settling time.

## SAR A/D < 500kHz

#### u 70% Applications

- n Slow Moving "Real World Process" Signals

- n Fast Acquisition & Conversion Allows More System Time For Processing, Computation, Decision Making

- n Multiplexed, Scanning Systems for Slow Moving Signals

#### u 30% Applications

- n AC Fast Moving Dynamic Signals

- n "Real Time" Processing of Input Signals

# Look at the Charge Transients

# Capacitor Type is Critical

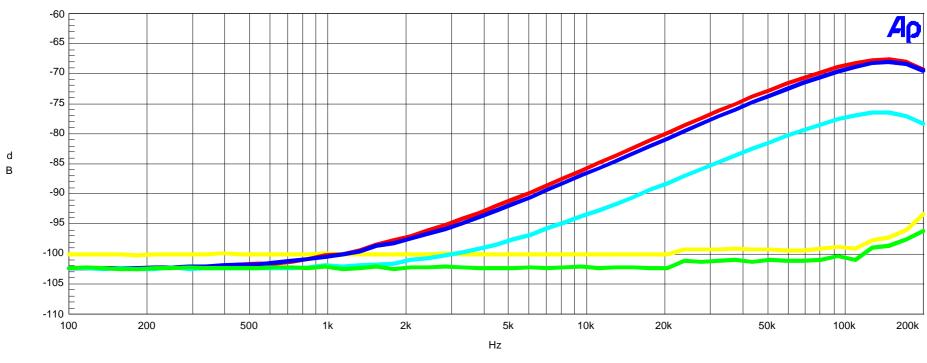

# THD+N vs. Frequency for Various Capacitor types

| Sweep | Trace | Color  | Line Style | Thick | Data             | Axis | Comment |

|-------|-------|--------|------------|-------|------------------|------|---------|

| 1     | 1     | Yellow | Solid      | 1     | Anlr.THD+N Ratio | Left | C = 0   |

| 2     | 1     | Red    | Solid      | 1     | Anlr.THD+N Ratio | Left | C1      |

| 3     | 1     | Blue   | Solid      | 1     | Anlr.THD+N Ratio | Left | C2      |

| 4     | 1     | Cyan   | Solid      | 1     | Anlr.THD+N Ratio | Left | C3      |

| 5     | 1     | Green  | Solid      | 1     | Anlr.THD+N Ratio | Left | C4      |

R = 100 ohm, C = 3.3 nF, Vp-p = 5V f(-3dB) = 482 kHz

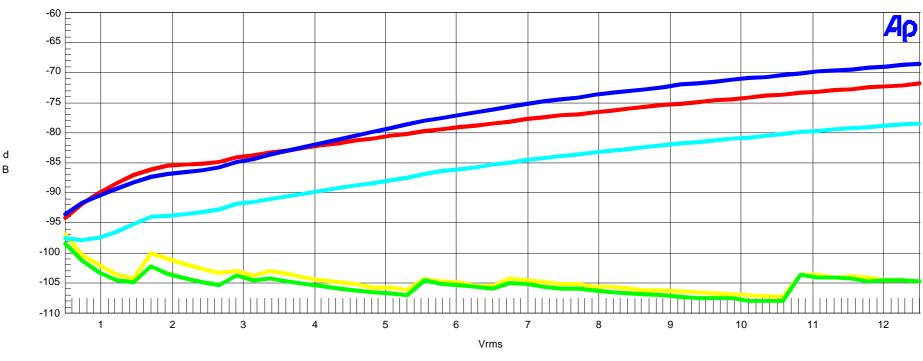

# THD+N vs. Voltage for Various Capacitor Types

| Sweep | Trace | Color  | Line Style | Thick | Data             | Axis | Comment |

|-------|-------|--------|------------|-------|------------------|------|---------|

| 1     | 1     | Yellow | Solid      | 1     | Anlr.THD+N Ratio | Left | C = 0   |

| 2     | 1     | Red    | Solid      | 1     | Anlr.THD+N Ratio | Left | C1      |

| 3     | 1     | Blue   | Solid      | 1     | Anlr.THD+N Ratio | Left | C2      |

| 4     | 1     | Cyan   | Solid      | 1     | Anlr.THD+N Ratio | Left | C3      |

| 5     | 1     | Green  | Solid      | 1     | Anlr.THD+N Ratio | Left | C4      |

R = 100 ohm, C = 3.3 nF, f = 10 kHz, f(-3dB) = 482 kHz

# Conclusions on "C" Type

u Best performance: Sliver Mica or COG(NPO)

u Avoid all other

u Others may cost less and be smaller but can distort signal

## Selecting the Fly-wheel Values

# Fly Wheel Component Selection

- u Pick  $C_{flt} = 20 C_{SH}$  (See Appendix for proof)

- $u R_{flt}$  Calculation

n

$$t_{flt\_settle} = t_{SAMPL} = 12 \ \mathcal{T}_{FLT}$$

Theoretical Minimum

n Practical results

w Use

$$t = 18 \mathcal{T}_{FLT}$$

Margin for:

- Ø Op Amp Output Load Transient

- Op Amp Output Small Signal Settling Time

n

$$R_{flt} = t_{SAMPL}/18 C_{flt}$$

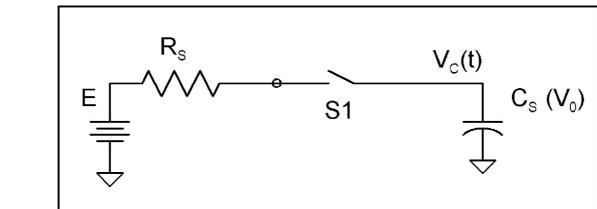

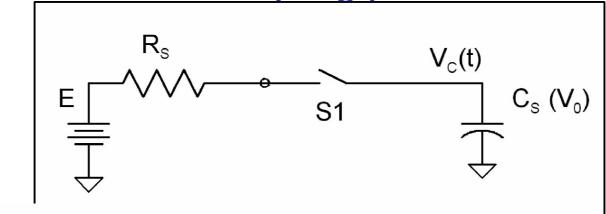

# ADC Sampling Considerations

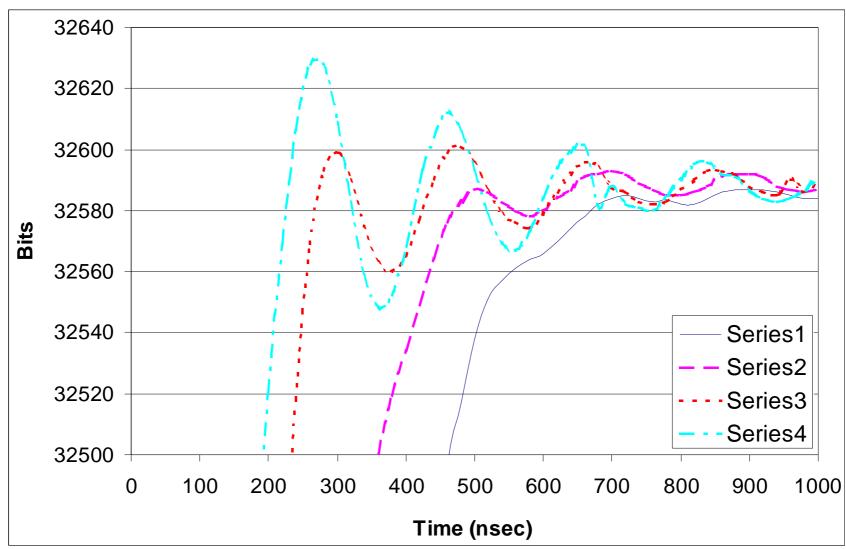

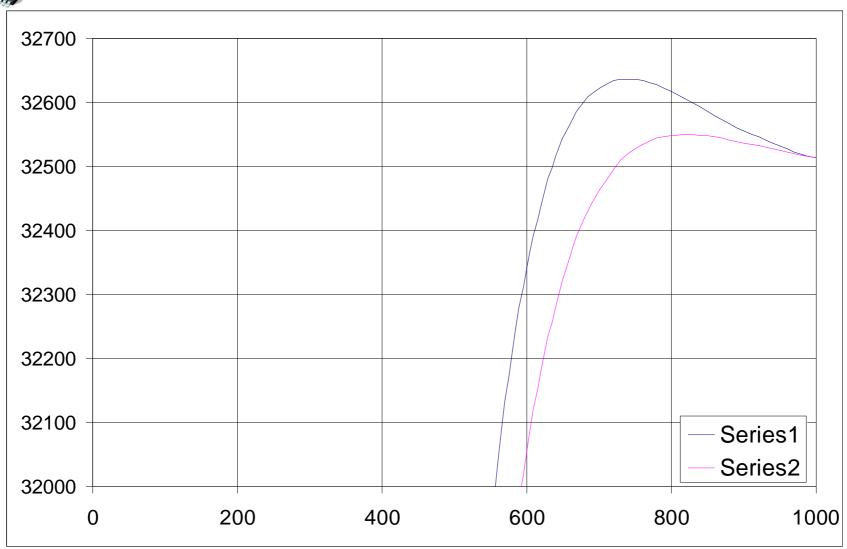

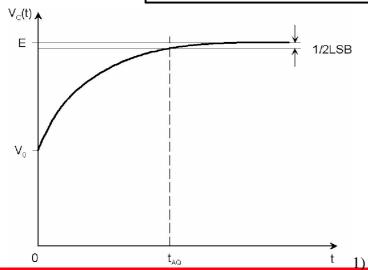

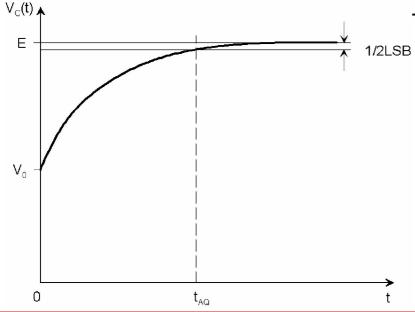

# Voltage on the sampling capacitor during sampling period

$$V_{C}(t) = V_{0} + (E - V_{0}) \times (1 - e^{-\frac{t}{\tau}})$$

$$E - V_{C}(t_{AQ}) \le \frac{1}{2} LSB$$

$$V_{C}(t_{AQ}) \ge E \times (1 - \frac{1}{2^{17}})$$

$$\tau \le \frac{t_{AQ}}{\ln(\frac{E - V_{0}}{E} \times 2^{17})}$$

**TEXAS INSTRUMENTS**

### ADC Sampling Considerations

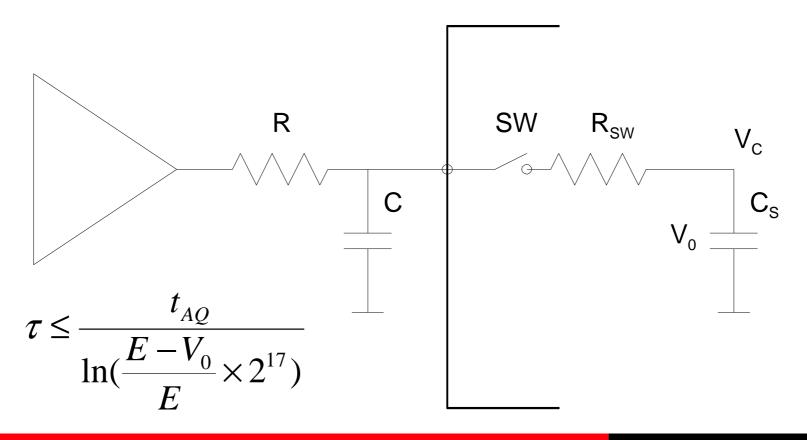

# Suggested input sampling switch transient-immunity RC filter

### Required Settling Time

| Number of bits | 0.5LSB     | Time Constants |

|----------------|------------|----------------|

| 10             | 0.0488281% | 8              |

| 12             | 0.0122070% | 9              |

| 14             | 0.0030518% | 11             |

| 16             | 0.0007629% | 12             |

| 18             | 0.0001907% | 13             |

| 20             | 0.0000477% | 15             |

| 22             | 0.0000119% | 17             |

| 24             | 0.0000030% | 18             |

See appendix for calculations

### Establish Op Amp Specs

Determine Op Amp specs needed based on system values set in design.

Op Amp specs to be determined:

u UGBW

u Slew Rate

u I<sub>out</sub>

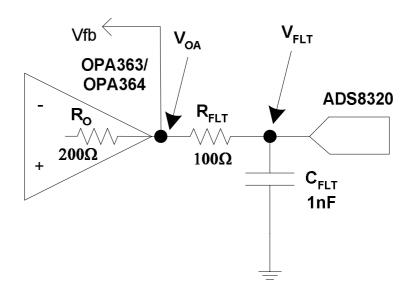

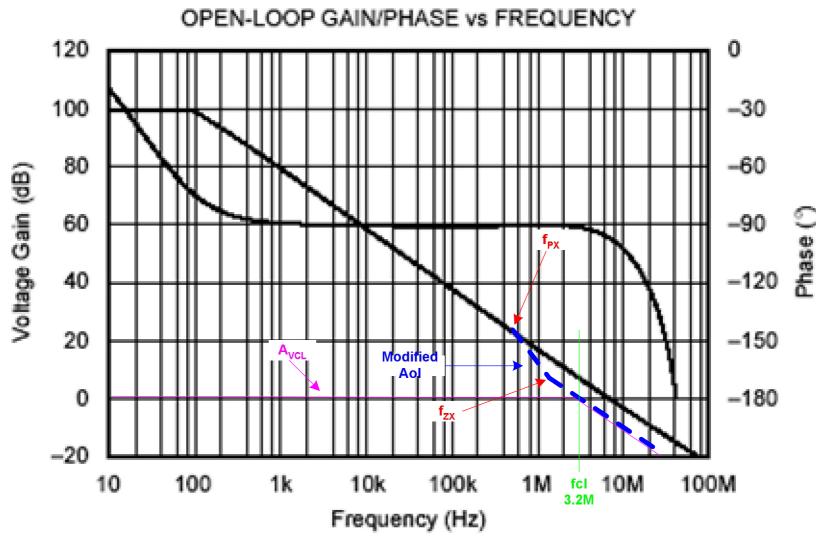

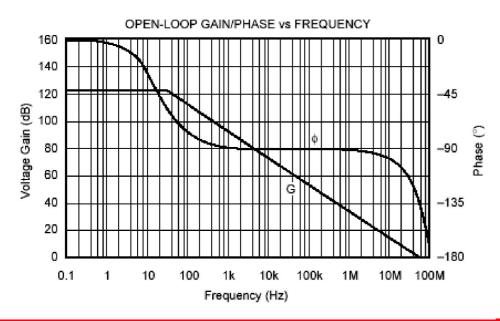

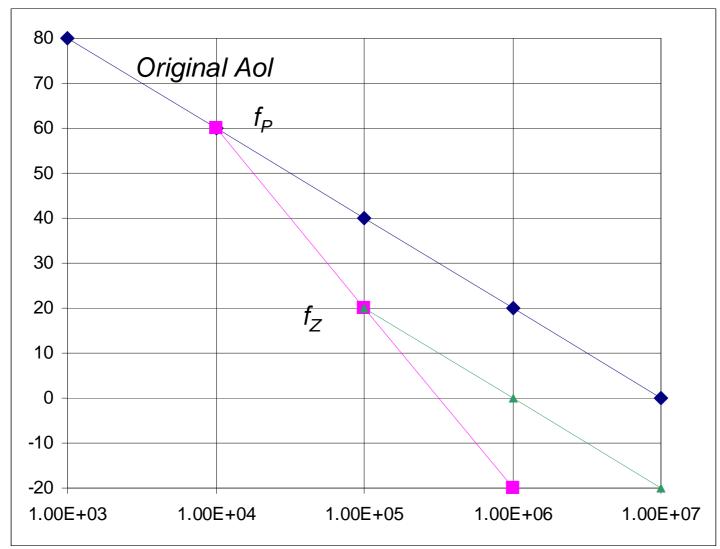

### Impact on UGBW

u Modified  $A_{ol}$  due to  $R_{FLT} \& C_{FLT}$

n

$$f_{PX} = 1/[2 \Pi(R_O + R_{FLT})C_{FLT}]$$

n

$$f_{ZX} = 1/[2 \Pi R_{FLT}C_{FLT}]$$

### u Stability Check

- n At  $f_{cl}$  "Rate-of-closure" is 20dB/decade à  $f_{ZX}$  cancels  $f_{PX}$  before  $f_{cl}$

- n  $f_{PX}$  and  $f_{ZX}$  are  $\leq$  decade apart w Phase of pole will be cancelled by phase of zero

- n This implies:  $R_{FLT} < 9 R_{\odot}$

### u Impact on UGBW

n  $UGBW_{mod} = UGBW_{orig} - (f_{ZX} - f_{PX})$

### Impact on UGBW-cont

43

### Op Amp Specs to Check

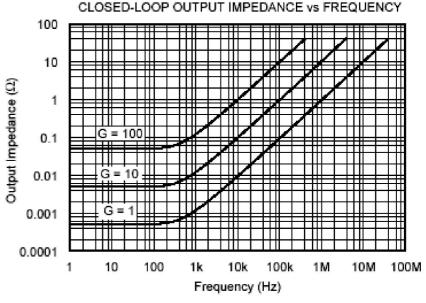

$uUGBW_{mod} > 2*1/[2 \Pi R_{FLT}C_{FLT}]$

u Op Amp Transient Output Drive to  $R_{FLT} \& C_{FLT}$

n

$$I_{Opk max} = (5\% V_{REF})/(R_{FLT})$$

### Interface Design Check List

- u Op Amp Common Mode Voltage

- u Op Amp Output Swing to Rail

- u Op Amp Settling Time

- u Filter Capacitor Type

- u Filter Component Values

- u Op Amp Specifications

### Appendix - Calculation Details

- 1.C<sub>flt</sub> as a Function of C<sub>sh</sub>

- 2. Open Loop Output Resistance

VS.

Closed Loop Output Resistance

- 3. Modified A<sub>ol</sub> Calculations

- 4. Time to Charge Capacitor

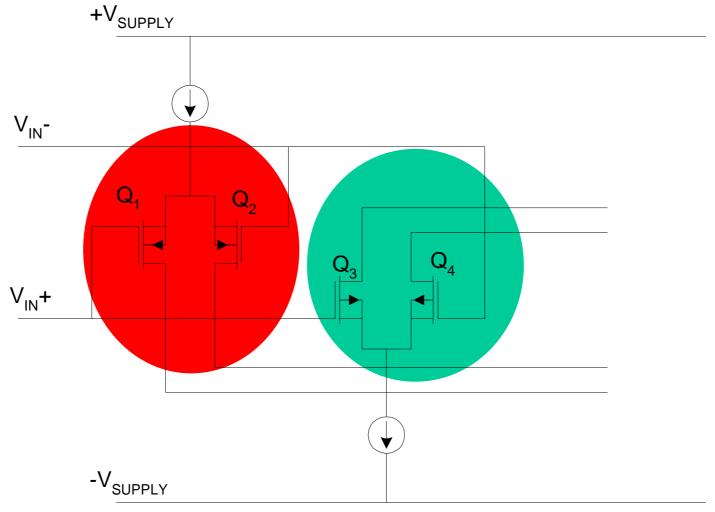

### **Op Amp Input Concerns**

Rail-to-Rail Input

## Input Stage-Parallel P-ch & N-ch

TEXAS INSTRUMENTS

## Looking at Input Stage **Performance**

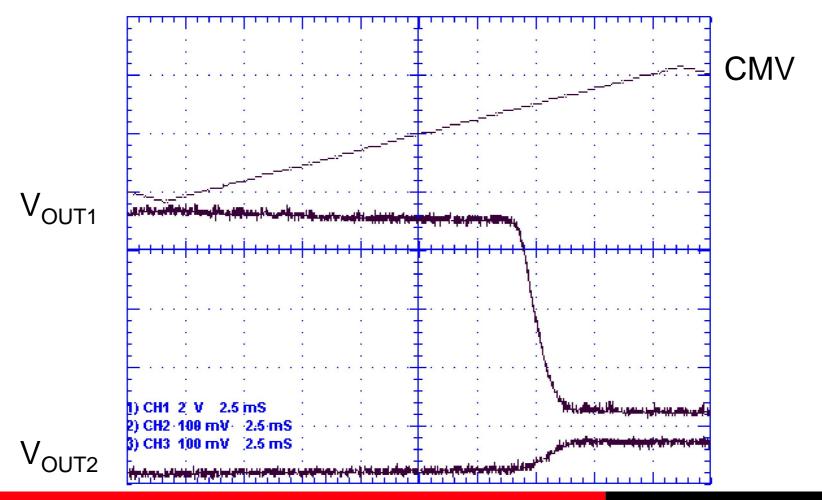

# Single Supply RRI Plot-Vos vs CMV

### (Most RRI Op Amps Except OPA363/OPA364)

OPA2340 (Dual: V<sub>OUT1</sub> & V<sub>OUT2</sub> from different halves)

50

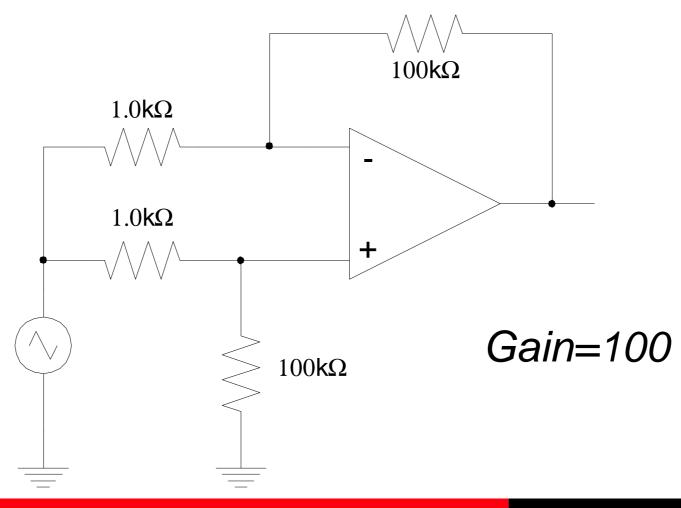

### Performance Requirements

The simple buffer stage.

Most accurate unity gain.

| Bits | (mV)   | (dB)  |

|------|--------|-------|

| 10   | 2.44   | 66.2  |

| 12   | 0.61   | 78.3  |

| 16   | 0.0382 | 102.3 |

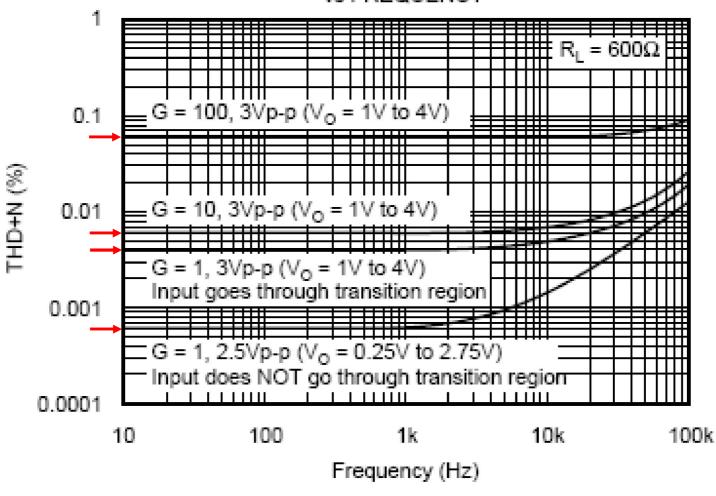

### OPA350 Data Sheet THD+N

### TOTAL HARMONIC DISTORTION + NOISE vs FREQUENCY

52

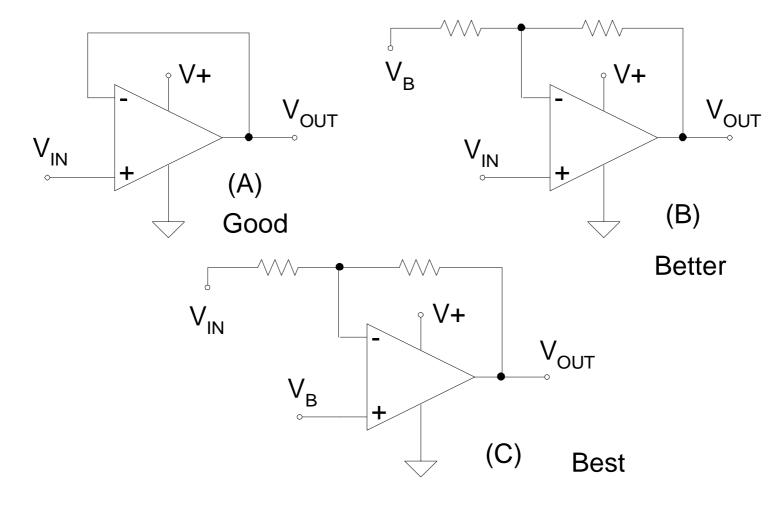

### Possible Input Schemes

| Sweep | Trace | Color  | Line Style | Thick | Data             | Axis | Comment               |

|-------|-------|--------|------------|-------|------------------|------|-----------------------|

| 1     | 1     | Yellow | Solid      | 1     | Anlr.THD+N Ratio | Left | OPA350 High CMRR G=-1 |

| 2     | 1     | Red    | Solid      | 1     | Anlr.THD+N Ratio | Left | OPA350 High CMRR G=+1 |

| 3     | 1     | Blue   | Solid      | 1     | Anlr.THD+N Ratio | Left | OPA350 Low CMRR G=+1  |

| 4     | 1     | Cyan   | Solid      | 1     | Anlr.THD+N Ratio | Left | OPA350 Low CMRR G=-1  |

54

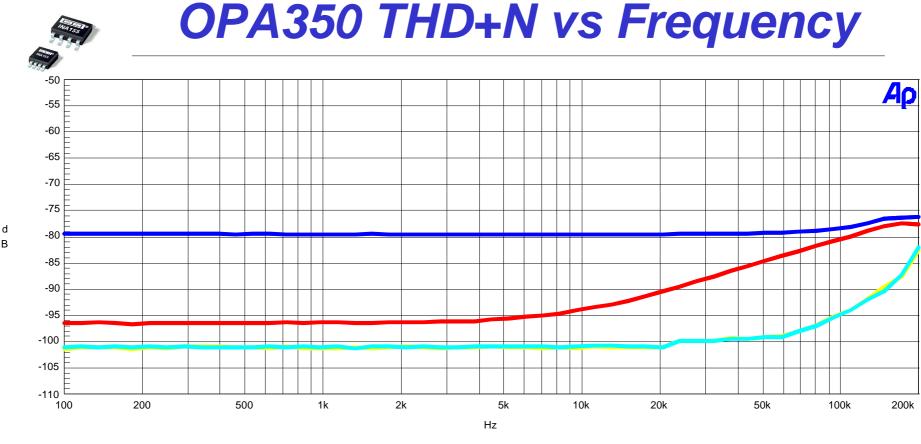

# OPA350 with RC, THD+N vs Frequency -50 -55 -60 -65

-70 -75 -80 -85 -90 -95

| Sweep | Trace | Color  | Line Style | Thick | Data             | Axis | Comment                 |

|-------|-------|--------|------------|-------|------------------|------|-------------------------|

| 1     | 1     | Yellow | Solid      | 1     | Anlr.THD+N Ratio | Left | OPA350 Low CMRR G=+1 C1 |

| 2     | 1     | Red    | Solid      | 1     | Anlr.THD+N Ratio | Left | OPA350 Low CMRR G=-1 C4 |

Hz

5k

10k

20k

50k

TEXAS INSTRUMENTS

100k

200k

1k

500

2k

-100

-105

-110

100

200

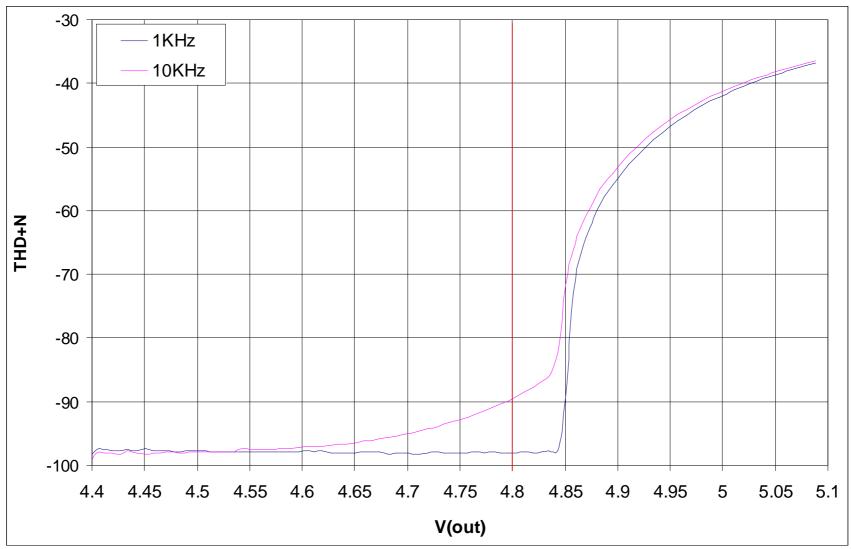

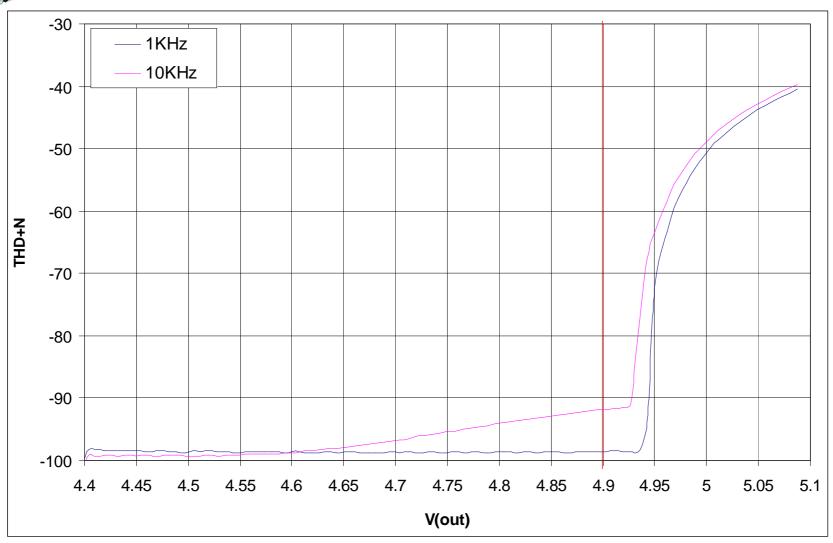

### OPA350 THD+N vs Input Voltage -55 -60 -65 -75 d -80 -85 -95 -100 -105 3.8 4.2 4.8 5.2 3.6 4.4 4.6 5.4 Vpp

| Sweep | Trace | Color  | Line Style | Thick | Data             | Axis | Comment                |

|-------|-------|--------|------------|-------|------------------|------|------------------------|

| 1     | 1     | Yellow | Solid      | 1     | Anlr.THD+N Ratio | Left | OPA350 Low CMRR 1kHz   |

| 2     | 1     | Red    | Solid      | 1     | Anlr.THD+N Ratio | Left | OPA350 Low CMRR 10kHz  |

| 3     | 1     | Cyan   | Solid      | 1     | Anlr.THD+N Ratio | Left | OPA350 Low CMRR 50kHz  |

| 4     | 1     | Green  | Solid      | 1     | Anlr.THD+N Ratio | Left | OPA350 Low CMRR 100kHz |

### Output Stage Concerns

Rail-to-Rail Output

### **OPA300**

### **OPA350**

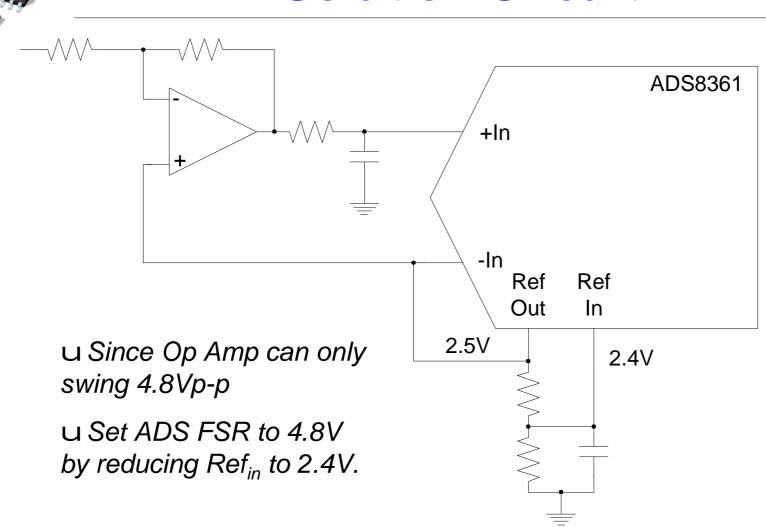

### **Solution Circuit**

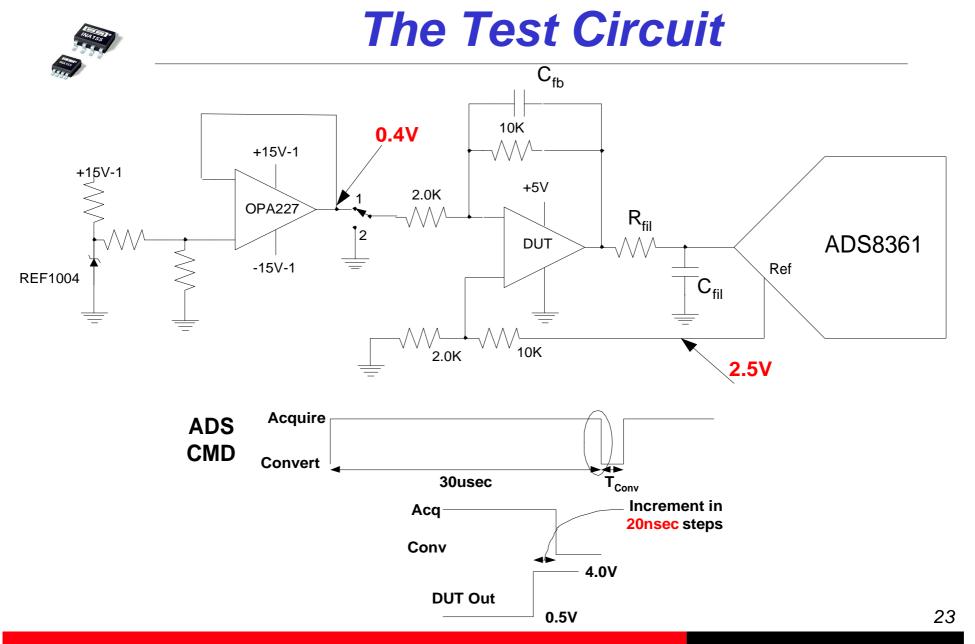

### Filter Design Example

$u R_{SW} = 100$  (Not needed for Buffer & Filter Calculations)

$$U$$

$C_{SH} = 50pF [for ADS8361]$

u Worst case Vacross C<sub>SH</sub> is V<sub>REF</sub>

n

$$V_{REF} = +5V$$

$$u t_{SAMPL} = 1.88 \mu s [for ADS8361]$$

# Filter Design Example(cont)

- u Charge Transfer Equation: Q = CV

- u Charge required to charge C<sub>SH</sub> to V<sub>REF</sub>

n

$$Q_{SH} = C_{SH}V_{REF}$$

n

$$Q_{SH} = 50pF.5V = 250pC$$

- u IDEAL  $C_{FLT}$

- n "Charge Bucket" to fill  $C_{SH}$  with only a 76 $\mu$ V (1/2LSB) droop on  $C_{FLT}$

n

$$Q_{FLT} = Q_{SH}$$

n

$$Q_{FLT} = C_{FLT} (38\mu V)$$

n

$$250pC = C_{FLT}(38\mu V)$$

$C_{FLT} = 6.6\mu F$

- u IDEAL  $C_{FIT} = 6.6 \mu F$

- n Not a good, small, cheap high frequency ceramic capacitor

- n Not practical for Op Amp to drive directly (stability, transient current)

- n Isolation resistor likely not large enough to help isolate Cload and still meet necessary filter time constant

# Filter Design Example(cont)

- u Partition the "Charge Bucket"

- n 95% from  $C_{FIT}$

- n 5% from Op Amp

$\cup$   $C_{FLT}$  value required to provide  $Q_{SH}$  with <5% droop on  $C_{FLT}$

n

$$Q_{FLT} = Q_{SH}$$

n

$$Q_{FLT} = C_{FLT} (0.05 V_{REF})$$

n

$$250pC = C_{FLT} (0.05.5V)$$

$C_{FLT} = 1nF$

- u During  $t_{SAMPL}$  the Op Amp must provide 5%  $V_{REF}$  to  $C_{FLT}$

- n Ensure  $C_{FIT}$  is at least  $10X > C_{SH}$

- w This implies dominant load for Op Amp Buffer is  $C_{FLT}$

- w  $1nF = 20 \times 50pF \stackrel{.}{a} C_{FLT} = 20 \times C_{SH}$

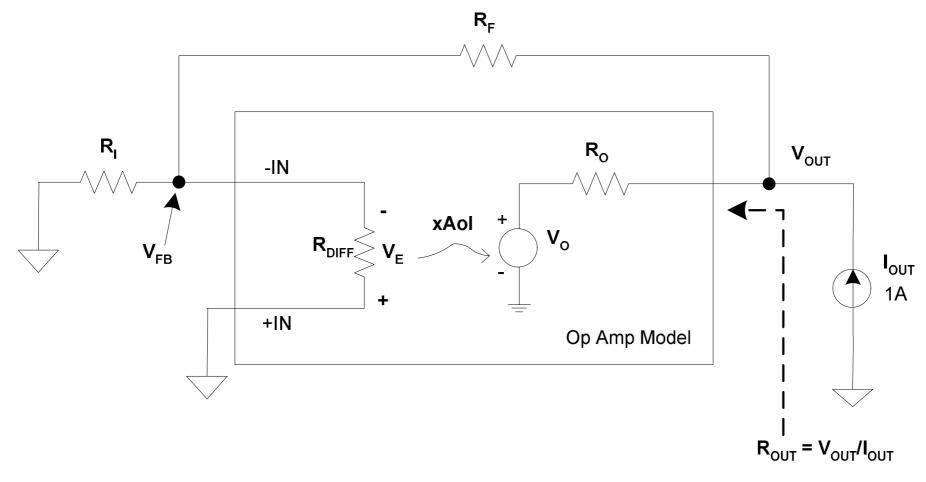

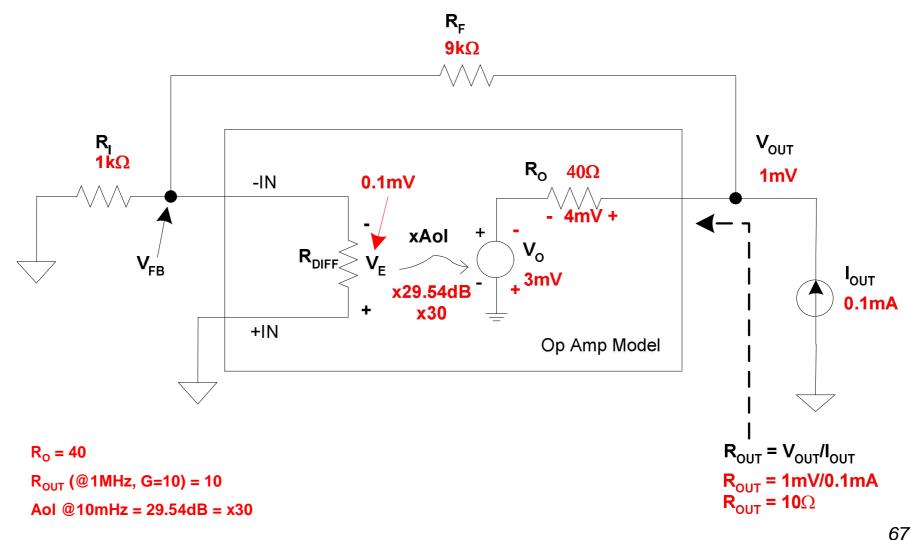

### Op Amp Model for Derivation of R<sub>OUT</sub>

### Derivation of R<sub>OUT</sub> (Closed Loop Output Resistance)

$$\beta = V_{FB}/V_{OUT} = [V_{OUT}(R_I / \{R_F + R_I\})]/V_{OUT} = R_I / (R_F + R_I)$$

$$R_{OUT} = V_{OUT}/I_{OUT}$$

$$V_O = -V_E \text{ AoI}$$

$$V_E = V_{OUT}[R_I/(R_F + R_I)]$$

$$\begin{split} &V_{\text{OUT}} = V_{\text{O}} + I_{\text{OUT}} R_{\text{O}} \\ &V_{\text{OUT}} = -V_{\text{E}} \text{AoI} + I_{\text{OUT}} R_{\text{O}} \\ &V_{\text{OUT}} = -V_{\text{OUT}} \left[ R_{\text{I}} / (R_{\text{F}} + R_{\text{I}}) \right] \text{AoI} + I_{\text{OUT}} R_{\text{O}} \\ &V_{\text{OUT}} + V_{\text{OUT}} \left[ R_{\text{I}} / (R_{\text{F}} + R_{\text{I}}) \right] \text{AoI} = I_{\text{OUT}} R_{\text{O}} \\ &V_{\text{OUT}} = I_{\text{OUT}} R_{\text{O}} / \left\{ 1 + \left[ R_{\text{I}} \text{AoI} / (R_{\text{F}} + R_{\text{I}}) \right] \right\} \end{split}$$

$$R_{OUT} = V_{OUT}/I_{OUT} = I_{OUT}R_O / \{1 + [R_IA_{OL}/(R_F + R_I)]\}$$

$$R_{OUT} = R_O / (1 + AoI\beta)$$

### **OPA353 Specifications**

$$R_O = 40$$

$R_{OUT}$  (@1MHz, G=10) = 10

AoI @1MHz = 29.54dB = x30

# **OPA353** R<sub>OUT</sub> Calculation

# R<sub>OUT</sub> vs R<sub>O</sub>

- □ R<sub>o</sub> does not change when feedback is used to close the loop

- □ Closed loop feedback forces V<sub>o</sub> to increase/decrease

- u The increase/decrease in  $V_o$  appears at  $V_{out}$  as a reduction in  $R_o$

- $\cup$   $R_{OUT}$  is the net effect of  $R_O$  and closed loop feedback controlling  $V_O$

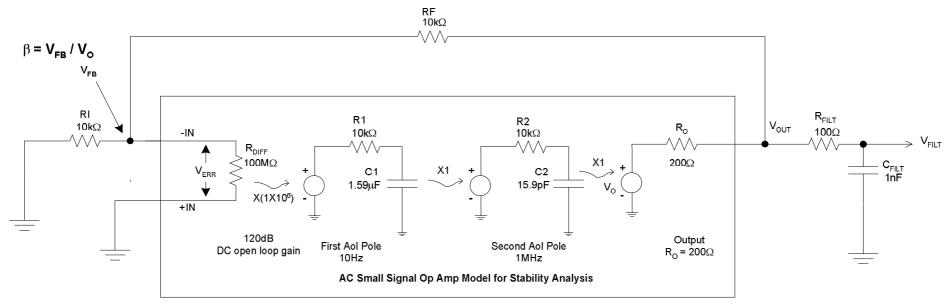

### **Op Amp Model for AC Stability Analysis**

- $\emptyset$   $R_o$  is constant over the Op Amp's bandwidth

- $\emptyset$   $R_o$  is defined as the Op Amp's Open Loop Output Resistance

- $\emptyset$   $R_0$  is measured at  $I_{OUT} = 0$  Amps, f = 1MHz

- $\emptyset$   $R_0$  is included in  $\beta$  calculation

# Aol Modified by Filter

### Modified Aol-The Math

$$V_{OUT} = \frac{V_O \left( R_{flt} + \frac{1}{sC_{flt}} \right)}{R_O + R_{flt} + \frac{1}{sC_{flt}}}$$

$$\frac{V_{OUT}}{V_O} = K = \frac{\left(R_{flt} + \frac{1}{sC_{flt}}\right)}{R_O + R_{flt} + \frac{1}{sC_{flt}}}$$

$$\frac{V_{OUT}}{V_O} = K = \frac{sC_{flt}R_{flt} + 1}{sC_{flt}(R_O + R_{flt}) + 1}$$

$$\frac{V_{OUT}}{V_O} = K = \frac{s + \frac{1}{C_{flt}R_{flt}}}{\frac{C_{flt}(R_O + R_{flt})}{C_{flt}R_{flt}}s + \frac{1}{C_{flt}R_{flt}}}$$

### Modified Aol-The Math - cont.

$$\frac{V_{OUT}}{V_{O}} = K = \frac{\left(s + \frac{1}{C_{flt}R_{flt}}\right)\left(\frac{C_{flt}R_{flt}}{C_{flt}(R_{O} + R_{flt})}\right)}{s + \left(\frac{1}{C_{flt}R_{flt}}\right)\left(\frac{C_{flt}R_{flt}}{C_{flt}(R_{O} + R_{flt})}\right)}$$

$$\frac{V_{OUT}}{V_{O}} = K = \frac{\left(s + \frac{1}{C_{flt}R_{flt}}\right)\left(\frac{R_{flt}}{(R_{O} + R_{flt})}\right)}{s + \left(\frac{1}{C_{flt}R_{flt}}\right)\left(\frac{R_{flt}}{(R_{O} + R_{flt})}\right)}$$

$$\frac{V_{OUT}}{V_O} = K = \left(\frac{R_{fit}}{(R_O + R_{fit})}\right) \frac{\left(s + \frac{1}{C_{fit}R_{fit}}\right)}{\left(s + \frac{1}{C_{fit}(R_O + R_{fit})}\right)}$$

$$f_p = \frac{1}{2\Pi C_{flt} (R_O + R_{flt})}; \quad f_z = \frac{1}{2\Pi C_{flt} R_{flt}}$$

# Voltage on the sampling capacitor during sampling period

$$V_C(t) = V_0 + (E - V_0) \times (1 - e^{-\frac{t}{\tau}})$$

$$E - V_C(t_{AQ}) \le \frac{1}{2} LSB$$

$$V_C(t_{AQ}) \ge E \times (1 - \frac{1}{2^{17}})$$

$$\tau \le \frac{t_{AQ}}{\ln(\frac{E - V_0}{E} \times 2^{17})}$$