## 描述

DDC 公司的 BU-65170、61580 及 BU-61585 (PCI) 总线控制器/远程终端/监控器终端 (BC/RT/MT) 高级通信引擎 (ACE) 终端兼容主处理器与 MIL-STD-1553A、B 或 STANAG 3838 总线之间全部的集成接口。

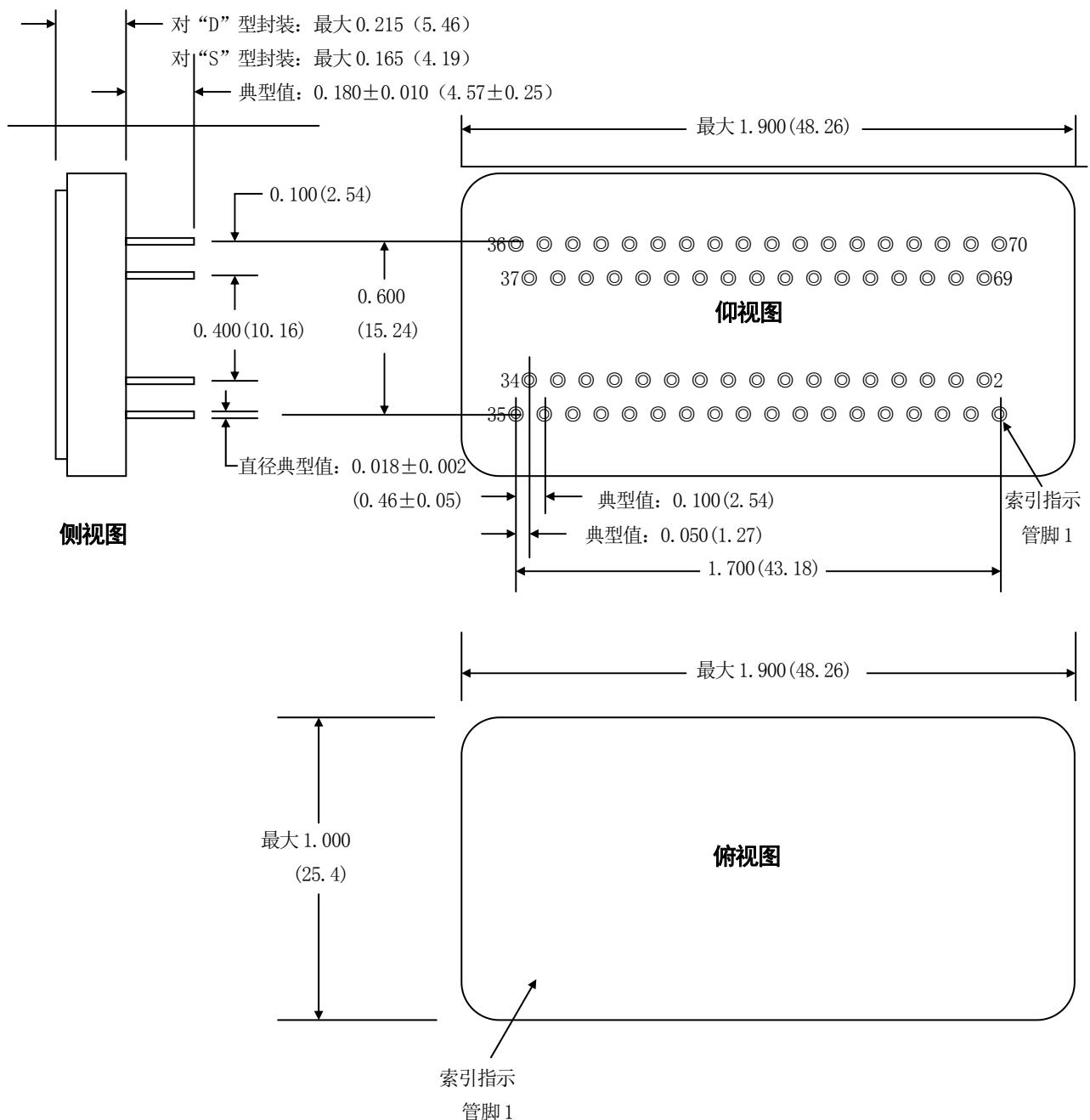

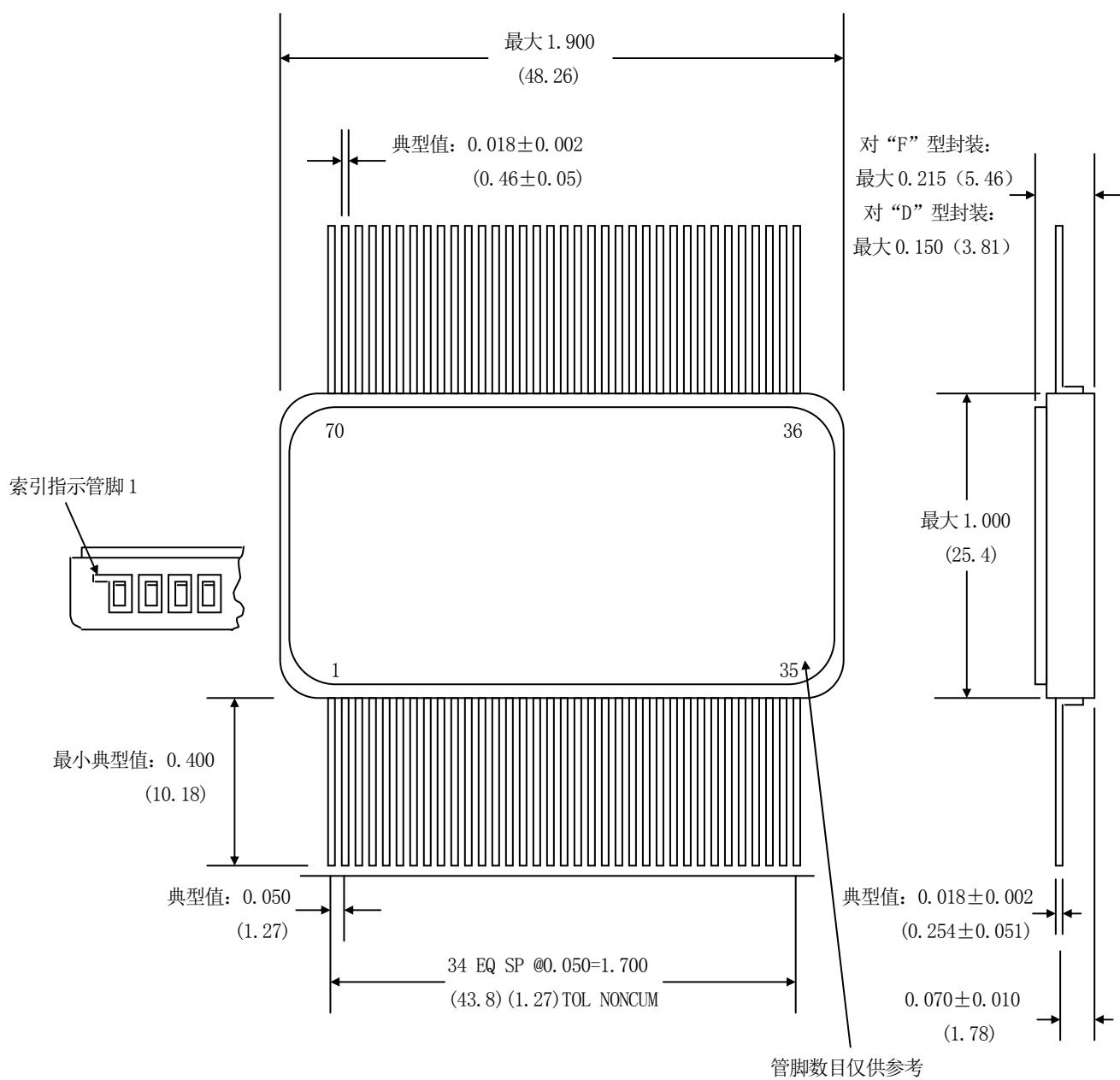

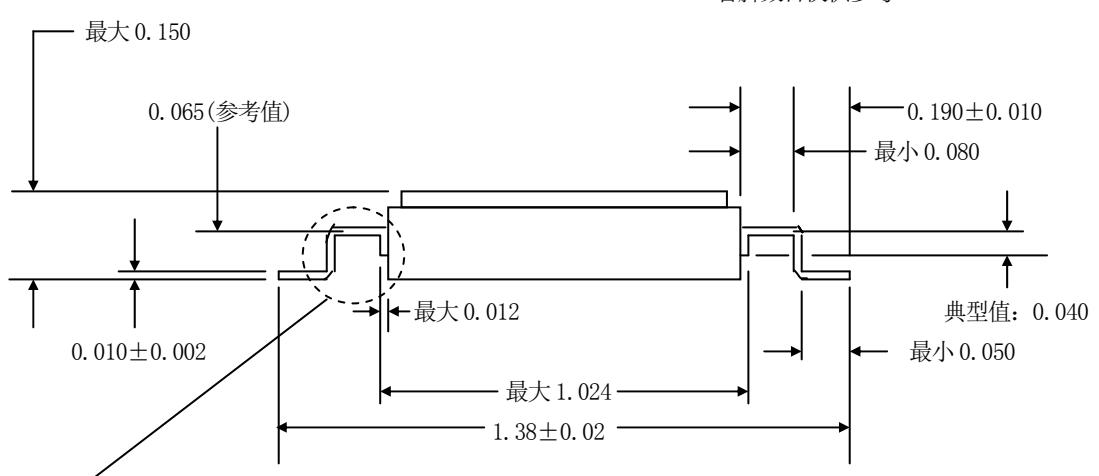

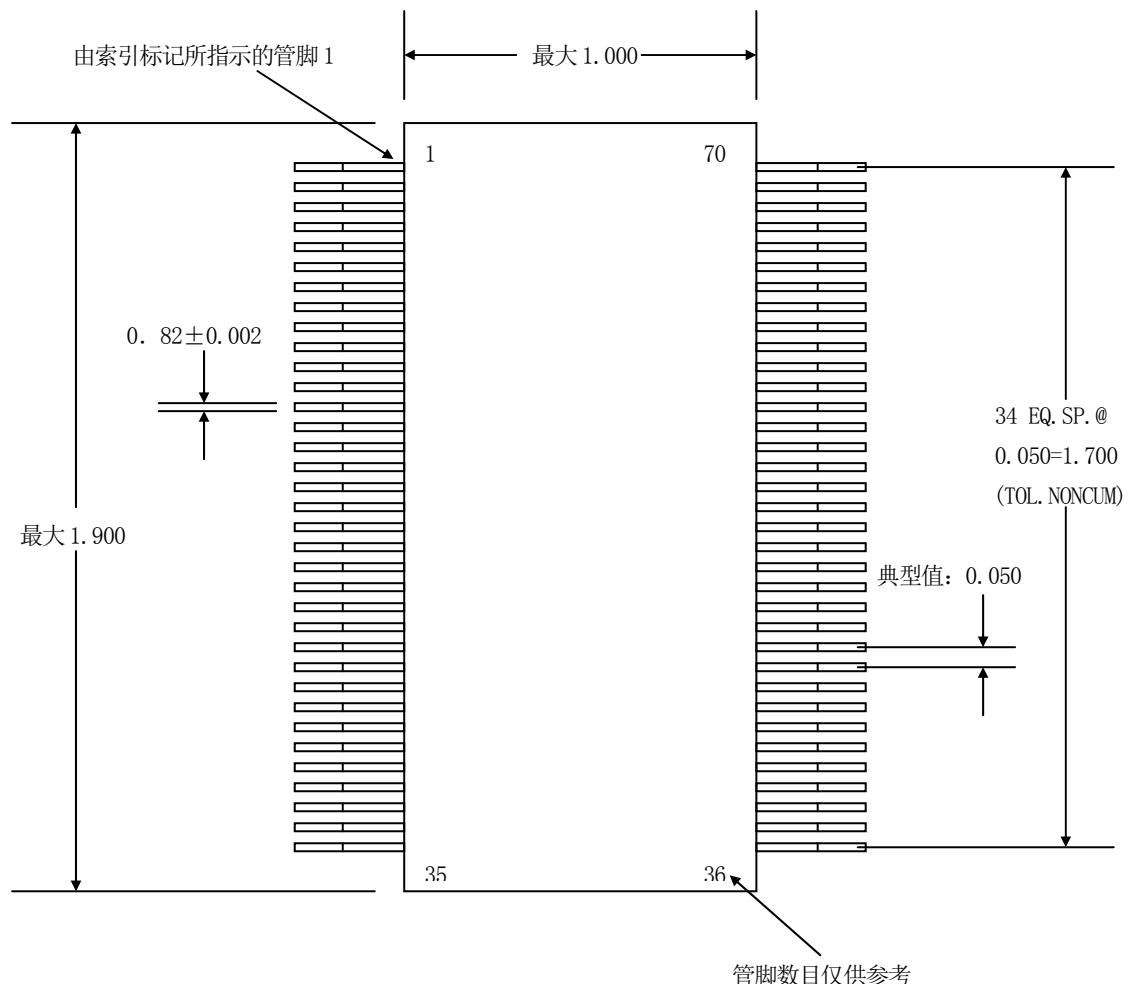

ACE 系列终端为 1.9 平方英寸、70 个引脚、low-profile、cofired 的多片模式 (MCM) 陶瓷封装片形式, 能够很好地适用于具有很高要求的场合。

BU-61585 ACE 集成了两个收发器、协议、存储器管理、处理器接口逻辑以及一个总计 12KW 的 RAM, 有双列直插及扁平封装两种封装形式可供选择。BU-61585 需+5V 以及或-15V、或-12V 电压供电。

BU-61585 内部 RAM 可被配置成  $12K \times 16$  或  $8K \times 17$  的形式, 在所有访问过程中, 通过利用 RAM 奇偶产生/校验,  $8K \times 17$  形式提供了对 RAM 完整检测的能力。为减小印制板的空间及粘合逻辑, 在和主处理器及内/外部 RAM 接口时, ACE 具有基本的灵活性。

ACE 终端的高级功能结构提供了和 DDC 的高级集成多路传输 (AIM) 系列混合器相兼容的软件, 同时体现了结构性增强的多样性。它允许灵活的操作, 同时不装载 (off-loading) 主处理器、保证数据抽样的一致性, 并支持海量数据的传送。

ACE 混合器可工作在 12 或 16MHz 下, 对可编程的 RT 地址 (硬连线是标准的) 以及外部发送器禁止输入来说, 允许有“有线连接”选项。

## 特征

- 全集成 MIL-STD-1553 接口

- 灵活的处理器/存储器接口

- 标准的  $4K \times 16$  以及可选的  $12K \times 16$  或  $8K \times 17$  RAM

- 可选的 RAM 奇偶产生/校验

- 自动 BC 重试

- 可编程的 BC 间隔定时

- BC 帧自动重复

- 灵活的 RT 数据缓存

- 可编程的非法化

- 可任选的消息监控器

- 同时制 RT/监控器模式

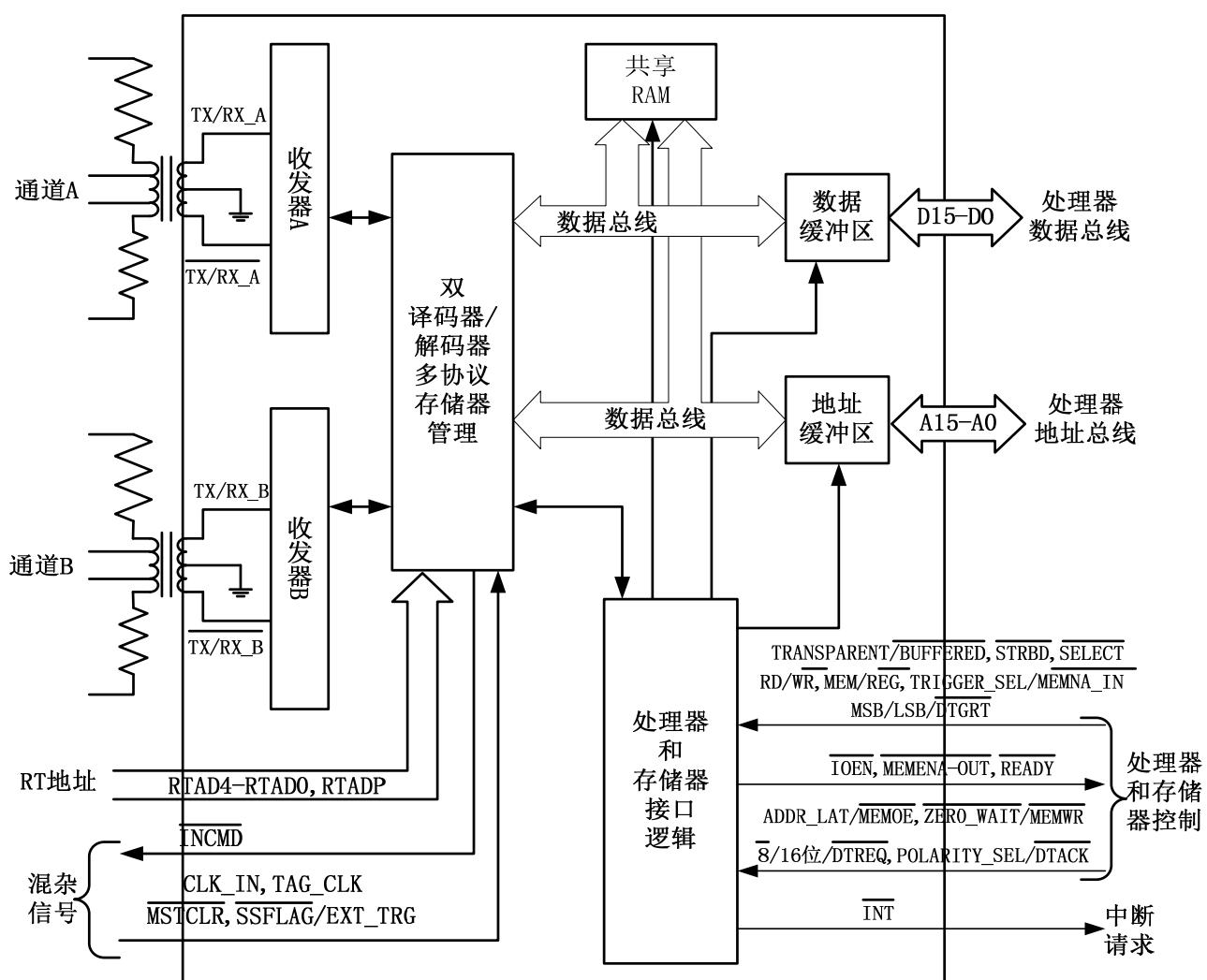

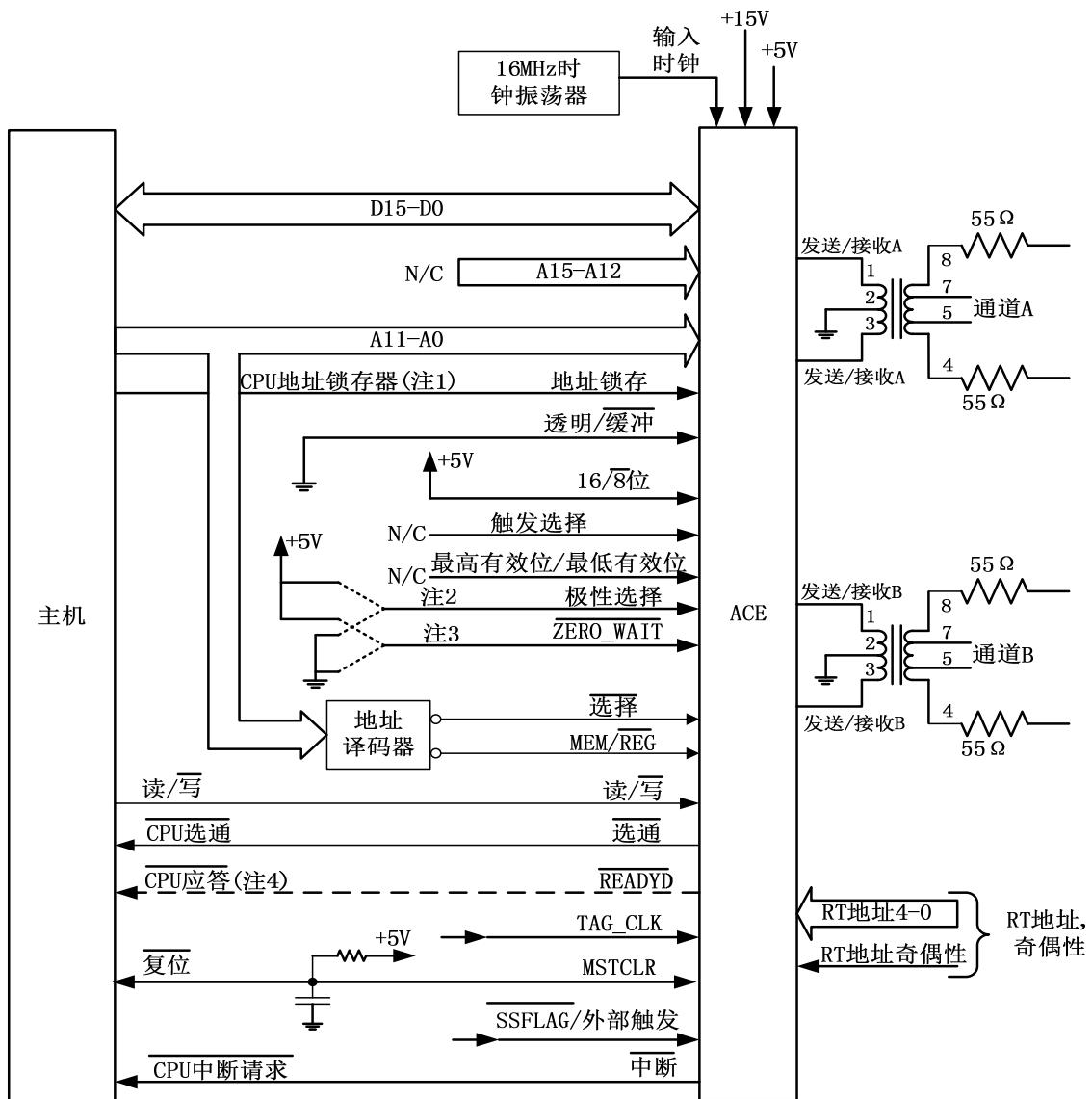

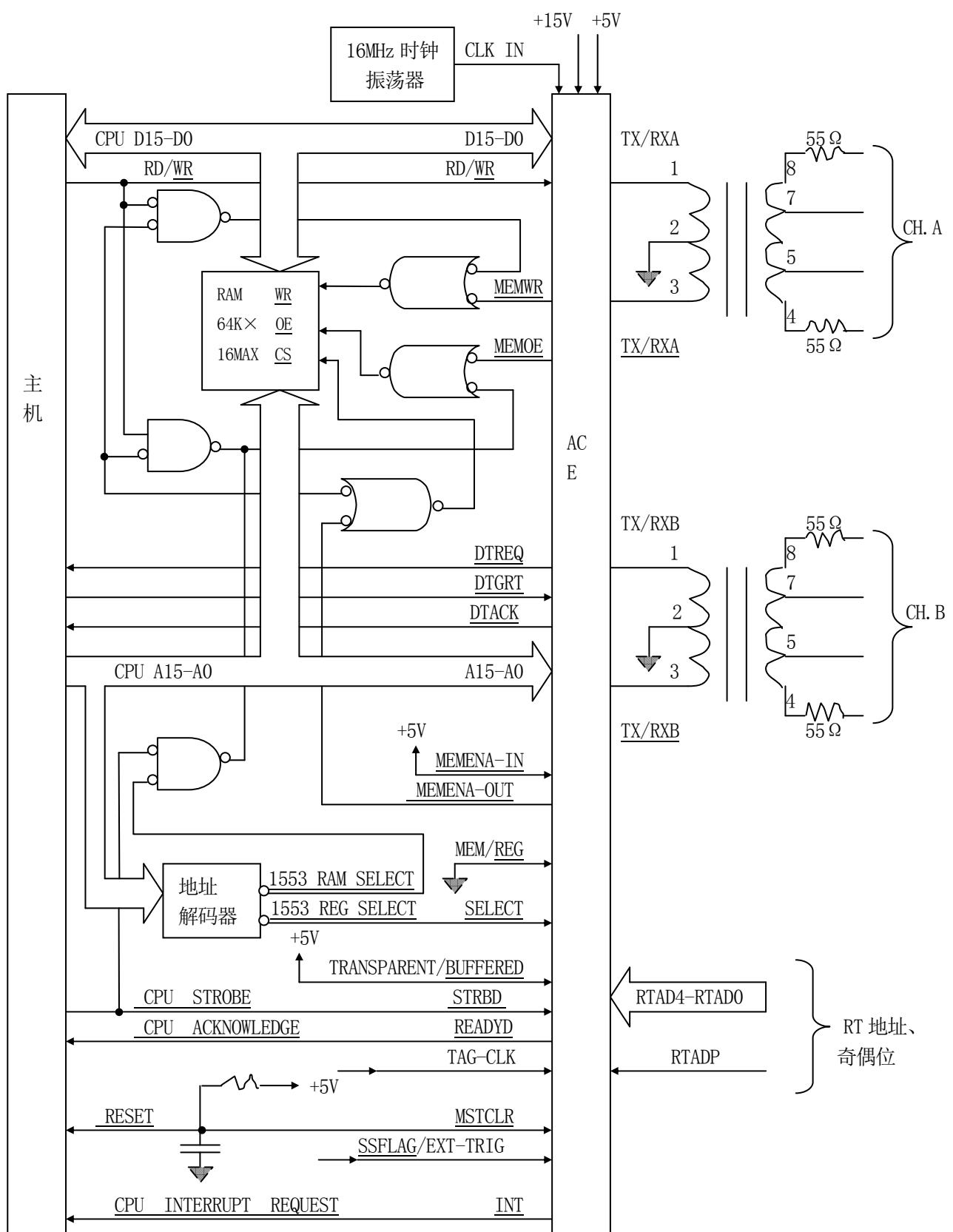

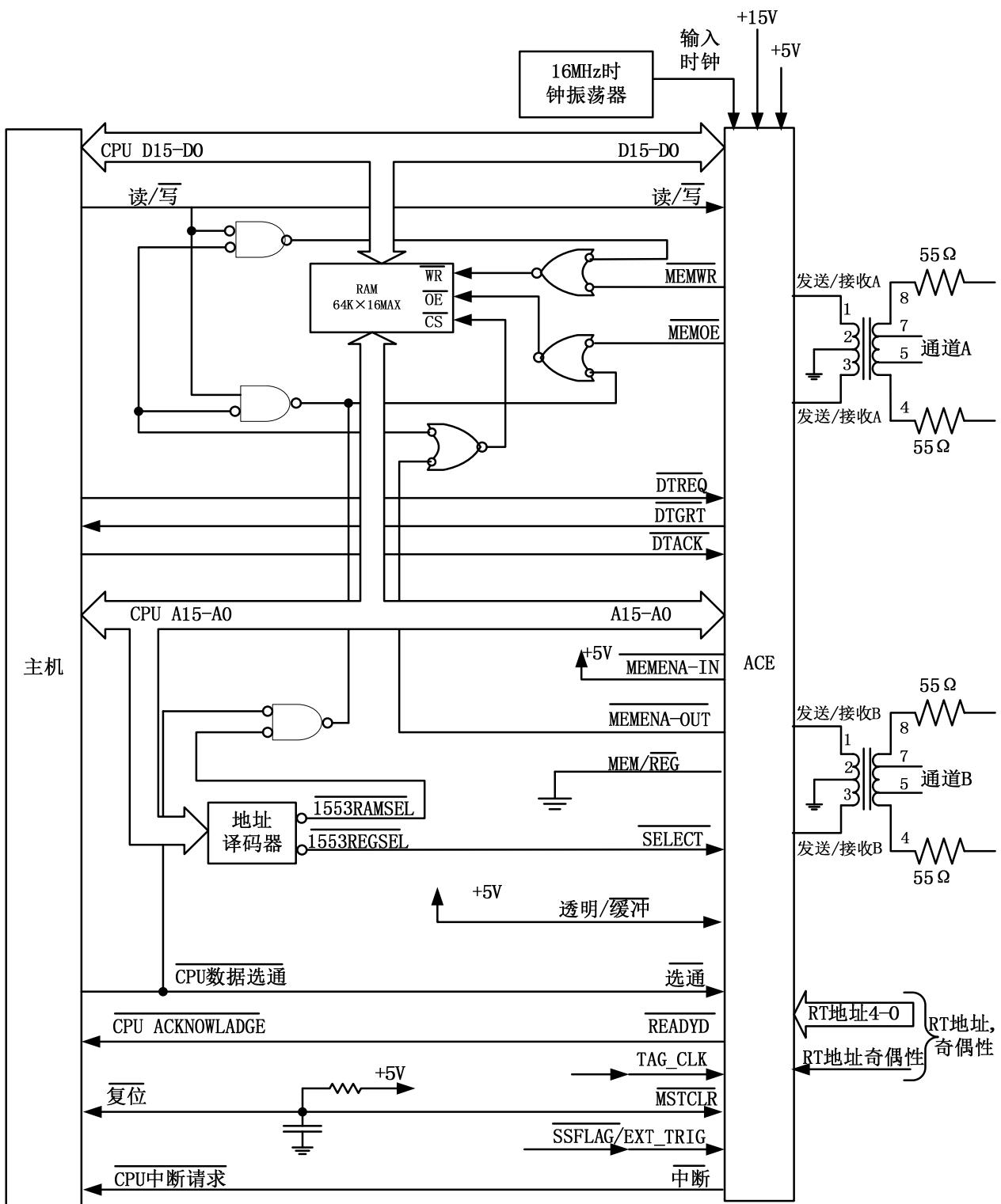

图 1 ACE 模块图

表1 “ACE” 系列详细说明

| 参数                                                                                                                                                                            | 最小    | 典型      | 最大    | 单位                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-------|--------------------------|

| <b>绝对最大值</b>                                                                                                                                                                  |       |         |       |                          |

| 电源电压                                                                                                                                                                          |       |         |       |                          |

| ■ 逻辑+5V                                                                                                                                                                       | -0.3  |         | 7.0   | V                        |

| ■ 收发器+5V                                                                                                                                                                      | -0.3  |         | 7.0   | V                        |

| ■ -15V                                                                                                                                                                        | -18.0 |         | 0.3   | V                        |

| ■ -12V                                                                                                                                                                        | -18.0 |         | 0.3   | V                        |

| 逻辑                                                                                                                                                                            |       |         |       |                          |

| ■ 电压输入范围                                                                                                                                                                      | -0.3  | VCC+0.3 |       | V                        |

| <b>接收器</b>                                                                                                                                                                    |       |         |       |                          |

| 差分输入电阻                                                                                                                                                                        |       |         |       |                          |

| ■ (BU-65170/61580/61585×1、BU-65170/61580/61585×2) (注 1-7)                                                                                                                     | 11    |         |       | KΩ                       |

| ■ (BU-65170/61580/61585×3、BU-65170/61580/61585×6) (注 1-7)                                                                                                                     | 2.5   |         |       | KΩ                       |

| 差分输入电容                                                                                                                                                                        |       |         |       |                          |

| ■ (BU-65170/61580/61585×1、BU-65170/61580/61585×2) (注 1-7)                                                                                                                     |       | 10      |       | pF                       |

| ■ (BU-65170/61580/61585×3、BU-65170/61580/61585×6) (注 1-7)                                                                                                                     |       | 5       |       | pF                       |

| 门限电压 (变压器耦合、短截线上测得)                                                                                                                                                           | 0.200 |         | 0.860 | V <sub>p-p</sub>         |

| 共模电压 (注 7)                                                                                                                                                                    |       |         | 10    | V <sub>peak</sub>        |

| <b>发送器</b>                                                                                                                                                                    |       |         |       |                          |

| 差分输出电压                                                                                                                                                                        |       |         |       |                          |

| ■ 跨接 35Ω 直接耦合、在总线上测得                                                                                                                                                          | 6     | 7       | 9     | V <sub>p-p</sub>         |

| ■ 跨接 70Ω 变压器耦合、在总线上测得                                                                                                                                                         |       | 20      | 27    | V <sub>p-p</sub>         |

| ■ (BU-65170/61580/61585×1、BU-65170/61580/61585×2、×3、×6)                                                                                                                       |       | 18      | 27    | V <sub>p-p</sub>         |

| 输出噪音 (差分、直接耦合)                                                                                                                                                                |       |         | 10    | mV <sub>p-p</sub> , diff |

| 输出偏移电压 (变压器耦合、短截线上测得)                                                                                                                                                         | -250  |         | 250   | mV                       |

| 上升/下降时间                                                                                                                                                                       | 100   | 150     | 300   | nsec                     |

| <b>逻辑</b>                                                                                                                                                                     |       |         |       |                          |

| V <sub>IH</sub>                                                                                                                                                               | 2.0   |         |       | V                        |

| V <sub>IL</sub>                                                                                                                                                               |       |         | 0.8   | V                        |

| I <sub>IH</sub> (V <sub>CC</sub> =5.5V, V <sub>IN</sub> =V <sub>CC</sub> )                                                                                                    | -10   |         | 10    | uA                       |

| I <sub>IL</sub> (V <sub>CC</sub> =5.5V, V <sub>IN</sub> =2.7V)                                                                                                                |       |         |       |                          |

| ■ <u>SSFLAG/EXT-TRIG</u>                                                                                                                                                      | -692  |         | -84   | uA                       |

| ■ 所有其它输入                                                                                                                                                                      | -346  |         | -42   | uA                       |

| I <sub>IL</sub> (V <sub>CC</sub> =5.5V, V <sub>IN</sub> =0.4V)                                                                                                                |       |         |       |                          |

| ■ <u>SSFLAG/EXT-TRIG</u>                                                                                                                                                      | -794  |         | -100  | uA                       |

| ■ 所有其它输入                                                                                                                                                                      | -397  |         | -50   | uA                       |

| V <sub>OH</sub> (V <sub>CC</sub> =4.5V, V <sub>IH</sub> =2.7V, V <sub>IL</sub> =0.2V, I <sub>OH</sub> =最大)                                                                    | 2.4   |         |       | V                        |

| V <sub>OL</sub> (V <sub>CC</sub> =4.5V, V <sub>IH</sub> =2.7V, V <sub>IL</sub> =0.2V, I <sub>OL</sub> =最大)                                                                    |       |         | 0.4   | V                        |

| I <sub>OL</sub>                                                                                                                                                               |       |         |       |                          |

| ■ DB15-DB0、A15-A0、 <u>MEMOE</u> /ADDR-LAT、 <u>MEMWR</u> / <u>ZERO-WAIT</u> 、 <u>DTREQ/16/8</u> 、 <u>DTACK</u> /POLARITY-SEL                                                   | 6.4   |         |       | mA                       |

| ■ <u>INCMD</u> 、 <u>INT</u> 、 <u>MEMENA-OUT</u> 、 <u>READYD</u> 、 <u>IOEN</u> 、 <u>TXA</u> 、 <u>TXA</u> 、 <u>TXB</u> 、 <u>TXB</u> 、 <u>TX-INH-OUT-A</u> 、 <u>TX-INH-OUT-B</u> | 3.2   |         |       | mA                       |

表1 “ACE” 系列详细说明 (续1)

| 参数                                                                                                                                                                            | 最小     | 典型    | 最大     | 单位 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|-------|--------|----|

| <b>逻辑 (续)</b>                                                                                                                                                                 |        |       |        |    |

| IOH                                                                                                                                                                           |        |       | 6.4    | mA |

| ■ DB15-DB0、A15-A0、 <u>MEMOE</u> /ADDR-LAT、 <u>MEMWR</u> / <u>ZERO-WAIT</u> 、 <u>DTREQ</u> /16/8、 <u>DTACK</u> /POLARITY-SEL                                                   |        |       | 3.2    | mA |

| ■ <u>INCMD</u> 、 <u>INT</u> 、 <u>MEMENA-OUT</u> 、 <u>READYD</u> 、 <u>IOEN</u> 、 <u>TXA</u> 、 <u>TXA</u> 、 <u>TXB</u> 、 <u>TXB</u> 、 <u>TX-INH-OUT-A</u> 、 <u>TX-INH-OUT-B</u> |        |       | 50     | pF |

| CI(输入电容)                                                                                                                                                                      |        |       | 50     | pF |

| CI0(双向信号输入电容)                                                                                                                                                                 |        |       | 50     | pF |

| <b>电源要求</b>                                                                                                                                                                   |        |       |        |    |

| 差分输入电阻                                                                                                                                                                        |        |       |        |    |

| ■ BU-65170/61580/61585×1                                                                                                                                                      |        |       |        |    |

| • +5V (逻辑)                                                                                                                                                                    | 4.5    | 5.0   | 5.5    | V  |

| • +5V (通道A、通道B)                                                                                                                                                               | 4.5    | 5.0   | 5.5    | V  |

| • -15V (通道A、通道B)                                                                                                                                                              | -15.75 | -15.0 | -14.25 | V  |

| ■ BU-65170/61580/61585×2                                                                                                                                                      |        |       |        |    |

| • +5V (逻辑)                                                                                                                                                                    | 4.5    | 5.0   | 5.5    | V  |

| • +5V (通道A、通道B)                                                                                                                                                               | 4.5    | 5.0   | 5.5    | V  |

| • -12V (通道A、通道B)                                                                                                                                                              | -12.6  | -12.0 | -11.4  | V  |

| ■ BU-65170/61580/61585×3、BU-65170/61580/61585×6                                                                                                                               |        |       |        |    |

| • +5V (逻辑)                                                                                                                                                                    | 4.5    | 5.0   | 5.5    | V  |

| • +5V (通道A、通道B)                                                                                                                                                               | 4.75   | 5.0   | 5.25   | V  |

| 漏电流                                                                                                                                                                           |        |       |        |    |

| ■ BU-65170/61580×1                                                                                                                                                            |        |       |        |    |

| • +5V (逻辑、通道A、通道B)                                                                                                                                                            | 95     | 190   | mA     |    |

| • -15V (通道A、通道B)                                                                                                                                                              |        |       |        |    |

| • 空闲                                                                                                                                                                          | 30     | 60    | mA     |    |

| • 25%发送器工作周期                                                                                                                                                                  | 68     | 108   | mA     |    |

| • 50%发送器工作周期                                                                                                                                                                  | 105    | 160   | mA     |    |

| • 100%发送器工作周期                                                                                                                                                                 | 180    | 255   | mA     |    |

| ■ BU-65170/61580×2                                                                                                                                                            |        |       |        |    |

| • +5V (逻辑、通道A、通道B)                                                                                                                                                            | 95     | 190   | mA     |    |

| • -12V (通道A、通道B)                                                                                                                                                              |        |       |        |    |

| • 空闲                                                                                                                                                                          | 30     | 60    | mA     |    |

| • 25%发送器工作周期                                                                                                                                                                  | 80     | 120   | mA     |    |

| • 50%发送器工作周期                                                                                                                                                                  | 130    | 185   | mA     |    |

| • 100%发送器工作周期                                                                                                                                                                 | 230    | 305   | mA     |    |

| ■ BU-65170/61580×3、BU-65170/61580×6                                                                                                                                           |        |       |        |    |

| • +5V (逻辑、通道A、通道B)                                                                                                                                                            |        |       |        |    |

| • 空闲                                                                                                                                                                          | 95     | 200   | mA     |    |

| • 25%发送器工作周期                                                                                                                                                                  | 245    | 350   | mA     |    |

| • 50%发送器工作周期                                                                                                                                                                  | 360    | 500   | mA     |    |

| • 100%发送器工作周期                                                                                                                                                                 | 590    | 800   | mA     |    |

表1 “ACE” 系列详细说明 (续2)

| 参数                                  | 最小    | 典型   | 最大 | 单位 |

|-------------------------------------|-------|------|----|----|

| <b>电源要求(续)</b>                      |       |      |    |    |

| 漏电流                                 |       |      |    |    |

| ■ BU-61585×1                        |       |      |    |    |

| • +5V (逻辑、通道A、通道B)                  | 105   | 240  | mA |    |

| • -15V (通道A、通道B)                    |       |      |    |    |

| • 空闲                                | 30    | 60   | mA |    |

| • 25%发送器工作周期                        | 68    | 120  | mA |    |

| • 50%发送器工作周期                        | 105   | 185  | mA |    |

| • 100%发送器工作周期                       | 180   | 305  | mA |    |

| ■ BU-61585×2                        |       |      |    |    |

| • +5V (逻辑、通道A、通道B)                  | 105   |      | mA |    |

| • -12V (通道A、通道B)                    |       |      |    |    |

| • 空闲                                | 30    | 240  | mA |    |

| • 25%发送器工作周期                        | 80    |      | mA |    |

| • 50%发送器工作周期                        | 130   |      | mA |    |

| • 100%发送器工作周期                       | 230   |      | mA |    |

| ■ BU-61585×3、BU-61585×6             |       |      |    |    |

| • +5V (逻辑、通道A、通道B)                  |       |      |    |    |

| • 空闲                                | 105   | 250  | mA |    |

| • 25%发送器工作周期                        | 255   | 400  | mA |    |

| • 50%发送器工作周期                        | 370   | 550  | mA |    |

| • 100%发送器工作周期                       | 600   | 850  | mA |    |

| <b>功耗</b>                           |       |      |    |    |

| 全部混合器                               |       |      |    |    |

| ■ BU-65170/61580×1                  |       |      |    |    |

| • 空闲                                | 0.850 | 1.85 | W  |    |

| • 25%发送器工作周期                        | 1.195 | 2.25 | W  |    |

| • 50%发送器工作周期                        | 1.450 | 2.72 | W  |    |

| • 100%发送器工作周期                       | 1.975 | 3.52 | W  |    |

| ■ BU-65170/61580×2                  |       |      |    |    |

| • 空闲                                | 0.835 | 1.67 | W  |    |

| • 25%发送器工作周期                        | 1.135 | 2.10 | W  |    |

| • 50%发送器工作周期                        | 1.435 | 2.59 | W  |    |

| • 100%发送器工作周期                       | 2.035 | 3.46 | W  |    |

| ■ BU-65170/61580×3、BU-65170/61580×6 |       |      |    |    |

| • 空闲                                | 0.475 | 1.00 | W  |    |

| • 25%发送器工作周期                        | 0.905 | 1.43 | W  |    |

| • 50%发送器工作周期                        | 1.160 | 1.86 | W  |    |

| • 100%发送器工作周期                       | 1.670 | 2.72 | W  |    |

| ■ BU-61585×1                        |       |      |    |    |

| • 空闲                                | 0.900 | 2.10 | W  |    |

| • 25%发送器工作周期                        | 1.245 | 2.50 | W  |    |

| • 50%发送器工作周期                        | 1.500 | 2.97 | W  |    |

| • 100%发送器工作周期                       | 2.025 | 3.77 | W  |    |

表1 “ACE” 系列详细说明 (续3)

| 参数                                  | 最小    | 典型   | 最大 | 单位 |

|-------------------------------------|-------|------|----|----|

| <b>功耗 (续)</b>                       |       |      |    |    |

| 全部混合器                               |       |      |    |    |

| ■ BU-61585×2                        |       |      |    |    |

| • 空闲                                | 0.885 | 1.92 | W  |    |

| • 25%发送器工作周期                        | 1.185 | 2.35 | W  |    |

| • 50%发送器工作周期                        | 1.485 | 2.84 | W  |    |

| • 100%发送器工作周期                       | 2.085 | 3.71 | W  |    |

| ■ BU-61585×3、BU-61585×6             |       |      |    |    |

| • 空闲                                | 0.525 | 1.25 | W  |    |

| • 25%发送器工作周期                        | 0.955 | 1.68 | W  |    |

| • 50%发送器工作周期                        | 1.210 | 2.11 | W  |    |

| • 100%发送器工作周期                       | 1.720 | 2.97 | W  |    |

| 最热 Die                              |       |      |    |    |

| ■ BU-65170/61580×1                  |       |      |    |    |

| • 空闲                                | 0.335 | 0.68 | W  |    |

| • 25%发送器工作周期                        | 0.600 | 1.06 | W  |    |

| • 50%发送器工作周期                        | 0.860 | 1.45 | W  |    |

| • 100%发送器工作周期                       | 1.385 | 2.23 | W  |    |

| ■ BU-65170/61580×2                  |       |      |    |    |

| • 空闲                                | 0.290 | 0.59 | W  |    |

| • 25%发送器工作周期                        | 0.590 | 0.92 | W  |    |

| • 50%发送器工作周期                        | 0.890 | 1.36 | W  |    |

| • 100%发送器工作周期                       | 1.490 | 2.16 | W  |    |

| ■ BU-65170/61580×3、BU-65170/61580×6 |       |      |    |    |

| • 空闲                                | 0.200 | 0.25 | W  |    |

| • 25%发送器工作周期                        | 0.630 | 0.68 | W  |    |

| • 50%发送器工作周期                        | 0.885 | 1.11 | W  |    |

| • 100%发送器工作周期                       | 1.395 | 1.97 | W  |    |

| ■ BU-61585×1                        |       |      |    |    |

| • 空闲                                | 0.335 | 0.68 | W  |    |

| • 25%发送器工作周期                        | 0.600 | 1.06 | W  |    |

| • 50%发送器工作周期                        | 0.860 | 1.45 | W  |    |

| • 100%发送器工作周期                       | 1.385 | 2.23 | W  |    |

| ■ BU-61585×2                        |       |      |    |    |

| • 空闲                                | 0.290 | 0.59 | W  |    |

| • 25%发送器工作周期                        | 0.590 | 0.92 | W  |    |

| • 50%发送器工作周期                        | 0.890 | 1.36 | W  |    |

| • 100%发送器工作周期                       | 1.490 | 2.16 | W  |    |

| ■ BU-61585×3、BU-61585×6             |       |      |    |    |

| • 空闲                                | 0.200 | 0.25 | W  |    |

| • 25%发送器工作周期                        | 0.630 | 0.68 | W  |    |

| • 50%发送器工作周期                        | 0.885 | 1.11 | W  |    |

| • 100%发送器工作周期                       | 1.395 | 1.97 | W  |    |

表1 “ACE” 系列详细说明 (续4)

| 参数                                  | 最小   | 典型                                | 最大   | 单位         |

|-------------------------------------|------|-----------------------------------|------|------------|

| <b>时钟输入</b>                         |      |                                   |      |            |

| 频率                                  |      |                                   |      |            |

| ■ 标称值 (可编程的)                        |      |                                   |      |            |

| • 缺省模式                              | 16.0 |                                   |      | MHz        |

| • 软件可编程选项                           | 12.0 |                                   |      | MHZ        |

| ■ 长期容许量                             |      |                                   |      |            |

| • 1553A 模式                          |      | 0.01                              |      | %          |

| • 1553B 模式                          |      | 0.1                               |      | %          |

| ■ 短期容许量、1 秒                         |      |                                   |      |            |

| • 1553A 模式                          |      | 0.001                             |      | %          |

| • 1553B 模式                          |      | 0.01                              |      | %          |

| ■ 工作周期                              |      |                                   |      |            |

| • 16MHz                             | 33   | 67                                |      | %          |

| • 12MHz                             | 40   | 60                                |      | %          |

| <b>1553 消息定时</b>                    |      |                                   |      |            |

| CPU 写操作的完成 (BC 开始到下一个消息的开始)         |      | 2.5                               |      | us         |

| BC 消息间隔 (注 8)                       |      | 9.5                               |      | us         |

| BC/RT/MT 响应暂停 (注 9)                 |      |                                   |      |            |

| ■ 18.5 标称值                          | 17.5 | 18.5                              | 19.5 | us         |

| ■ 22.5 标称值                          | 21.5 | 22.5                              | 23.5 | us         |

| ■ 50.5 标称值                          | 49.5 | 50.5                              | 51.5 | us         |

| ■ 128.0 标称值                         | 127  | 129.5                             | 131  | us         |

| RT T 响应暂停 (注 11)                    | 4    |                                   | 7    | us         |

| 发送器看门狗暂停                            |      | 688                               |      | us         |

| <b>热参数</b>                          |      |                                   |      |            |

| 热电阻、节点- 壳                           |      |                                   |      |            |

| 最热 Die (θ JC)                       |      |                                   |      |            |

| ■ BU-65170/61580×1、BU-65170/61580×2 |      |                                   | 6.99 | °C/W       |

| ■ BU-65170/61580×3、BU-65170/61580×6 |      |                                   | 6.8  | °C/W       |

| 工作节温                                | -55  |                                   | 150  | °C         |

| 储藏温度                                | -65  |                                   | 150  | °C         |

| 引线温度 (焊接、10 秒)                      |      |                                   | +300 | °C         |

| <b>物理特征</b>                         |      |                                   |      |            |

| 尺寸                                  |      |                                   |      |            |

| ■ BU-65170/61580/61585 S            |      | 1.9×1.0×0.165<br>(48.3×25.4×4.19) |      | 英寸<br>(毫米) |

| ■ BU-65170/61580/61585 V            |      | 1.9×1.0×0.150<br>(48.3×25.4×3.81) |      | 英寸<br>(毫米) |

| 重量                                  |      |                                   |      |            |

| ■ BU-65170/61580/61585 S/V          |      | 0.6(17)                           |      | 盎司 (克)     |

表1注：注1到注6适用于接收器差分电阻及差分电容的说明

- (1) 该说明包括接收器及发送器 (在内部是连在一起的)

- (2) 阻抗的测试是直接在 BU-65170/61580××混合器的管脚 TX/RX A(B) 及 TX/RX A(B) 之间进行的。

- (3) 假定混合器所有的电源及地输入端都被连接。

- (4) 该说明适用于上电及非上电两种情况

- (5) 该说明假定是 2V rms 的平衡、差分、正旋输入的情况，适用频率范围是 75KHz 到 1MHz。

- (6) 所给的最小电阻及最大电容参数在整个工作范围内都是满足要求的，但未经在整个工作范围内测试。

- (7) 假定共模电压的频率范围是直流到 2MHz，在短截线一侧的隔离变压器的管脚上(直接耦合或变压器耦合)测得，以混合器的地为参考点。使用的变压器必须是 DDC 推荐的或能提供相同的最小 CMRR (共模抑制比) 的其它变压器。

- (8) 对最小消息间间隔定时来说，其典型值在软件的控制下可以增加到 (65535us 减去消息本身的时间)，其单位增量是 1us。

- (9) 是软件可编程的 (4 个选项)，包括 RT-to-RT 暂停 (发送指令的中间奇偶位到发送 RT 状态的中间同步位之间的时间)。

- (10) 是对+5V 逻辑及收发器而言的，对通道 A 及通道 B 来说，是+5V。

- (11) 是从指令字的中间奇偶位过零点开始到 RT 状态字的中间同步位过零点为止进行测量的。

- (12) 对 BU-65171、BU-61581、及 BU-61586 的说明与对 BU-65170、BU-61580、及 BU-61585 的说明是分别完全相同的。

-

## 1 介绍

DDC 的集成 BC/RT/MT 混合器 ACE 系列在微处理器和 MIL-STD-1553A、B Notice 2、McAir、或 STANAG 3838 总线之间提供了完整的、灵活的接口，可完成 BC、RT 及 MT 模式。封装形式为一个单片 1.9 平方英寸、70 个引脚的 DIP 或表面贴装，或 J-引线封装。ACE 系列含有两个低功耗收发器和编码/解码器、完整的 BC/RT/MT 多协议逻辑、存储器管理及中断逻辑、共享的  $4K \times 16$  静态 RAM 以及一个与主处理器总线可直接相连的缓冲接口。

BU-65170/61580 含内部地址锁存器及双向数据缓存器，可与主处理器总线直接接口。在缓存的共享 RAM 配置方式下，BU-65170/61580 可与 16 位及 8 位微处理器直接相连。另外，通过直接存储器访问 (DMA) 接口，ACE 可以和 16 位微处理器总线相连。BU-65170/61580 含有 4KW 的缓存 RAM，非此即彼，无论在共享 RAM，还是在 DMA 配置方式下，ACE 都可以和多达 64KW 的外部 RAM 相连。

ACE RT 模式是多协议的，支持 MIL-STD-1553A、MIL-STD-1553B Notice 2、STANAG 3838 (含 EFA 总线)，以及 McAir A3818、A5232 及 A5690 协议，完全服从 McAir 规则，但需使用正弦收发器 (收发器选项 5)，参见 BU-61590 数据页以获取 McAir 终端的更多信息。

RT 模式的存储器管理方案提供了一个广播数据分离的选项，与 1553B Notice 2 是一致性的。双缓存器和循环缓存器选项都可以通过子地址编程。这些功能有助于保证数据的一致性，并且对海量数据传送来说，有助于 (off-load) 主处理器。

ACE 系列完成 3 种监控器模式：字监控器、可选择的消息监控器、合并型 RT/可选择监控器。其它功能包括自动重试及 BC 模式的可编程消息间间隔选项、内部定时标签寄存器、内部中断状态寄存器以及 RT 模式的内部指令非法化。

## 2 功能概述

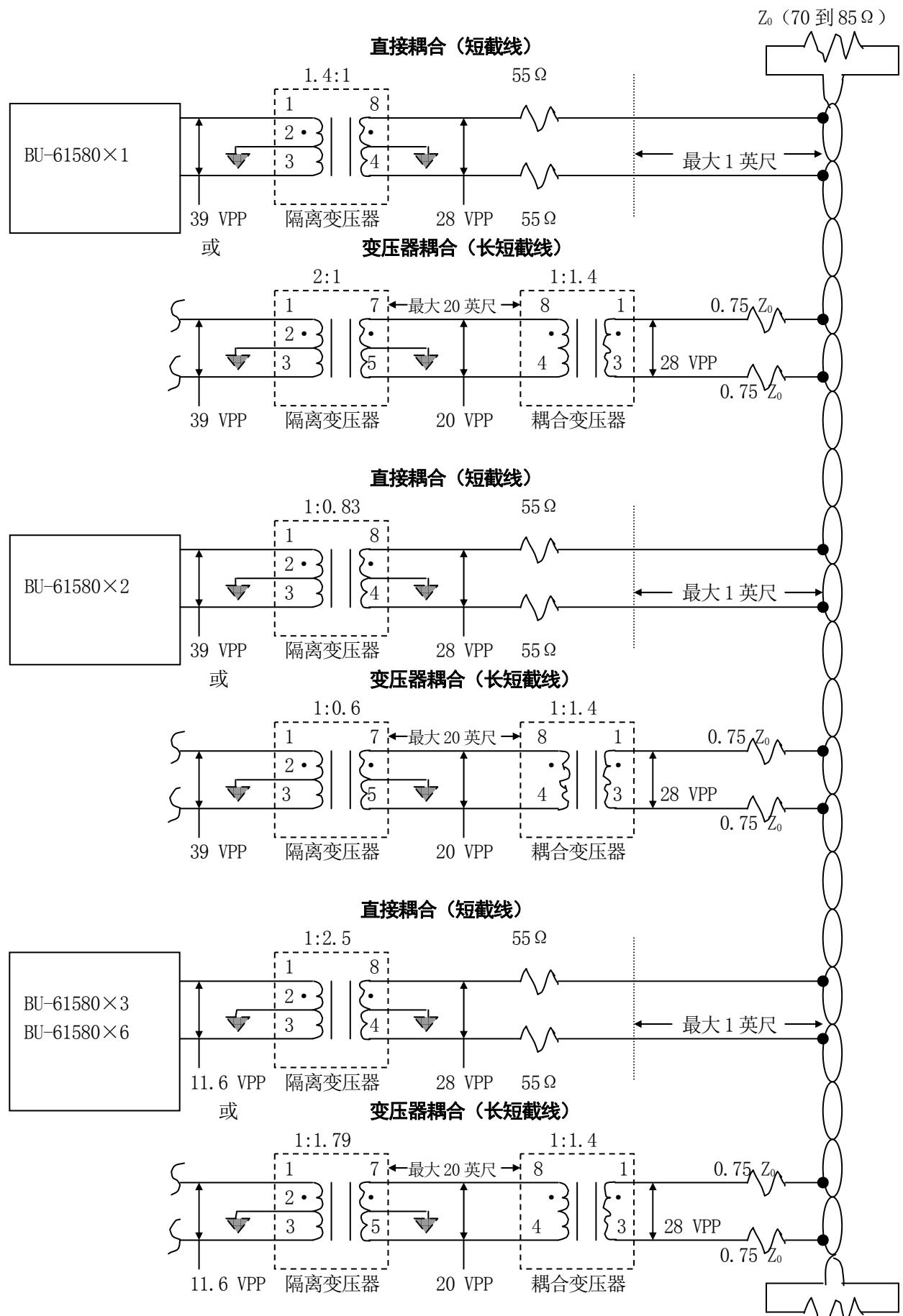

### 2.1 收发器

BU-65170/61580  $\times 3$  ( $\times 6$ ) 中的收发器全部都是单片的，只需+5V 电源输入。除取消了对其它电源输入的要求外，只需+5 电源输入的收发器还需要利用升压，而不是降压的隔离变压器。与 15V 或 12V 的发送器相比，这样做可能具有的优点是终端输入阻抗较高，因此，输入阻抗的测试就具有更大的余量，被用于对 1553 有效性的测试。这样，还允许在嵌入式 1553 终端的隔离变压器和 LRU 系统连接器之间使用更长的电缆。

对+5V 和-15V/-12V 前端来说，BU-61580  $\times 1$  ( $\times 2$ ) 使用低功耗双极性单片及厚片混合技术，收发器只需+5V 和-15V/-12V (不需要+15V/+12V)，并包括电源发送器。该电源发送器为使用长电缆及总线装载海量数据时提供了超级线驱动能力。另外，BU-65170/61580  $\times 1$  中的单块收发器最大限度地减小了变压器耦合的 20V 峰-峰电压的残端电平，使它们满足 MIL-STD-1760 的要求。

就前端过压保护、门限、共模反射、字的出错率来说，BU-65170/61580 的接收器部分与 MIL-STD-1553B 是完一致的，另外，接收器滤波器和 J 型芯片的曼彻斯特 II 解码器已经被设计成最佳工作形式。

## 2.2 J型数字单片芯片

J型数字单片芯片是ACE终端家族基本成员的代表，开发的J型芯片是DDC的1553协议及接口设计的第五代产品。最近几年，DDC的1553协议及接口设计的发展历程为：(1)分离元件部分，包括多功能混合器（在单个混合器的内部具有很多数量的芯片）及可编程逻辑器件。(2)多功能典型的ASIC，可在单个混合器中完成编码器/解码器及RT协议功能。(3)BUS-61553高级集成多路传输混合器(AIM-HY)系列，除了一个双单/厚片收发器及分离的RAM芯片外，它还包括一个典型的协议芯片和一个分离的典型存储器管理/处理器接口芯片(4)BUS-61559带有增强RT功能的AIM-HY'er，它带有增强的RT功能(AIM-HY'er—除了AIM-HY系列所具有的功能外，AIM-HY'er系列还具有存储器管理及处理器接口功能)。(5)全集成的J型芯片。

J型芯片含有一个双编码/解码器、完整的BC协议、1553A/B/McAir RT及MT模式、存储器管理及中断逻辑、与主处理器总线及可任选的外部RAM灵活的带缓存的接口、以及4KW的片内RAM。参见图1点划线内的部分。除了能实现早期AIM-HY'er系列所有的协议、存储器管理以及接口功能外，J型芯片还做了大量的改进以方便硬件及软件的设计，并进一步off-load 1553终端的主处理器。

## 2.3 解码器

BU-65170 RT和BU-61580 BC/RT/MT缺省模式的操作要求1个16MHz的时钟输入。如果需要，软件编程选项允许对1个12MHz的时钟进行操作。当前的大部分1553解码器采样使用了10MHz或12MHz时钟。在16MHz模式（跟随硬件或软件复位后的缺省），ACE解码器使用16MHz时钟采集1553串行数据。在12MHz模式，解码器采样使用时钟的两个边缘，这样就提供了24MHz的采样速率。比较快的采用速率为J芯片的曼彻斯特II解码器在位出错率和过零失真容限方面提供了优异的性能。

针对MIL-STD-1773应用，需要光纤收发器接口，可以使用一款不含收发器的J芯片—BU-65620。它提供了管脚可编程选项，可以直接接口到光纤接收器的单端输出，不需要外部逻辑。

## 2.4 时间定标

ACE内部含有可读写的内部定时标签寄存器，该寄存器是一个CPU可读写的16位计数器，其分辨率是可编程的，为2、4、6、8、16、32、或64us/LSB。同样，定时标签寄存器的时钟也可以是外部振荡器。另一个选项允许定时标签寄存器的增量是软件可控的。这样做可以支持定时标签寄存器的自检，对BC和RT模式来说，每一个被处理的消息都被装载到相应的描述器堆栈入口的第二个位置(TIME TAG WORD)。

其它选项有：在同步模式指令(不带数据)之后清除定时标签寄存器、或在同步模式指令(带数据)之后装载定时标签寄存器。当定时标签寄存器从0000滚动到FFFF时使能中断请求并设置中断状态寄存器中的一位。假如定时标签寄存器没被装载或已被复位，对64us/LSB到2us/LSB的分辨率来说，这将产生约4秒到131ms的时间间隔。

RT模式的另一个可编程选项是，当ACE响应了一个发送矢量字模式指令后，自动清除“服务请求状态字”位。

## 2.5 中断

ACE系列器件为中断的产生和处理提供了很多可编程选项，中断输出管脚(INT)具有3种软件可编程的工作模式：脉冲、软件控制下清除的电平输出、读中断状态寄存器后自动清除的电平输出。

各中断都被中断屏蔽寄存器所使能。使用中断状态寄存器，主处理器可轻易地判断中断原因，中断状态寄存器提供了中断事件的当前状态。中断状态寄存器的更新有两种途径。在标准中断处理模式中，只有当事件存在且中断屏蔽寄存器中相应的位被使能后，中断状态寄存器中特定的位才会被更新。在增强的中断处理模式中，只要事件存在，不必考虑中断屏蔽寄存器中相应位的内容，中断状态寄存器中特定的位就会被更新。在任何情况下，对特定的事件来说，中断屏蔽寄存器中各个位都会使能一次中断。

# 3 寻址、内部寄存器及存储器管理

正常情况下，BU-65170/61580与主处理器的软件接口有17个内部可操作的寄存器，另有8个测试寄存器，加上 $64K \times 16$ 的共享存储器地址空间。BU-65170/61580的 $4K \times 16$ 的内部RAM就存在于该地址空间。参看图2及图24。

ACE的17个非测试寄存器及测试寄存器地址影像的定义及可访问性如下所示：

## 3.1 中断屏蔽寄存器

对各种事件，用于使能或禁止中断请求。

### 3.2 配置寄存器#1 和#2

用于选择 BU61580 的工作模式、RT 状态字的位的软件控制，激活的存储器区域、BC 因差错停止、RT 存储器管理模式选择，以及定时标签操作的控制。

### 3.3 起始/复位寄存器

用于“指令”类型的功能，比如软件复位、BC/MT 起始、中断复位、定时标签复位以及定时标签寄存器测试。当 BC 工作在自动重复模式时，或在当前消息的结尾，或在当前 BC 帧的结尾，该寄存器可停止 BC。

### 3.4 BC/RT 指令堆栈指针寄存器

当 BU-61580 工作在 BC 或 RT 模式时，该寄存器允许主 CPU 为当前或最近的消息确定其指针位置。

### 3.5 BC 控制字/RT 子地址控制字寄存器

在 BC 模式，它允许主机访问当前或最近的 BC 控制字，BC 控制字包含的位可对激活的总线及消息格式做出选择、使能离线自检、屏蔽状态字的位、使能重试及中断、以及指定对 MIL-STD-1553A 或 MIL-STD-1553B 差错的处理。在 RT 模式，它允许主机访问当前或最近的 RT 子地址控制字，RT 子地址控制字用于选择存储器管理方案并为当前消息使能中断。读/写的可访问性可用来帮助测试 ACE。

### 3.6 定时标签寄存器

保持实时时钟的值，该寄存器的分辨率是可编程的，为 2、4、8、16、32、及 64us/LSB。TAG-CLK 输入信号可以使外部振荡器作为定时标签寄存器的时钟。BC、RT 以及 MT 模式下的 SOM 和 EOM 序列将使定时标签寄存器的当前值写到 RAM 的堆栈区。

### 3.7 中断状态寄存器

镜像中断屏蔽寄存器并包含一个屏蔽中断位。它允许主处理器通过单一的读操作来判断造成中断请求的原因。

### 3.8 配置寄存器#3、#4 及#5

用于使能 BU-61580 很多先进的功能，包括所有的增强模式功能，即所有前一代产品 (BUS-61559 AIM-HY'er) 所没有的功能。对所有这三种模式来说，“增强模式”的使用可以使能配置寄存器#1 中不同的只读位。对 BC 模式来说，增强模式功能包括扩展的 BC 控制字和 BC 块状态字、附加的因差错停止及因状态停止等设置功能、帧自动重复、可编程消息间间隔定时、自动重试、扩展的状态字屏蔽以及在处理完任何所选择的消息之后产生中断的能力。对 RT 模式来说，增强模式功能包括扩展的 RT 块状态字、合并型 RT/可选择的消息监控器模式、RTFAIL 输出信号 (从 J 型芯片) 到 RTFLAG RT 状态字位的内部打包、各接收 (广播) 子地址的双缓存方案、交替的 (全软件可编程) RT 状态字。对 MT 模式来说，使用增强模式可以使能可选择的消息监控器的使用、使能合并型 RT/可选择的消息监控器模式、以及使能监控器触发能力。

### 3.9 数据堆栈地址寄存器

用于在可选择的字监控器模式下，指出用来存储消息的字 (第二个指令字、数据字、RT 状态字) 的共享 RAM 的当前地址的位置。

### 3.10 帧定时保持寄存器

提供当前 BC 帧中的定时保持只读指示信息，该寄存器的分辨率是 100us/LSB。

### 3.11 消息定时保持寄存器

提供 BC 帧中下一个消息启动前的定时保持只读指示信息，该寄存器的分辨率是 1us/LSB。

### 3.12 BC 帧/RT 最后一个指令/MT 触发字寄存器

在 BC 模式, 它编程 BC 帧定时, 用于帧自动重复模式。该寄存器的分辨率是 100us/LSB, 范围是 6.55 秒。在 RT 模式, 该寄存器存储 ACE RT 处理的当前 (或最近) 的 1553 指令字。在字监控器模式, 该寄存器指定一个 16 位的触发 (指令) 字, 触发字可用来启动或终止监控器、或产生中断。

### 3.13 状态字寄存器及 BIT 字寄存器

提供 BU-65170/61580 的 RT 状态及 BIT (自检测) 字的只读指示信息。

### 3.14 测试模式寄存器 0-7

这些寄存器可用来使 BU-65170/61580、或加入 BU-65170/61580 的系统的产品测试或维修测试变得方便。

| 表 2 地址影像             |    |    |    |    |    | 表 3 中断屏蔽寄存器(读/写 00h)                |         |

|----------------------|----|----|----|----|----|-------------------------------------|---------|

| 地址线                  |    |    |    |    |    | 位                                   | 描述      |

| HEX                  | A4 | A3 | A2 | A1 | A0 |                                     | 15(MSB) |

| 00                   | 0  | 0  | 0  | 0  | 0  | 中断屏蔽寄存器 (读/写)                       | 14      |

| 01                   | 0  | 0  | 0  | 0  | 1  | 配置寄存器#1 (读/写)                       | 13      |

| 02                   | 0  | 0  | 0  | 1  | 0  | 配置寄存器#2 (读/写)                       | 12      |

| 03                   | 0  | 0  | 0  | 1  | 1  | 起始/复位寄存器 (写)                        | 11      |

| 03                   | 0  | 0  | 0  | 1  | 1  | BC/RT 指令堆栈指针寄存器 (读)                 | 10      |

| 04                   | 0  | 0  | 1  | 0  | 0  | BC 控制字*/RT 子地址控制字寄存器 (读/写)          | 9       |

| 05                   | 0  | 0  | 1  | 0  | 1  | 定时标签寄存器 (读/写)                       | 8       |

| 06                   | 0  | 0  | 1  | 1  | 0  | 中断状态寄存器 (读)                         | 7       |

| 07                   | 0  | 0  | 1  | 1  | 1  | 配置寄存器#3 (读/写)                       | 6       |

| 08                   | 0  | 1  | 0  | 0  | 0  | 配置寄存器#4 (读/写)                       | 5       |

| 09                   | 0  | 1  | 0  | 0  | 1  | 配置寄存器#5 (读/写)                       | 4       |

| 0A                   | 0  | 1  | 0  | 1  | 0  | 数据堆栈地址寄存器 (读) *                     | 3       |

| 0B                   | 0  | 1  | 0  | 1  | 1  | BC 帧定时保持寄存器 (读) *                   | 2       |

| 0C                   | 0  | 1  | 1  | 0  | 0  | 下一消息 BC 定时保持寄存器 (读) *               | 1       |

| 0D                   | 0  | 1  | 1  | 0  | 1  | BC 帧定时*/ RT 最后一个指令/MT 触发字*寄存器 (读/写) | 0       |

| 0E                   | 0  | 1  | 1  | 1  | 0  | RT 状态字寄存器 (读)                       |         |

| 0F                   | 0  | 1  | 1  | 1  | 1  | RT BIT 字寄存器 (读)                     |         |

| 10                   | 1  | 0  | 0  | 0  | 0  | 测试模式寄存器 0                           |         |

| •                    |    |    |    |    |    |                                     |         |

| •                    |    |    |    |    |    |                                     |         |

| 17                   | 1  | 0  | 1  | 1  | 1  | 测试模式寄存器 7                           |         |

| 18                   | 1  | 1  | 0  | 0  | 0  | 保留                                  |         |

| •                    |    |    |    |    |    |                                     |         |

| •                    |    |    |    |    |    |                                     |         |

| 1F                   | 1  | 1  | 1  | 1  | 1  | 保留                                  |         |

| *不适用于 BU-65170/61571 |    |    |    |    |    |                                     |         |

| 表 4 配置寄存器#1 (读/写 01h) |                        |           |                  |                        |

|-----------------------|------------------------|-----------|------------------|------------------------|

| 位                     | BC 功能 (位 11-0 仅用于增强模式) | 非交替状态的 RT | 交替状态的 RT (仅增强模式) | 监控器功能 (位 12-0 仅用于增强模式) |

| 15 (MSB)              | RT/BC-MT (逻辑 0)        | 逻辑 1      | 逻辑 1             | 逻辑 0                   |

| 14                    | MT/BC-RT (逻辑 0)        | 逻辑 0      | 逻辑 0             | 逻辑 1                   |

|         |                  |                         |                  |                  |

|---------|------------------|-------------------------|------------------|------------------|

| 13      | 当前区域 B/A         | 当前区域 B/A                | 当前区域 B/A         | 当前区域 B/A         |

| 12      | 消息因差错停止          | 使能消息监控器<br>(MMT)        | 使能消息监控器<br>(MMT) | 使能消息监控器<br>(MMT) |

| 11      | 帧因差错停止           | 动态总线控制接受                | S10              | 触发字被使能           |

| 10      | 状态设置“因消息停止”      | 忙                       | S09              | 因触发启动            |

| 9       | 状态设置“因帧停止”       | 服务请求                    | S08              | 因触发结束            |

| 8       | 帧自动重复            | 子系统标志                   | S07              | 未使用              |

| 7       | 使能外部触发           | RTFLAG 仅增强模式)           | S06              | 外部触发被使能          |

| 6       | 使能内部触发           | 未使用                     | S05              | 未使用              |

| 5       | 使能消息间隔定时器        | 未使用                     | S04              | 未使用              |

| 4       | 重试被使能            | 未使用                     | S03              | 未使用              |

| 3       | 双次/单次重试          | 未使用                     | S02              | 未使用              |

| 2       | BC 被使能 (只读)      | 未使用                     | S01              | 监控器被使能 (只读)      |

| 1       | BC 帧在处理 (只读)     | 未使用                     | S00              | 监控器被触发 (只读)      |

| 0 (LSB) | BC 消息在处理<br>(只读) | RT 消息在处理 (仅<br>增强模式、只读) | RT 消息在处理<br>(只读) | 监控器激活 (只读)       |

| 表 5 配置寄存器#2 (读/写 02h) |                  | 表 6 起始/复位寄存器 (写 03h) |             |

|-----------------------|------------------|----------------------|-------------|

| 位                     | 描述               | 位                    | 描述          |

| 15 (MSB)              | 增强型中断            | 15 (MSB)             | 保留          |

| 14                    | 逻辑 0             | •                    | •           |

| 13                    | 使能忙查询表           | •                    | •           |

| 12                    | 使能 RX SA 双缓存器    | •                    | •           |

| 11                    | 写覆盖无效数据          | 7                    | 保留          |

| 10                    | 禁止 256 字边界       | 6                    | BC/MT 因消息停止 |

| 9                     | 定时标签分辨率 2 (TTR2) | 5                    | BC 因帧停止     |

| 8                     | 定时标签分辨率 1 (TTR1) | 4                    | 定时标签测试时钟    |

| 7                     | 定时标签分辨率 0 (TTR0) | 3                    | 定时标签复位      |

| 6                     | 接收同步指令而清除定时标签    | 2                    | 中断复位        |

| 5                     | 接收同步指令而装载定时标签    | 1                    | BC/MT 起始    |

| 4                     | 中断状态自动清除         | 0 (LSB)              | 复位          |

| 3                     | 电平/脉冲中断请求        |                      |             |

| 2                     | 清除服务请求           |                      |             |

| 1                     | 增强型 RT 存储器管理     |                      |             |

| 0 (LSB)               | 分离广播数据           |                      |             |

| 表 7 BC/RT 指令堆栈指针寄存器 (读 03H) |           | 表 10 定时标签寄存器 (读/写 05H) |         |

|-----------------------------|-----------|------------------------|---------|

| 位                           | 描述        | 位                      | 描述      |

| 15 (MSB)                    | 指令堆栈指针 15 | 15 (MSB)               | 定时标签 15 |

| •                           | •         | •                      | •       |

| •                           | •         | •                      | •       |

|         |          |         |        |

|---------|----------|---------|--------|

| •       | •        | •       | •      |

| 0 (LSB) | 指令堆栈指针 0 | 0 (LSB) | 定时标签 0 |

表 8 BC 控制字寄存器 (读/写 04H, 仅 BU-61580)

| 位       | 描述             |

|---------|----------------|

| 15(MSB) | 保留             |

| 14      | 屏蔽 M.E. (消息差错) |

| 13      | 屏蔽服务请求位        |

| 12      | 屏蔽子系统忙位        |

| 11      | 屏蔽子系统标志位       |

| 10      | 屏蔽终端标志位        |

| 9       | 屏蔽保留位          |

| 8       | 使能重试           |

| 7       | 总线通道 A/B       |

| 6       | 离线自检           |

| 5       | 屏蔽广播位          |

| 4       | 使能 EOM 中断      |

| 3       | 1553A/B 选择     |

| 2       | 模式码格式          |

| 1       | 广播格式           |

| 0 (LSB) | RT-to-RT 格式    |

表 11 中断状态寄存器 (读 06H)

| 位        | 描述                     |

|----------|------------------------|

| 15 (MSB) | 主中断                    |

| 14       | RAM 奇偶错误               |

| 13       | BC/RT 发送器暂停            |

| 12       | BC/RT 指令堆栈滚动结束         |

| 11       | MT 指令堆栈滚动结束            |

| 10       | MT 数据堆栈滚动结束            |

| 9        | HS(握手)失败               |

| 8        | BC 重试                  |

| 7        | RT 地址奇偶错误              |

| 6        | 定时标签滚动结束               |

| 5        | RT 循环缓存器滚动结束           |

| 4        | RT 子地址控制字 EOM          |

| 3        | BC 帧结尾                 |

| 2        | 格式错误                   |

| 1        | BC 状态设置/RT 模式码/MT 方式触发 |

| 0 (LSB)  | 消息结尾 (EOM)             |

表 9 RT 子地址控制字 (读/写 04H)

| 位       | 描述                  |

|---------|---------------------|

| 15(MSB) | RX: 使能双缓存           |

| 14      | TX: EOM 中断          |

| 13      | TX: 循环缓存中断          |

| 12      | TX: 存储器管理 2 (MM2)   |

| 11      | TX: 存储器管理 1 (MM1)   |

| 10      | TX: 存储器管理 0 (MM0)   |

| 9       | RX: EOM 中断          |

| 8       | RX: 循环缓存中断          |

| 7       | RX: 存储器管理 2 (MM2)   |

| 6       | RX: 存储器管理 1 (MM1)   |

| 5       | RX: 存储器管理 0 (MM0)   |

| 4       | BCST: EOM 中断        |

| 3       | BCST: 循环缓存中断        |

| 2       | BCST: 存储器管理 2 (MM2) |

| 1       | BCST: 存储器管理 1 (MM1) |

| 0 (LSB) | BCST: 存储器管理 0 (MM0) |

表 12 配置寄存器#3 (读/写 07H)

| 位        | 描述                  |

|----------|---------------------|

| 15 (MSB) | 使能增强模式              |

| 14       | BC/RT 指令堆栈容量 1      |

| 13       | BC/RT 指令堆栈容量 0      |

| 12       | MT 指令堆栈容量 1         |

| 11       | MT 指令堆栈容量 0         |

| 10       | MT 数据堆栈容量 2         |

| 9        | MT 数据堆栈容量 1         |

| 8        | MT 数据堆栈容量 0         |

| 7        | 禁止非法化               |

| 6        | 越权模式 T/R 错误         |

| 5        | 使能交替的状态字            |

| 4        | 禁止非法的 RX 传送         |

| 3        | 禁止忙 RX 传送           |

| 2        | 使能 RTFAIL-RTFLAG 打包 |

| 1        | 使能 1553A 模式码        |

| 0 (LSB)  | 增强型模式码处理            |

表 13 配置寄存器#4 (读/写 08H)

| 位       | 描述          |

|---------|-------------|

| 15(MSB) | 使能外部 BIT 字  |

| 14      | 若忙则禁止 BIT 字 |

| 13      | 模式指令越权忙     |

表 16 BC 帧定时保持寄存器 (读/写 0BH)

| 位       | 描述          |

|---------|-------------|

| 15(MSB) | BC 帧定时保持 15 |

| •       | •           |

| •       | •           |

|         |                            |                             |                |

|---------|----------------------------|-----------------------------|----------------|

| 12      | 使能扩展的 BC 控制字               | •                           | •              |

| 11      | 广播屏蔽使能/XOR                 | 0 (LSB)                     | BC 帧定时保持 0     |

| 10      | 若 1553A 位与消息差错位都为逻辑 1, 则重试 |                             | 注: 分辨率=1us/LSB |

| 9       | 如果状态设置则重试                  |                             |                |

| 8       | 第一次重试交替/同一总线               | 表 17 BC 消息定时保持寄存器 (读/写 0CH) |                |

| 7       | 第二次重试交替/同一总线               | 位                           | 描述             |

| 6       | 若消息差错且无数据, 则响应也有效          | 15(MSB)                     | BC 消息定时保持 15   |

| 5       | 忙且无数据, 则响应也有效              | •                           | •              |

| 4       | MT 标签间隔选项                  | •                           | •              |

| 3       | 和配置寄存器#5 一起锁存 RT 地址        | •                           | •              |

| 2       | 测试模式 2                     | 0 (LSB)                     | BC 消息定时保持 0    |

| 1       | 测试模式 1                     |                             | 注: 分辨率=1us/LSB |

| 0 (LSB) | 测试模式 0                     |                             |                |

| 表 14 配置寄存器#5 (读/写 09H)                          |                                | 表 18 BC 帧定时/RT 最后一个指令/MT 触发字寄存器 (读/写 0DH) |          |

|-------------------------------------------------|--------------------------------|-------------------------------------------|----------|

| 位                                               | 描述                             | 位                                         | 描述       |

| 15 (MSB)                                        | 12MHz 时钟选择                     | 15 (MSB)                                  | 位 15     |

| 14                                              | 逻辑 0                           | •                                         | •        |

| 13                                              | 外部 TX 禁止 A, BU65170/61580×6 只读 | •                                         | •        |

| 12                                              | 外部 TX 禁止 B, BU65170/61580×6 只读 | •                                         | •        |

| 11                                              | 使能扩展的过零点                       | 0 (LSB)                                   | 位 0      |

| 10                                              | 响应暂停选择 1                       |                                           |          |

| 9                                               | 响应暂停选择 0                       | 表 19 RT 状态字寄存器 (读/写 0EH)                  |          |

| 8                                               | 使能间隔检查                         | 位                                         | 描述       |

| 7                                               | 禁止广播                           | 15 (MSB)                                  | 逻辑 0     |

| 6                                               | RT 地址锁存/透明 (注)                 | 14                                        | 逻辑 0     |

| 5                                               | RT 地址 4                        | 13                                        | 逻辑 0     |

| 4                                               | RT 地址 3                        | 12                                        | 逻辑 0     |

| 3                                               | RT 地址 2                        | 11                                        | 逻辑 0     |

| 2                                               | RT 地址 1                        | 10                                        | 消息差错     |

| 1                                               | RT 地址存 0                       | 9                                         | 测试手段     |

| 0 (LSB)                                         | RT 地址奇偶位                       | 8                                         | 服务请求     |

| 注: 只读: 65170/61580 逻辑 0, 65171/61581/61586 逻辑 1 |                                | 7                                         | 保留       |

| 表 15 监控器数据堆栈地址寄存器 (读/写 0AH)                     |                                | 6                                         | 保留       |

| 位                                               | 描述                             | 5                                         | 保留       |

| 15(MSB)                                         | 监控器数据堆栈地址 15                   | 4                                         | 广播指令接收   |

| •                                               | •                              | 3                                         | 忙        |

| •                                               | •                              | 2                                         | 子系统标志    |

| •                                               | •                              | 1                                         | 动态总线控制接受 |

| 0 (LSB)                                         | 监控器数据堆栈地址 0                    | 0 (LSB)                                   | 终端标志     |

| 表 20 RT BIT 字寄存器 (读 0FH) |          | 表 21 BC 模式块状态字 |        |

|--------------------------|----------|----------------|--------|

| 位                        | 描述       | 位              | 描述     |

| 15(MSB)                  | 发送器暂停    | 15 (MSB)       | EOM    |

| 14                       | 环路测试失败 B | 14             | SOM    |

| 13                       | 环路测试失败 A | 13             | 通道 B/A |

|         |                  |         |             |

|---------|------------------|---------|-------------|

| 12      | 握手失败             | 12      | 错误标志        |

| 11      | 发送器关闭 B          | 11      | 状态设置        |

| 10      | 发送器关闭 A          | 10      | 格式错误        |

| 9       | 禁止终端标志           | 9       | 无响应暂停       |

| 8       | 通道 B/A           | 8       | 环路测试失败      |

| 7       | 高端字计数            | 7       | 屏蔽的状态设置     |

| 6       | 低端字计数            | 6       | 重试计数 1      |

| 5       | 接收的同步不正确         | 5       | 重试计数 0      |

| 4       | 接收的奇偶/曼彻斯特错误     | 4       | 正确的数据块传送    |

| 3       | RT-RT 间隔/同步/地址错误 | 3       | 错误的状态地址/无间隔 |

| 2       | RT-RT 无响应错误      | 2       | 字计数错误       |

| 1       | RT-RT 第二个指令字错误   | 1       | 同步类型错误      |

| 0 (LSB) | 指令字内容错误          | 0 (LSB) | 无效的字        |

表 22 RT 模式块状态字

表 24 消息监控器模式块状态字

| 位       | 描述               | 位        | 描述               |

|---------|------------------|----------|------------------|

| 15(MSB) | EOM              | 15 (MSB) | EOM              |

| 14      | SOM              | 14       | SOM              |

| 13      | 通道 B/A           | 13       | 通道 B/A           |

| 12      | 错误标志             | 12       | 错误标志             |

| 11      | RT-RT 格式         | 11       | RT-RT 传送         |

| 10      | 格式错误             | 10       | 格式错误             |

| 9       | 无响应暂停            | 9        | 无响应暂停            |

| 8       | 环路测试失败           | 8        | 正确的数据块传送         |

| 7       | 数据堆栈滚动结束         | 7        | 数据堆栈滚动结束         |

| 6       | 非法的指令字           | 6        | 保留               |

| 5       | 字计数错误            | 5        | 字计数错误            |

| 4       | 错误的数据同步          | 4        | 错误的数据同步          |

| 3       | 无效的字             | 3        | 无效的字             |

| 2       | RT-RT 间隔/同步/地址错误 | 2        | RT-RT 间隔/同步/地址错误 |

| 1       | RT-RT 第二个指令字错误   | 1        | RT-RT 第二个指令错误    |

| 0 (LSB) | 指令字内容错误          | 0 (LSB)  | 指令字内容错误          |

表 23 字监控器识别字

| 位       | 描述   | 6       | 该 RT     |

|---------|------|---------|----------|

| 15(MSB) | 间隔定时 | 5       | 广播       |

| •       | •    | 4       | 错误       |

| •       | •    | 3       | 指令/数据    |

| •       | •    | 2       | 通道 B/A   |

| 8       | 间隔定时 | 1       | 邻接的数据/间隔 |

| 7       | 字标志  | 0 (LSB) | 模式码      |

注：表 21 到 24 不是寄存器，但它们是 RAM 中存储的字

#### 4 总线控制器 (BC) 结构

BU-61580 的 BC 协议能完成所有的 MIL-STD-1553B 消息格式，利用 BC 控制字中的位及各消息指令字中的 T/R 位，基于消息—消息的消息格式是可编程的。BC 控制字允许在各消息基础上对 1553 消息格式、1553A/B 类型的 RT、总线通道、自检、以及状态字屏蔽分别进行指定，另外，对各消息来说，可以使能或禁止自动重试和/或中断请求。BC 可以完成 MIL-STD-1553B 需要的所有的错误检查，包括响应时间的有效性、同步类型及同步编码、曼彻斯特 II 编码、

奇偶、位计数、字计数、状态字 RT 地址区域、以及各种 RT-to-RT 传送错误。BU-61580 的响应暂停值可被编程为 18、22、50 或 130us，长的响应暂停时间值可以使能较大长度总线的操作和/或重复器的应用。

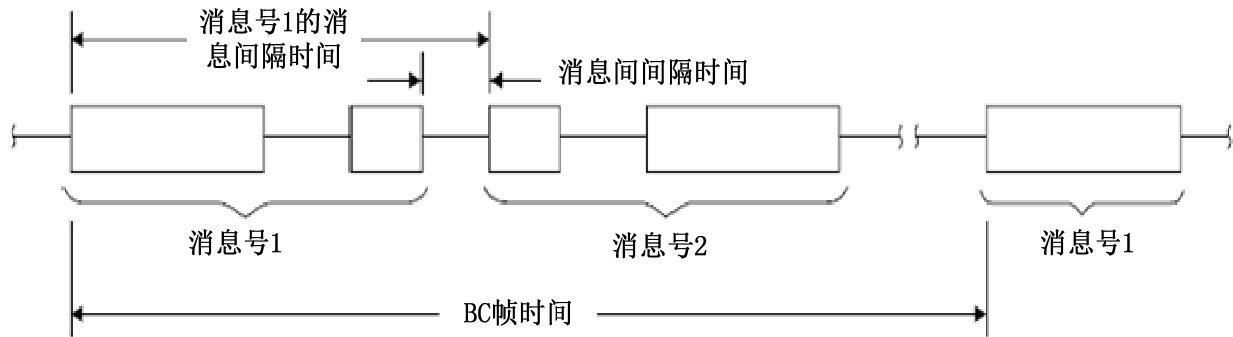

图 2 示出了 BC 的消息间隔定时和帧定时。在没有处理器介入的情况下，通过编程，BU-61580 最多可以处理 512 个消息的 BC 帧。通过编程，可以选择对单个帧的操作方式、也可以选择对自动重复帧的操作方式。在自动重复模式，对帧重复率的控制，可以通过对 BC 帧定时器编程的方式内部进行，也可以利用外部触发输入方式进行。通过编程，内部 BC 帧定时可以以 100us 为增量单位增加到 6.55 秒。另外，对 BC 帧定时来说，在单个消息的基础上，就可对消息间隔定时（从当前消息开始时开始测量到下一个顺序的消息开始时测量停止）进行编程。两个连续的消息之间的时间间隔可以被编程，以 1us 为增量单位，最高到 65.5ms。

图 2 BC 消息间隔及帧定时

#### 4.1 BC 存储器组织

表 25 说明了 BC 模式典型的存储器影像，需要重点指出的是：对在标准 BC 模式中的 BU-61580 而言，唯一固定的位置是两个堆栈指针位置（地址位置 0100（16 进制）及 0104）及两个消息计数位置（0101 及 0105）。在增强型 BC 模式中，使能帧自动重复模式需要额外保留 4 个存储器位置以备使用，这些位置用于 2 个初始的堆栈指针位置（地址 102（16 进制）及 106）以及初始的消息计数位置（103 和 107）。用户可以自由地在 64K（内部 4K）共享 RAM 地址空间中的任何其它地方放置堆栈及 BC 消息块。

表 25 典型的 BC 存储器组织（所列为 4K RAM）

| 地址 (16 进制) | 描述                        | 地址 (16 进制) | 描述                        |

|------------|---------------------------|------------|---------------------------|

| 0000-0OFF  | 堆栈 A                      | 0107       | 初始的消息计数 B（注）<br>(自动帧重复模式) |

| 0100       | 堆栈指针 A（固定位置）              | 0108-012D  | 消息块 0                     |

| 0101       | 消息计数 A（固定位置）              | 012E-0153  | 消息块 1                     |

| 0102       | 初始的堆栈指针 A（注）<br>(自动帧重复模式) | 0154-0179  | 消息块 2                     |

| 0103       | 初始的消息计数 A（注）<br>(自动帧重复模式) | ⋮          | ⋮                         |

| 0104       | 堆栈指针 B                    | 0E06-0E0F  | 消息块 93                    |

| 0105       | 消息计数 B                    | 0EFC-0EFF  | 未使用                       |

| 0106       | 初始的堆栈指针 B（注）<br>(自动帧重复模式) | 0F00-0FFF  | 堆栈 B                      |

注：只用于在帧自动重复被使能情况下的增强型 BC 模式。

为描述简单起见，假定了对表 25 中每一个消息块典型的 BC 存储器影像来说，BC 消息最大长度的位置。对一个 32 个数据字的 RT-to-RT 传送来说，BC 消息块的最大值是 38 个字，即：控制字+2 个指令字+环路返回字+2 个状态字+32 个数据字。但是，需注意，这是假定 256 字界限被禁止情况下的例子。

#### 4.2 BC 存储器管理

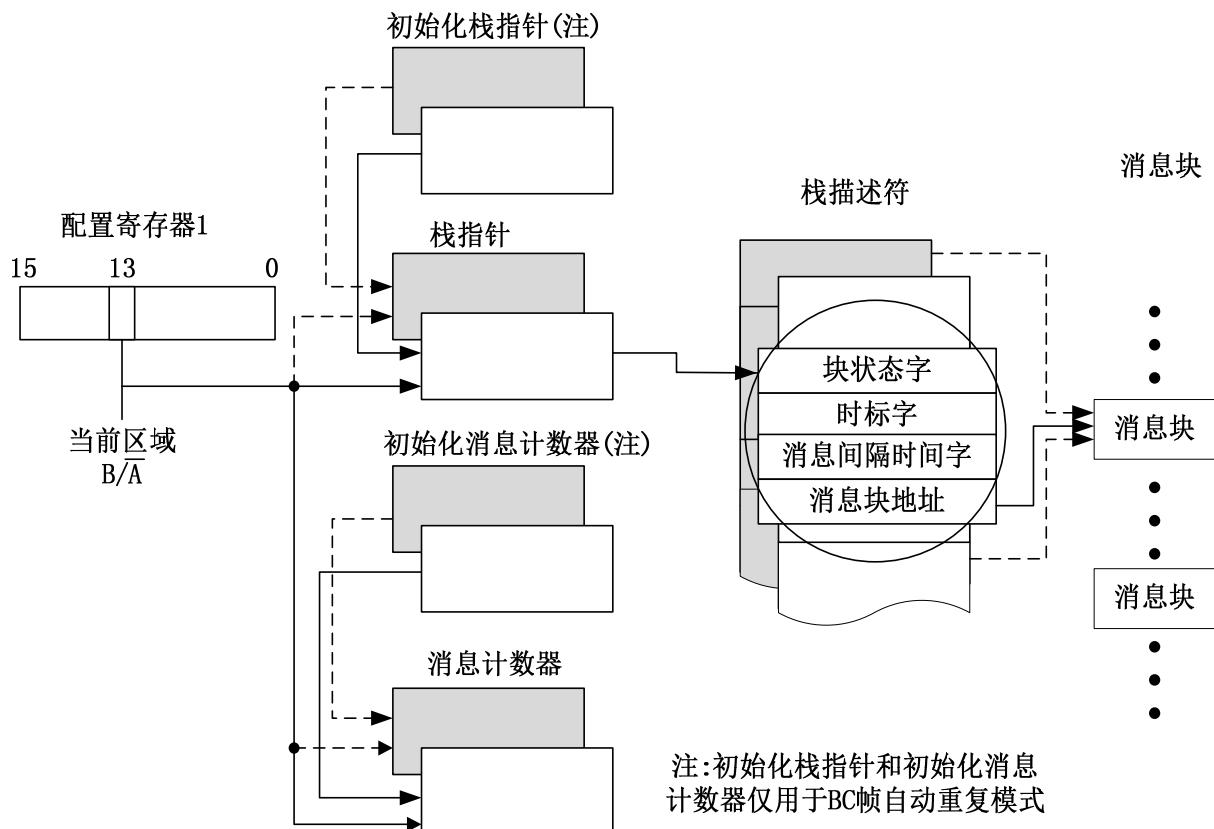

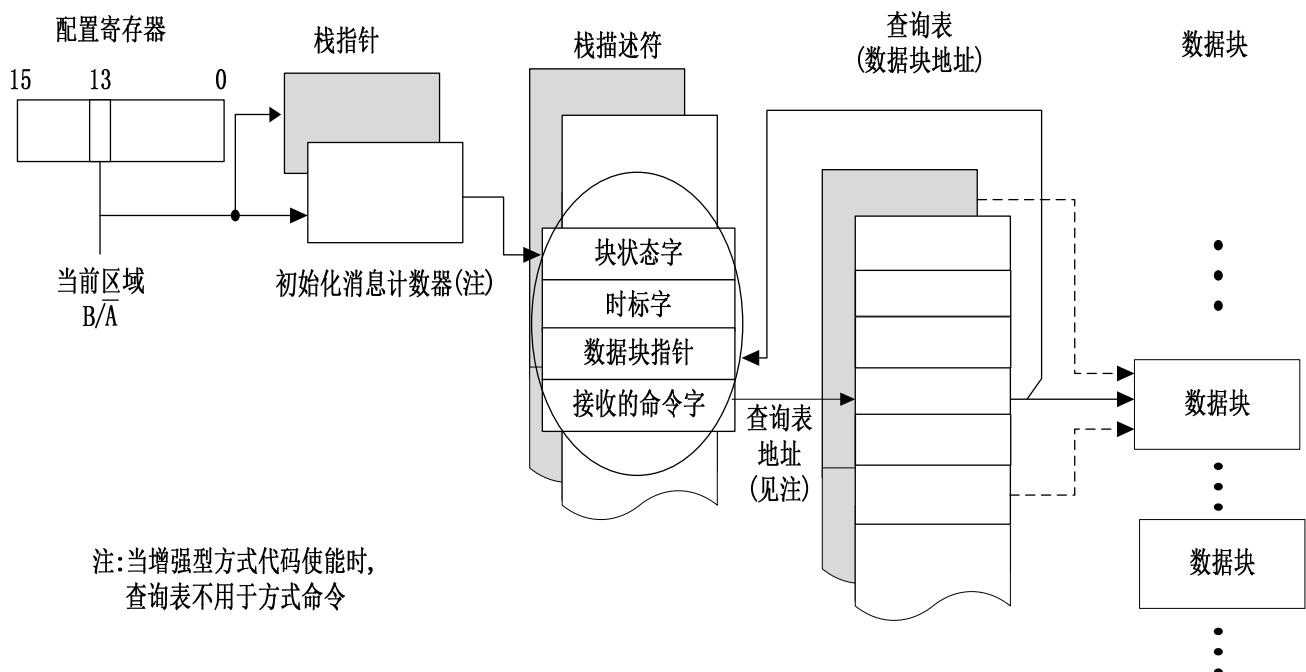

图 3 说明了 BU-61580 的 BC 存储器管理方案，BC 存储器管理的一个特点是总体的双缓存机构，这样就为不同的 BC 模式数据结构（堆栈指针位置及消息计数器位置、描述器堆栈区域、以及 BC 消息块）提供了 2 套设置。配

置寄存器#1 的第 13 位负责选择当前的激活区域。在任何时刻, BU-61580 的内部 1553 存储器管理逻辑都可以唯一地访问“激活”区域中不同的数据结构。图 3 分别用“非阴影”及“阴影”区域描绘出了“激活”及“非激活”区域,但是,在任何时刻,“激活”及“非激活”区域都可被主处理器访问。在多数情况下,主处理器访问“非激活”区域,同时 1553 总线处理“激活”区域中的消息。

通过编程,BC 可发送最多可达 512 个消息的多消息帧。利用共享 RAM 中的“激活区域消息计数”位置(该位置由主处理器初始化),可以通过编程确定要处理的消息的数量。另外,主处理器必须初始化另一个位置,即:“激活区域堆栈指针”。对每一个要被处理的消息来说,堆栈指针都要参考共享 RAM 堆栈区域中 4 个字的消息块描述器。BC 堆栈的容量可以通过编程选择为: 256、512、1024 或 2048 个字。

在 BC 帧自动重复模式,初始的堆栈指针位置及初始的消息计数器位置必须在处理第一帧前被主机装载,单帧模式则不需使用这两个位置。

对各消息来说,BC 块描述器的第 3 及第 4 个字分别是消息间间隔定时及消息块地址。在开始处理消息前,这两个存储器位置必须被主机写入。消息间间隔定时是可选项,块地址指针指出了每一个消息块的起始位置,每一个 BC 消息块的第一个字是 BC 控制字。

在每一个消息的开始及结尾,“块状态字”及“定时标签字”都要写到堆栈中的消息块描述器中。块状态字包含以下内容:指出消息是正在处理还是已经完成、总线通道、状态置位、响应暂停、重试计数、状态地址失配、环路测试(在线自检)失败、以及其它错误情况。表 21 说明了 BC 块状态字的位影像。16 位的定时标签字能反映内部定时标签寄存器的当前内容。该可读/写寄存器能工作在所有 3 种模式下,其分辨率是可编程的,从 2 到 64us/LSB。另外,定时标签寄存器可使用外部时钟。

图 3 BC 存储器管理

#### 4.3 BC 消息块格式及 BC 控制字

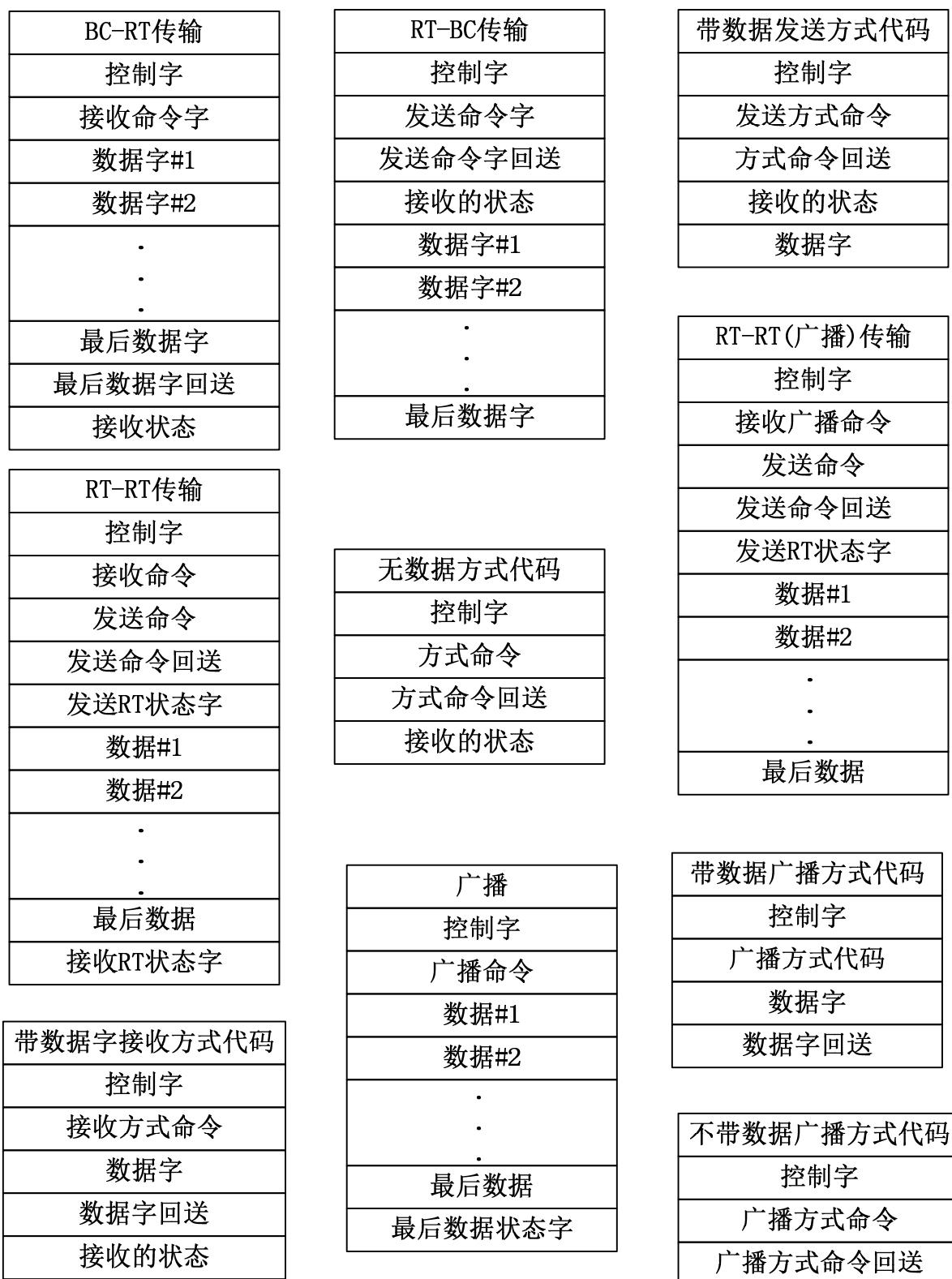

在 BC 模式, BU-61580 支持所有的 MIL-STD-1553 消息格式,对每一个 1553 消息格式来说, BU-61580 管理 BC 消息块中特定的字序列,包括控制字的位置、指令字的位置以及(被发送的)将由 BC 协议逻辑从 RAM 中读出的数据字的位置。另外,必须定位随后紧邻的位置,以便存储接收到的环路返回字、RT 状态字及数据字。图 4 说明了对不同的 MIL-STD-1553 消息格式来说 BC 消息块的组织方式。注意对所有的消息格式来说,BC 控制字位于该消息块的第一个位置。

对每一个 BC 消息块格式来说,块中的第一个字是 BC 控制字,BC 控制字不在 1553 总线上发送。取而代之的是,

它包含选择激活的总线及消息格式、使能离线自检、屏蔽状态字的位、使能重试及中断、以及指出 MIL-STD-1553A 或 MIL-STD-1553B 差错处理等位。BC 控制字的位影像及定义在表 8 中作了说明。

BC 控制字之后是要被发送的指令字，再之后是第二个指令字（对一个 Rt-to-Rt 传送来说），再之后是要被发送的数据字（对接收指令来说）。最后一个要被发送的字之后的位置是为环路返回字保留的，环路返回字是一种在线自检功能，环路返回字之后的位置是为接收到的状态字及数据字（对发送指令而言）保留的。

图 4 BC 消息块格式

#### 4.4 自动重试

BU-61580 BC 可以完成自动的消息重试功能。当被使能时，重试就会发生，它紧跟在响应暂停或格式差错情况

发生之后。作为增加的选项，当消息差错状态字被 1553A RT 置位或当“状态设置”情况发生时，随后重试就会被使能。对一个失败的消息来说，或者一次、或者两次消息重试就会发生，总线通道（同一个或另外一个）对第一次及第二次重试尝试来说是可独立编程的。在单个消息基础上，可使能或禁止重试。

#### 4.5 BC 中断

BC 中断可因堆栈滚动结束、重试、消息结尾（全部的）、消息结尾（在与单个消息的 BC 控制字的连接中）、响应暂停、消息差错、BC 帧结尾以及状态设置等事件的发生而被中断屏蔽寄存器所使能。在单个消息基础上，利用 BC 控制字，可编程“状态设置”的定义，它允许屏蔽（“关注/不关注”）各 RT 状态字的位。

### 5 RT 结构

BU-65170/61580 RT 协议的设计意味着 DDC 的 1553 RT 第五代产品的启用，ACE RT 一个显著的特点是它的真正多协议功能，包括为支持 1553A、不同的 McAir 协议、以及 MIL-STD-1553B Notice2 的可编程选项。假定兼容所有的 1553 协议，则 BU-65170/61580 RT 的响应时间是 2 到 5us 的死时间（4 到 7 微秒/1553B）。BU-65170/61580 增加的多协议功能包括了对 RT 状态字及“自检测”(BIT)字的全软件控制。另外，对 1553B 来说，通过 BU-65170/61580 协议逻辑，这些字可以实时地被通过公式所确定。

BU-65170/61580 RT 协议的设计可以完成所有 MIL-STD-1553B 消息格式及双冗余模式码，该设计主要基于为与 MIL-STD-1553B 兼容而已经通过 SEAFAC 测试的上一代产品。ACE RT 能完成综合错误检测、字及格式的有效性、以及不同的 RT-to-RT 传送错误的检测。BU-65170/61580 RT 另一些重要功能包括一套中断事件、内部指令非法化、以及通过子地址可编程的忙。

#### 5.1 RT 存储器组织

表 26 说明了 RT 模式下 BU-61580 典型的存储器影像。像在 BC 模式下那样，两个堆栈指针位于共享 RAM 地址空间中的固定位置：区域 A 堆栈指针的地址是 0100（16 进制），区域 B 堆栈指针的地址是 0104。除了堆栈指针外，对 RT 模式来说，还有其它几个 ACE 地址空间区域被指定为固定位置。所有 RT 模式的操作都要有区域 A 查询表及区域 B 查询表，还有几个固定位置是为可任选的功能选项分配的，这些功能选项为：指令非法化查询表、模式码选择中断表、模式码数据表、以及忙位查询表。需指出的是，任何未被使能的可任选的固定位置都可用于通常目的，即存储（数据块）。

RT 查询表可以为各 Tx/Rx/Bcst — 子地址提供将数据块影像到 RAM 区域中的机制，对区域 A，该表的地址范围是 0140 到 01BF，对区域 B，该表的地址范围是 01C0 到 023F，RT 查询表包含子地址控制字及各数据块指针。如果使用它的话，地址范围 0300-03FF 可以被指定为 RAM 的非法化部分，实际的堆栈 RAM 区域和各数据块可以被放置在共享 RAM 地址空间中任何非固定的区域。

#### 5.2 RT 存储器管理

ACE 系列产品一个显著的特点就是其 RT 存储器管理结构所具有的灵活性。RT 结构允许在子地址基础上对每一个发送、接收、或广播子地址进行存储器管理方案编程，还有，为了和 MIL-STD-1553B Notice2 兼容，BU-65170/61580 还提供了一个选项，可以将从广播消息中接收到的数据和从非广播消息中接收到的数据分离开。

除了支持全部的双缓存方案（就像在 BC 模式中的那样），ACE RT 还提供了一对 128 个字的查询表用于存储器管理控制，在子地址的基础上，它们是可编程的（参见表 27）。这些 128 个字的表包含有 32 个字的表，用于发送消息指针及接收消息指针。第三个可选项也是查询表，用于广播消息指针，以便在需要的情况下，与 MIL-STD-1553B Notice2 兼容。

每一个 RT 查询表的第四部分都存储了 32 个子地址控制字（参见表 9、表 28）。各子地址控制字可用来为每一个发送、接收、以及广播（可任选的）子地址选择 RT 存储器管理选项以及中断方案。

对每一个发送子地址来说，都有两个可能的存储器管理方案：(1) 单消息；(2) 循环缓存。对每一个接收（以及可任选的广播）子地址来说，都有三个可能的存储器管理方案：(1) 单消息；(2) 双缓存；(3) 循环缓存。对每一个发送、接收、以及广播子地址来说，通过相应的子地址控制字，可分别对两个中断事件进行编程：(1) 在每个消息送到子地址后；(2) 在每次循环缓存滚动结束后。在 RAM 中的另一个表可用来在所选择的模式码消息之后使能中断。

当对一个给定的子地址使用循环缓存方案时，可以通过子地址控制字的 3 个位（见表 28）对循环缓存器的容量进行编程，循环缓存器容量的选项是 128、256、1024、2048、4096 及 8192 个数据字。

| 表 26 典型 RT 存储器影像 (对 4KRAM) |                 | 表 27 查询表                   |      |                 |             |

|----------------------------|-----------------|----------------------------|------|-----------------|-------------|

| 地址 (16 进制)                 | 描述              | 区域 A                       | 区域 B | 描述              | 注释          |

| 0000-00FF                  | 堆栈 A            | 0140                       | 01C0 | Rx (/Bcst)_SA0  | 接收 (/广播)查询表 |

| 0100                       | 堆栈指针 A (固定位置)   | ⋮                          | ⋮    | ⋮               |             |

| 0101-0103                  | 保留              | 015F                       | 01DF | Rx (/Bcst)_SA31 |             |

| 0104                       | 堆栈指针 B (固定位置)   | 0160                       | 01E0 | Tx_SA0          | 发送查询表       |

| 0105-0107                  | 保留              | ⋮                          | ⋮    | ⋮               |             |

| 0108-010F                  | 模式码选择中断表 (固定区域) | 017F                       | 01FF | Tx_SA31         |             |

| 0110-013F                  | 模式码数据 (固定区域)    | 0180                       | 0200 | Bcst_SA0        | 广播          |

| 0140-01BF                  | 查询表 A (固定区域)    | ⋮                          | ⋮    | ⋮               | 查询表         |

| 01C0-023F                  | 查询表 B (固定区域)    | 019F                       | 021F | Bcst_SA31       | 可任选         |

| 0240-0247                  | 忙位查询表 (固定区域)    | 01A0                       | 0220 | SACW_SA0        | 子地址控制字      |

| 0248-025F                  | 未使用             | ⋮                          | ⋮    | ⋮               | 查询表         |

| 0260-027F                  | 数据块 0           | 01BF                       | 023F | SACW_SA31       | (可任选)       |

| 0280-02FF                  | 数据块 1-4         | 表 28 子地址控制字 (存储器管理子地址缓存方案) |      |                 |             |

| 0300-03FF                  | 指令非法化表 (固定区域)   | MM2                        | MM1  | MM0             | 描述          |

| 0400-041F                  | 数据块 5           | 0                          | 0    | 0               | 单消息或双缓存     |

| 0420-043F                  | 数据块 6           | 0                          | 0    | 1               | 128-字       |

| ⋮                          | ⋮               | 0                          | 1    | 0               | 256-字       |

| ⋮                          | ⋮               | 0                          | 1    | 1               | 512-字       |

| ⋮                          | ⋮               | 1                          | 0    | 0               | 1024-字      |

| 0FE0-0FFF                  | 数据块 100         | 1                          | 0    | 1               | 2048-字      |

|                            |                 | 1                          | 1    | 0               | 4096-字      |

|                            |                 | 1                          | 1    | 1               | 8192-字      |

### 5.3 单消息模式

图 5 说明了 RT 单消息存储器管理方案, 当 BU-65170/61580 工作在“AIM-HY”(缺省)模式时, 对**所有的**发送、接收及广播子地址来说, 都可完成单消息方案。在单消息模式(也适于双缓存及循环缓存模式)下, 配置寄存器#1 的第 13 位可控制一个整体的双缓存方案, 这要在图中所示的不同的存储器结构: 堆栈指针(固定地址)、描述器堆栈(用户定义地址)、RT 查询表(固定地址)、以及数据字块(用户定义地址)中的两个设置中做出选择。图 5、6 及 6 分别用非阴影及阴影区域描绘出了“激活”及“非激活”区域。

如图所示, ACE 在各消息的消息描述器(在堆栈中)的第 4 个位置存储接收到的每一个消息中的指令字。T/R 位、子地址区域、以及(可任选的)广播/自有地址可作为激活区域查询表的索引, 并为当前消息定位数据块指针, 于是 BU-65170/61580 RT 存储器管理逻辑就可以访问数据块指针以便为当前消息确定数据字块的起始地址, RT 数据字块的最大值是 32 个字。

对单消息模式中的一个特定的子地址来说, 对接收/广播子地址而言有数据块内容的写覆盖; 对发送子地址而言有读覆盖。在单消息模式中, 对同一子地址访问多个数据块是可能的, 但这需要主机参与, 以更新各查询表指针。

为完成数据打包子地址, 就像 MIL-STD-1553B Notice2 所要求的那样, 对打包子地址而言, 必须使用单消息方案, Notice2 建议子地址 30 作为打包子地址。

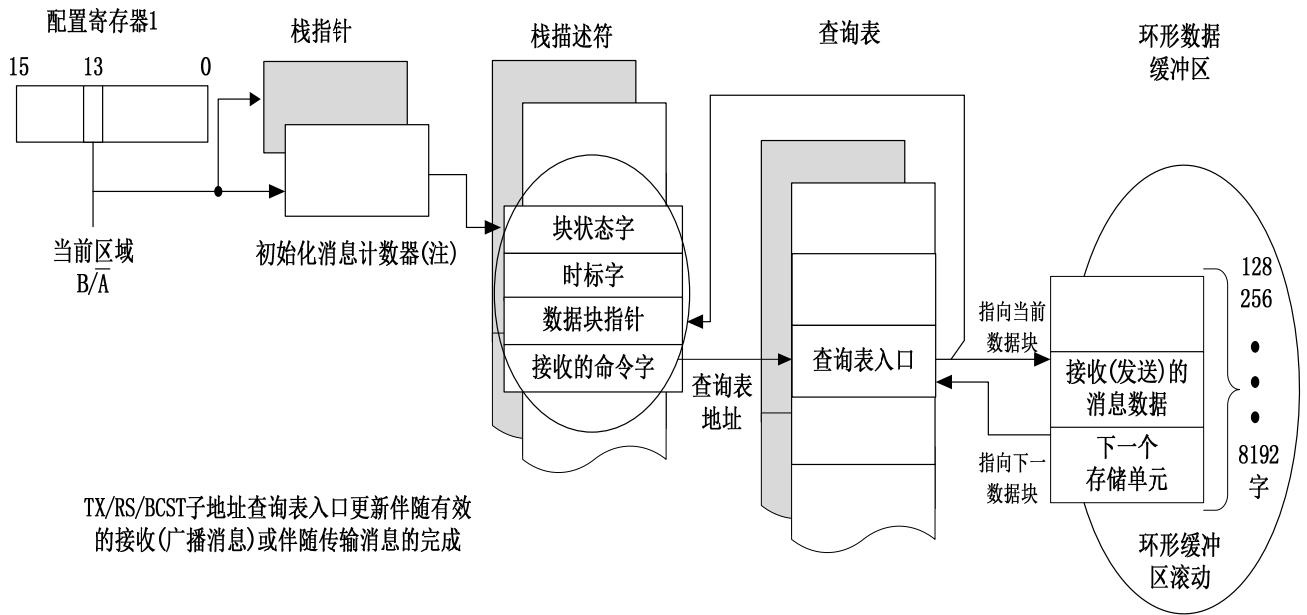

### 5.4 循环缓存模式

图 6 说明了 RT 循环缓存存储器管理方案, 循环缓存模式方便了海量数据的传送。RT 循环缓存器的容量由图中右侧示出, 并可通过各子地址控制字对其编程, 从 128 到 8192 个字(在平均功率为 2 的情况下)。像单消息模式一样, 主处理器在开始时要装载各查询表入口。在每一个消息的开始, ACE 在位于 RAM 堆栈区域中的各消息块描述器的第 3 个位置存储查询表入口, 像单消息模式一样。ACE 向(或从)循环缓存器传送接收或发送数据字, 数据字的起始位置由查询表指针确定。

在有效(或可任选的无效)消息的结尾, 查询表入口的值更新到被访问的当前消息最后一个地址的下一个位置, 结果, 指向同一 Tx/Rx (/Bcst) 子地址的下一个消息的数据字将从循环缓存器中下一个紧邻的地址块中被访问出来。

作为推荐选项，在一个无效接收（或广播）消息之后，可通过编程不更新查询表指针，这样，就允许 1553 总线控制器重试该失败的消息，形成有效（重试）数据写覆盖无效数据的结果，这也消除了 RT 主处理器的普通开支。当指针到达循环缓存器的底部边界（在 BU-65170/61580 地址空间中，字边界为 128, 256, ---8192 个字）时，指针将指向循环缓存器的顶部边界，如图 6 所示。

#### 5.4.1 完成海量数据传送

使用循环缓存器方案传送海量数据是比较理想的，即倍乘来自/发往同一子地址的消息，若这样做，建议使能循环缓存中断请求。这样做时，发往被选择子地址的海量消息的例行传送，**包括错误以及重试**，对 RT 主处理器来说就是透明的，除了按惯例在海量传送开始前初始化子地址的查询表指针外，还可配置 BU-65170/61580，使它仅在已经接收到指向指定子地址的所期望数量的有效数据字之后发出一个中断请求。

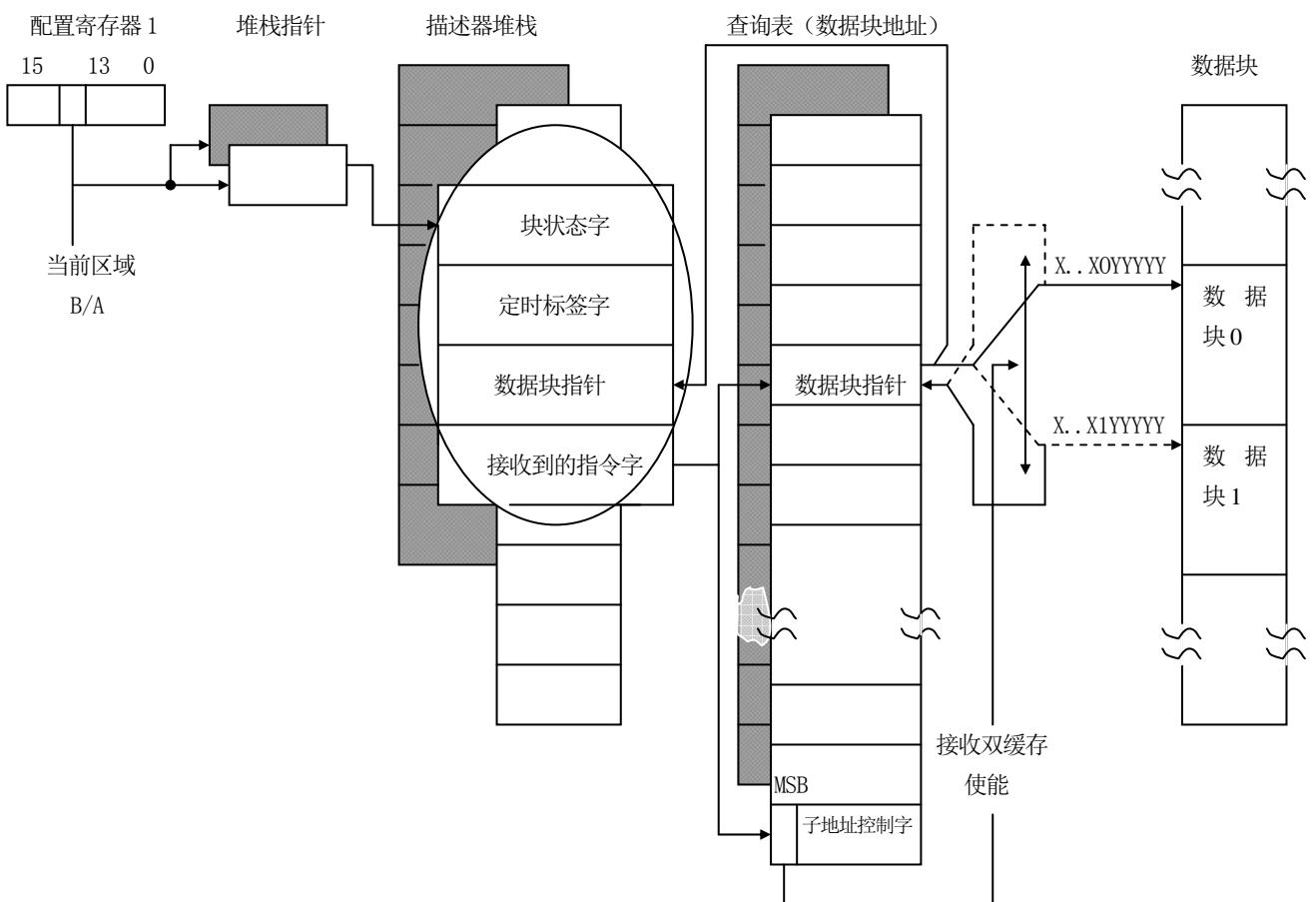

#### 5.5 子地址双缓存模式

对接收（及广播）子地址来说，BU-65170/61580 RT 提供了第三个存储器管理选项，即子地址双缓存。子地址双缓存提供了确保数据的一致性的方法，图 7 说明了 RT 子地址双缓存方案，类似单消息和循环存储模式，可利用子地址控制字在子地址的基础上选用双缓存模式。双缓存的目的是为主处理器提供方便的办法，用来访问已经接收到给定子地址中的最新的、有效的数据。通过对每一个接收（和/或广播）子地址定位 2 个 32 位的数据字块，该项服务可以在最大程度上确保数据的一致性。

在指定的时刻，两个块中的一个将被指定为“激活”的 1553 数据块，同时另一个将被指定为“非激活”块。从下一个接收消息中发往该子地址的数据字将被存储在“激活”块中。在完成消息的基础上，假定该消息是有效的并且子地址双缓存被使能，则 BU-65170/61580 将自动为各子地址切换“激活”与“非激活”块。ACE 通过拨动子地址的查询表指针的第五位及重写该指针完成这项功能，结果，接收到的数据字的最新有效块就一直处于可被主处理器访问的状态。

作为确保数据一致性的方法，主处理器可以可靠地访问最新有效的接收到的数据字块，但要按下述序列执行：

- (1) 通过子地址控制字禁止各子地址的双缓存，即临时将子地址存储器管理方案切换到单消息模式。

- (2) 读接收（或广播）子地址查询表指针的当前值，该指针指向当前的“激活”数据字块。通过翻转（取反）该指针值的位 5，就有可能定位“非激活”数据字块的起始位置，在最新的有效消息送往该子地址的期间，该块将包含接收到的数据字。

- (3) 从“非激活”（最新）数据字块中读出字。

- (4) 通过子地址控制字重新使能各子地址的双缓存模式。

图 5 RT 存储器管理：单消息模式

图 6 RT 存储器管理: 循环缓存模式

图 7 RT 存储器管理: 子地址双缓存模式

## 5.6 RT 中断

像 BC 模式那样, BU-65170/61580 RT 提供了很多可屏蔽的中断, RT 中断事件包括 (每一个) 消息的结尾、消息差错、被选择的子地址 (子地址控制字) 中断、循环缓存滚动结束、被选择的模式码中断、以及堆栈滚动结束。

## 5.7 描述器堆栈

在每一个消息的开始及结尾, BU-65170/61580 RT 都要在激活区域堆栈中存储一个 4 个字的消息描述器, RT 堆栈的容量是可通过编程从 256、512、1024 及 2048 个字中选择的。图 5、6 和 7 示出了这 4 个字: 块状态字、定时标签字、数据块指针、以及 1553 接收到的指令字。RT 块状态字包含了下述事件的指示信息: 正在处理或已处理完的消息、总线通道、RT-to-RT 传送及 RT-to-RT 传送错误、消息格式错误、环路测试(自检)失败、循环缓存滚动结束、非法的指令、以及其它错误情况。表 22 说明了 RT 块状态字的位影像。

像在 BC 模式中那样, 定时标签字存储了 BU-65170/61580 可读/写的定时标签寄存器的当前内容, 定时标签寄存器的分辨率是可通过编程从 2、4、8、16、32 及 64us/LSB 中选择的, 还有, 时间标签计数器的增量可来自外部时钟源, 也可通过软件指令。

ACE 为当前消息存储被访问的查询表位置的内容, 像数据块指针那样指出数据字块的起始位置, 该项服务可使被存储的消息数据块的定位变得方便。ACE 在 RT 消息描述器的第 4 个位置存储全部 16 位的 1553 指令字。

## 5.8 RT 指令非法化

BU-65170/61580 为 RT 指令非法化提供了一个内部机制, 另外, 还可设置忙状态位, 以便它是唯一被编程的发送/接收/广播子地址的子集。

非法化方案使用 BU-65170/61580 地址空间中的一个 256 个字的区域, 该功能的一个优点是通过取消外部具有非法功能的 PROM、PLD 或 RAM 器件, 简化了对印制电路板的要求。BU-J1165170/61580 的非法化方案提供了最大的灵活性, 它允许广播/自有地址、T/R 位、子地址、以及字计数/模式码的 4096 种可能组合的子集被非法化, 基于 RAM 的非法化技术的另一个优点是它提供了高度的自检性能。

### 5.8.1 寻址非法化表

表 29 说明了非法化 RAM 的寻址方案, 如表所示, 非法化 RAM 的基址是 0300 (16 进制)。ACE 以 BROADCAST/OWN ADDRESS 的值、T/R 位、子地址、以及当前指令字中字计数/模式码区域 (WC/MC4) 的 MSB 为基础, 计算非法化表的索引。

表 29 非法化 RAM 地址定义

| 位        | 描述 | 位 | 描述                           | 位       | 描述      |

|----------|----|---|------------------------------|---------|---------|

| 15 (MSB) | 0  | 9 | 1                            | 4       | SA3     |

| 14       | 0  | 8 | 1                            | 3       | SA2     |

| 13       | 0  | 7 | <u>BROADCAST/OWN-ADDRESS</u> | 2       | SA1     |

| 12       | 0  | 6 | T/R                          | 1       | SA0     |

| 11       | 0  | 5 | SA4                          | 0 (LSB) | WC4/MC4 |

| 10       | 0  |   |                              |         |         |

内部 RAM 为指令非法化保留了 256 个字, 广播指令的非法化与“非广播接收指令及模式指令的非法化”是相互分离的。

指令的非法化可以达到以字计数的水平, 例如, 到子地址 1 的一个单字接收指令可能是合法的, 但到子地址 1 的一个双字接收指令则可能是非法的。

非法表中首批 64 个字与广播接收指令 (每个子地址 2 个字) 有关, 下一批 64 个字与广播发送指令有关。由于非模式码广播发送指令被定义为无效, 因此用户无需对表 (子地址 0 和 31 除外) 中的该部分初始化。再下一批 64 个字与非广播接收指令有关, 最后 64 个字与非广播发送指令有关。0 和 15 之间带有字计数/模式码 (WC/MC) 的消息区域可以被非法化, 这要通过设置非法化表中各偶数地址位的相关数据位来实现, 同样, 16 和 31 之间带有 WC/MC 的消息区域可以被非法化, 这要通过设置非法化表中各奇数地址位的相关数据位来实现。

非法化时要注意下述问题:

- (1) 要非法化一个给定的广播/自有地址-T/R 子地址的特定的字计数, 各非法化字中适当的位应被置位成逻辑 1, 位值为逻辑 0 则表示相应的指令字是合法指令。ACE 将以设置其 RT 状态字中的“消息差错”位作为对一个非法的非广播指令的响应。

- (2) 从子地址 00001 到 11110, “WC/MC”区域指定了各指令字的字计数区域, 从子地址 00000 到 11111, “WC/MC”区

域指定了各指令字的模式码区域。

- (3) 由于非模式码广播发送消息不是由 MIL-STD-1553B 所定义的，因此非法化 RAM 中地址从 0342 到 037D 中的与这些指令相应的 60 个字都无需初始化。ACE 将不响应一个非模式码广播发送指令，但将会自动设置其内部状态寄存器中的“消息差错”位，而不管非法化 RAM 中的相应位是否已经被设置。如果下一个消息是“发送状态”或“发送最后一个指令”模式码，ACE 将以置位其“消息差错”位作为响应。

## 5.9 可编程的忙

为了与 MIL-STD-1553B Notice2 相兼容，BU-65170/61580 RT 提供了一种方法，即作为子地址的一项功能，可通过软件控制的方法设置忙状态字的位。通过位于 BU-65170/61580 的地址空间中的忙查询表，是有可能在指令广播/自有地址、T/R 位、以及子地址的基础上设置忙位的。当忙位被置位时，另一个可编程选项允许被接收的消息的数据字或被存储、或不被存储。

## 5.10 其它 RT 功能

BU-65170/61580 允许由主处理器读通过由硬线连接 RT 的地址，同样，在软件控制下以及/或自动地在环路返回自检失败之后，也有若干选项用于设置 RT 的 FLAG (标志) 状态字位。其它可由软件控制的 RT 选项包括可由软件编程的 RT 状态字及 RT BIT 字、紧随发送矢量字模式指令之后的服务请求状态字位的自动清零、接收到同步模式指令之后清零和/或装载定时标签寄存器的能力、因忙和/或消息差错 (非法) 等状态字位而与数据字传送有关的选项、以及 1553A 及保留的模式码的处理。

# 6 MT 结构

BU-61580 提供了 3 种总线监控器 (MT) 模式：

- (1) “AIM-HY” (缺省) 或 “AIM-HY er” 字监控器模式；

- (2) 可选择的消息监控器模式；

- (3) 同时制远程终端/可选择的消息监控器模式。

在新应用中，强烈推荐使用可选择的消息监控器，而不是字监控器。除了能提供基于 RT 地址、T/R 位、以及子地址的监控器滤波外，消息监控器还消除了用软件来判断消息的起始和结尾的必要性，该类软件的开发正变成一项乏味的工作，并且，在运行时，将使 CPU 承担高度的普通开支。

## 6.1 字监控器

在字监控器模式，BU-61580 监控两个 1553 总线，在初始化完字监控器并将它放到线上后，BU-61580 将存储所有从两个总线上接收到的指令、状态、以及数据字。对从两总线中任何一个上接收到的任一个字，BU-61580 都要在 RAM 中存储一对字，第一个字是来自接收到的字中的 16 位数据，第二个字是监控器 ID 字 (识别字)，或“标签”字。ID 字包含了与总线通道、同步类型、字的有效性、以及中间字定时间隔有关的一些信息。BU-61580 在共享 RAM 地址空间中的循环缓存器中存储数据字及 ID 字，表 23 示出了监控器 ID 字的位影像。

## 6.2 监控器触发字

触发字寄存器为字监控器模式提供了额外的灵活性，BU-61580 在 MT 触发字寄存器中存储 16 位触发字的值，该寄存器的内容代表了触发指令字的值。BU-61580 带有可编程选项，来启动或关闭字监控器，和/或在从 1553 总线上接收到触发指令字后发出一个中断请求。

## 6.3 可选择的消息监控器模式

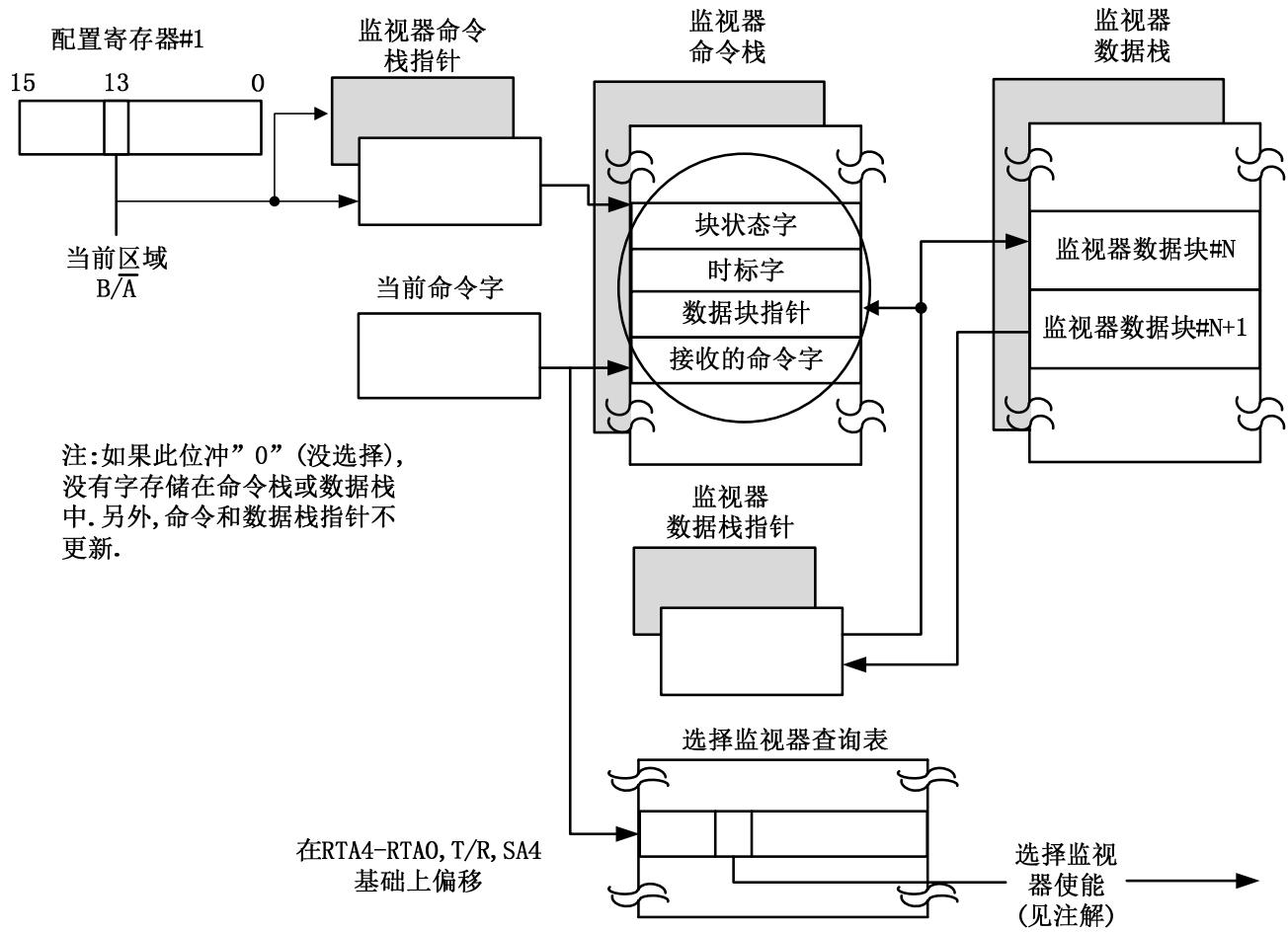

BU-61580 可选择的消息监控器提供的功能可以大量缩减软件、降低主 CPU 的处理负担。可选择的消息监控器与基于 RT 地址的监控器滤波、T/R 位、以及接收到的 1553 指令字的子地址区域一起，可完成对来自双 1553 总线消息的可选择性监控。可选择的消息监控器通过区分指令字及状态字，大大简化了主处理器软件，它在 BU-61580 RAM 中保持两个堆栈：指令堆栈及数据堆栈。

## 6.4 同时制 RT/消息监控器模式

可选择的消息监控器可被用作纯正被动的监控器或被编程用作同时制 RT/监控器, RT/监控器模式为 BU-61580 打包的 RT 地址提供完整的远程终端操作, 并为其它 30 个非广播 RT 地址提供总线监控能力。这样, 就使 BU-61580 同时具有全功能 RT 及“探听”总线活动情况的全部或子集(包含总线上的其它 RT)的能力, 这种工作类型有时需要备份总线控制器。合并的 RT/监控器在 BU-61580 地址空间中保持三个堆栈: RT 指令堆栈、监控器指令堆栈、以及监控器数据堆栈。不同堆栈的指针在 BU-61580 地址空间中都有其固定的位置。

## 6.5 可选择的消息监控器存储器组织

表 30 说明了在可选择的消息监控器模式中的 ACE 典型的存储器影像, 该工作模式在 RAM 中定义了几个固定位置, 这些位置是用和合并的 RT/可选择的消息监控器模式相兼容的方式定位的, 典型的可选择的消息监控器存储器影像的例子可参见表 7。固定的存储器影像由 2 个监控器指令堆栈指针(位置为 102h 及 106h)、2 个监控器数据堆栈指针(位置为 103h 及 107h)、以及一个基于 RT 地址、T/R 及子地址的可选择的消息监控器查询表(0280-02FFh)组成。假定一个监控器指令堆栈的容量为 1K 字、一个监控器数据堆栈的容量为 2K 字。

可选择的消息监控器工作情况的说明可参见图 8, 在接收到一个有效的指令字后, BU-61580 将参考可选择的消息监控器查询表(地址的固定块)来检查当前指令的情况(使能/禁止), 如果是禁止, 则 BU-61580 将忽略(并且不存储)当前消息; 如果是使能, 则 BU-61580 将在监控器指令堆栈中由监控器指令堆栈指针所确定的地址位置建立一个入口。

与 RT 模式类似, ACE 将在消息描述器中存储一个块状态字、16 位的定时标签字、以及数据块指针, 同时还存储紧跟在接收到的指令字之后所接收的 1553 指令字。ACE 在消息的开始及结尾对块状态字及定时标签字进行写操作。监控器块状态字包含了以下事件的指示信息: 正在处理或已处理完的消息、总线通道、监控器数据堆栈滚动结束、RT-to-RT 传送及 RT-to-RT 传送错误、消息格式错误、以及其它错误情况。表 24 给出了消息监控器块状态字。对当前消息来说, 数据块指针指出了存储在监控器数据堆栈中的第一个字(跟在指令字之后的第一个字), 于是 BU-61580 将在监控器数据堆栈中紧邻的位置存储该消息中的后续字(有可能是第二个指令字、数据字、状态字)。

表 30 典型的可选择消息监控器存储器影像(对 4KRAM 而言)

| 地址(16 进制) | 描述                | 地址(16 进制) | 描述               |

|-----------|-------------------|-----------|------------------|

| 0000-0101 | 未使用               | 0108-027F | 未使用              |

| 0102      | 监控器指令堆栈指针 A(固定位置) | 0280-02FF | 可选择的监控器查询表(固定区域) |

| 0103      | 监控器数据堆栈指针 A(固定位置) | 0300-03FF | 未使用              |

| 0104-0105 | 未使用               | 0400-07FF | 监控器指令堆栈 A        |

| 0106      | 监控器指令堆栈指针 B(固定位置) | 0800-0FFF | 监控器数据堆栈 A        |

| 0107      | 监控器数据堆栈指针 B(固定位置) |           |                  |

监控器指令堆栈的容量可被编程为 256、1K、4K、或 16K 个字, 监控器数据堆栈的容量可被编程为 512、1K、2K、4K、8K、16K、32K、或 64K 个字。

可以对监控器指令堆栈滚动结束、监控器数据堆栈滚动结束、和/或消息结尾等事件使能监控器中断, 另外, 监控器触发事件来说, 在字监控器模式中也应该有一个中断被使能。

图 8 可选择的消息监控器存储器管理

## 7 处理器及存储器接口

ACE 终端为与主处理器及外部可任选的存储器接口提供了很大的灵活性, 图 1 示出了与处理器/存储器接口的 14 个控制信号, 其中 6 个具有第二功能。图 9 到图 14 示出了可用于 BU-65170 或 BU-61580 与主处理器总线接口的 6 种配置。各种可能的配置可以使与 8-、16- 及 32-位处理器总线接口所需要的粘合逻辑的数值减到绝对最少, 同时它们所具有的功能还使其与不具有握手应答的“等待状态”的处理器的接口变得方便, 最后, ACE 支持与外部双端口 RAM 可靠地接口, 这种接口类型使得访问 1553 RAM 所需要的处理器带宽减到最小。

16 位缓存模式(图 9)是使用时最普通的配置, 它提供了与 16 位或 32 位微处理器直接的、共享的 RAM 接口。在这种模式下, ACE 的内部地址及数据缓存器在主处理器地址、数据总线及相应的内部存储器总线之间提供了必要的隔离。在缓存模式下, 1553 共享 RAM 的地址空间被限定在 BU-65170/61580 4K 字的内部 RAM 范围内。16 位的缓存模式提供了一对管脚可编程的选项:

- (1) 通过 POLARITY-SEL 输入信号, 可以选择 RD/WR 控制输入的逻辑感应, 比如: 对 Motorola 680×0 处理器来说, 当 RD/WR 为低时是写操作; 对 intel i960 系列微处理器来说, 当 RD/WR 为高时是写些操作;

- (2) 通过将输入信号 ZERO-WAIT 固定为逻辑 1, ACE 终端可以和握手输入应答类型的处理器接口, 以适应硬件控制的等待状态, 很多流行的处理器芯片都具有这种输入口。在这种情况下, 只有当 BU-65170/61580 已经锁存了内部写数据或已经将读数据提供给 D15-D0 后, 它才断言其 READYD 输出为低。

通过将输入信号 ZERO-WAIT 固定为逻辑 0, 可以很容易地将 BU-65170/61580 与非握手输入应答类型的处理器接口, Analog Device 公司的 ADSP2101 DSP 就是这种类型的芯片。在这种配置下, 处理器可以在完成对 BU-65170/61580 的内部 RAM 或寄存器的访问之前清除其选通输出。在这种情况下, READYD 将在 STRBD 的上升沿之后变高, 并一直维持为高直到传送完成为止。正常情况下, 当 ZERO-WAIT 为低时, READYD 也是低。

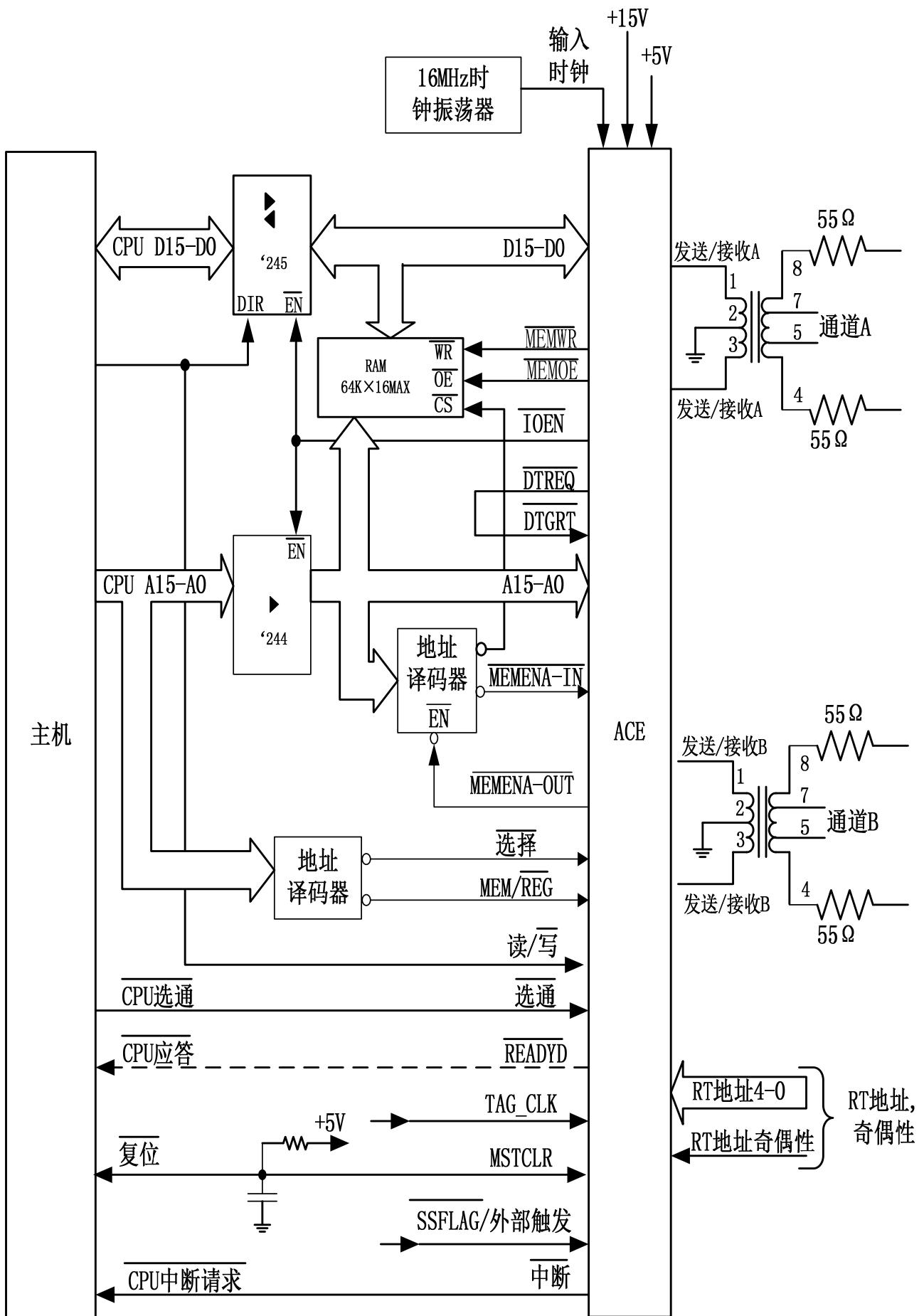

与 16 位缓存模式类似, 16 位的透明模式(见图 10)也支持共享 RAM 与主 CPU 接口, 透明模式的优点在于通过使用外部 RAM, 可以允许缓存器 RAM 的容量扩展到 64K 字。透明模式的缺点是它需要外部地址及数据缓存器, 以将处理器总线从存储器/ BU-65170/61580 总线中隔离出来。

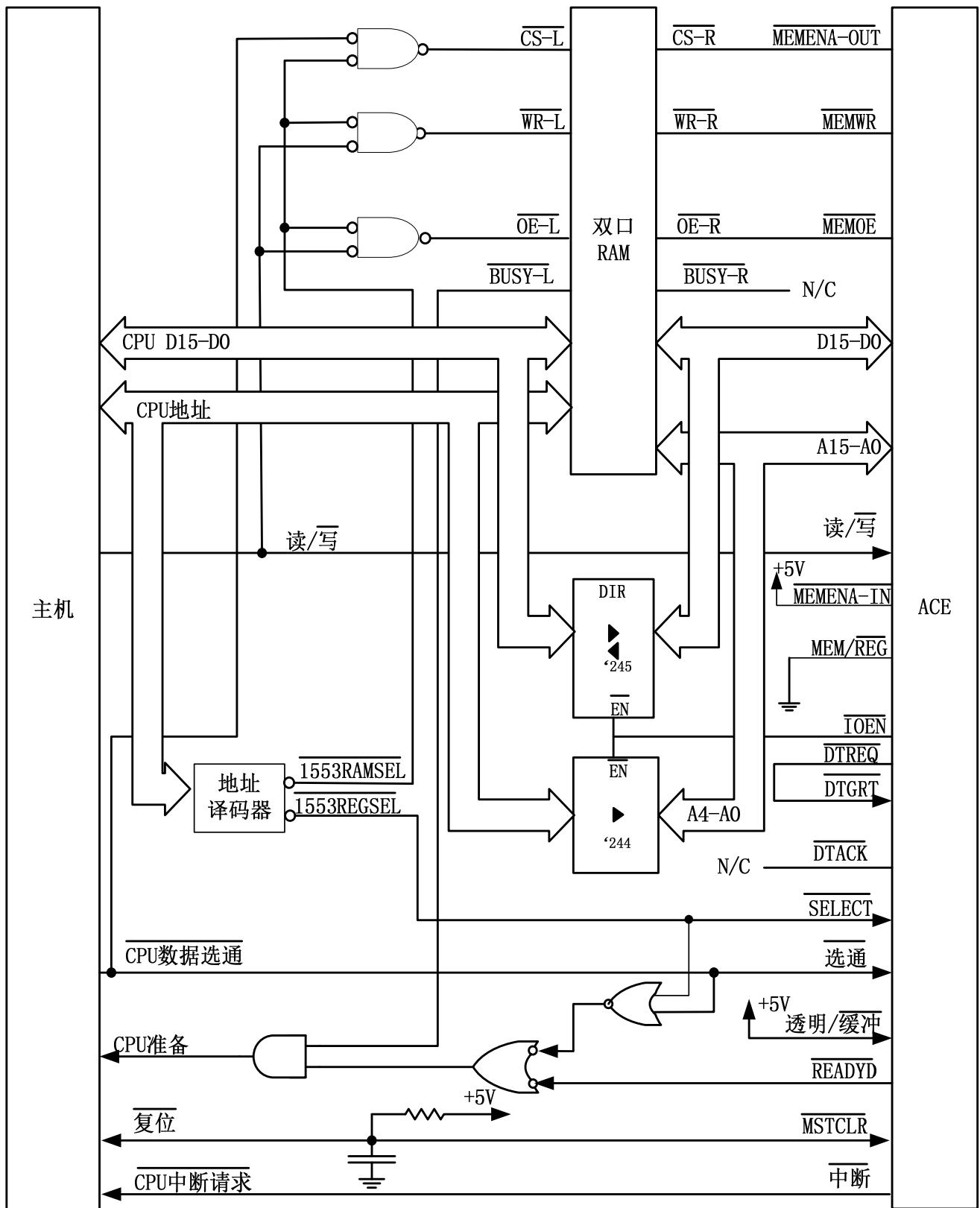

透明模式的修正版本使用了双端口 RAM，而不是传统的静态 RAM，参见图 11。它大大加快了主机访问 RAM 的速度，它的唯一限制是双端口 RAM 的访问时间。这种配置消除了 BU-65170/61580 访问存储器的分配延时，最坏的延时时间仅发生在主机与 BU-65170/61580 1553 逻辑同时访问同一存储器地址的情况下，通常情况下，这种情况很少发生，并且 ACE 可使这种延时限制在 250ns 左右。

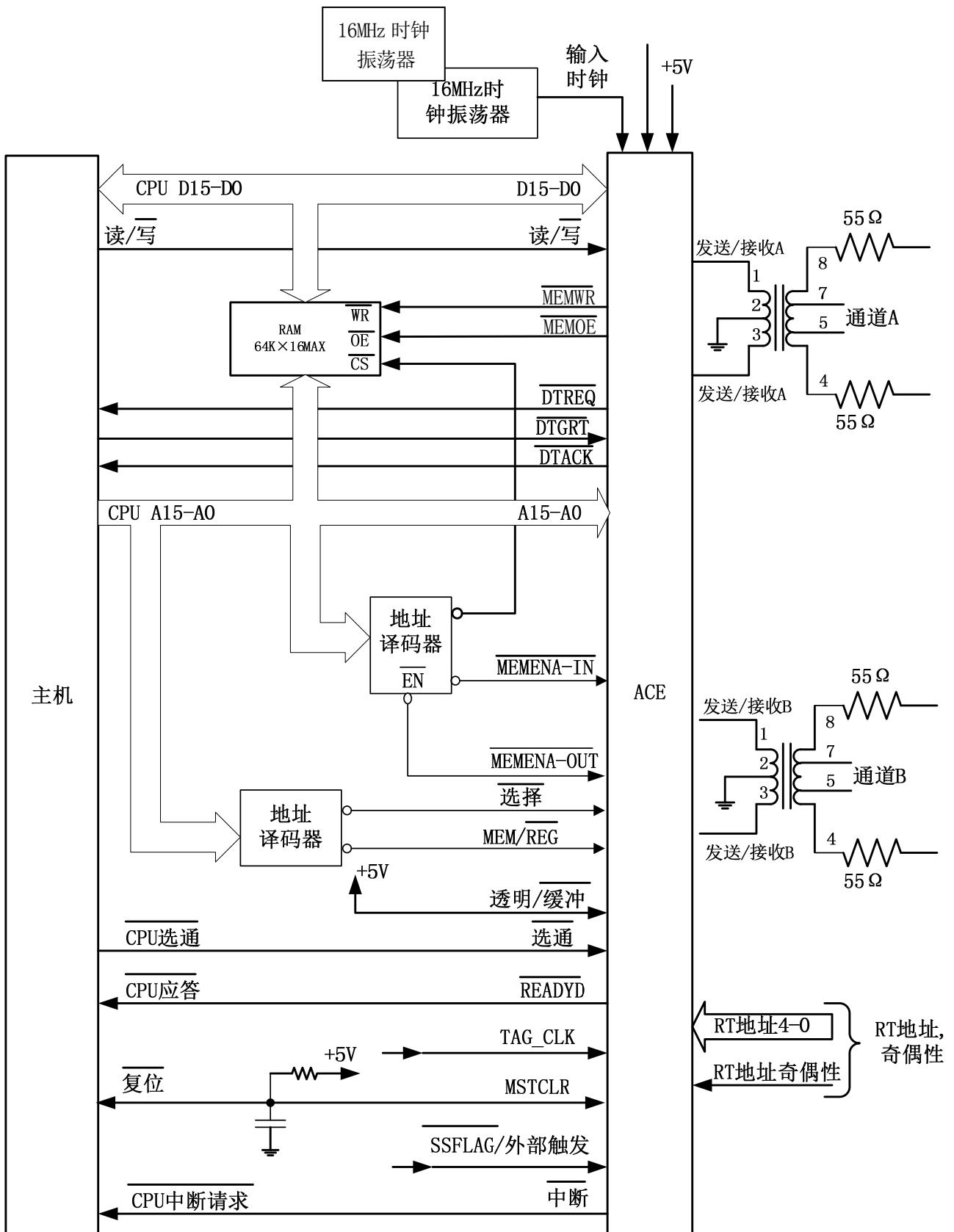

图 12 说明了 16 位直接存储器访问 (DMA) 模式的连接情况，在该配置下，是主处理器，而不是 ACE 终端，来分配地址及数据总线，这种分配包括两个 DMA 输出信号请求 (DTREQ) 及应答 (DTACK)、以及输入信号同意 (DTGRT)。DAM 接口允许 ACE 器件与海量系统 RAM 接口，同时消除了对外部缓存器的需要。在系统地址空间大于 64K 字情况下，当 BU-65170/61580 访问 RAM 时（同时断言 DTACK 为低），主处理器有必要为高端地址位（高于 A15）提供一个页寄存器。

通过标准的 ACE 接口 (SELECT、STRBD、READYD、等等)，可以访问内部 RAM，通过 ACE 的分配逻辑及输出控制信号，如图 35 所示，主 CPU 可以访问外部 RAM。如图 13 所示，非此即彼，主处理器及 ACE 都可以控制 RAM，后者需要使用外部逻辑，但允许主处理器以 RAM 允许的最快访问速度直接访问 RAM，而不必等待 ACE 握手应答输出 (READYD)。

图 14 说明的是 8 位缓存模式，这种接口允许与 8 位微处理器及 8 位微控制器直接接口。类似 16 位缓存配置，对缓存器 RAM 的限制值是 BU-65170/61580 内部 4K 字的 RAM。在 8 位模式，主 CPU 通过嵌入 ACE 接口的一对 8 位寄存器访问 BU-65170/61580 的内部寄存器及 RAM。通过 3 个可捆扎的输入口：ZERO-WAIT、POLARITY-SEL、以及 TRIGGER-SEL，可以进一步配置 8 位接口。通过将 ZERO-WAIT 连到逻辑 0，BU-65170/61580 可以以最小的粘合逻辑和 8 位微控制器、比如 intel8051 系列接口，该系列没有握手输入应答类型。可编程的 POLARITY-SEL 以及 TRIGGER-SEL 输入口允许 BU-65170/61580 适应 8 位微处理器家族所使用的字节次序习惯以及 “AO” 逻辑感应。

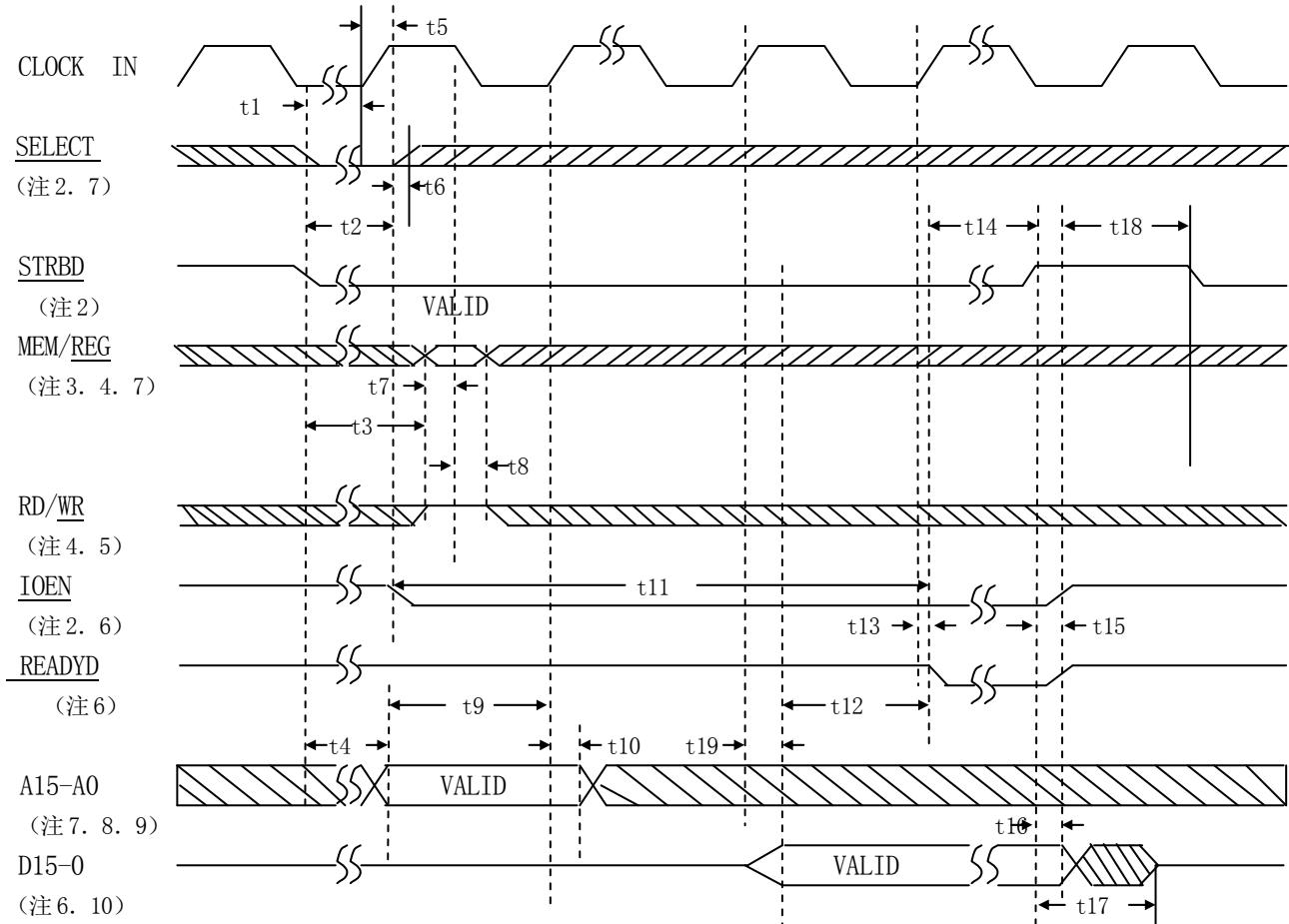

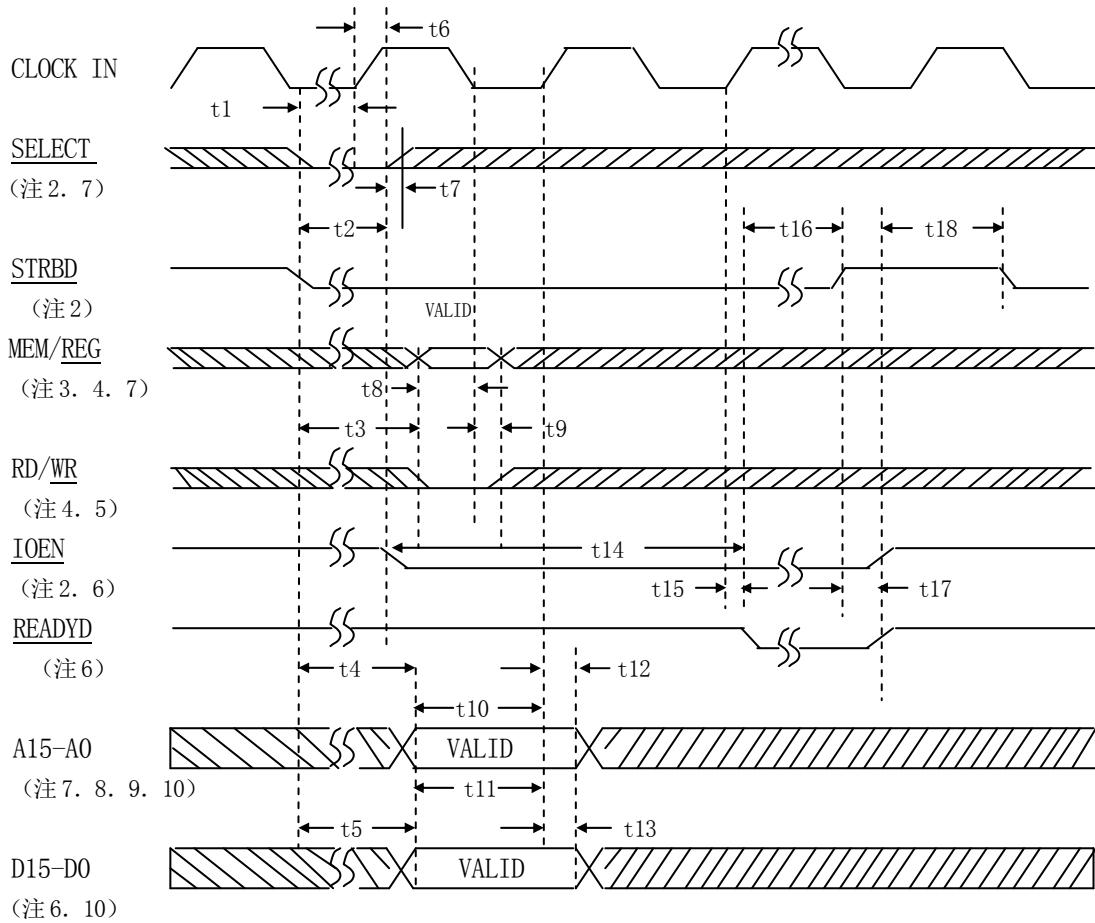

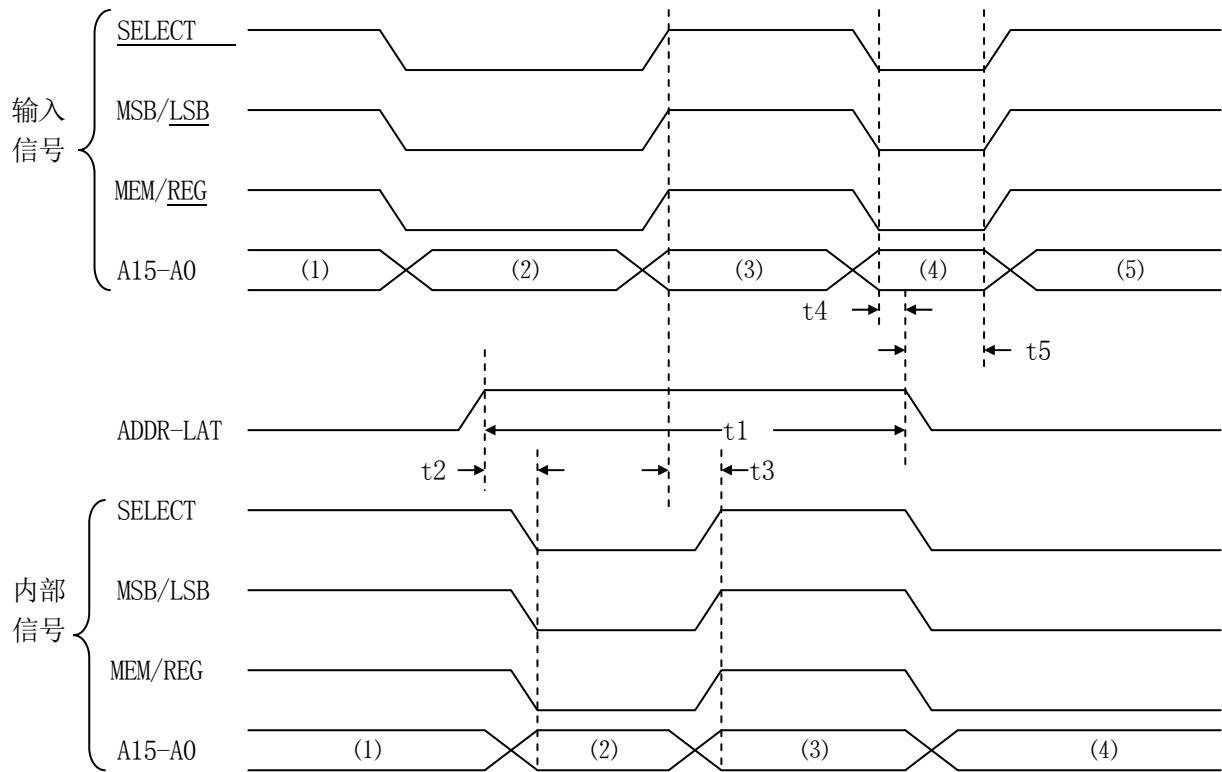

## 7.1 处理器接口定时

图 15 及 16 说明的是在 16 位缓存非零等待模式下，主处理器访问 ACE 内部 RAM 或寄存器的定时，图 15 说明的是在 16 位缓存非零等待模式下读周期的定时，而图 16 说明的是在 16 位缓存非零等待模式下写周期的定时。

在一个 CPU 传送周期，信号 STRBD 及 SELECT 必须在系统时钟的上升沿被采样为低，才能请求访问 BU-65170/61580 的内部共享 RAM。当 STRBD 及 SELECT 为低，且 1553 的协议/存储器管理单元不正在访问内部 RAM 时，传送才会在系统时钟的第一个上升沿开始，输出信号 IOEN 的下降沿表明传送开始。在传送周期开始后，ACE 在第一个时钟下降沿内部锁存信号 MEM/REG 及 RD/WR。在信号 IOEN 变低后，在第一个时钟上升沿，地址输入信号在内部被锁存。注意使用 ADDR-LAT 输入信号时，可以在任意时间锁存地址线。

当信号 IOEN 变低后，在第三个系统时钟的上升沿，输出信号 READYD 将被断言为低，READYD 被断言为低说明对主处理器来说，在并行数据总线上读数据是可以的，或写数据已经被存储，此时，CPU 将使 STRBD 信号变高，完成该传送周期。

## 7.2 地址锁存定时

图 17 说明的是缓存接口模式下地址输入锁存的工作及定时状况，在透明模式下，地址缓存器一直是透明的。由于透明模式需要使用外部缓存器，因此需要锁存外部地址，以多路传输地址总线处于多路传输状态，但是在缓存模式下，可以使用 ACE 的内部地址锁存功能来实现多路传输。

ADDR-LAT 输入信号可以控制地址锁存操作，当 ADDR-LAT 为高时，锁存器输出信号（用来驱动 ACE 内部存储器总线）将跟踪地址输入端 A15-A00 的状态，当它是低时，内部存储器总线的状态被保持锁定为刚好在 ADDR-LAT 的下降沿之前 A15——A00 的状态。

# 8 杂散信号

## 8.1 自检

BU-65170/61580 产品加入了几项自检功能，这些功能包括 BC 及 RT 模式下所有消息的在线打包自检、BC 模式下的离线打包自检、以及其他几项内部自检功能。

BC/RT 在线环路测试包含编码器/解码器及收发器的打包测试，BC 离线自检包含编码器/解码器，不含收发器。这些测试用来检查接收到的每一个被发送字的版本的有效性（同步、编码、位计数、奇偶），并检查接收到的最后一个被发送字的版本，将其与被编码的字进行一位一位地比较。如果内部发送器的看门狗定时器处于暂停状态，则环路测试也是失败。注意看门狗定时器的暂停值依赖于所选择的工作模式（1553A 还是 1553B），环路测试失败将导致消息块状态字中的一位被设置，并且，如果被使能的话，还将导致一个中断请求。若有合适的主处理器软件，BC 离

线测试可以完成并行及串行数据路径、编码器、解码器、以及大部分BC协议和存储器管理逻辑的测试。

另外，还有内在的自检功能，包括3个配置寄存器的位及8个测试寄存器的使用。它可以测试J型芯片内部大约99%的逻辑。这些测试包括一个编码器测试、一个解码器测试、一个寄存器测试、一个协议测试、以及一个失败安全定时器（发送器暂停）测试。

还有一个测试模式，在该测试模式下，通过对一对测试寄存器进行写操作，主处理器可以仲裁1553总线的激活性，该测试模式可以与字监控器模式一起工作，以方便端对端的自检。

## 8.2 RAM的奇偶产生与校验

J型单片结构就是在J型芯片内部的4K字之外可以扩展一定数量的缓存RAM，对这个片外缓存RAM来说，J型芯片可以对其完成奇偶产生与校验。奇偶产生与校验为检查内部缓存器中数据的完整性提供了一种机制，另外，还要使用17位，而不是16位的宽缓存RAM，对该RAM来说，J型芯片将为所有（主机及1553）的写访问产生一个第17位（奇偶位），并且为所有的读访问校验该奇偶位。如果奇偶错误发生，则将发出一个中断申请，中断状态寄存器中相应的位将被置位。BU-61585中还额外加入了一个 $8K \times 17$ 的RAM芯片。

注：

- 1、CPU地址锁存信号由处理器用多路地址/数据总线提供。

- 2、如果极性选择=1，读/写对读为高，写为低，如果极性选择=0，读/写对读为低，写为高。

- 3、ZERO\_WAIT对于非0等待接口应该接逻辑“1”，对于0等待接口应该接逻辑“0”。

- 4、CPU应答仅对于非0等待的接口类型进行处理器输入。

图9 16位缓存模式

图 10 16 位透明模式

图 11 使用双端口 RAM 的 16 位透明模式

图 12 16 直接存储器访问 (DMA) 模式

图 13 带有降低处理器对外部 RAM 访问时间的外部逻辑的 16 位 DMA 模式

\*BU-61585 还额外需要地址线 A12 及 A13。

**注:** (1) CPU D7-D0 同时连到 D15-D8 及 D7-D0。 (2) CPU ADDRESS LATCH 信号由带有多路传输地址/数据缓存器的处理器提供。 (3) 如果 POLARITY-SEL=“1”，则当 MSB/LSB 为低时选择的是 MSB，为高时选择的是 LSB。如果 POLARITY-SEL=“0”，则当 MSB/LSB 为低时选择的是 LSB，为高时选择的是 MSB。 (4) 对非零等待接口来说，ZERO-WAIT 应该被连到逻辑 1，对零等待接口来说，ZERO-WAIT 应该被连到逻辑 0。 (5) TRIGGER-SEL 输入端的工作情况如下：对非零等待接口（ZERO-WAIT=“1”）来说，如果 TRIGGER-SEL=“1”，则对读访问而言，内部 16 位传送就会被 MSB 传送所触发、对写访问而言，内部 16 位传送就会被 LSB 传送所触发。如果 TRIGGER-SEL=“0”，则对读访问而言，内部 16 位传送就会被 LSB 传送所触发、对写访问而言，内部 16 位传送就会被 MSB 传送所触发。 对零等待（ZERO-WAIT=“0”）接口来说，若 TRIGGER-SEL=“1”，则对读访问及写访问而言，内部 16 位传送就会被 LSB 传送所触发。若 TRIGGER-SEL=“0”，则对读访问及写访问而言，内部 16 位传送就会被 MSB 传送所触发。 (6) CPU ACKNOWLEDGE 处理器输入信号只用在非零等待类型的接口中。

图 14 8 位缓存模式

图 15 CPU 读 RAM (16 位、缓存零等待模式)

图 15 及表 31 注：

- (1) 对 16 位缓存非零等待配置来说, TRANSPARENT/BUFFERED 必须被连到逻辑 0, ZERO-WAIT 及 DTREQ/16/8 必须被连到逻辑 1。输入端 TRIGGER-SEL 及 MSB/LSB 可以被连到+5V 或地。