### 第三章 外部存储器接口(EMIF)

## 3.1 概述

---

### 外部存储器接口的用途

为**DSP**芯片与众多外部设备之间提供一种连接方式，**EMIF**最常见的用途就是同时连接**FLASH**和**SDRAM**。

**EMIF**性能优良，跟外部**SDRAM**和异步器件连接时，具有很大的方便性和灵活性。根据**DSP**器件的不同，**EMIF**数据总线可以是**32位**或**16位**的。

# SRAM vs DRAM

- ◆ SRAM是**Static Random Access Memory**的缩写，中文含义为静态随机访问存储器，它是一种类型的半导体存储器。“静态”是指只要不掉电，存储在**SRAM**中的数据就不会丢失。这一点与**DRAM**不同，**DRAM**需要进行周期性的刷新操作。同时，我们不应将**SRAM**与只读存储器(**ROM**)和**Flash Memory**相混淆，因为**SRAM**是一种易失性存储器，它只有在电源保持连续供应的情况下才能够保持数据。“随机访问”是指存储器的内容可以任意顺序访问，而不管前一次访问的是哪一个位置。

- ◆ DRAM是**Dynamic RAM**的缩写，中文含义为动态随机存取存储器，需要不断的刷新，才能保存数据。而且是行列地址复用的，许多都有页模式。**SDRAM: Synchronous DRAM**，即数据的读写需要时钟来同步。

- ◆ 一个是静态的，一个是动态的，静态的是用的双稳态触发器来保存信息，而动态的是用电子，要不时的刷新来保持。

- ◆ DRAM容量大，SRAM容量小

# SDRAM的结构

# FLASH ROM

---

**Flash-ROM**（闪存）已经成为了目前最成功、流行的一种固态内存，与 **EEPROM** 相比具有读写速度快，而与 **SRAM** 相比具有非易失、以及价廉等优势。而基于 **NOR** 和 **NAND** 结构的闪存是现在市场上两种主要的非易失闪存技术。Intel 于 1988 年首先开发出 **NOR flash** 技术，彻底改变了原先由 **EPROM** 和 **EEPROM** 一统天下的局面。紧接着，1989 年东芝公司发表了 **NAND flash** 技术（后将该技术无偿转让给韩国 **Samsung** 公司），强调降低每比特的成本，更高的性能，并且象磁盘一样可以通过接口轻松升级。

**NOR** 的特点是芯片内执行（**XIP, eXecute In Place**），这样应用程序可以直接在闪存内运行，不必再把代码读到系统 **RAM** 中。**NOR** 的传输效率很高，在 1~4MB 的小容量时具有很高的成本效益，但是很低的写入和擦除速度大大影响了它的性能。

**NAND** 结构能提供极高的单元密度，可以达到高存储密度，并且写入和擦除的速度也很快，这也是为何所有的 **U 盘**都使用 **NAND** 闪存做为存储介质的原因。应用 **NAND** 的困难在于闪存和需要特殊的系统接口。

# NAND flash和NOR flash的对比

## 性能比较

闪存是非易失内存，可以对称为块的内存单元块进行擦写和再编程。任何闪存器件的写入操作只能在空或已擦除的单元内进行，所以大多数情况下，在进行写入操作之前必须先执行擦除。

**NAND**器件执行擦除操作是十分简单的，而**NOR**则要求在进行擦除前先要将目标块内所有的位都写为0。由于擦除**NOR**器件时是以64~128KB的块进行的，执行一个写入/擦除操作的时间为5s，与此相反，擦除**NAND**器件是以8~32KB的块进行的，执行相同的操作最多只需要4ms。

# NAND flash和NOR flash的对比

---

## 接口差别

**NOR** 闪存带有**SRAM**接口，有足够的地址引脚来寻址，可以很容易地存取其内部的每一个字节。

**NAND**闪存使用复杂的**I/O**口来串行地存取资料，各个产品或厂商的方法可能各不相同。**8**个引脚用来传送控制、地址和资料信息。**NAND**读和写操作采用**512**字节的块，这一点有点像硬盘管理此类操作，很自然地，基于**NAND**的闪存就可以取代硬盘或其它块设备。

# NAND flash和NOR flash的对比

---

## 容量和成本

**NAND** 闪存的单元尺寸几乎是**NOR**闪存的一半，由于生产过程更为简单，**NAND**结构可以在给定的模具尺寸内提供更高的容量，也就相应地降低了价格。

**NOR** 闪存容量为1~16MB，而**NAND** 闪存只是用在8MB以上的产品当中，这也说明**NOR**主要应用在代码存储介质中，**NAND**适合于资料存储，**NAND**在 CompactFlash、Secure Digital、PC Cards和MMC存储卡市场上所占份额最大。

# NAND flash和NOR flash的对比

---

## 可靠性和耐用性

寿命(耐用性): 在**NAND**闪存中每个块的最大擦写次数是一百万次，而**NOR**的擦写次数是十万次。

位交换: 位反转的问题更多见于**NAND**闪存，如果用来存储操作系统、配置文件或其它敏感信息时，必须使用**EDC/ECC**算法以确保可靠性。

坏块处理: **NAND**器件中的坏块是随机分布的，需要对介质进行初始化扫描以发现坏块，并将坏块标记为不可用。

# NAND flash和NOR flash的对比

---

## 易于使用

可以非常直接地使用基于**NOR**的闪存，可以像其它内存那样连接，并可以在上面直接运行代码。

由于需要**I/O**接口，**NAND**要复杂得多。各种**NAND**器件的存取方法因厂家而异。在使用**NAND**器件时，必须先写入驱动程序，才能继续执行其它操作。向**NAND**器件写入信息需要相当的技巧，因为设计师绝不能向坏块写入，这就意味着在**NAND**器件上自始至终都必须进行虚拟映像。

## 3.2 EMIF寄存器

| 偏移量 | 缩写               | 说明                                        |

|-----|------------------|-------------------------------------------|

| 04h | <b>AWCCR</b>     | 异步等待周期配置寄存器                               |

| 08h | <b>SDCR</b>      | <b>SDRAM</b> 配置寄存器                        |

| 0Ch | <b>SDRCR</b>     | <b>SDRAM</b> 刷新控制寄存器                      |

| 10h | <b>A1CR</b>      | 异步1配置寄存器                                  |

| 20h | <b>SDTIMR</b>    | <b>SDRAM</b> 时序寄存器                        |

| 3Ch | <b>SDSRETR</b>   | <b>SDRAM</b> 自刷新退出时序寄存器                   |

| 40h | <b>EIRR</b>      | EMIF中断寄存器 44h EIMREMIIF中断屏蔽寄存器            |

| 48h | <b>EIMSR</b>     | EMIF中断屏蔽设置寄存器                             |

| 4Ch | <b>EIMCR</b>     | EMIF中断屏蔽清除寄存器                             |

| 60h | <b>NANDFCR</b>   | <b>NAND Flash</b> 控制寄存器                   |

| 64h | <b>NANDFSR</b>   | <b>NAND Flash</b> 状态寄存器                   |

| 70h | <b>NANDF1ECC</b> | <b>NAND Flash</b> 1纠错码寄存器( <b>CS2</b> 空间) |

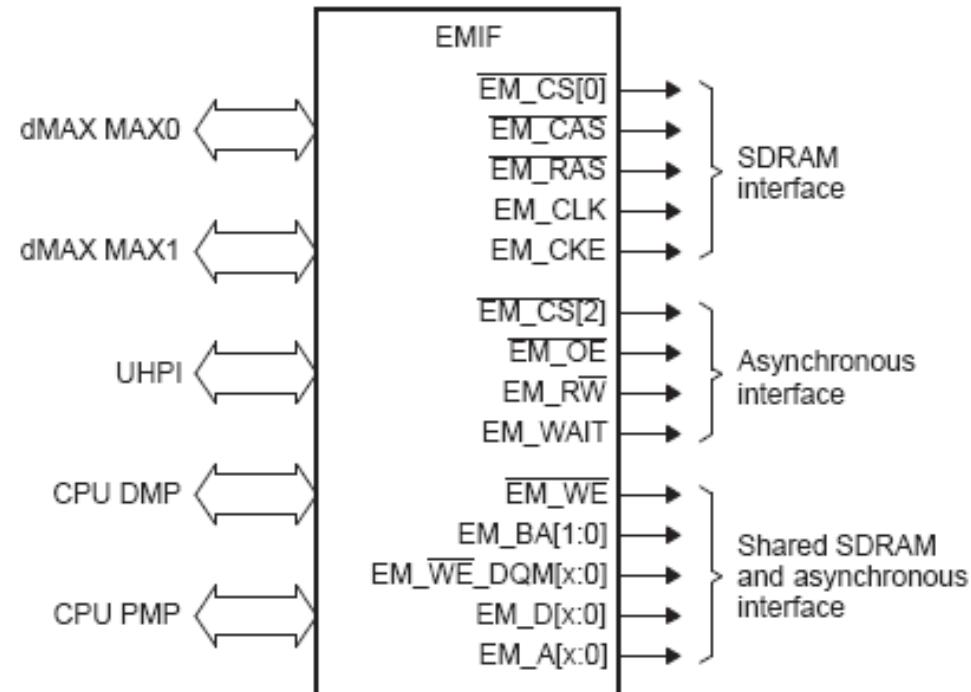

## 3.3 EMIF结构和操作

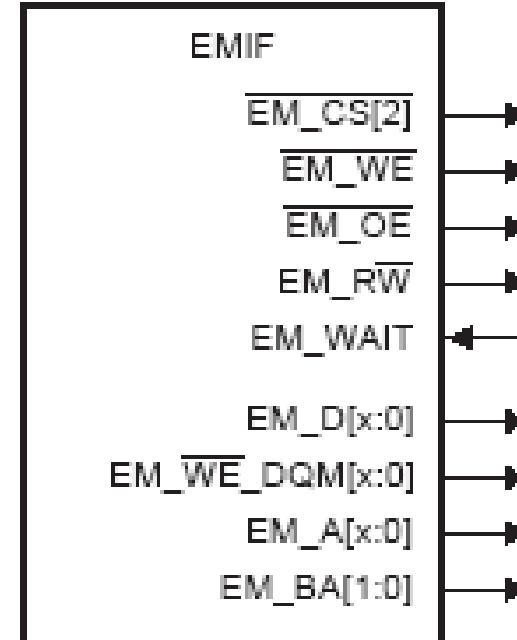

### 3.3.1 EMIF引脚描述

- 1、SDRAM专用EMIF引脚

- 2、异步储存器专用引脚

- 3、访问SDRAM和异步储存器的EMIF引脚

## 3.3 EMIF结构和操作

### 访问SDRAM和异步存储器的EMIF引脚

| 引脚             | I/O | 功能描述                                                                                                                |

|----------------|-----|---------------------------------------------------------------------------------------------------------------------|

| EM_D[x:0]      | I/O | <b>EMIF数据总线</b><br>不同器件的数据总线宽度不同，请参考器件的数据手册。                                                                        |

| EM_A[x:0]      | O   | <b>EMIF地址总线</b><br>当与SDRAM器件连接时，地址总线主要为SDRAM提供行地址和列地址。<br>当与异步器件连接时，这些引脚与EM_BA引脚共同形成送到器件的地址。                        |

| EM_BA[1:0]     | O   | <b>EMIF存储区地址线</b><br>当与SDRAM连接时，为SDRAM提供存储区地址。<br>当与异步器件连接时，这些引脚与EM_A引脚共同形成送到器件的地址。                                 |

| EM_WE_DQM[x:0] | O   | <b>低电平有效写触发或字节使能引脚</b><br>与SDRAM器件连接时，这些引脚与SDRAM的DQM引脚相连，在数据访问中分别使能/禁用每一字节。<br>与异步器件连接时，这些引脚可作为字节使能(DQM)或字节写触发(WE)。 |

| EM_WE          | O   | <b>低电平有效写使能引脚</b><br>与SDRAM器件连接时，此引脚与SDRAM的WE引脚相连用于向器件发送命令。<br>与异步器件连接时，在异步写访问周期，提供一低电平信号。                          |

## 3.3 EMIF结构和操作

### SDRAM专用EMIF引脚

| 引脚       | I/O | 功能描述                                                                                                                             |

|----------|-----|----------------------------------------------------------------------------------------------------------------------------------|

| EM_CS[0] | O   | <b>SDRAM器件低电平有效芯片使能引脚</b><br>该引脚与SDRAM器件的片选引脚连接，用于使能/禁用命令。即使EMIF没有连接SDRAM器件，缺省情况下它也保持此SDRAM的片选有效。当访问异步存储区时此引脚失效，在完成异步存取后自动恢复其功能。 |

| EM_RAS   | O   | <b>低电平有效行地址选通引脚</b><br>此引脚连接在SDRAM器件的RAS引脚上，用于向此器件发送命令。                                                                          |

| EM_CAS   | O   | <b>低电平有效列地址选通引脚</b><br>此引脚连接在SDRAM器件的CAS引脚上，用于向此器件发送命令。                                                                          |

| EM_CKE   | O   | <b>时钟使能引脚</b><br>此引脚连接在SDRAM器件的CKE引脚上，发出自刷新命令使器件进入自刷新模式。                                                                         |

| EM_CLK   | O   | <b>SDRAM时钟引脚</b><br>此引脚与SDRAM器件的CLK相连。                                                                                           |

## 3.3 EMIF结构和操作

### 异步储存器专用引脚

| 引脚       | I/O | 功能描述                                                                                                                                                                                                                                        |

|----------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EM_CS[2] | O   | <b>低电平有效异步器件使能引脚</b><br>此引脚与异步器件的片选引脚相连接。它仅在访问异步存储器时有效。                                                                                                                                                                                     |

| EM_WAIT  | I   | <b>可编程极性等待输入引脚/ NAND Flash准备好输入引脚</b><br>EMIF接口中插入EM_WAIT等待可以扩展异步器件访问的触发周期。为了实现这一功能，异步1配置寄存器(A1CR)的EW位必须置1。另外，必须配置A1CR的WP0位来定义EM_WAIT脚的极性。并不是所有器件上都有EM_WAIT引脚，详细内容可以参考器件数据手册。当NAND Flash控制寄存器(NANDFCR)的CS2NAND位被置位时，此引脚作为NAND Flash准备好输入引脚。 |

| EM_OE    | O   | <b>低电平有效异步器件使能引脚</b><br>此引脚在异步读访问的触发周期提供一个低电平信号。                                                                                                                                                                                            |

| EM_RW    | O   | <b>读/写选择引脚</b><br>此引脚在异步读取的整个周期呈现高电平，写入周期呈现低电平。                                                                                                                                                                                             |

### 3.3.2 时钟控制

---

**EMIF** 的内部时钟来自**DSP** 的锁相环(**PLL**)控制器的**SYSCLK3**时钟模块，不能直接利用外部输入时钟。

**SYSCLK3**时钟模块的频率通过对锁相环控制器的乘法器和除法器的设置来进行控制。

**EMIF**的时钟是通过**EM\_CLK**引脚输出的，可在跟外部存储器连接时使用。**EMIF**时钟(**EM\_CLK**)在器件复位期间不工作，释放复位引脚后**PLL**控制器不再对器件复位，**EM\_CLK**重新开始以**PLL**控制器设定的频率输出时钟信号

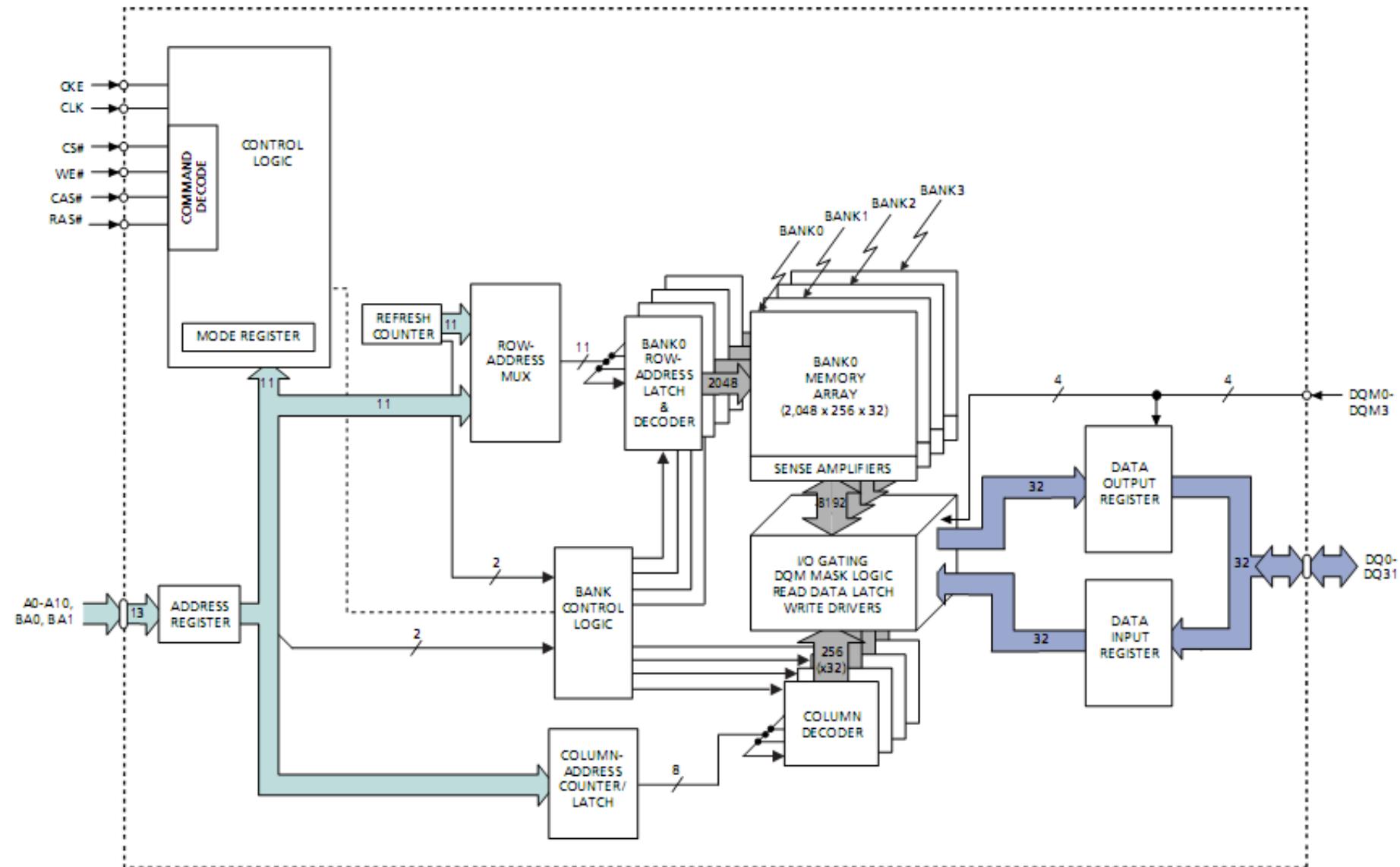

### 3.3.4 SDRAM控制器和接口

---

EMIF可以跟大多数标准SDRAM 器件进行无缝接口，并且支持自刷新模式和优先刷新。另外，有些参数可通过编程来设定，如刷新速率，CAS延迟和很多SDRAM时序参数，这样就提供了很大的灵活性。

EMIF支持与具有下列特点的SDRAM器件的无缝连接：

Pre-charge 位为A[10]

列地址位数为8. 9或10

行地址位数根据DSP器件不同可以变化：

--对于有12位EMIF地址引脚的DSP： 11或12位行地址位

--对于有13位EMIF地址引脚的DSP： 11. 12或13位行地址位

内部存储区数为1. 2或4

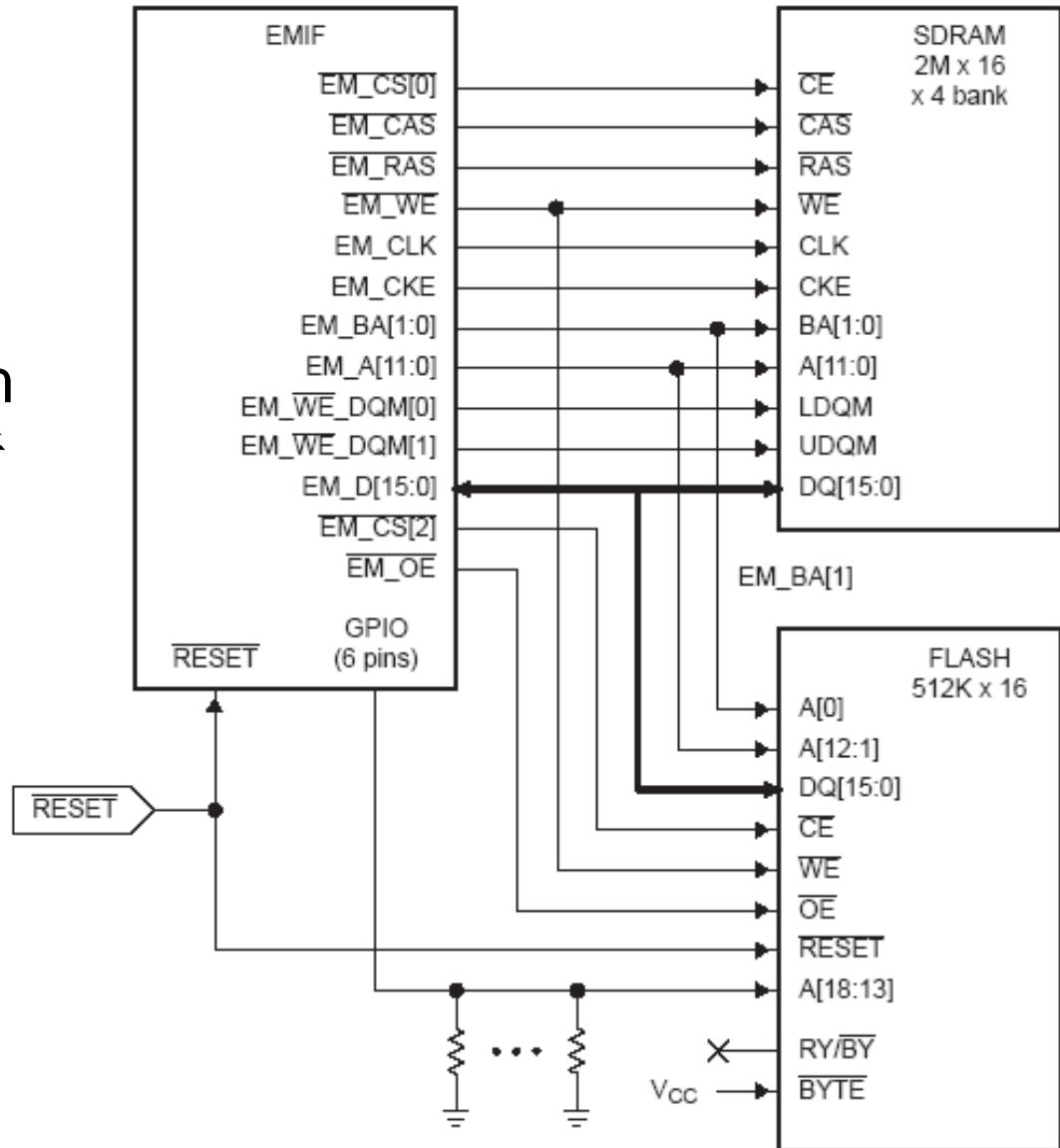

# EMIF与2Mx16x4 SDRAM的连接图

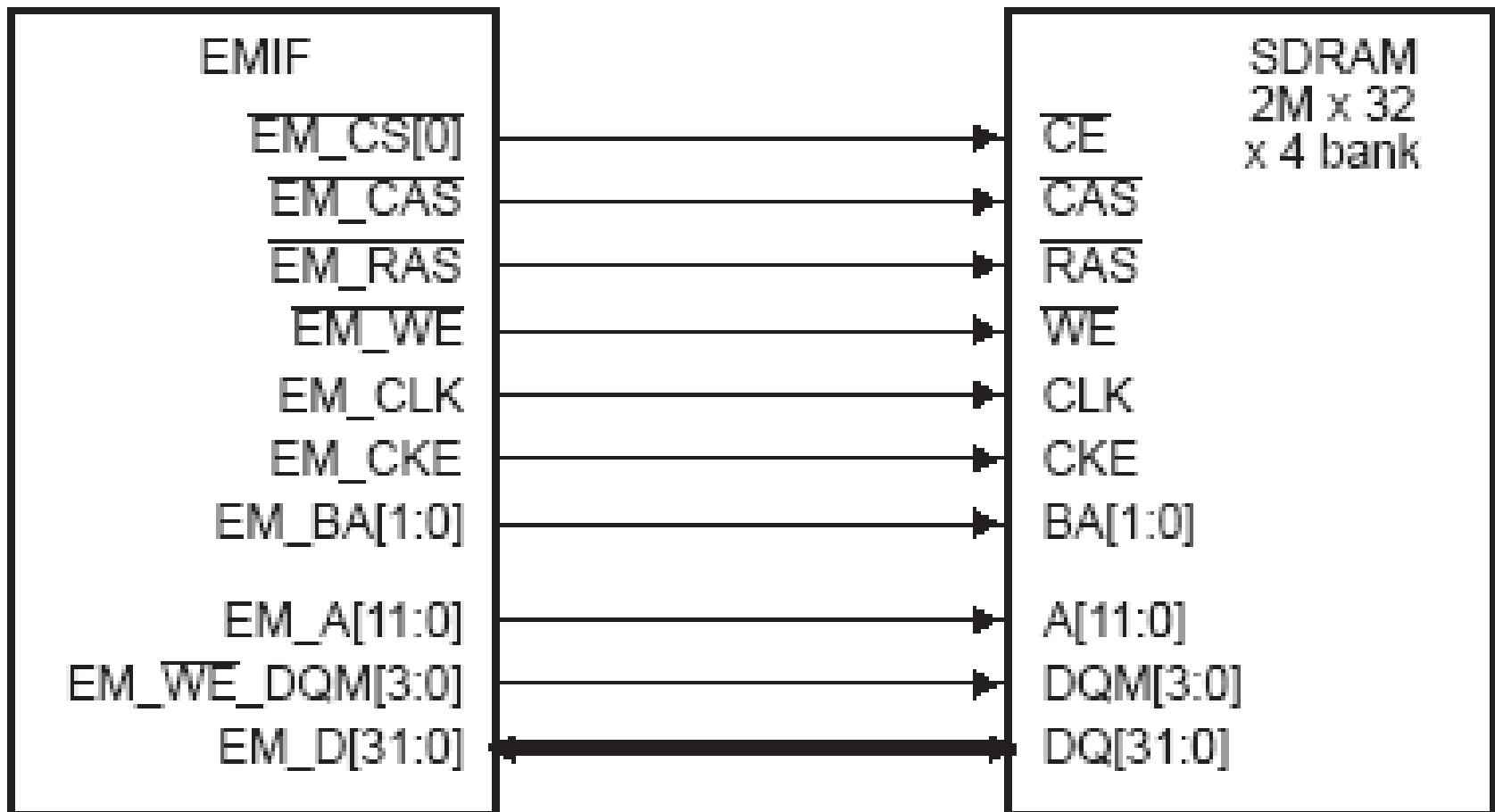

# EMIF与2Mx32x4 SDRAM的连接图

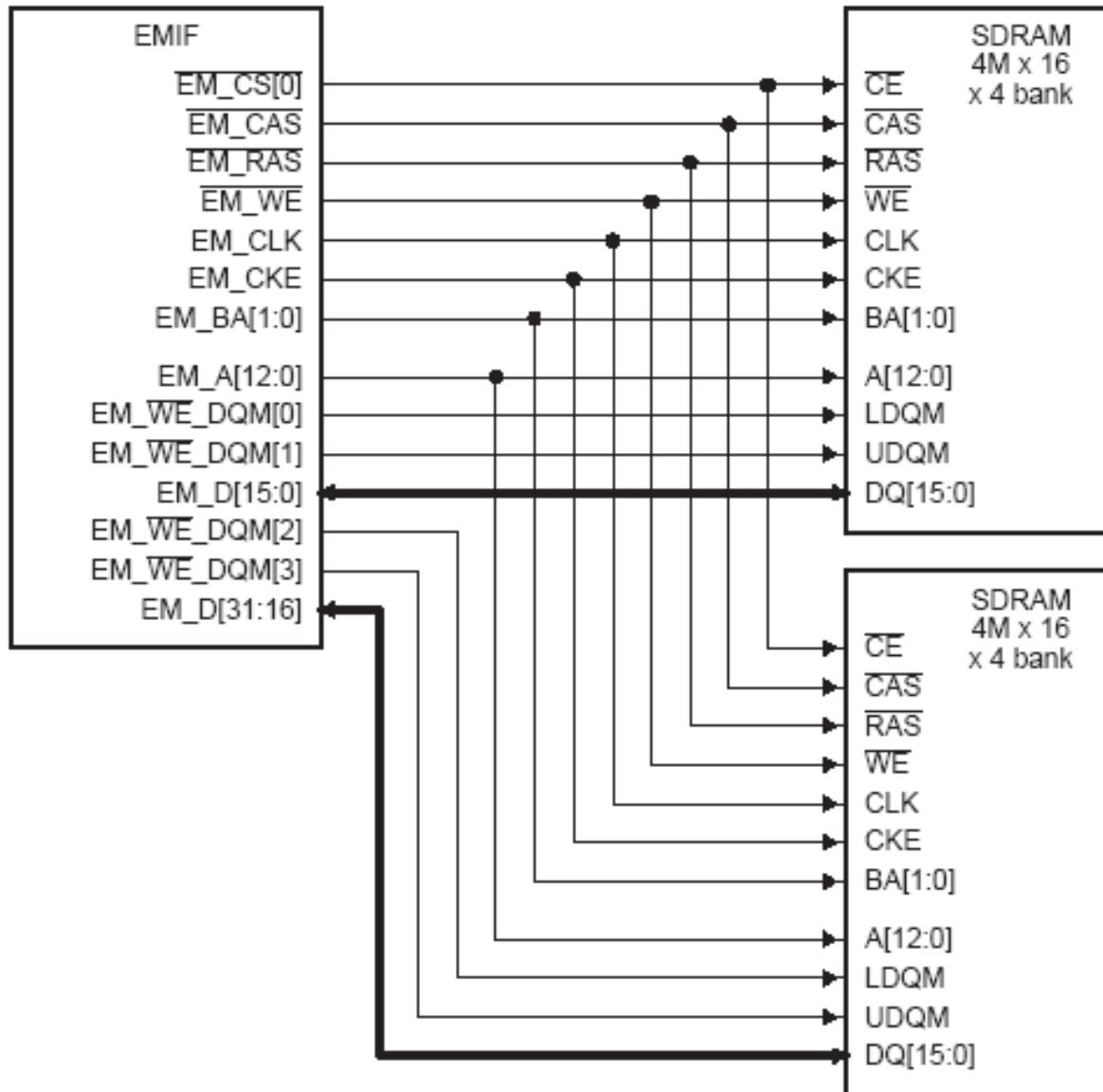

# EMIF与双4Mx16x4 SDRAM的连接图

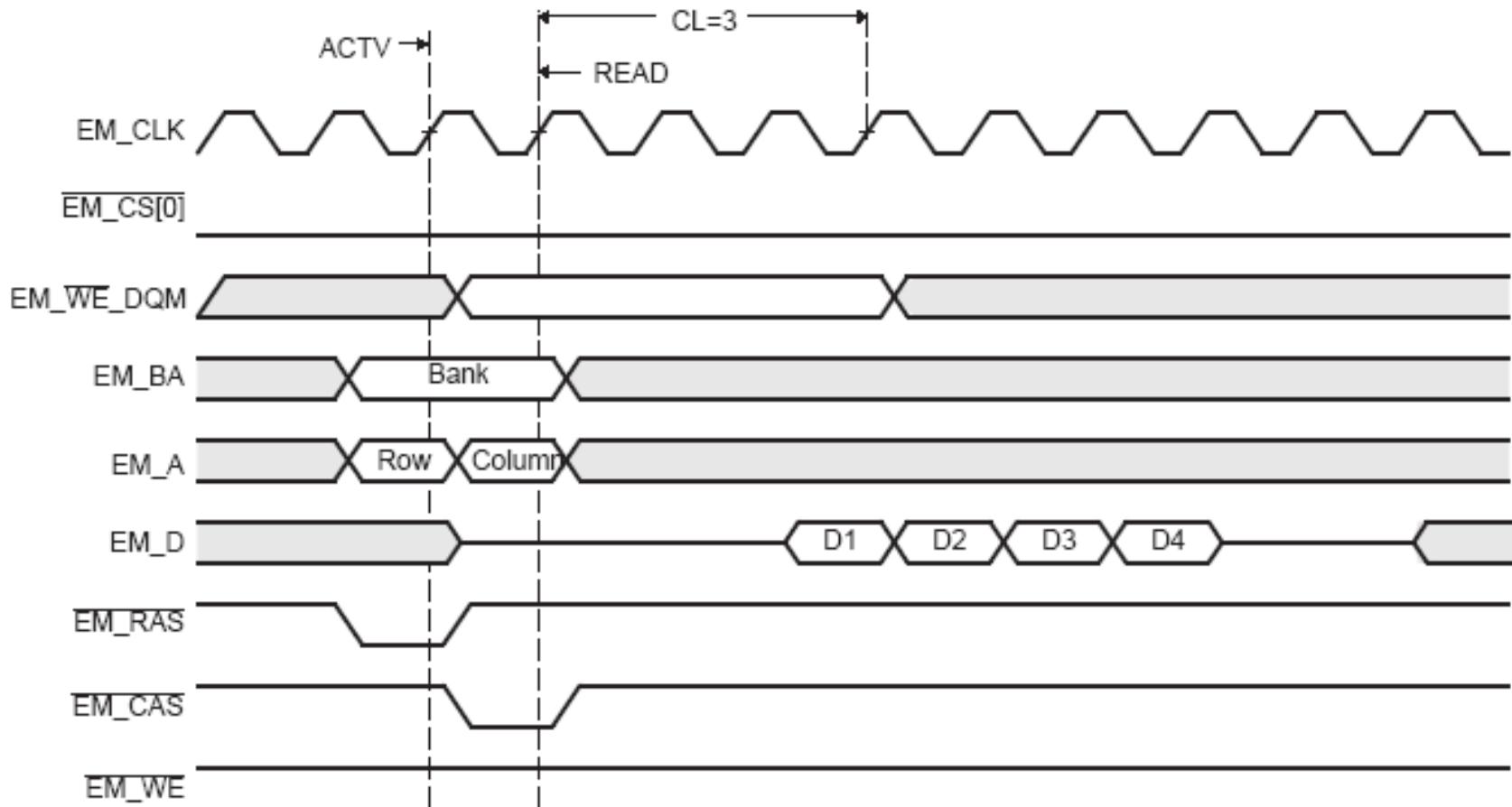

# SDRAM读操作

当EMIF收到任一个SDRAM的读操作请求时，就会进行一个或多个读访问。

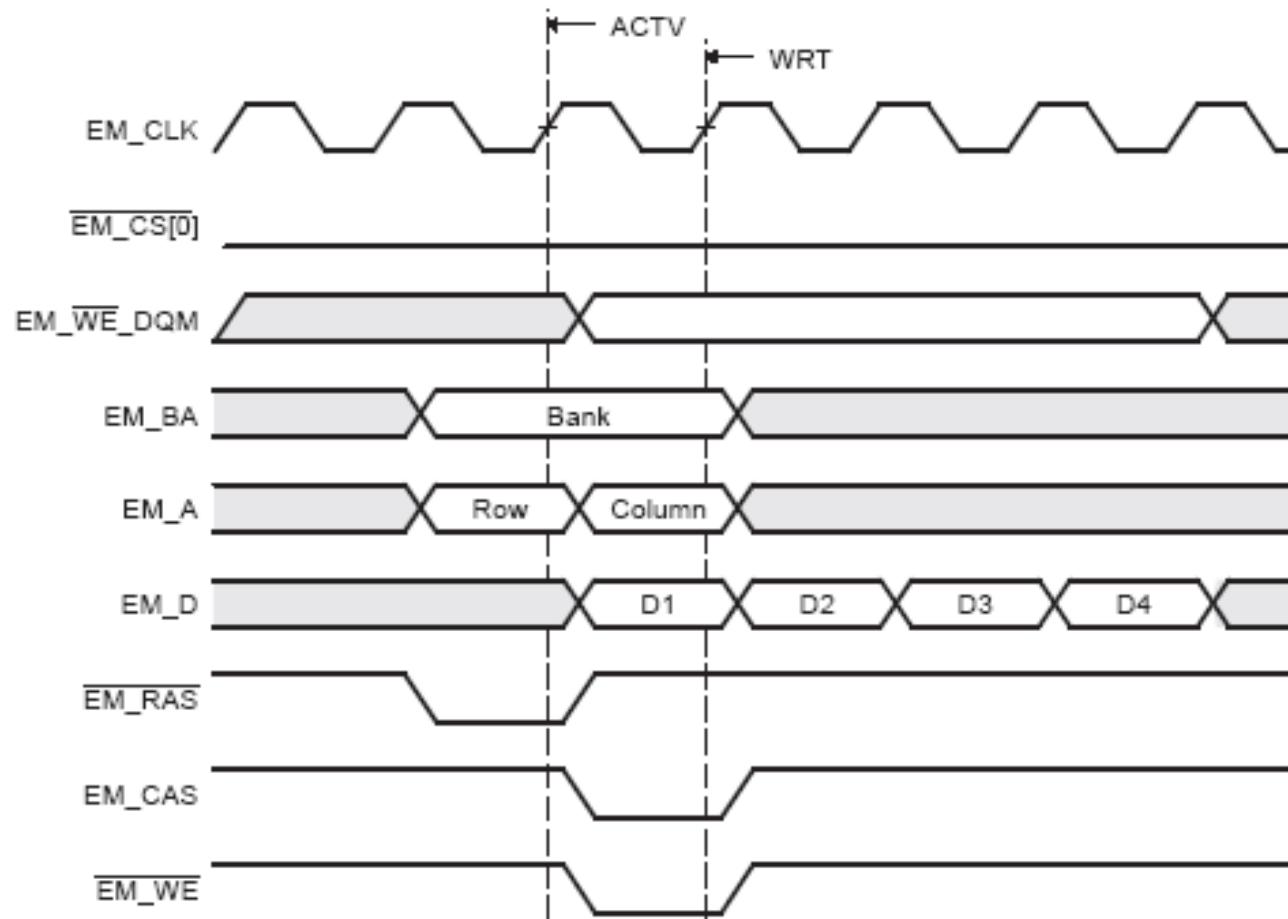

# SDRAM写操作

当EMIF收到任一个SDRAM的写操作请求时，EMIF就会进行一个或多个写访问操作。

### 3.3.5 异步控制器和接口

- ◆ EMIF可以很容易的与各种异步器件直接连接，这些异步器件包括NOR Flash, NAND Flash和 SRAM。

- ◆ 两种主要运行模式的对比：

| 触发模式    | EM_WE_DQM引脚功能 | EM_CS[2] 的操作      |

|---------|---------------|-------------------|

| WE 触发模式 | 写触发           | 异步访问期间一直处于激活状态    |

| 选择触发模式  | 字节使能          | 仅在一个访问中的触发阶段是被激活的 |

## 3.3.5 异步控制器和接口

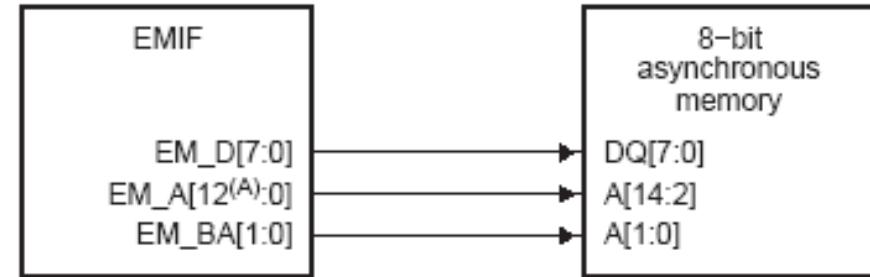

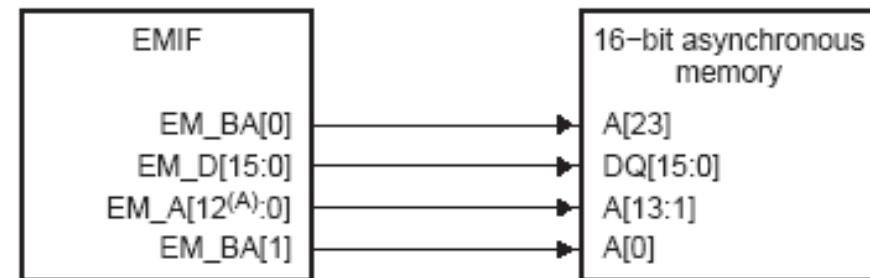

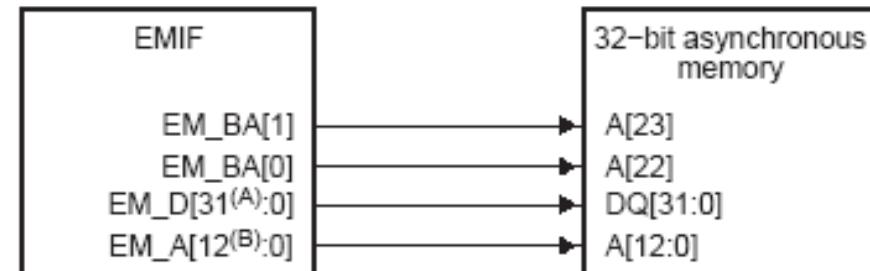

### 1. 异步存储器接口

**EMIF**的地址引脚**EM\_A[x:0]**给出的一般是32位字地址的最低有效位。

**BA[1:0]**引脚或者给出半字和字节选择信号，或者给出**EM\_A[23:22]**的信号，这取决于异步1配置寄存器(**A1CR**)中数据总线宽度的配置。

## 3.3.5 异步控制器和接口

### 1. 异步存储器接口

a) EMIF与8位存储器的接口

b) EMIF与16位存储器的接口

c) EMIF与32位存储器的接口

### 3.3.5 异步控制器和接口

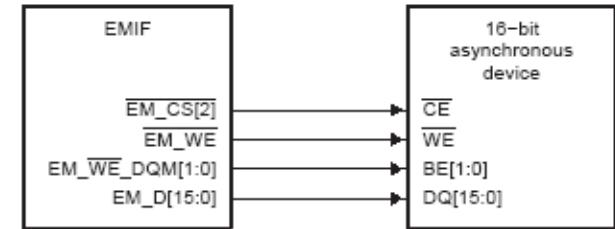

图a 给出了EMIF与一个字节使能的外部存储器的接口图。使用这个接口时EMIF要工作在选择触发模式，这样EM\_WE\_DQM就作为字节使能端工作。

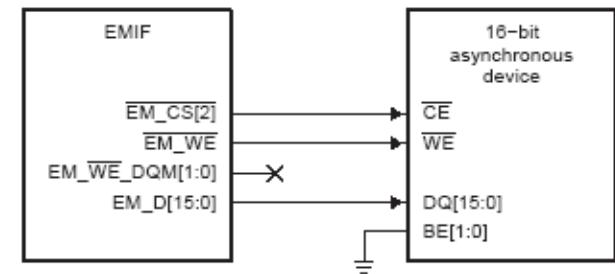

图b给出了当EMIF同一个字节使能的外部存储器的接口时，也可以处于WE触发模式，但是此时BE[1:0]要被置为低电平，而不是跟EM\_WE\_DQM[1:0]引脚相连。在这种接口状态下，不能进行字节写操作。

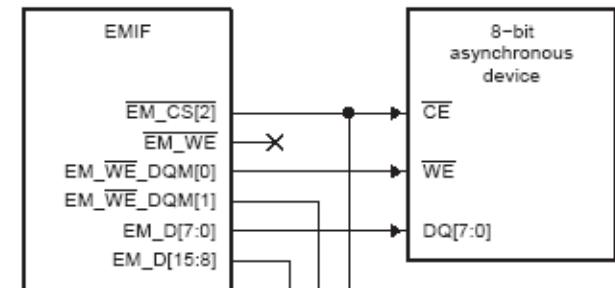

图c EMIF同多个8位存储器的接口图。在这种情况下，EM\_WE\_DQM信号跟存储器的WE相连，使用这个接口时EMIF要工作在WE触发模式，这样就可以对外部存储器进行字节操作。

(a)

(b)

(c)

## 3.3.5 异步控制器和接口

### 异步1配置寄存器(A1CR)

| 参数                | 说明                                                                                                                                    |

|-------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| SS                | 选择触发模式。SS = 0时选择WE触发模式， SS = 1时选择触发模式                                                                                                 |

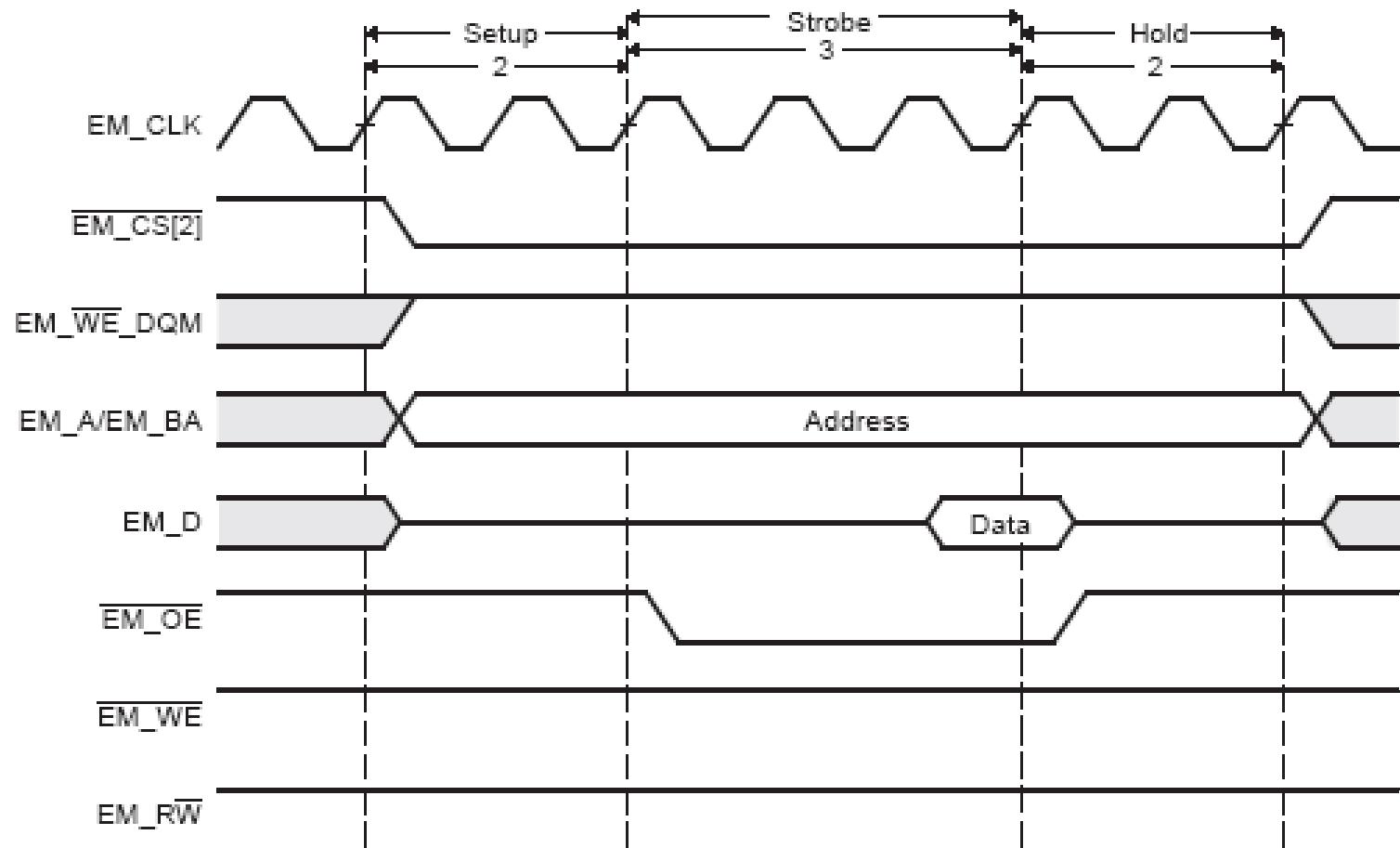

| W_SETUP/R_SETUP   | 读/写建立时间宽度<br>这些位定义了地址引脚(EM_A 和 EM_BA), 字节使能(EM_WE_DQM), 异步片选使能(EM_CS[2])在读触发(ARE)和写触发(EM_WE)信号下落前的EMIF时钟周期数, 至少一个时钟周期。                |

| W_STROBE/R_STROBE | 读/写触发时间宽度<br>这些位定义了读触发引脚(ARE)和写触发引脚(WE)上升沿和下降沿之间的EMIF时钟周期数, 至少一个时钟周期。                                                                 |

| W_HOLD/R_HOLD     | 读写保持时间宽度<br>这些位定义了地址引脚(EM_A 和 EM_BA), 字节使能(EM_WE_DQM), 异步片选使能(EM_CS[2])在读触发(ARE)和写触发(EM_WE)信号上升前的EMIF时钟周期数, 至少一个时钟周期。                 |

| ASIZE             | 异步器件数据总线宽度<br><b>ASIZE</b> = 0时选择8位总线<br><b>ASIZE</b> = 1时选择16位总线<br><b>ASIZE</b> = 2时选择32位总线<br>配置 <b>ASIZE</b> 位确定了EM_A和EM_BA引脚的功能。 |

### 3.3.5 异步控制器和接口

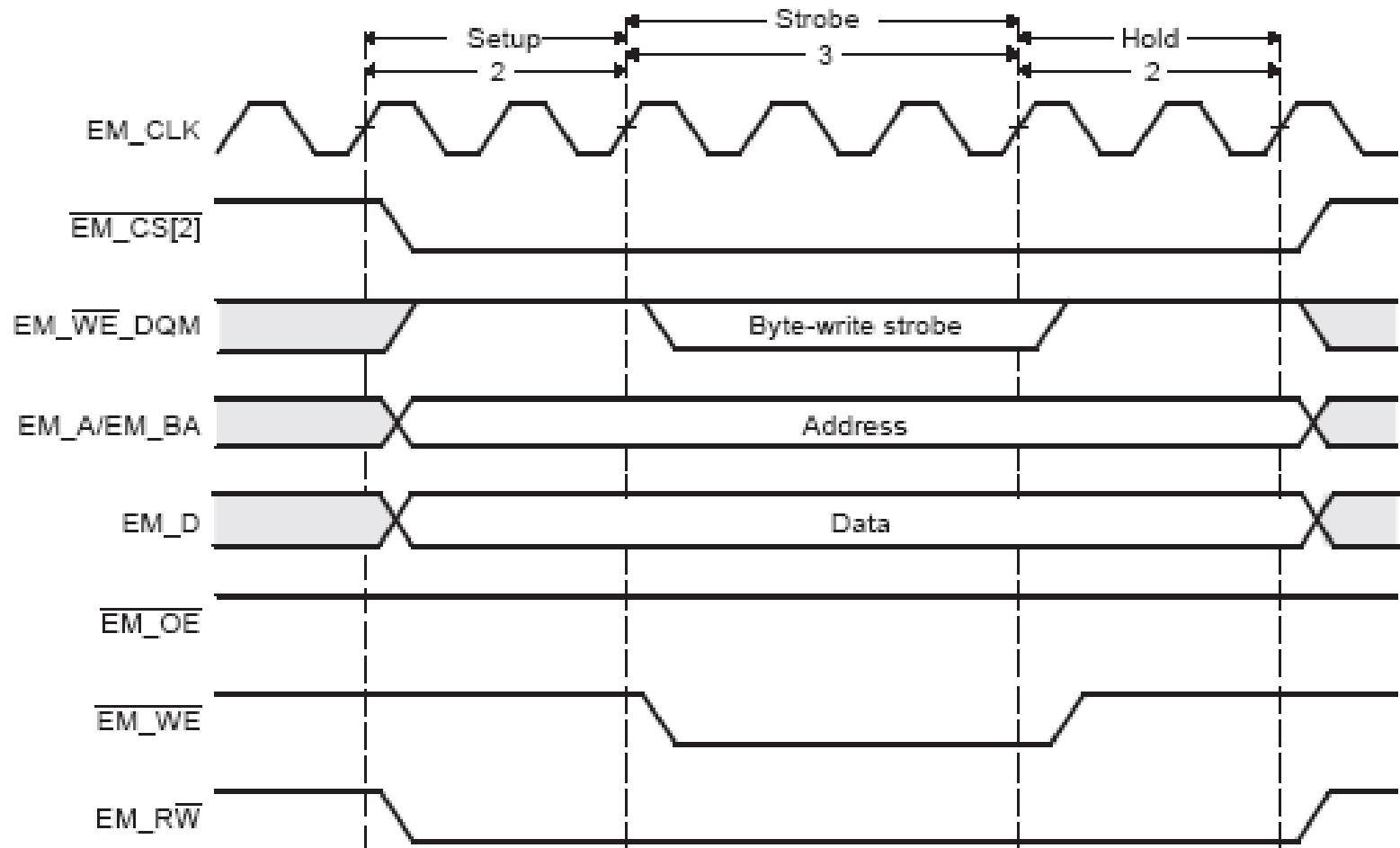

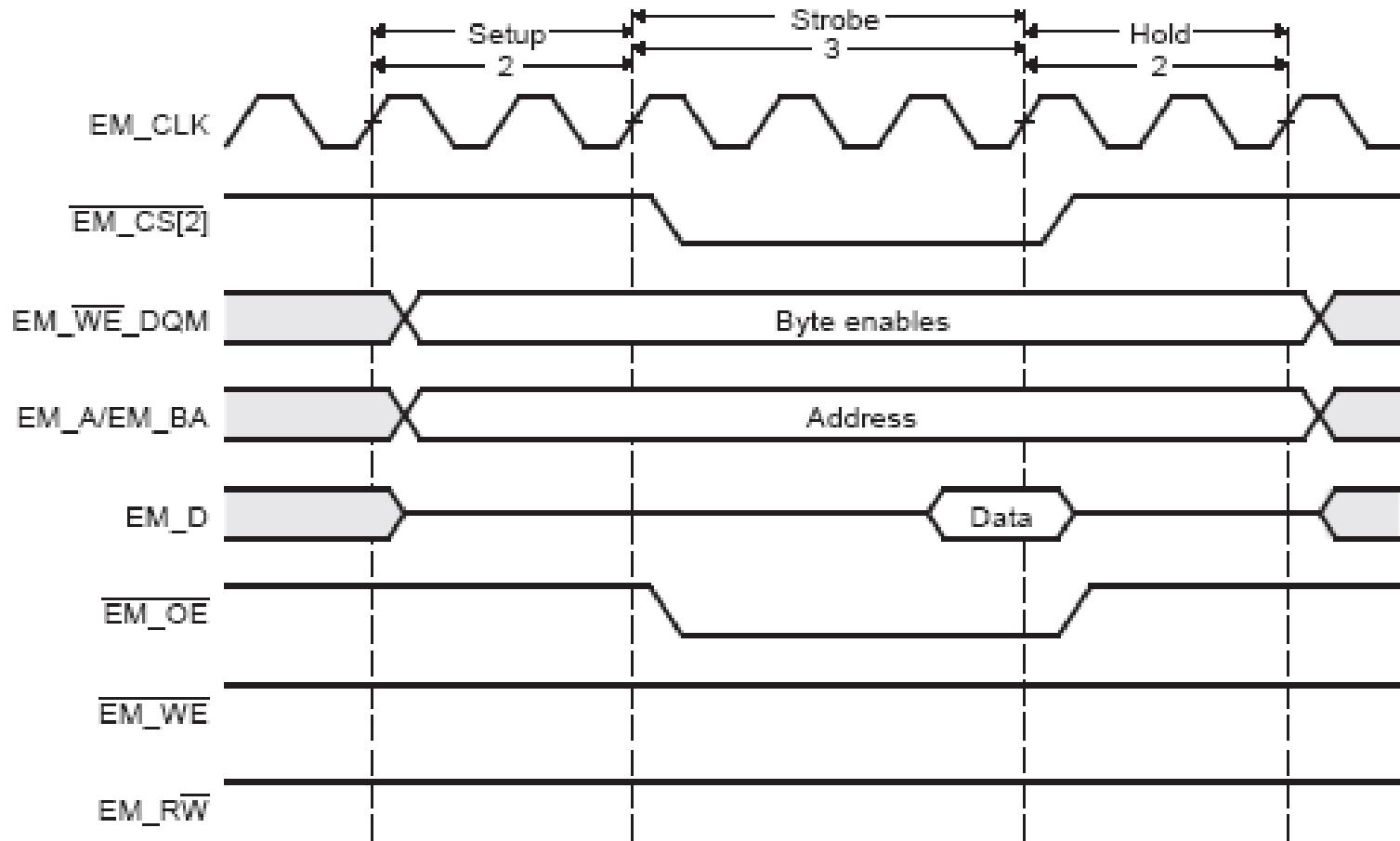

**WE**触发模式下异步读周期的时序

### 3.3.5 异步控制器和接口

**WE**触发模式下异步写周期的时序

### 3.3.5 异步控制器和接口

选择触发模式下异步读周期的时序

### 3.3.5 异步控制器和接口

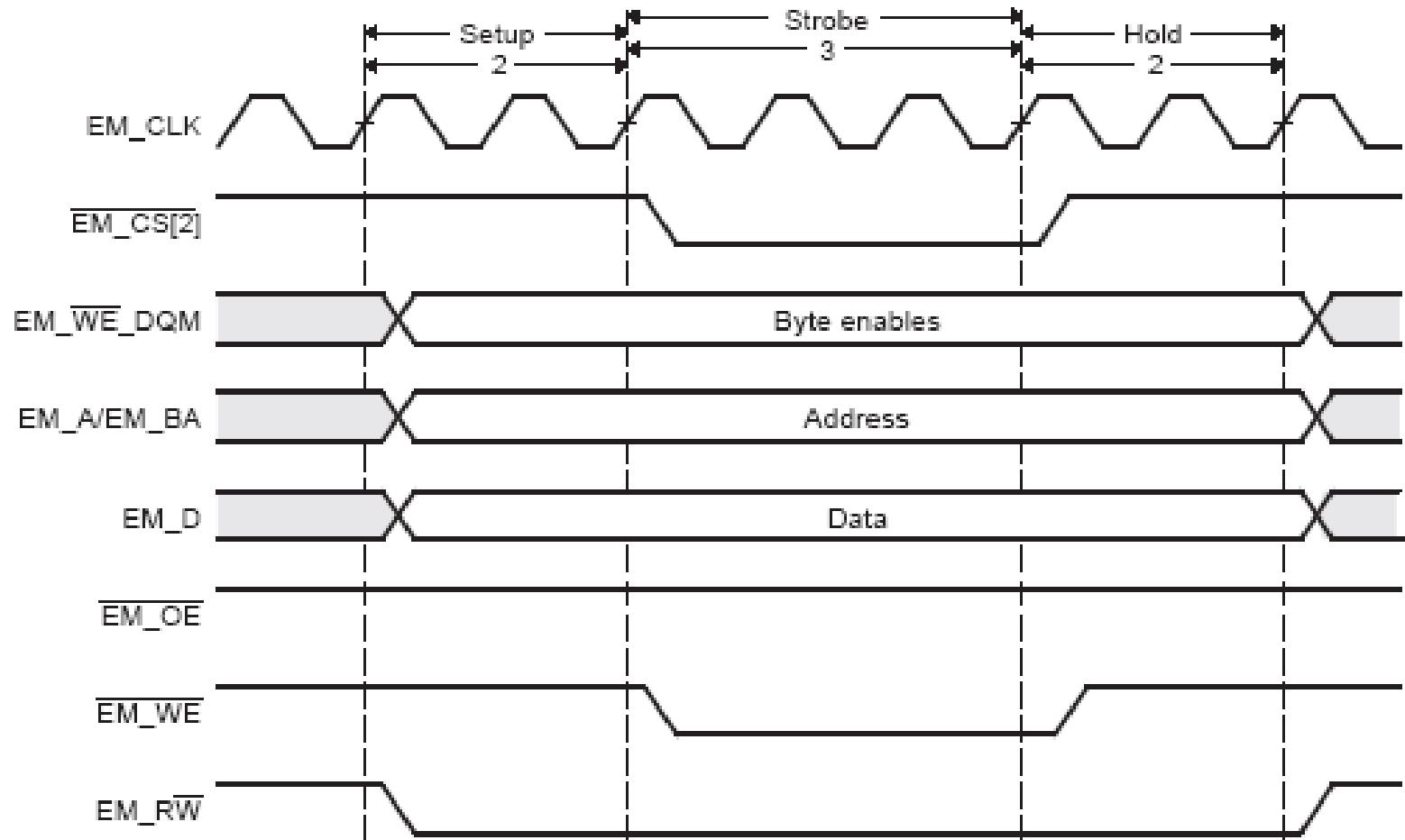

选择触发模式下异步写周期的时序

## 3.4 配置举例

EMIF与SDRAM和Flash的硬件连接图

Flash有三个地址输入源

EM\_WE引脚接到了Flash的WE输入端，EMIF运行在选择触发模式下

## 3.4.2 SDRAM接口配置

### 1). 对PLL的编程

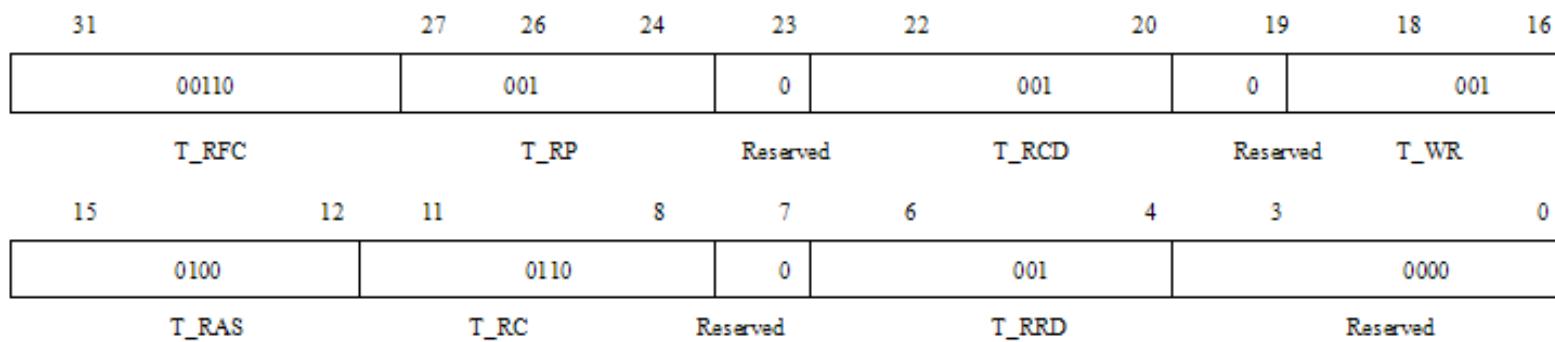

### 2). SDRAM时序寄存器(SDTIMR)的设置

| 字段    | 公式                                   | MT48LC4M16A2-75数据手册上的值                     | 计算值 |

|-------|--------------------------------------|--------------------------------------------|-----|

| T_RFC | $T_{RFC} \geq (tRFC * fEM\_CLK) - 1$ | $tRC = 68 \text{ ns (min)}$                | 6   |

| T_RP  | $T_{RP} \geq (tRP * fEM\_CLK) - 1$   | $tRP = 20 \text{ ns (min)}$                | 1   |

| T_RCD | $T_{RCD} \geq (tRCD * fEM\_CLK) - 1$ | $tRCD = 20 \text{ ns (min)}$               | 1   |

| T_WR  | $T_{WR} \geq (tWR * fEM\_CLK) - 1$   | $tRDL = 2 \text{ CLK} = 20\text{ns (min)}$ | 1   |

| T_RAS | $T_{RAS} \geq (tRAS * fEM\_CLK) - 1$ | $tRAS = 49 \text{ ns (min)}$               | 4   |

| T_RC  | $T_{RC} \geq (tRC * fEM\_CLK) - 1$   | $tRC = 68 \text{ ns (min)}$                | 6   |

| T_RRD | $T_{RRD} \geq (tRRD * fEM\_CLK) - 1$ | $tRRD = 14 \text{ ns (min)}$               | 1   |

## 3.4.2 SDRAM接口配置

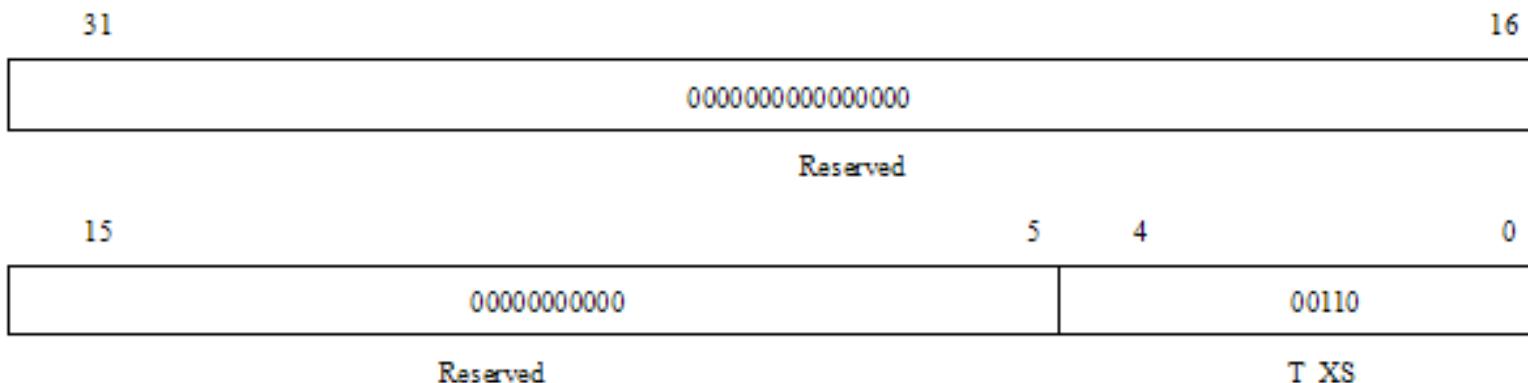

### 3). SDRAM自刷新退出时序寄存器(SDSRETR)的设置

| 字段   | 公式                                  | MT48LC4M16A2-75数据手册上的值      | 计算值 |

|------|-------------------------------------|-----------------------------|-----|

| T_XS | $T_{XS} \geq (tXSR * fEM\_CLK) - 1$ | $tRC = 68 \text{ ns (min)}$ | 6   |

## 3.4.2 SDRAM接口配置

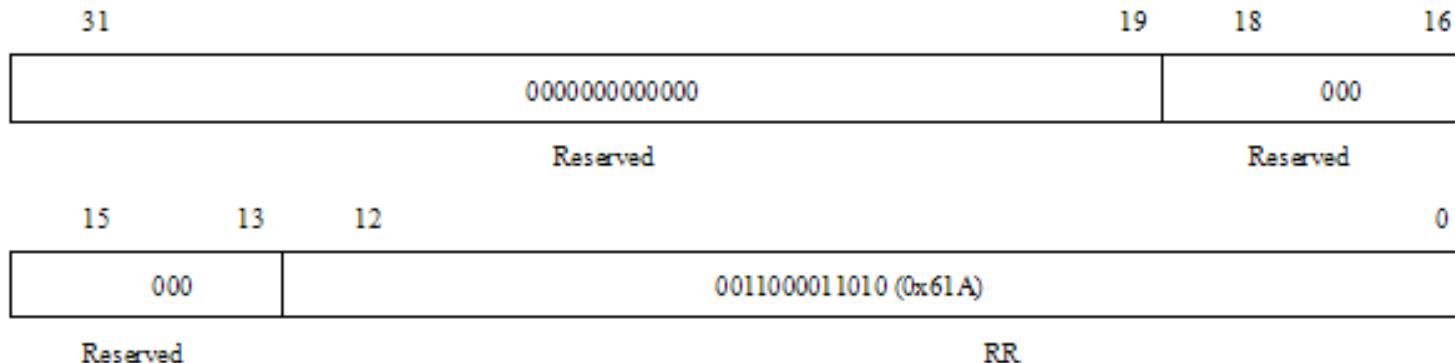

### 4). SDRAM刷新控制寄存器(SDRCR)的设置

| 字段 | 公式                                            | 数据手册数值                                                                            | 计算值                            |

|----|-----------------------------------------------|-----------------------------------------------------------------------------------|--------------------------------|

| RR | $RR \leq fEM\_CLK * tRefreshPeriod / ncycles$ | $tRefreshPeriod = 64ms;$<br>$ncycles = 4096$<br>EMIF时钟频率:<br>$fEM\_CLK = 100 MHz$ | $RR = 1562$ 周期<br>$= 0x61A$ 周期 |

## 3.4.2 SDRAM接口配置

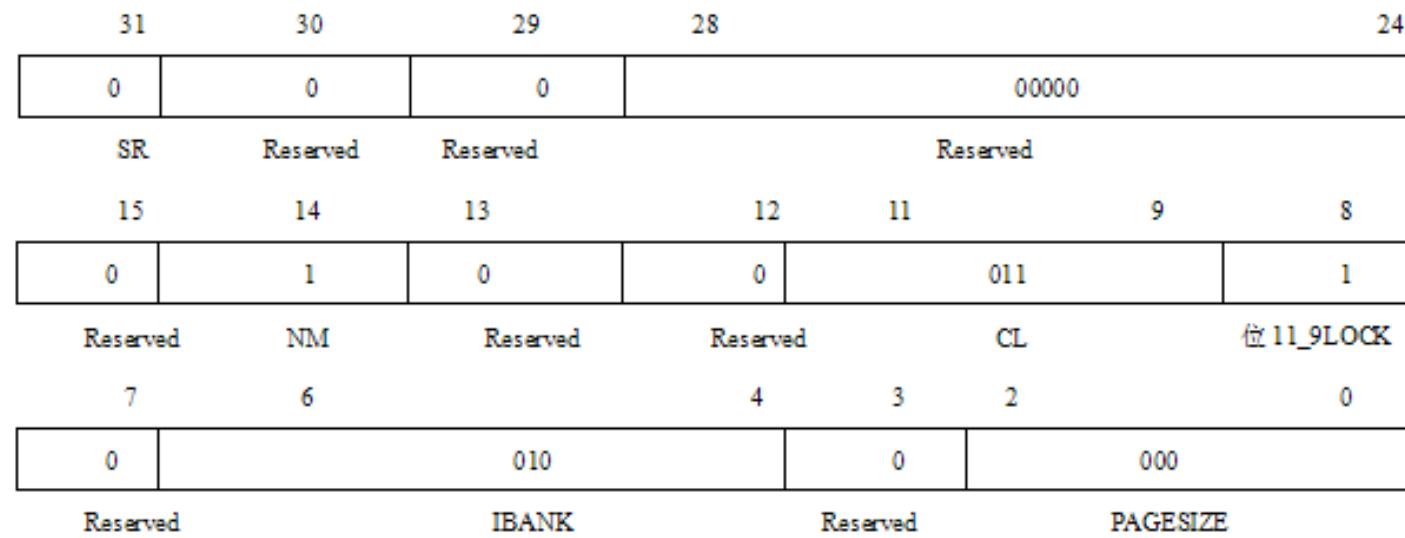

### 5). SDRAM配置寄存器(SDCR)的设置

| 字段        | 值    | 目的             |

|-----------|------|----------------|

| SR        | 0b   | 避免EMIF进入自刷新状态  |

| NM        | 1b   | 配置EMIF为16位数据总线 |

| CL        | 011b | 选择CAS延迟3       |

| 位11_9LOCK | 1b   | 允许写入CL区        |

| IBANK     | 010B | 选择4个内部SDRAM存储区 |

| PAGESIZE  | 0b   | 选择256字的页面      |