# VS1005g - Audio Processing Platform IC

## **Analog Hardware Features**

- Three channels of 24-bit audio ADC

- Two 24-bit audio DACs

- Stereo earphone driver for 30  $\Omega$  load

- internal microphone amplifiers

- Stereo FM radio receiver with RDS

- 10 bit ADC, 3-5 exteranal inputs

- Operation from single power supply, four programmable internal regulators

## **Digital Hardware Features**

- 100 MIPS VS\_DSP<sup>4</sup> processor core

- 128 kB program RAM (32 kWord)

- 128 kB data RAM (64 kWord)

- Protected 8 Mbit FLASH (Optional)

- USB 2.0 High Speed (480 Mbit/s) Device/Host

- I2S and SPDIF digital audio interfaces

- NAND FLASH interface with EEC

- SD Card interface

- 2 SPI bus interfaces

- 10BaseT Ethernet controller

- UART interface

- All digital pins are user configurable for general purpose IO

- Flexible clock selection, default operation from 12.288 MHz

- Internal PLL clock multiplier for digital logic

- RTC with battery backed memory

- Reed-Solomon error correction

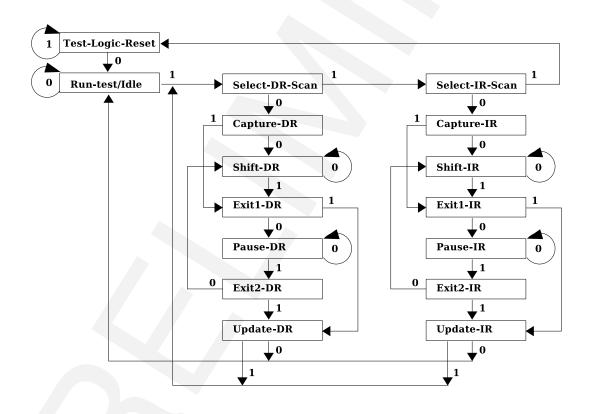

- HW support for debug with VSIDE via JTAG

## **Firmware and MegaLib Features**

- Decoders: MP3, WMA, Ogg Vorbis, AAC, HE-AAC, FLAC, WAV PCM

- Encoders: MP3, Ogg Vorbis, WAV PCM

- File I/O for SD cards and NAND flash

- FM tuner and RDS decoder

- USB host and slave libraries

- Graphical display with resistive touch panel

- Extensive audio DSP library

- IP stack of Ethernet

- Flexible boot options

- Extensive customization with VSIDE

### Applications

- Portable Recorders

- Digital Docking Stations

- MP3 Players

- Internet Radio

- Wireless Headphones

- Audio Co-processor

## Overview

VS1005 is a flexible audio platform device. It is built around VS\_DSP<sup>4</sup>, which is a powerful DSP (Digital Signal Processor) core. The digital interfaces provide flexible access to external devices in stand alone application and flexible digital audio data inputs and outputs when the device is used as an audio signal processor in more complex systems. The analog interfaces provide high quality audio inputs and outputs and the control ADC can be used for example for interfacing a resistive touch panel.

VS1005 has an embedded FLASH memory of 8 Mbits (1 MBytes) for customization by VLSI, customers or third parties. The firmware and hardware are designed to completely prevent access to the FLASH in protected mode. After programming, VS1005 can be booted from the embedded memory as a fully customized stand-alone audio processor.

Product is offered in six different variants. See section 3. for details.

Figure 1: vs1005 photo

# Contents

| VS | S1005 Front Page 1 |                                                 |    |  |  |  |

|----|--------------------|-------------------------------------------------|----|--|--|--|

| 1  | Discl              | aimer                                           | 7  |  |  |  |

| 2  | Defin              | itions                                          | 7  |  |  |  |

| 3  | Produ              | uct Variants                                    | 7  |  |  |  |

| 4  | Chara              | acteristics & Specifications                    | 7  |  |  |  |

|    | 4.1                | Absolute Maximum Ratings                        | 7  |  |  |  |

|    | 4.2                | Recommended Operating Conditions                | 8  |  |  |  |

|    | 4.3                | Analog Characteristics of Audio Outputs         | 9  |  |  |  |

|    | 4.4                | Analog Characteristics of Audio Inputs          | 10 |  |  |  |

|    | 4.5                | SAR Characteristics                             | 10 |  |  |  |

|    | 4.6                | FM Characteristics                              | 10 |  |  |  |

|    | 4.7                | Analog Characteristics of Regulators            | 11 |  |  |  |

|    | 4.8                | Analog Characteristics of VHIGH voltage monitor | 12 |  |  |  |

|    | 4.9                | Analog Characteristics of CVDD voltage monitor  | 12 |  |  |  |

|    | 4.10               | Digital Characteristics                         | 12 |  |  |  |

| 5  | Packa              | age and Pin Descriptions                        | 13 |  |  |  |

|    | 5.1                | Packages                                        | 13 |  |  |  |

|    | 5.2                | Pin Assignments                                 | 15 |  |  |  |

|    | 5.3                | Vs1005 Pin Descriptions                         | 16 |  |  |  |

|    |                    | 5.3.1 PCB Layout Recommendations                | 18 |  |  |  |

| 6  | Exam               | nple Schematic                                  | 19 |  |  |  |

| 7  | VS10               | 05 General Description                          | 20 |  |  |  |

|    | 7.1                | VS1005 Internal Architecture                    | 21 |  |  |  |

|    |                    | 7.1.1 Regulator Section                         | 21 |  |  |  |

|    |                    | 7.1.2 IO Section                                | 22 |  |  |  |

CONTENTS

|    |       | 7.1.3       | Digital Section                        | 22 |

|----|-------|-------------|----------------------------------------|----|

|    | 7.2   | Analog Se   | ection                                 | 24 |

| 8  | Oscil | lator and   | Reset Configuration                    | 25 |

| 9  | Firm  | ware Oper   | ation                                  | 26 |

|    | 9.1   | SPI Boot    |                                        | 26 |

|    | 9.2   | NAND FL     | ASH Probe                              | 27 |

|    | 9.3   | UART Bo     | ot/Monitor                             | 28 |

|    | 9.4   | Default Fi  | rmware Features                        | 29 |

|    |       | 9.4.1       | USB Mass Storage and Audio Device      | 29 |

|    |       | 9.4.2       | Default Player Application             | 29 |

|    | 9.5   | Supported   | d Audio Codecs                         | 31 |

|    |       | 9.5.1       | Supported MP3 (MPEG layer III) Formats | 31 |

| 10 | VS10  | 05 Periphe  | erals and Registers                    | 32 |

|    | 10.1  | The Proce   | essor Core                             | 32 |

|    | 10.2  | VS1005 N    | Memory Map                             | 32 |

|    | 10.3  | VS1005 F    | Peripherals                            | 33 |

|    | 10.4  | Interrupt ( | Controller                             | 34 |

|    |       | 10.4.1      | Interrupt Controller Registers         | 35 |

|    |       | 10.4.2      | Enable INT_ENABLE[L/H][0/1]            | 35 |

|    |       | 10.4.3      | Origin INT_ORIGIN[0/1]                 | 35 |

|    |       | 10.4.4      | Vector INT_VECTOR                      | 36 |

|    |       | 10.4.5      | Enable Counter INT_ENCOUNT             | 36 |

|    |       | 10.4.6      | Global Disable INT_GLOB_DIS            | 36 |

|    |       | 10.4.7      | Global Enable INT_GLOB_EN              | 36 |

|    | 10.5  | DSP Cloc    | k Domain Registers                     | 37 |

|    |       | 10.5.1      | General Purpose Software Registers     | 37 |

|    |       | 10.5.2      | Peripheral IO control                  | 37 |

|    |       | 10.5.3      | PLL clock control                      | 37 |

CONTENTS

| 10.6 XTAL Clock Domain Registers                        | 39 |

|---------------------------------------------------------|----|

| 10.6.1 Analog Control Registers                         | 39 |

| 10.6.2 Regulator and Peripheral Clock Control Registers | 41 |

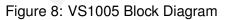

| 10.7 24-bit Digital to Analog Converter (DAC)           | 43 |

| 10.7.1 Configuring Analog DAC Modules                   | 43 |

| 10.8 Audio Interfaces                                   | 44 |

| 10.8.1 DAC volume control                               | 44 |

| 10.8.2 DAC Offset Registers                             | 44 |

| 10.8.3 Sample Rate Converter (SRC) Registers            | 45 |

| 10.9 SPI Peripherals                                    | 47 |

| 10.10 Common Data Interfaces                            | 51 |

| 10.10.1 Ethernet Controller                             | 54 |

| 10.10.2 Reed-Solomon Codec                              | 57 |

| 10.10.3 Nand Flash Interface                            | 61 |

| 10.10.4 SD Card Interface                               | 63 |

| 10.11 USB Peripheral                                    | 65 |

| 10.11.1 USB Peripheral Registers                        | 66 |

| 10.11.2 USB Clocking Modes                              | 69 |

| 10.11.3 USB Host                                        | 69 |

| 10.12 Interruptable General purpose IO ports 0-2        | 70 |

| 10.13 S/PDIF Peripheral                                 | 72 |

| 10.13.1 S/PDIF Receiver                                 | 72 |

| 10.13.2 S/PDIF Receiver Registers                       | 73 |

| 10.13.3 S/PDIF Transmitter                              | 75 |

| 10.13.4 S/PDIF Transmitter Registers                    | 76 |

| 10.14 Uart Peripheral                                   | 79 |

| 10.14.1 Uart Peripheral Registers                       | 79 |

| 10.15 Watchdog Peripheral                               | 81 |

| 10.15.1 Watchdog Registers                              | 81 |

| 10.16 Line and Mic Inputs                               | 82 |

CONTENTS

| 10.16.1 Configuring Analog Modules for Mic and Line Input Modes 83 |

|--------------------------------------------------------------------|

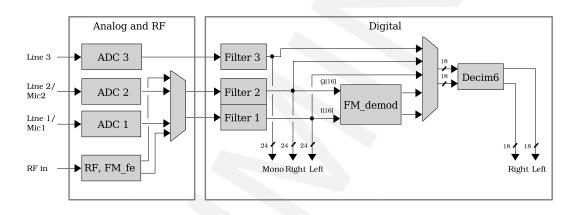

| 10.16.2 Digital Filter Operation Modes                             |

| 10.17 FM Receiver                                                  |

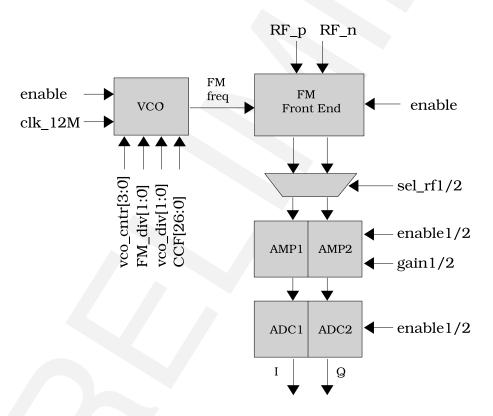

| 10.17.1 Configuring RF and Analog Modules for FM Receiver Mode 85  |

| 10.17.2 Configuring FM Demodulator                                 |

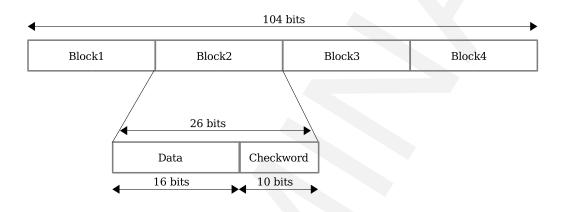

| 10.17.3 Radio Data System (RDS)                                    |

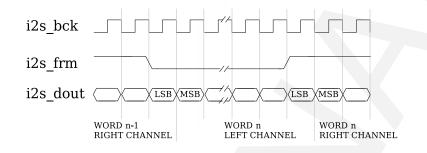

| 10.18 I2S Peripheral                                               |

| 10.18.1 I2S Peripheral Registers                                   |

| 10.19 Timer Peripheral                                             |

| 10.19.1 Timer Peripheral Registers                                 |

| 10.20 Real Time Clock (RTC)                                        |

| 10.20.1 RTC Peripheral Registers                                   |

| 10.21 10-Bit Analog-to-Digital Converter (ADC)                     |

| 10.22 Pulse Width Modulation Unit                                  |

| 10.23 Special Features                                             |

| 10.23.1 Software Protection                                        |

| 11 VS1005 Debugger 100                                             |

| 12 Document Version Changes103                                     |

| 13 Contact Information 104                                         |

# **List of Figures**

| 1  | vs1005 photo                                        | 1  |

|----|-----------------------------------------------------|----|

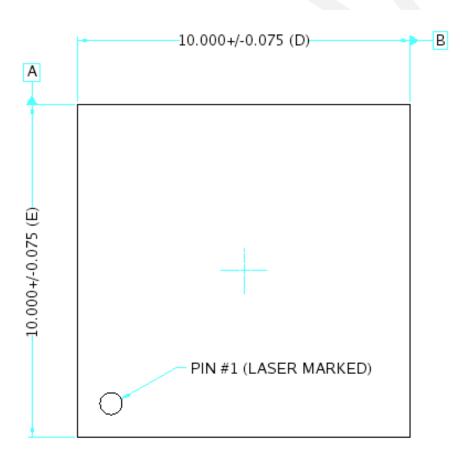

| 2  | Top View, LFGA-88                                   | 13 |

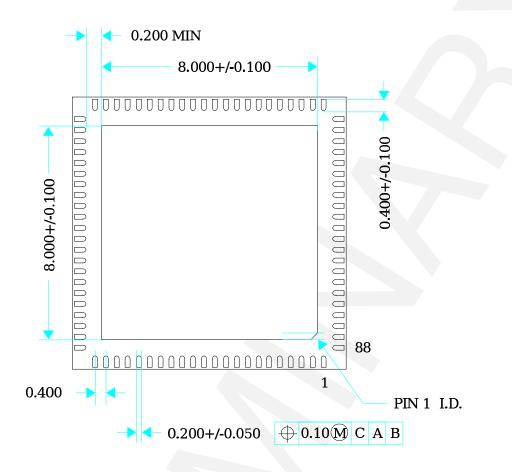

| 3  | Bottom View, LFGA-88.                               | 14 |

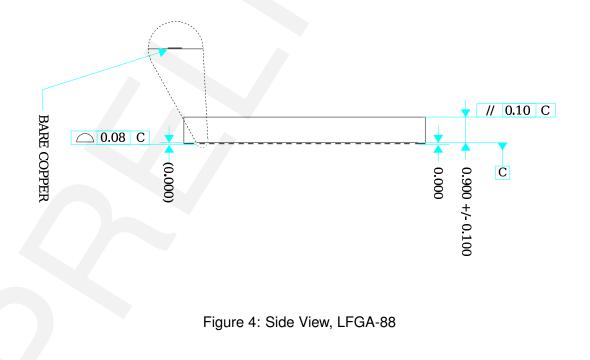

| 4  | Side View, LFGA-88                                  | 14 |

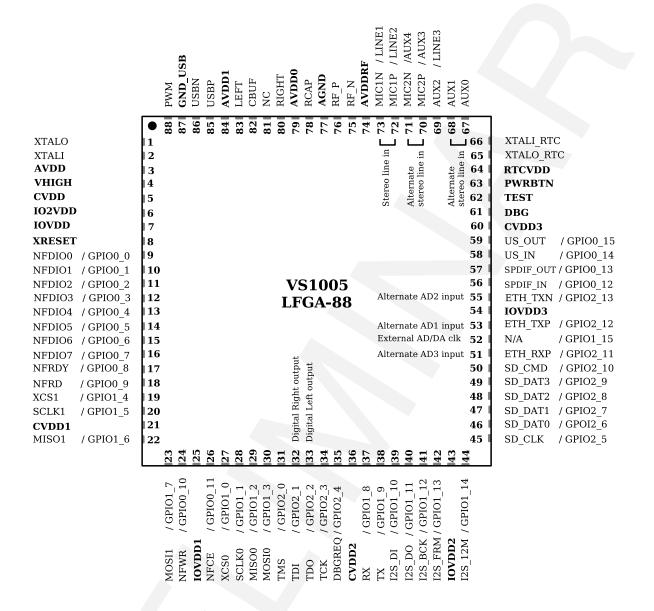

| 5  | vs1005 88-pin LFGA Pin Assignment.                  | 15 |

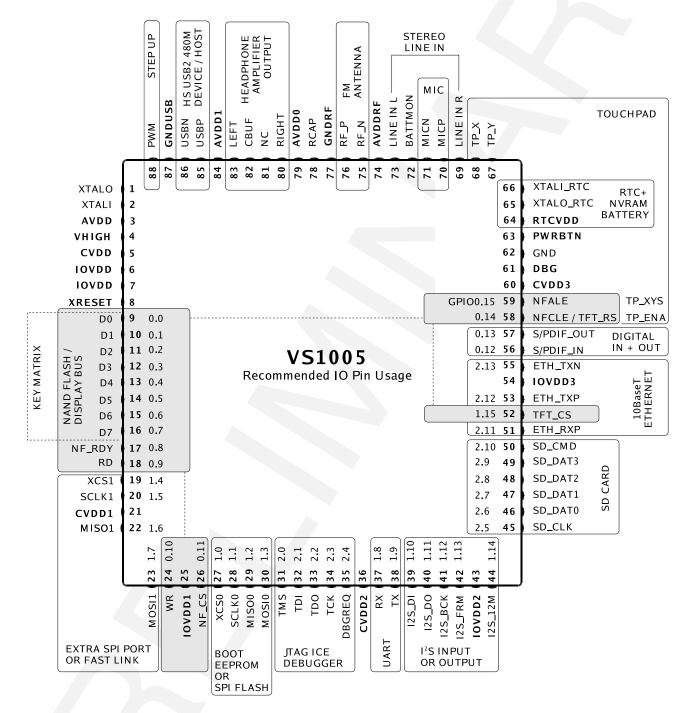

| 6  | vs1005 default pin usage.                           | 19 |

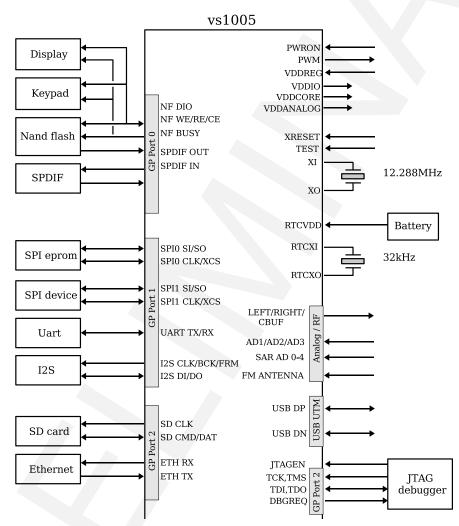

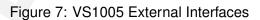

| 7  | VS1005 External Interfaces                          | 20 |

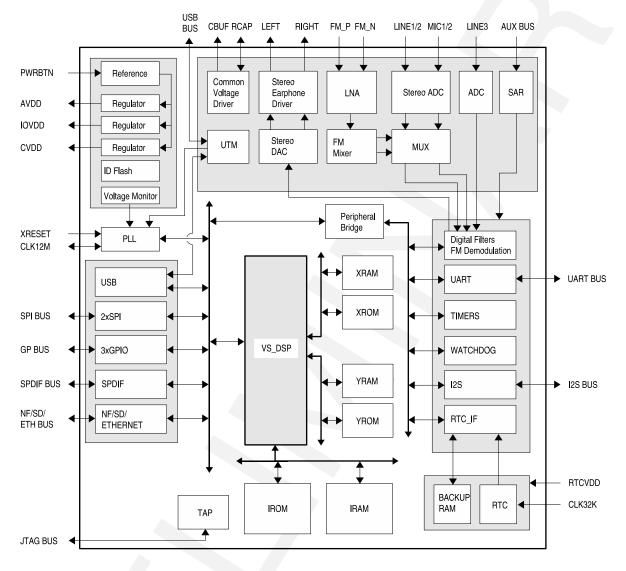

| 8  | VS1005 Block Diagram                                | 21 |

| 9  | User's Memory Map.                                  | 32 |

| 10 | Vs1005 audio path                                   | 44 |

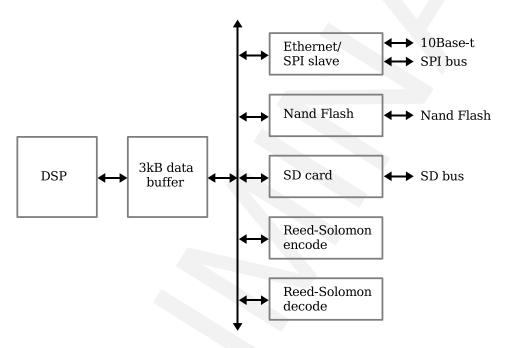

| 11 | Block Diagram of Data Interfaces                    | 51 |

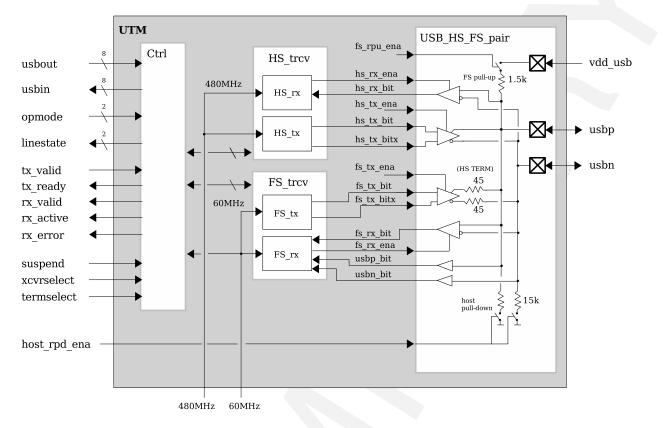

| 12 | VS1005 USB Block Diagram.                           | 65 |

| 13 | VS1005 UTM Functional Block Diagram.                | 66 |

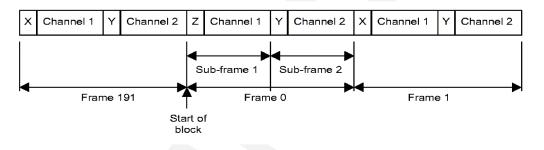

| 14 | S/PDIF Frame Format                                 | 72 |

| 15 | S/PDIF Sub-Frame Format.                            | 72 |

| 16 | RS232 Serial Interface Protocol                     | 79 |

| 17 | AD and FM signal paths                              | 82 |

| 18 | Block Diagram of FM Receiver, RF and analog section | 85 |

| 19 | RDS data structure                                  | 89 |

| 20 | I2s Frame format                                    | 90 |

| 21 | JTAG state machine.                                 | 00 |

# 1 Disclaimer

All properties and figures are subject to change.

# 2 Definitions

```

B Byte, 8 bits.

```

**b** Bit.

Ki "Kibi" =  $2^{10}$  = 1024 (IEC 60027-2).

**Mi** "Mebi" =  $2^{20}$  = 1048576 (IEC 60027-2).

**VS\_DSP** VLSI Solution's DSP core.

W Word. In VS\_DSP, instruction words are 32-bit and data words are 16-bit wide.

## 3 Product Variants

| Device ID (Order Code) | Mp3 Encoder | Mp3 decoder | Embedded 8 Mbit Flash |

|------------------------|-------------|-------------|-----------------------|

| VS1005G-Q              |             | X           |                       |

| VS1005G-F-Q            |             | Х           | X                     |

| VS1205G-Q              | Х           | Х           |                       |

| VS1205G-F-Q            | Х           | Х           | Х                     |

| VS8005G-Q              |             |             |                       |

| VS8005G-F-Q            |             |             | Х                     |

# 4 Characteristics & Specifications

#### 4.1 Absolute Maximum Ratings

| Parameter                                 | Symbol               | Min  | Max                    | Unit |

|-------------------------------------------|----------------------|------|------------------------|------|

| Regulator input voltage                   | VHIGH                | -0.3 | 5.25                   | V    |

| Analog Positive Supply                    | AVDD                 | -0.3 | 3.6                    | V    |

| Digital Positive Supply                   | CVDD                 | -0.3 | 1.95                   | V    |

| Digital RTC Supply                        | RTCVDD               | -0.3 | 1.95                   | V    |

| I/O Positive Supply                       | IOVDD                | -0.3 | 3.6                    | V    |

| Voltage at Any Digital Input <sup>3</sup> |                      | -0.3 | IOVDD+0.3 <sup>1</sup> | V    |

| Voltage at power Button                   | PWRBTN               | -0.3 | 3.6                    | V    |

| Voltage at RTC Pins                       | XTALI_RTC, XTALO_RTC | -0.3 | CVDD+0.3 <sup>4</sup>  | V    |

| Total Injected Current on Pins            |                      |      | $\pm$ 200 $^2$         | mA   |

| Operating Temperature                     |                      | -40  | +85                    | °C   |

| Storage Temperature                       |                      | -65  | +150                   | °C   |

<sup>1</sup> Must not exceed 3.6 V

- <sup>2</sup> Latch-up limit

- <sup>3</sup> Except RTC and pwrbtn pin

$^4$  Must not exceed 1.95V

VS1005g Datasheet 4 CHARACTERISTICS & SPECIFICATIONS

#### 4.2 Recommended Operating Conditions

| Voltage Specification                |           |          |     |      |      |  |  |  |  |

|--------------------------------------|-----------|----------|-----|------|------|--|--|--|--|

| Parameter                            | Symbol    | Min      | Тур | Max  | Unit |  |  |  |  |

| Operating temperature                |           | -40      |     | +85  | °C   |  |  |  |  |

| Analog and digital ground $^1$       | AGND DGND |          | 0.0 |      | V    |  |  |  |  |

| Regulator input voltage <sup>2</sup> | VHIGH     | AVDD+0.3 | 4.0 | 5.25 | V    |  |  |  |  |

| Analog positive supply <sup>3</sup>  | AVDD      | 2.75     | 2.8 | 3.6  | V    |  |  |  |  |

| Digital positive supply $^3$         | CVDD      | 1.65     | 1.8 | 1.95 | V    |  |  |  |  |

| Digital RTC supply                   | RTCVDD    | 1.2      | 1.5 | 1.95 | V    |  |  |  |  |

| I/O positive supply <sup>3</sup>     | IOVDD     | 1.8      | 2.8 | 3.6  | V    |  |  |  |  |

<sup>1</sup> Must be connected together as close the device as possible for latch-up immunity.

<sup>2</sup> At least 4.0 V is required for compliant USB level.

<sup>3</sup> Regulator output of the device.

| Oscillator Specification                   |           |     |                     |     |      |  |  |  |

|--------------------------------------------|-----------|-----|---------------------|-----|------|--|--|--|

| Parameter                                  | Symbol    | Min | Тур                 | Max | Unit |  |  |  |

| Input clock frequency <sup>1</sup>         | XTALI     | 11  | 12.288 <sup>2</sup> | 13  | MHz  |  |  |  |

| Input clock duty cycle                     |           | 40  | 50                  | 60  | %    |  |  |  |

| Oscillator frequency tolerance             |           |     | +/-10               |     | ppm  |  |  |  |

| Startup time                               |           |     | 1                   |     | ms   |  |  |  |

| Internal clock frequency, USB connected    | CLKU      | 60  |                     | 60  | MHz  |  |  |  |

| Internal clock frequency, USB disconnected | CLKI      |     |                     | 98  | MHz  |  |  |  |

| RTC clock frequency <sup>3</sup>           | XTALI_RTC |     | 32768               |     | Hz   |  |  |  |

| RTC frequency tolerance                    |           |     | +/-100              |     | ppm  |  |  |  |

| RTC oscillator startup time                |           |     | 1000                |     | ms   |  |  |  |

<sup>1</sup> The maximum sample rate that can be played with correct speed is XTALI/128. With 11 MHz XTALI sample rates over 85937 Hz are played at 85937 Hz.

$^2$  When full speed (FS) or high speed (HS) USB is used it is recommended that XTAL of 12.0MHz 0r 12.288MHz is used.  $^3$  The 32kHz crystal is optional, but required for RTC time counter.

VS1005g Datasheet 4 CHARACTERISTICS & SPECIFICATIONS

#### 4.3 Analog Characteristics of Audio Outputs

Unless otherwise noted: AVDD=3.6V, CVDD=1.8V, IOVDD=2.8V, Vref=1.6V, TA=+25°C, XTALI=12 MHz, Internal Clock Multiplier  $3.0\times$ . DAC tested with full-scale output sinewave, measurement bandwidth 20..20000 Hz, analog output load: LEFT to CBUF 30  $\Omega$ , RIGHT to CBUF 30  $\Omega$ . Microphone test amplitude 50 mVpp, f=1 kHz, Line input test amplitude 2.2 Vpp, f=1 kHz. FM test signal input level -70 dBm, deviation 75 kHz, pre-emphasis 50 us, f=1 kHz.

| DAC Characteristics                                  |        |       |                        |                  |      |  |  |

|------------------------------------------------------|--------|-------|------------------------|------------------|------|--|--|

| Parameter                                            | Symbol | Min   | Тур                    | Max              | Unit |  |  |

| DAC Resolution                                       |        |       | 24                     |                  | bits |  |  |

| Dynamic range (DAC unmuted, A-weighted, min gain)    | IDR    |       | 100                    |                  | dB   |  |  |

| S/N ratio (full scale signal, no load)               | SNR    |       | 92                     |                  | dB   |  |  |

| S/N ratio (full scale signal, 30 ohm load)           | SNRL   |       | 90                     |                  | dB   |  |  |

| Total harmonic distortion, -3dB level, no load       | THD    |       | 0.01                   |                  | %    |  |  |

| Total harmonic distortion, -3dB level, 30 ohm load   | THDL   |       | 0.05                   |                  | %    |  |  |

| Crosstalk (L/R to R/L), 30 ohm load, without CBUF 1  | XTALK1 |       | -75                    |                  | dB   |  |  |

| Crosstalk (L/R to R/L), 30 ohm load, with CBUF       | XTALK2 |       | -54                    |                  | dB   |  |  |

| Gain mismatch (L/R to R/L)                           | GERR   | -0.5  |                        | 0.5              | dB   |  |  |

| Frequency response                                   | AERR   | -0.05 |                        | 0.05             | dB   |  |  |

| Full scale output voltage                            | LEVEL  |       | 1.0                    |                  | Vrms |  |  |

| Deviation from linear phase                          | PH     |       | 0                      | 5                | 0    |  |  |

| Analog output load resistance                        | AOLR   |       | <b>30</b> <sup>2</sup> |                  | Ω    |  |  |

| Analog output load capacitance                       | AOLC   |       |                        | 100 <sup>3</sup> | pF   |  |  |

| DC level, V <sub>ref</sub> =1.2V (CBUF, LEFT, RIGHT) |        | 1.1   |                        | 1.3              | V    |  |  |

| DC level, V <sub>ref</sub> =1.6V (CBUF, LEFT, RIGHT) |        | 1.5   |                        | 1.7              | V    |  |  |

| CBUF disconnect current (short-circuit protection)   |        |       | 130                    | 200              | mA   |  |  |

<sup>1</sup> Loaded from Left/Right pin to analog ground via 100  $\mu$ F capacitors.

$^2$  AOLR may be lower than *Typical*, but distortion performance may be compromised. Also, there is a maximum current that the internal regulators can provide.

<sup>3</sup> CBUF must have external 10  $\Omega$  + 47 nF load, LEFT and RIGHT must have external 20  $\Omega$  + 10 nF load for optimum stability and ESD tolerance.

#### 4.4 Analog Characteristics of Audio Inputs

| ADC Characteristics                  |        |                        |       |                   |         |  |  |  |

|--------------------------------------|--------|------------------------|-------|-------------------|---------|--|--|--|

| Parameter                            | Symbol | Min                    | Тур   | Max               | Unit    |  |  |  |

| ADC Resolution                       |        |                        | 24    |                   | bits    |  |  |  |

| Microphone input amplifier gain      | MICG   |                        | 20    |                   | dB      |  |  |  |

| Microphone input amplitude           |        |                        | 50    | 140 <sup>1</sup>  | mVpp AC |  |  |  |

| Microphone Total Harmonic Distortion | MTHD   |                        | 0.02  | 0.10              | %       |  |  |  |

| Microphone S/N Ratio, A-weighted     | MSNR   | <b>50</b> <sup>2</sup> | 75    |                   | dB      |  |  |  |

| Line input amplitude                 |        |                        | 2200  | 2800 <sup>1</sup> | mVpp AC |  |  |  |

| Line input Total Harmonic Distortion | LTHD   |                        | 0.015 | 0.10              | %       |  |  |  |

| Line input S/N Ratio                 | LSNR   | <b>80</b> <sup>2</sup> | 90    | 100               | dB      |  |  |  |

| Sample rate                          |        | 24                     |       | 192               | kHz     |  |  |  |

| Line and Microphone input impedances |        |                        | 100   |                   | kΩ      |  |  |  |

$^{\rm 1}$  Above typical amplitude the Harmonic Distortion increases.

<sup>2</sup> Limit Min due to noise level of production tester.

#### 4.5 SAR Characteristics

| SAR Characteristics          |        |     |        |      |      |  |  |  |  |

|------------------------------|--------|-----|--------|------|------|--|--|--|--|

| Parameter                    | Symbol | Min | Тур    | Max  | Unit |  |  |  |  |

| SAR resolution               |        |     | 10     |      | bits |  |  |  |  |

| Input amplitude range        |        | 0   |        | AVDD | V    |  |  |  |  |

| SAR sample rate <sup>1</sup> |        |     |        | 100  | kHz  |  |  |  |  |

| Integral Nonlinearity        | INL    |     | +/-2   |      | LSB  |  |  |  |  |

| Differential Nonlinearity    | DNL    |     | +/-0.5 |      | LSB  |  |  |  |  |

<sup>1</sup> XTAL dependent

#### 4.6 FM Characteristics

| FM Characteristics                                                    |        |     |     |     |      |

|-----------------------------------------------------------------------|--------|-----|-----|-----|------|

| Parameter                                                             | Symbol | Min | Тур | Max | Unit |

| Channel frequency range, 10kHz steps                                  |        | 76  |     | 108 | MHz  |

| FM mono S/N Ratio, deviation 22kHz, Input level -50dBm <sup>1</sup>   | LSNR   |     | 72  |     | dB   |

| FM stereo S/N Ratio, deviation 45kHz, Input level -50dBm <sup>1</sup> | LSNR   |     | 47  |     | dB   |

| FM mono S/N Ratio, deviation 22kHz, Input level -90dBm <sup>1</sup>   | LSNR   |     | 45  |     | dB   |

| FM stereo S/N Ratio, deviation 45kHz, Input level -90dBm <sup>1</sup> | LSNR   |     | 27  |     | dB   |

| Total harmonic distortion, deviation 75kHz                            | THD    |     | 0.1 | 0.3 | %    |

| Stereo separation                                                     |        |     | 40  |     | dB   |

<sup>1</sup> Measured over whole FM band

### 4.7 Analog Characteristics of Regulators

| Parameter                                 | Symbol | Min  | Тур                    | Max  | Unit  |

|-------------------------------------------|--------|------|------------------------|------|-------|

| IOVDD                                     |        |      |                        |      |       |

| Recommended voltage setting range         |        | 1.7  |                        | 3.6  | V     |

| Voltage setting step size                 |        | 55   | 60                     | 65   | mV    |

| Default setting, reset mode <sup>1</sup>  |        |      | 1.8                    |      | V     |

| Default setting, active mode <sup>2</sup> |        |      | 1.8/3.6 <sup>3</sup>   |      | V     |

| Load regulation                           |        |      | 4.0                    |      | mV/mA |

| Line regulation from VHIGH                |        |      | 2.0                    |      | mV/V  |

| Continuous current                        |        |      | <b>30</b> <sup>4</sup> | 60   | mA    |

| IOVDD2                                    |        |      |                        |      |       |

| Recommended voltage setting range         |        | 1.7  |                        | 3.6  | V     |

| Voltage setting step size                 |        | 55   | 60                     | 65   | mV    |

| Default setting, reset mode <sup>1</sup>  |        |      | 1.8                    |      | V     |

| Default setting, active mode <sup>2</sup> |        |      | 1.8/3.6 <sup>3</sup>   |      | V     |

| Load regulation                           |        |      | 4.0                    |      | mV/mA |

| Line regulation from VHIGH                |        |      | 2.0                    |      | mV/V  |

| Continuous current                        |        |      | <b>30</b> <sup>4</sup> | 60   | mA    |

| CVDD                                      |        |      |                        |      |       |

| Recommended voltage setting range         |        | 1.65 |                        | 1.95 | V     |

| Voltage setting step size                 |        | 25   | 30                     | 35   | mV    |

| Default setting, reset mode <sup>1</sup>  |        |      | 1.8                    |      | V     |

| Default setting, active mode <sup>2</sup> |        |      | 1.8                    |      | V     |

| Continuous current                        |        |      | <b>25</b> <sup>4</sup> | 70   | mA    |

| Load regulation                           |        |      | 2.0                    |      | mV/mA |

| Line regulation from VHIGH                |        |      | 2.0                    |      | mV/V  |

| AVDD                                      |        |      |                        |      |       |

| Recommended voltage setting range         |        | 2.6  |                        | 3.6  | V     |

| Voltage setting step size                 |        | 35   | 40                     | 45   | mV    |

| Default setting, reset mode <sup>1</sup>  |        |      | 2.5                    |      | V     |

| Default setting, active mode <sup>2</sup> |        |      | 2.7                    |      | V     |

| Continuous current                        |        |      | <b>30</b> <sup>4</sup> | 70   | mA    |

| Load regulation                           |        |      | 1.5                    |      | mV/mA |

| Line regulation from VHIGH                |        |      | 2.0                    |      | mV/V  |

| PWRBTN                                    |        |      |                        |      |       |

| Minimum startup voltage                   |        |      | 0.9                    |      | V     |

| Minimum startup pulse                     |        |      | 100                    |      | ms    |

<sup>1</sup> Device enters reset mode when XRESET pin is pulled low.

<sup>2</sup> Device enters active mode when XRESET pin is pulled high after reset mode. Regulator settings can be modified when booted from external memory (see section 9).

<sup>3</sup> Depends on GPIO0\_7 pin status in boot (see section 9).

$^4$  Device is tested with a 30 mA load.

#### 4.8 Analog Characteristics of VHIGH voltage monitor

| Parameter       | Symbol | Min | Тур       | Max | Unit |

|-----------------|--------|-----|-----------|-----|------|

| Trigger voltage | AMON   |     | 1.07×AVDD |     | V    |

| Hysteresis      |        |     | 50        |     | mV   |

#### 4.9 Analog Characteristics of CVDD voltage monitor

| Parameter       | Symbol | Min  | Тур  | Max | Unit |

|-----------------|--------|------|------|-----|------|

| Trigger voltage | CMON   | 1.40 | 1.45 |     | V    |

| Hysteresis      |        |      | 2    |     | mV   |

#### 4.10 Digital Characteristics

| Parameter                                            | Symbol | Min                | Тур | Max                | Unit    |

|------------------------------------------------------|--------|--------------------|-----|--------------------|---------|

| High-Level Input Voltage                             |        | $0.7 \times IOVDD$ |     | IOVDD+0.3          | V       |

| Low-Level Input Voltage                              |        | -0.2               |     | $0.3 \times IOVDD$ | V       |

| High-Level Output Voltage, -1.0 mA load <sup>1</sup> |        | $0.7 \times IOVDD$ |     |                    | V       |

| Low-Level Output Voltage, 1.0 mA load <sup>1</sup>   |        |                    |     | $0.3 \times IOVDD$ | V       |

| XTALO high-level output voltage, -0.1 mA load        |        | $0.7 \times IOVDD$ |     |                    | V       |

| XTALO low-level output voltage, 0.1 mA load          |        |                    |     | $0.3 \times IOVDD$ | V       |

| Input leakage current                                |        | -1.0               |     | 1.0                | $\mu A$ |

| Rise time of all output pins, load = 30 pF $^1$      |        |                    |     | 50                 | ns      |

<sup>1</sup> Pins GPIO0\_[15:0], GPIO1\_[15:0], GPIO2\_[13:0].

## 5 Package and Pin Descriptions

#### 5.1 Packages

LFGA-88 is lead (Pb) free and RoHS-compliant package. RoHS is a short name of *Directive 2002/95/EC on the restriction of the use of certain hazardous substances in electrical and electronic equipment.*

LFGA package and pin dimensions are shown in figures 2, 3 and 4. For more information about LFGA-88 package and dimensions visit *http://www.vlsi.fi/*.

Figure 2: Top View, LFGA-88.

# VS1005g Datasheet 5 PACKAGE AND PIN DESCRIPTIONS

5 PACKAGE AND PIN DESCRIPTIONS

#### 5.2 Pin Assignments

Figure 5: vs1005 88-pin LFGA Pin Assignment.

# VS1005g Datasheet 5 PACKAGE AND PIN DESCRIPTIONS

#### 5.3 Vs1005 Pin Descriptions

| Pin Name         | LFGA<br>Pin | Pin Type | Function                                             |

|------------------|-------------|----------|------------------------------------------------------|

| XTALO            | 1           | AO       | Crystal output                                       |

| XTALI            | 2           | AI       | Crystal input                                        |

| AVDD             | 3           | APWR     | Analog power supply, Regulator output                |

| VHIGH            | 4           | PWR      | Power supply, Regulator input                        |

| CVDD             | 5           | CPWR     | Core power supply, Regulator output                  |

| IO2VDD           | 6           | IO2PWR   | Serial Flash power supply, Regulator output          |

| IOVDD            | 7           | IOPWR    | I/O power supply, Regulator output                   |

| XRESET           | 8           | DI       | Active low asynchronous reset, schmitt-trigger input |

| NFDIO0 / GPIO0_0 | 9           | DIO      | Nand-flash IO0 / General-purpose IO Port 0, bit 0    |

| NFDIO1 / GPIO0_1 | 10          | DIO      | Nand-flash IO1 / General-purpose IO Port 0, bit 1    |

| NFDIO2 / GPIO0_2 | 11          | DIO      | Nand-flash IO2 / General-purpose IO Port 0, bit 2    |

| NFDIO3 / GPIO0_3 | 12          | DIO      | Nand-flash IO3 / General-purpose IO Port 0, bit 3    |

| NFDIO4 / GPIO0_4 | 13          | DIO      | Nand-flash IO4 / General-purpose IO Port 0, bit 4    |

| NFDIO5 / GPIO0_5 | 14          | DIO      | Nand-flash IO5 / General-purpose IO Port 0, bit 5    |

| NFDIO6 / GPIO0_6 | 15          | DIO      | Nand-flash IO6 / General-purpose IO Port 0, bit 6    |

| NFDIO7 / GPIO0_7 | 16          | DIO      | Nand-flash IO7 / General-purpose IO Port 0, bit 7    |

| NFRDY / GPIO0_8  | 17          | DIO      | Nand-flash READY / General-purpose IO Port 0, bit 8  |

| NFRD / GPIO0_9   | 18          | DIO      | Nand-flash RD / General-purpose IO Port 0, bit 9     |

| XCS1 / GPIO1_4   | 19          | DIO      | SPI1 XCS / General-Purpose I/O Port 1, bit 4         |

| SCLK1 / GPIO1_5  | 20          | DIO      | SPI1 CLK / General-Purpose I/O Port 1, bit 5         |

| CVDD1            | 21          | CPWR     | Core power supply, connect to regulator CPWR         |

| MISO1 / GPIO1_6  | 22          | DIO      | SPI1 MISO / General-Purpose I/O Port 1, bit 6        |

| Pin Name           | LFGA<br>Pin | Pin Type | Function                                            |

|--------------------|-------------|----------|-----------------------------------------------------|

| MOSI1 / GPIO1_7    | 23          | DIO      | SPI1 MOSI / General-Purpose I/O Port 1, bit 7       |

| NFWR / GPIO0_10    | 24          | DIO      | Nand-flash WR / General-purpose IO Port 0, bit 10   |

| IOVDD1             | 25          | IOPWR    | I/O power supply, connect to regulator IOPWR        |

| NFCE / GPIO0_11    | 26          | DIO      | Nand-flash CE / General-purpose IO Port 0, bit 11   |

| XCS0 / GPIO1_0     | 27          | DIO      | SPI0 XCS / General-Purpose I/O Port 1, bit 0        |

| SCLK0 / GPIO1_1    | 28          | DIO      | SPI0 CLK / General-Purpose I/O Port 1, bit 1        |

| MISO0 / GPIO1_2    | 29          | DIO      | SPI0 MISO / General-Purpose I/O Port 1, bit 2       |

| MOSI0 / GPIO1_3    | 30          | DIO      | SPI0 MOSI / General-Purpose I/O Port 1, bit 3       |

| TMS / GPIO2_0      | 31          | DIO      | JTAG TMS / General-Purpose I/O Port 2, bit 0        |

| TDI / GPIO2_1      | 32          | DIO      | JTAG TDI / General-Purpose I/O Port 2, bit 1        |

| TDO / GPIO2_2      | 33          | DIO      | JTAG TDO / General-Purpose I/O Port 2, bit 2        |

| TCK / GPIO2_3      | 34          | DIO      | JTAG TCK / General-Purpose I/O Port 2, bit 3        |

| DBGREQ / GPIO2_4   | 35          | DIO      | Debug interrupt / General-Purpose I/O Port 2, bit 4 |

| CVDD2              | 36          | CPWR     | Core power supply, connect to regulator CPWR        |

| RX / GPIO1_8       | 37          | DIO      | UART RX / General-Purpose I/O Port 1, bit 8         |

| TX / GPIO1_9       | 38          | DIO      | UART TX / General-Purpose I/O Port 1, bit 9         |

| I2S_DI / GPIO1_10  | 39          | DIO      | I2S data in / General-Purpose I/O Port 1, bit 10    |

| I2S_DO / GPIO1_11  | 40          | DIO      | I2S data out / General-Purpose I/O Port 1, bit 11   |

| I2S_BCK / GPIO1_12 | 41          | DIO      | I2S bit clock / General-Purpose I/O Port 1, bit 12  |

| I2S_FRM / GPIO1_13 | 42          | DIO      | I2S frame sync / General-Purpose I/O Port 1, bit 13 |

| IOVDD2             | 43          | IOPWR    | I/O power supply, connect to regulator IOPWR        |

| I2S_12M / GPIO1_14 | 44          | DIO      | I2S 12.288 MHz clock output (XTALI) / General-      |

|                    |             |          | Purpose I/O Port 1, bit 14                          |

# VS1005g Datasheet 5 PACKAGE AND PIN DESCRIPTIONS

| Pin Name             | LFGA<br>Pin | Pin Type | Function                                                |

|----------------------|-------------|----------|---------------------------------------------------------|

| SD_CLK / GPIO2_5     | 45          | DIO      | SD card clock / General-Purpose I/O Port 2, bit 5       |

| SD_DAT0 / GPIO2_6    | 46          | DIO      | SD card data line 0 / General-Purpose I/O Port 2, bit 6 |

| SD_DAT1 / GPIO2_7    | 47          | DIO      | SD card data line 1 / General-Purpose I/O Port 2, bit 7 |

| SD_DAT2 / GPIO2_8    | 48          | DIO      | SD card data line 2 / General-Purpose I/O Port 2, bit 8 |

| SD_DAT3 / GPIO2_9    | 49          | DIO      | SD card data line 3 / General-Purpose I/O Port 2, bit 9 |

| SD_CMD / GPIO2_10    | 50          | DIO      | SD card cmd line / General-Purpose I/O Port 2, bit 10   |

| ETH_RXP / GPIO2_11   | 51          | DIO      | Ethernet RXP / General-Purpose I/O Port 2, bit 11       |

| GPIO1_15             | 52          | DIO      | General-Purpose I/O Port 1, bit 15                      |

| ETH_TXP / GPIO2_12   | 53          | DIO      | Ethernet TXP / General-Purpose I/O Port 2, bit 12       |

| IOVDD3               | 54          | IOPWR    | I/O power supply, connect to regulator IOPWR            |

| ETH_TXN / GPIO2_13   | 55          | DIO      | Ethernet TXN / General-Purpose I/O Port 2, bit 13       |

| SPDIF_IN / GPIO0_12  | 56          | DIO      | S/PDIF data in / General-Purpose I/O Port 0, bit 12     |

| SPDIF_OUT / GPIO0_13 | 57          | DIO      | S/PDIF data out / General-Purpose I/O Port 0, bit 13    |

| GPIO0_14             | 58          | DIO      | General-Purpose I/O Port 0, bit 14                      |

| GPIO0_15             | 59          | DIO      | General-Purpose I/O Port 0, bit 15                      |

| VDD3                 | 60          | CPWR     | Core power supply, connect to regulator CPWR            |

| DBG                  | 61          | DI       | Debug mode enable (active high), connect to DGND        |

| TEST                 | 62          | DI       | Test mode input (active high), connect to DGND          |

| PWRBTN               | 63          | AIO      | Power button for Regulator startup (and Power Key)      |

| RTCVDD               | 64          | RTCPWR   | Real time clock power supply                            |

| XTALO_RTC            | 65          | AO       | Real time clock crystal output                          |

| XTALI_RTC            | 66          | AI       | Real time clock crystal input                           |

| Pin Name          | LFGA | Pin Type   | Function                                                                                          |

|-------------------|------|------------|---------------------------------------------------------------------------------------------------|

| - III Hullio      | Pin  | i ili iypo |                                                                                                   |

| AUX0              | 67   | AI         | SAR A/D input 0 / Alternate line input 2                                                          |

| AUX1              | 68   | AI         | SAR A/D input 1 / Alternate line input 1                                                          |

| AUX2 / LINE3      | 69   | AI         | SAR A/D input 2 / Line input 3                                                                    |

| MIC2P / AUX3      | 70   | AI         | Microphone 2 positive differential input, self-biasing / SAR A/D input 3 / Alternate line input 2 |

| MIC2N / AUX4      | 71   | AI         | Microphone 2 negative differential input, self-biasing / SAR A/D input 4 / Alternate line input 1 |

| MIC1P / LINE1     | 72   | AI         | Microphone 1 positive differential input, self-biasing / line input 1                             |

| MIC1N / LINE2     | 73   | AI         | Microphone 1 negative differential input, self-biasing / line input 2                             |

| AVDDRF            | 74   | APWR1V8    | 1.8V RF power supply, connect to regulator CPWR                                                   |

| RF_N              | 75   | Al         | FM antenna negative differential input                                                            |

| RF_P              | 76   | AI         | FM antenna positive differential input                                                            |

| AGND <sup>1</sup> | 77   | APWR       | Analog reference ground                                                                           |

| RCAP              | 78   | AIO        | Filtering capacitance for reference                                                               |

| AVDD0             | 79   | APWR       | Analog power supply, connect to regulator APWR                                                    |

| RIGHT             | 80   | AO         | Right channel output                                                                              |

| N/A               | 81   | N/A        | Not connected pin                                                                                 |

| CBUF              | 82   | AO         | Common voltage buffer for headphones                                                              |

| LEFT              | 83   | AO         | Left channel output                                                                               |

| AVDD1             | 84   | APWR       | Analog power supply, connect to regulator APWR                                                    |

| USBP              | 85   | AIO        | USB differential + in / out, controllable 1.5k $\Omega$ pull-up                                   |

| USBN              | 86   | AIO        | USB differential - in / out                                                                       |

| GNDUSB            | 87   | APWR       | USB ground, connect to ground network in PCB                                                      |

| PWM               | 88   | DO         | PWM output                                                                                        |

<sup>1</sup> Connect to RCAP capasitor without vias in pcb board.

5 PACKAGE AND PIN DESCRIPTIONS

| Alternate pin functions in vs1005 package |      |          |                                             |  |  |

|-------------------------------------------|------|----------|---------------------------------------------|--|--|

| Pin Name                                  | LFGA | Pin Type | Function                                    |  |  |

|                                           | Pin  |          |                                             |  |  |

| Analog Line input 1                       | 71   | AI       | Alternate analog input pin for Line input 1 |  |  |

| Analog Line input 2                       | 70   | AI       | Alternate analog input pin for Line input 2 |  |  |

| Analog Line input 1                       | 68   | AI       | Alternate analog input pin for Line input 1 |  |  |

| Analog Line input 2                       | 67   | AI       | Alternate analog input pin for Line input 2 |  |  |

| Digital DA/AD Clock                       | 52   | DO       | Digital DA/AD clock output, xtal/2/4        |  |  |

| Digital DAC Right                         | 32   | DO       | DAC right channel digital output, xtal/2    |  |  |

| Digital DAC Left                          | 33   | DO       | DAC left channel digital output, xtal/2     |  |  |

| Digital ADC 1                             | 53   | DI       | Digital ADC 1 input, xtal/2                 |  |  |

| Digital ADC 2                             | 55   | DI       | Digital ADC 2 input, xtal/2                 |  |  |

| Digital ADC 3                             | 51   | DI       | Digital ADC 3 input, xtal/2                 |  |  |

| TMS                                       | 31   | DI       | Jtag Test Mode Select                       |  |  |

| TDI                                       | 32   | DI       | Jtag Test Data In                           |  |  |

| TDO                                       | 33   | DO       | Jtag Test Data Out                          |  |  |

| TCK                                       | 34   | DI       | Jtag Test Clock                             |  |  |

| DBGREQ                                    | 35   | DO       | Hardware debug state pin                    |  |  |

Pin type descriptions:

| Туре | Description                    | Туре    | Description                            |

|------|--------------------------------|---------|----------------------------------------|

| DI   | Digital input, CMOS Input Pad  | APWR    | Analog power supply pin or ground      |

| DO   | Digital output, CMOS Input Pad | APWR1V8 | Analog power supply pin, 1.8V          |

| DIO  | Digital input/output           | RTCPWR  | Real time clock power supply pin, 1.8V |

| AI   | Analog input                   | DGND    | Core or I/O ground pin                 |

| AO   | Analog output                  | CPWR    | Core power supply pin                  |

| AIO  | Analog input/output            | IOPWR   | I/O power supply pin                   |

Package bottom plate is a ground net and it is connected to ground network in PCB.

NOTE: Unused inputs should not be left floating. Tie either HIGH or LOW as appropriate. At power-up all GPIO is three stated and current leakage from IOVDD is cut. Outputs that are three-statable should only be pulled high or low to ensure signals at power-up and in standby.

#### 5.3.1 PCB Layout Recommendations

The following recommendations should be followed to ensure reliable operation.

- Analog power nets that are connected to regulator APWR/CPWR output should have bypass capasitors.

- USBP and USBN traces should be kept within 2mm of each other and with preferred length of 20-30mm (max 75mm). A solid ground plane is preferred under USBP and USBN traces.

- USBP and USBN traces should be very close to same length, drawn together and their characteristic differential impedance 90 Ohms

- No vias are allowed in USBP or USBN traces, only 45 degree angles should be used.

- USBP and USBN traces should be isolated from all other signal traces.

- RF\_P and RF\_N traces should be isolated from all other signal traces.

EXAMPLE SCHEMATIC

# 6 Example Schematic

Default pin usage is shown in figure 6.

Figure 6: vs1005 default pin usage.

VS1005g Datasheet 7 VS1005 GENERAL DESCRIPTION

# 7 VS1005 General Description

Vs1005 architecture is based on VS\_DSP core. VS\_DSP core architecture is described in VS\_DSP User's Manual. Chip is powered with internal regulator which provides voltages for three separate power domains. The core and periphery I/O power domains can be driven off separately, allowing simple I/O interfacing and minimizing power consumption. RTC has its own power supply which enables the RTC usage when the rest of the chip is powered down. RTC also includes a small backup ram. Vs1005 has two clock domains which are clocked by PLL. Analog interfaces are clocked with a XTAL clock but the dsp, digital intarfaces and memories are clocked with a multiplied clock. Vs1005 external interfaces are shown in figure 7.

### 7.1 VS1005 Internal Architecture

Vs1005 block diagram is shown in figure 8.

#### 7.1.1 Regulator Section

The VHIGH pin in the regulator section is used as a common main power supply for voltage regulation. This input is connected to three internal regulators, which are activated when the PWRBTN pin voltage is kept above 0.9V for about one millisecond, so that AVDD starts to rise and reaches about 1.5 V. After the PWRBTN has given this initial start current, the regulators reach their default voltages even if the PWRBTN is released. VHIGH must be sufficiently (about 0.3 V) above the highest regulated power (normally AVDD) so that regulation can be properly performed.

The PWRBTN state can also be read by software, so it can be used as one of the user interface

buttons.

A power-on reset monitors the core voltage and asserts reset if CVDD drops below the CMON level. It is also possible to force a reset by keeping PWRBTN pressed for longer than approximately 5.6 seconds. This feature can be disabled by software. A watchdog counter and the XRESET pin can also generate a reset for the device.

Resets do not cause the regulators to shut down, but they restore the default regulator voltages. After boot the firmware and user software can change the voltages.

Return to power-off is possible only with active software control (VSDSP writes the regulator shutdown bits), or when VHIGH voltage is removed for a sufficiently long time. In the default firmware player the power button has to be pressed for 2 seconds to make the software power-down the system and turn the regulators off.

#### 7.1.2 IO Section

IOVDD is used for the level-shifters of the digital I/O and crystal oscillator. The regulated IO voltage is internally connected. The IOVDD regulator output must be connected to IOVDD1, IOVDD2 and IOVDD3 input pins. Proper bypass capacitors should also be used.

The firmware uses GPIO0\_7 to select I/O voltage level. After reset the I/O voltage is 1.8 V. If GPIO0\_7 has a pull-down resistor, 1.8 V I/O voltage is used. If GPIO0\_7 has a pull-up resistor, 3.3 V I/O voltage is used.

#### 7.1.3 Digital Section

All digital logic except the real time clock is powered from core voltage CVDD. The regulated core voltage is internally connected. The CVDD regulator output must be connected to CVDD1, CVDD2 and CVDD3 input pins. CVDD pins should have proper bypass capacitors.

Real time clock power pin can be connected to CVDD net or it can have its own power supply which enables its use during chip power-down. The inputs and outputs of the RTC logic have level shifters but the RTCVDD voltage should not exceed the CVDD voltage range.

#### Clock

The crystal amplifier uses a crystal connected to XTALI and XTALO. An external logic-level input clock can also be used. When VS1005 is used with FS USB, 12 MHz crystal allows lower power consumption. With FS/HS USB the input clock of 12 MHz or 12.288 MHz is recommended.

An internal phase-locked loop (PLL) generates the internal clock by multiplying the input clock by  $1.0 \times, 1.5 \times, ..., 8.0 \times$ . When USB is connected, the clock is  $5.0 \times 12 \text{ MHz} = 60 \text{ MHz}$ . When the player is active, the clock will be automatically changed according to the requirements of the song being played.

XRESET disables the clock buffer and puts the digital section into powerdown mode.

In usb suspend state the core clock is switced to RTC clock and the clock oscillator is powered down.

#### $VSDSP^4$

VSDSP<sup>4</sup> is VLSI Solution's proprietary digital signal processor with a 32-bit instruction word, two 16-bit data buses, and both 16-bit and 32/40-bit arithmetic.

IROM, XROM, and YROM contain the firmware, including the default player application. Most of the instruction RAM and some of the X and Y data RAM's can be used to customize and extend the functionality of the player.

For software customization the firmware supports nand flash and SD card boot. The vs1005xF version can use also the internal serial flash as a boot device.

#### UART

An asynchronous serial port is used for debugging and special applications. The default speed is 115200 bps. RX and TX pins can also be used for general-purpose I/O when the UART is not required.

#### SPIs

A synchronous serial port peripheral is used for SPIEEPROM boot, and can be used to access other SPI peripherals (for example LCD or SED) by using another chip select. The SPI0 is only used for boot if the XCS0 pin has a high level after reset (pull-up resistor attached). These pins can also be used for general-purpose I/O when the SPI is not required.

The default player uses MISO0 and MOSI0 for LED outputs.

#### NAND FLASH Interface

The NAND FLASH peripheral calculates a simple error-correcting code (ECC), and automates some of the communication with a NAND FLASH chip. The firmware uses the peripheral to access both small-page (512+16 B pages) and large-page (2048+64 B pages) NAND FLASH chips. The first sector in the FLASH tells the firmware how it should be accessed.

The NAND FLASH interface pins can also be used as general-purpose I/O. The default firmware uses GPIO0\_[4:0] for keys, and GPIO0\_[7:6] for other purposes. Pull-up and pull-down resistors must be used for these connections so that the data transfer to and from the NAND FLASH isn't disturbed when keys are pressed.

#### **SD Card Interface**

The SD card interface automates some of the communication with an SD card. Peripheral supports 1-bit and 4-bit data transfers.

The SD card interface pins can also be used as general-purpose I/O.

#### **Ethernet Controller**

Ethernet Controller is an interface to 10base-t network. The interface uses digital signal levels and external components are required to connect to ethernet. The core clock must be switched to 60 MHz when ethernet peripheral is used.

The ethernet interface pins can also be used as general-purpose I/O.

#### USB

The USB peripheral handles USB2.0 Full Speed and High Speed harware protocols. Low speed communication is not supported, but is correctly ignored. The USBP pin has a software-controllable  $1.5k\Omega$  pull-up.

A control endpoint (1 IN and 1 OUT) and upto 6 other endpoints (3 IN and 3 OUT) can be used simultaneously. Bulk, interrupt, and isochronous transfer modes are selectable for each endpoint. USB receive from USB host to device (OUT) uses a 2 KiB buffer, thus allowing very high transfer speeds. USB transmit from device to USB host (IN) also uses a 2 KiB buffer and allows all IN endpoints to be ready to transmit simultaneously. Double-buffering is also possible, but not usually required.

The firmware uses the USB peripheral to implement both USB Mass Storage Device and USB Audio Device. Which device is activated depends on the state of GPIO0\_6 when the USB connection is detected. If GPIO0\_6 has a pull-up resistor, VS1005 appears as an USB Audio Device. If GPIO0\_6 has a pull-down resistor, VS1005 appears as an USB Mass Storage Device.

#### 7.2 Analog Section

The third regulator provides power for the analog section.

The analog section consists of digital to analog converters, an earphone driver and FM receiver. This includes a buffered common voltage generator (CBUF, around 1.2 V) that can be used as a virtual ground for headphones.

The regulator AVDD output pin must be connected to AVDD1 and AVDD2 pins with proper bypass capacitors, because they are not connected internally. The AVDDRF pin is connected to regulator CVDD pin with proper bypass capacitors or with external regulator from VHIGH.

The USB pins use the internal AVDD voltage, and the firmware configures AVDD to 3.6 V when USB is attached.

AVDD voltage level can be monitored by software. Currently the firmware does not take advantage of this feature.

CBUF contains a short-circuit protection. It disconnects the CBUF driver if pin is shorted to ground. In practise this only happens with external power regulation, because there is a limit to how much power the internal regulators can provide.

VS1005g Datasheet OSCILLATOR AND RESET CONFIGURATION

# 8 Oscillator and Reset Configuration

The reset module gathers reset sources and controls the system's internal reset signals. Reset Sources are:

- POR : Power-On reset and CVDD voltage monitor

- XRESET : External active low reset pin

- *wdog\_rst* : Watchdog timer reset

- *dbg\_rst* : Debugger reset

- PWRBTN : Power Button reset after 5 seconds

Two clock sources can be used :

- 11MHz 13MHz Oscillator

- 32kHz RTC oscillator

# 9 Firmware Operation

The firmware uses the following pins (see the example schematics in Section 6):

| Pin     | Description                                                                                     |

|---------|-------------------------------------------------------------------------------------------------|

| PWRBTN  | High level starts regulator, is also read as the Power button Key.                              |

| GPIO0_0 | external 1 M $\Omega$ pull-down resistor, Key 1 connects a 100 k $\Omega$ pull-up resistor $^1$ |

| GPIO0_1 | external 1 M $\Omega$ pull-down resistor, Key 2 connects a 100 k $\Omega$ pull-up resistor      |

| GPIO0_2 | external 1 M $\Omega$ pull-down resistor, Key 3 connects a 100 k $\Omega$ pull-up resistor      |

| GPIO0_3 | external 1 M $\Omega$ pull-down resistor, Key 4 connects a 100 k $\Omega$ pull-up resistor      |

| GPIO0_4 | external 1 M $\Omega$ pull-down resistor, Key 5 connects a 100 k $\Omega$ pull-up resistor      |

| GPIO0_6 | external pull-down resistor for USB Mass Storage Device, pull-up for USB                        |

|         | Audio Device                                                                                    |

| GPIO0_7 | external pull-down resistor for 1.8 V I/O voltage, pull-up resistor for 3.3 V I/O               |

|         | voltage                                                                                         |

| NFCE    | external pull-up resistor for normal operation, pull-down to use RAM disk for                   |

|         | UMS Device                                                                                      |

| XCS     | external pull-up to enable SPI EEPROM boot                                                      |

| SI      | Power LED control during firmware operation                                                     |

| SO      | Feature LED control during firmware operation                                                   |

| USBN    | external 1 M $\Omega$ pull-up                                                                   |

| USBP    | external 1 M $\Omega$ pull-up                                                                   |

<sup>1</sup> Smaller pull-down resistors may be needed for keys if the capacitance on the GPIO pins is high.

Boot order:

| Stage             | Description                                                 |

|-------------------|-------------------------------------------------------------|

| Power on          | Power button (PWRBTN) pressed when VHIGH has enough volt-   |

|                   | age                                                         |

| Reset             | Power-on reset, XRESET, or watchdog reset causes software   |

|                   | restart                                                     |

| UART Boot         | Almost immediately after power-on UART can be used to enter |

|                   | emulator mode.                                              |

| SPI EEPROM Boot   | If XCS is high, SPI Boot is tried.                          |

| NAND FLASH probed | If NFCE is high, NAND FLASH is checked.                     |

| Default firmware  | The firmware in ROM takes control.                          |

#### 9.1 SPI Boot

The first boot method is SPI EEPROM. If GPIO1\_0 is low after reset, SPI boot is skipped. If GPIO1\_0 is high, it is assumed to have a pull-up resistor and SPI boot is tried.

First the first four bytes of the SPI EEPROM are read using 16-bit address. If the bytes are "VLS5" (for protected host) or "WLS5" (for unprotected host), a 16-bit EEPROM is assumed and the boot continues. If the last 3 bytes are read as "VLS", a 24-bit EEPROM is assumed and boot continues in 24-bit mode. Both 16-bit and 24-bit EEPROM should have the "VLS5" or

"WLS5" string starting at address 0, and the rest of the boot data starting at address 4. If no identifier is found, SPI EEPROM boot is skipped.

Boot records are read from EEPROM until an execute record is reached. Unknown records are skipped using the data length field.

| Byte | Description                            |

|------|----------------------------------------|

| 0    | type 0=I-mem 1=X-mem 2=Y-mem 3=execute |

| 1,2  | data len lo, hi – data length in bytes |

| 3, 4 | address Io, hi – record address        |

| 5    | data*                                  |

#### 9.2 NAND FLASH Probe

If NAND FLASH chip select (NFCE) is high, a NAND FLASH is assumed to be present and the first sector is read. The access methods (nandTypes 0..5) are tried in order to find the "VLN5" identification. If the first bytes are "VLN5", a valid boot sector is assumed. This sector gives the necessary information about the NAND FLASH so that it can be accessed in the right way.

| NandFlash Header |                     |                                                  |  |  |  |  |  |

|------------------|---------------------|--------------------------------------------------|--|--|--|--|--|

| Byte             | Value               | Description                                      |  |  |  |  |  |

| 0,1,2,3          | 0x56 0x4c 0x4E 0x35 | 'V' 'L' 'N' '5' – Identification                 |  |  |  |  |  |

| 4                | 0x03                | NandType lo (0x0003 = large-page with 3-byte     |  |  |  |  |  |

|                  |                     | block address), See table                        |  |  |  |  |  |

| 5                | 0x00                | NandType hi                                      |  |  |  |  |  |

| 6                | 0x08                | BlockSizeBits ( $2^8 * 512 = 128$ KiB per block) |  |  |  |  |  |

| 7                | 0x13                | FlashSizeBits ( $2^{19} * 512 = 256$ MiB flash)  |  |  |  |  |  |

| 8,9              | 0x00 0x46           | NandWaitNs – NAND FLASH access time in ns        |  |  |  |  |  |

| 10,11            | 0x00 0x01           | Number of extra blocks for boot (example:        |  |  |  |  |  |

|                  |                     | 0x0001)                                          |  |  |  |  |  |

| 12,13,14,15      | 0x42 0x6f 0x4f 0x74 | 'B' 'o' 'O' 't' – Optional boot ident            |  |  |  |  |  |

| 16511            |                     | code                                             |  |  |  |  |  |

|                        | NandFlash Type Configuration                                               |  |  |  |  |  |  |  |

|------------------------|----------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Low byte<br>(byte 0x4) | Description                                                                |  |  |  |  |  |  |  |

| 0                      | 512+16 B small-page flash with 2-byte block address (<= 32 MB)             |  |  |  |  |  |  |  |

| 1                      | 2048+64 B large-page flash with 2-byte block address (<= 128 MB)           |  |  |  |  |  |  |  |

| 2                      | 512+16B small-page flash with 3-byte block address (> 32 MB $<=$ 8 GB)     |  |  |  |  |  |  |  |

| 3                      | 2048+64 B large-page flash with 3-byte block address (> 128 MB $<=$ 32 GB) |  |  |  |  |  |  |  |

| 4                      | 512+16 B small-page flash with 4-byte block address (> 8 GB)               |  |  |  |  |  |  |  |

| 5                      | 2048+64 B large-page flash with 4-byte block address (> 32 GB)             |  |  |  |  |  |  |  |

If bytes 12-15 contain "BoOt", the value in bytes 10 and 11 determines how many sectors are read from NAND-flash. Value 1 means two 512-byte sectors are read, value 0 means only

the first block is needed. After the data is read into memory, the boot records in this data are processed, transferring code and data sections into the right places in memory and possibly executed. If an unknown boot record is encountered, the booting is stopped and control returns to the firmware code.

|           | NandFlash Record Configuration                             |  |  |  |  |  |  |  |

|-----------|------------------------------------------------------------|--|--|--|--|--|--|--|

| Code byte | Description                                                |  |  |  |  |  |  |  |

| 17, 16    | type 0x8000=I-mem 0x8001=X-mem 0x8002=Y-mem 0x8003=execute |  |  |  |  |  |  |  |

| 19, 18    | data length in (words -1) : 0 = 1 word, 1 = 2 words, etc.  |  |  |  |  |  |  |  |

| 21, 20    | address – record address                                   |  |  |  |  |  |  |  |

| 22        | data                                                       |  |  |  |  |  |  |  |

#### 9.3 UART Boot/Monitor

When byte 0xef is sent to RX at 115200 bps, the firmware enters monitor mode and communicates with **vs3emu**. Memory contents can be displayed, executables can be loaded and run, or the firmware code can be restarted or continued.

The UART is also a convenient way to program the NAND FLASH boot sector(s) or the SPI EEPROM.

#### 9.4 Default Firmware Features

#### 9.4.1 USB Mass Storage and Audio Device

When USB cable insertion is detected by the firmware, playing of the current file is stopped and USB handling code is started. The internal clock is configured to  $4.0 \times 12 \text{ MHz} = 48 \text{ MHz}$ , the analog power is configured to 3.6 V, the USB peripheral is initialized, and the USB pull-up resistor is enabled.

If GPIO0\_6 has a pull-up resistor, VS1005 appears as an USB Audio Device. If GPIO0\_6 has a pull-down resistor, VS1005 appears as an USB Mass Storage Device.

If during power-on the NAND FLASH contained a valid boot sector, the NAND FLASH disk will be used with the mass storage device. The NAND FLASH disk requires a filesystem-level formatting before it can be used. If NFCE had a pull-down instead of pull-up, or if a valid boot sector was not found, a RAM disk is used instead.

The RAM disk is preformatted and can be used immediately It does not retain its contents between USB detachment and insertion. The RAM disk is only intended for loading software through USB. You can copy a file **VS1005\_B.RUN** to RAM disk and it will be automatically run when you disconnect the USB cable. This mechanism can be used to program the NAND FLASH boot sector (perhaps containing custom boot code), and also for programming an SPI EEPROM or micro SD card in case NAND FLASH is not used in the application.

#### 9.4.2 Default Player Application

When the USB cable is detached, the contents of the disk is checked. If the disk seems to contain a FAT16 or FAT32 filesystem, a cleanup of unused sectors is performed. The cleanup makes the disk perform faster the next time something is written on it. If a full disk has been formatted or erased, this cleanup can take considerable time, even 30 seconds or more. After the cleanup is finished the player starts to play files.

Note: normally Windows formats smaller than about 16 MB disks as FAT12. The player has only partial support for FAT12 disks: no cleanup is performed, subdirectories are not allowed, and files are assumed not to be fragmented. If disks as small as or smaller than this are required, it is possible to format them as FAT16 with the following command. format e: /A:512 /FS:FAT

The default player application only decodes mp3 files, but it can be extended to allow some simple codecs, like a WAV decoder.

In addition to the power button, 5 keys are connected to GPIO0\_[4:0] so that they connect a 100 k $\Omega$  pull-up to the I/O when the button is pressed, and 1 M $\Omega$  pull-downs keep the lines low otherwise. The resistors are needed because these lines are also used for NAND FLASH communication. The keys are read approximately 16 times per second.

The key control can be changed by replacing the default key mapping table. The default user interface uses six buttons.

| Button | Short Press < 1 second | Long Press >= 1 second            |

|--------|------------------------|-----------------------------------|

| POWER  | Power On, Pause / Play | Power off (pressed for 2 seconds) |

| KEY1   | Volume Down            | Volume Down                       |

| KEY2   | Volume Up              | Volume Up                         |

| KEY3   | Previous               | Rewind                            |

| KEY4   | Next                   | Fast Forward                      |

| KEY5   | EarSpeaker             | Random On / Off                   |

#### **Power Button**

A press of the power button turns on the system. After boot the power LED (the LED connected to SI) is turned on. After the startup a short press of the power button toggles between pause and play modes. In pause mode the power LED flashes. When the power button is pressed for 2 seconds, the system powers down.

#### **Volume Buttons**

Volume can be turned up or down with 0.5 dB steps using the volume buttons. A short press changes the volume by 0.5 dB, a long press will change the volume by approximately 8 dB every second.

#### Previous / Next Buttons

A song can be changed using the previous and next buttons. A short press of the *previous* button will restart the song if it has been played for at least 5 seconds, and go to the previous song otherwise. A short press of the *next* button goes to the next song. A long press of *previous* or *next* will rewind and fast forward the song, respectively.

#### **Feature Button**

The sixth button controls two features: the EarSpeaker spatial processing and the random play function. A long press of the *feature* button toggles the random play function. When random play becomes activated, a new song is automatically randomly selected. When random play mode is active, the feature LED (the LED connected to SO) will light up. A short press of the *feature* button will select between four EarSpeaker modes: *off, minimal, normal,* and *extreme*.

#### 9.5 Supported Audio Codecs

|      | Conventions                                   |  |  |  |  |  |  |

|------|-----------------------------------------------|--|--|--|--|--|--|

| Mark | Description                                   |  |  |  |  |  |  |

| +    | Format is supported                           |  |  |  |  |  |  |

| ?    | Format is supported but not thoroughly tested |  |  |  |  |  |  |

| -    | Format exists but is not supported            |  |  |  |  |  |  |

|      | Format doesn't exist                          |  |  |  |  |  |  |

#### 9.5.1 Supported MP3 (MPEG layer III) Formats

#### MPEG 1.0<sup>1</sup>:

| Samplerate / Hz |    | Bitrate / kbit/s |    |    |    |    |    |     |     |     |     |     |     |     |

|-----------------|----|------------------|----|----|----|----|----|-----|-----|-----|-----|-----|-----|-----|

|                 | 32 | 40               | 48 | 56 | 64 | 80 | 96 | 112 | 128 | 160 | 192 | 224 | 256 | 320 |

| 48000           | +  | +                | +  | +  | +  | +  | +  | +   | +   | +   | +   | +   | +   | +   |

| 44100           | +  | +                | +  | +  | +  | +  | +  | +   | +   | +   | +   | +   | +   | +   |

| 32000           | +  | +                | +  | +  | +  | +  | +  | +   | +   | +   | +   | +   | +   | +   |

#### MPEG 2.0<sup>1</sup>:

| Samplerate / Hz |   | Bitrate / kbit/s |    |    |    |    |    |    |    |    |     |     |     |     |

|-----------------|---|------------------|----|----|----|----|----|----|----|----|-----|-----|-----|-----|

|                 | 8 | 16               | 24 | 32 | 40 | 48 | 56 | 64 | 80 | 96 | 112 | 128 | 144 | 160 |

| 24000           | + | +                | +  | +  | +  | +  | +  | +  | +  | +  | +   | +   | +   | +   |

| 22050           | + | +                | +  | +  | +  | +  | +  | +  | +  | +  | +   | +   | +   | +   |

| 16000           | + | +                | +  | +  | +  | +  | +  | +  | +  | +  | +   | +   | +   | +   |

#### MPEG 2.5<sup>1</sup>:

| Samplerate / Hz |   | Bitrate / kbit/s |    |    |    |    |    |    |    |    |     |     |     |     |

|-----------------|---|------------------|----|----|----|----|----|----|----|----|-----|-----|-----|-----|

|                 | 8 | 16               | 24 | 32 | 40 | 48 | 56 | 64 | 80 | 96 | 112 | 128 | 144 | 160 |

| 12000           | + | +                | +  | +  | +  | +  | +  | +  | +  | +  | +   | +   | +   | +   |

| 11025           | + | +                | +  | +  | +  | +  | +  | +  | +  | +  | +   | +   | +   | +   |

| 8000            | + | +                | +  | +  | +  | +  | +  | +  | +  | +  | +   | +   | +   | +   |

<sup>1</sup> Also all variable bitrate (VBR) formats are supported.

All real-life sound sources are external, leaving traces of the acoustic

# 10 VS1005 Peripherals and Registers

#### 10.1 The Processor Core

VS\_DSP is a 16/32-bit DSP processor core that also has extensive all-purpose processor features. VLSI Solution's free VSIDE Software Package contains all the tools and documentation needed to write, simulate and debug Assembly Language or Extended ANSI C programs for the VS\_DSP processor core. VLSI Solution also offers a full Integrated Development Environment VSIDE for full debug capabilities.

#### 10.2 VS1005 Memory Map

VS1005's Memory Map is shown in Figure 9.

| 0x0000 | Instruction (32-bit | ) | X (16-bit)    | Y (16-bit)            |

|--------|---------------------|---|---------------|-----------------------|

| 0x003F | System vectors      |   |               |                       |

| 0x1800 |                     |   | X Data<br>RAM | Y Data<br>RAM         |

| 0x1880 | User<br>Instruction |   | Stack         | Stack                 |

|        | RAM                 |   | X Data<br>RAM | Y Data<br>RAM         |

| 0x8000 |                     |   |               |                       |

| 0xF400 | Instruction<br>ROM  |   | X Data<br>ROM | Y Data<br>ROM         |

| 0xF800 |                     |   |               | USB RX<br>Buffer      |

| 0xFC00 |                     |   |               | USB TX<br>Buffer      |

| 0xFFFF |                     |   |               | Hardware<br>Registers |

Figure 9: User's Memory Map.

#### 10.3 VS1005 Peripherals

System peripherals are located in Y-address space. The peripherals that use PLL clock are in addresses 0xFC00 - 0xFD3F and peripherals that use xtal clock are in addresses 0xFE00 - 0xFEDF.

Peripheral address spaces are summarized in the following table:

|                          | VS1005 Peripheral Addresses                          |  |  |  |  |  |  |

|--------------------------|------------------------------------------------------|--|--|--|--|--|--|

| Address                  | Device                                               |  |  |  |  |  |  |

| PLL clocked pheripherals |                                                      |  |  |  |  |  |  |

| 0xFC00 - 0xFC1F          | Interrupt controller                                 |  |  |  |  |  |  |

| 0xFC20 - 0xFC3F          | DSP interface registers                              |  |  |  |  |  |  |

| 0xFC40 - 0xFC4F          | SPI 0                                                |  |  |  |  |  |  |

| 0xFC50 - 0xFC5F          | SPI 1                                                |  |  |  |  |  |  |

| 0xFC60 - 0xFC65          | 10base-t ethernet controller                         |  |  |  |  |  |  |