PCM1864的SCKI 由C5517CLKOUT输出12M时钟,参考PCM1864DBT规格书中的example进行配置

配置寄存器顺序如下,产生的BCK为3MHz LRCK46.87kHz。请问如果需要产生48kHz的输出,要怎么配置?

0x94 0x00 0x00 // Change to Page 0

0x94 0x01 0x40 // PGA CH1_L to 32dB

0x94 0x02 0x40 // PGA CH1_R to 32dB

0x94 0x03 0x40 // PGA CH2_L to 32dB

0x94 0x04 0x40 // PGA CH2_R to 32dB

0x94 0x05 0x86 // Enable SMOOTH PGA Change; Independent Link PGA;

0x94 0x06 0x41 // Polarity: Normal, Channel: VINL1[SE]

0x94 0x07 0x41 // Polarity: Normal, Channel: VINR1[SE]

0x94 0x08 0x44 // Polarity: Normal, Channel: VINL3[SE]

0x94 0x09 0x44 // Polarity: Normal, Channel: VINR3[SE]

0x94 0x0A 0x00 // Secondary ADC Input: No Selection

0x94 0x0B 0x44 // RX WLEN: 24bit; TX WLEN: 24 bit; FMT: I2S format

0x94 0x10 0x03 // GPIO0_FUNC - SCK Out; GPIO0_POL - Normal

0x94 0x11 0x50 // GPIO3_FUNC - DOUT2; GPIO3_POL - Normal

0x94 0x12 0x04 // GPIO0_DIR - GPIO0 - Output

0x94 0x13 0x40 // GPIO3_DIR – GPIO3 - Output

0x94 0x20 0x11 // MST_MODE: Master; CLKDET_EN: Disable

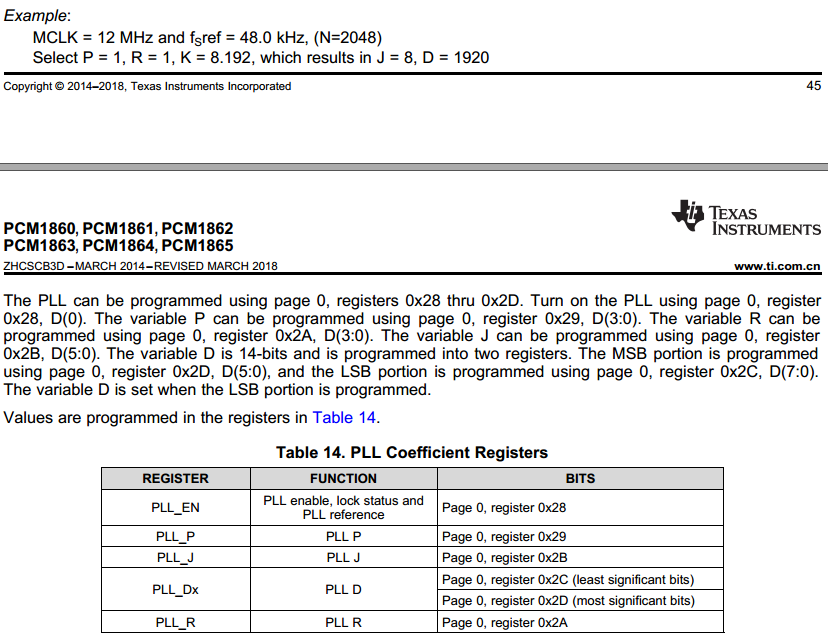

0x94 0x28 0x01 //PLL Enable

0x94 0x29 0x00 //PLL_P

0x94 0x2A 0x00 //PLL_R

0x94 0x2B 0x08 //PLL_J

0x94 0x2C 0x80 //PLL_D_LSB

0x94 0x2D 0x07 //PLL_D_MSB