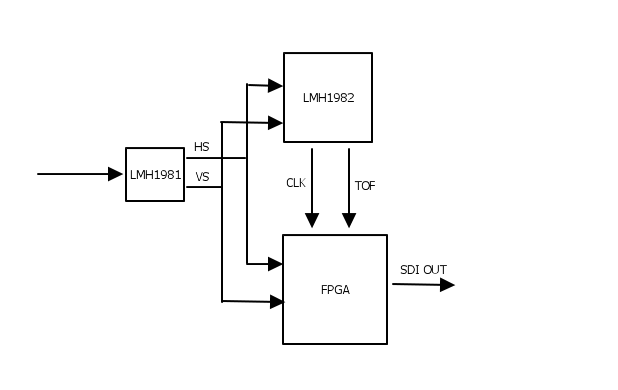

上图是我的测试环境:

1. PAL 黑场信号进入LMH1981,解码输出的HS、VS 信号同时进入LMH1982 和我的FPGA芯片;LMH1982恢复出的CLK 和TOF信号输出至FPGA 作为SDI发送使用;

2. LMH输出的CLK 我目前是配置为148.5M输出;

目前我遇到的问题如下:

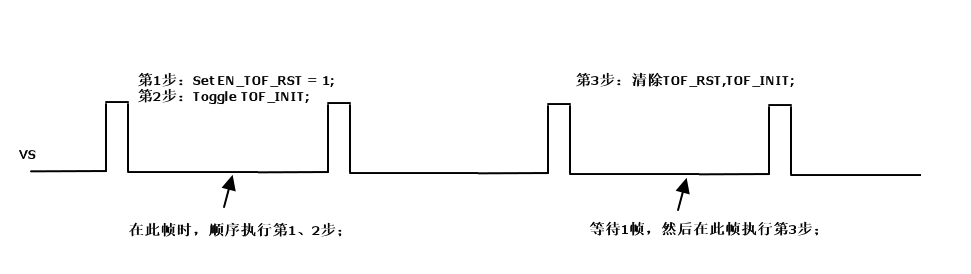

1. 在插拔LMH1981的REF输入之后, FPGA 抓取到LMH1982的TOF 与 LMH1981的VS/HS对齐会有两种位置关系(即TOF的位置偏移相对于LMH1981的同步头不是完全确定的)

请问什么原因可能导致以上的问题?