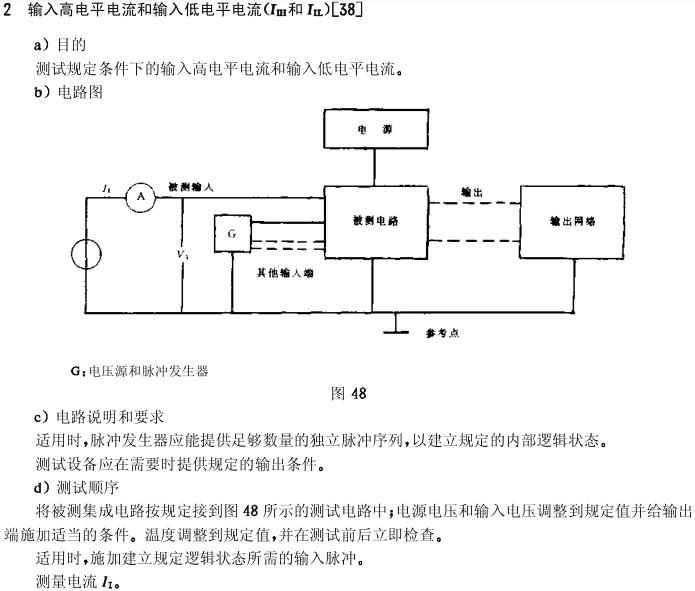

我们在用一颗TI的高速 CMOS 逻辑双路单稳多频振荡器CD54HC221,我们将芯片送到第三方测试机构进行规格参数检测,发现100片IC里面有19片在输入漏电流这个指标上超标(对照规格书)。第三方机构的测试方法如国标GB/T 17574-1998中的第Ⅳ篇所述:

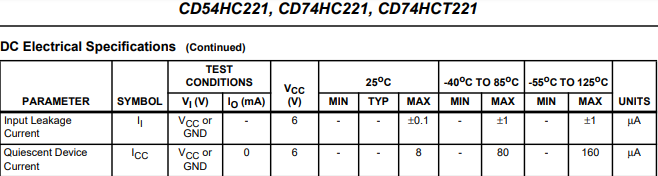

失效品的输入漏电流测试结果为-1.7046uA,超过了规格书指标+/-0.1uA(25℃环境)。

测试机构说:对于CMOS器件,输入脚一般是Cmos 的G脚,理论上期望G-S是无限大高阻,再大的电阻加了电压就会有电流,因为半导体电子迁移,存在微弱电流从G流到S脚,称做漏电流。

请问一下测试机构对漏电流的定义跟TI规格书Input Leakage Current相符吗?国标GB/T 17574-1998中的第Ⅳ篇所述的测试方法跟TI对Input Leakage Current测试方法相符吗?