你好:

请问:

1. 如果DLPC410 通过user 正常初始化后,无任何数据加载,此时 mirror 是什么状态 ? float park, 0 或 1?

2. DDC_INIT_ACTIVE 是在上电是就 assert (high)吗? 还是 ARST deassert (high)后,DDC_INIT_ACTIVE 才 assert。

在9.3.2中,说 ARST deassert 后 DLPC410 开始初始化; 但在 8.3.6.1 中说 上电后 DDC_INIT_ACTIVE assert;

3. 如果 Global reset 后,可正确察到 RESET_ACTIVE (4.5us high),是否意味着初始化正常,数据加载正常? 现在遇到一个问题,Global reset后可正确观察dao RESET_ACTIVE(4.5us),再持续发送 no-op row cycle 8us, 但DMD上并未正确显示数据,mirror应该还是float park 状态。

对初始化过程(从 user 与 DLPC410 交互角度),请帮忙看下理解是否有误:

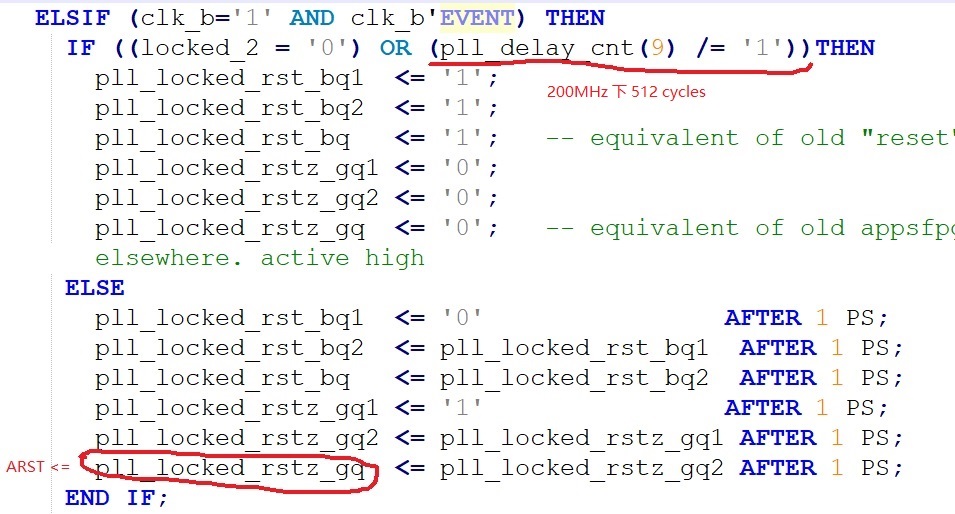

1. 上电后, ARST assert (low);

2. 当可提供有效 REF_50M 给 DLPC410后, ARST deassert;(8.3.5.2)

3. 当提供有效 ref clock,ARST deassert后,在 DDC_INIT_ACTIVE时, 提供 training pattern data;

4. 等待 DDC_INIT_ACTIVE完成,大约 220ms;在 DDC_INIT_ACTIVE deassert后 ,delay 64个 DCLKIN后 再提供 row cycle (即user可以正常进行 row cycle operation);