工程师您好:

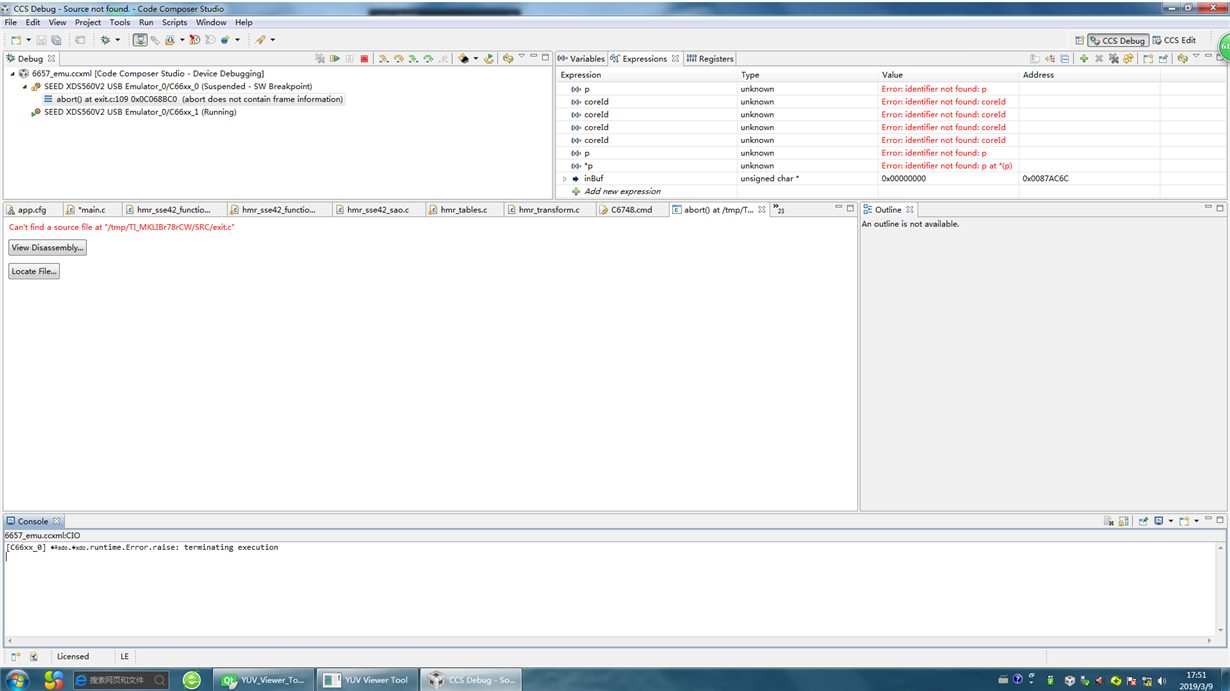

我最近调试一个使用IPC的程序,C6657的核0是一个TCP网络,核1是处理核。核1需要使用malloc申请大量内存空间,但是会默认将内存申请到L2SRAM中,超出了内存大小。于是注释掉了biso.heapsize行,使用HeapMem创建一个堆供核1的malloc使用,但是修改Memory.defaultHeapInstance后程序有时加载后直接出错,或者运行时也不能双核协调运行,请问可能是什么问题

cfg配置如下

var System = xdc.useModule('xdc.runtime.System');

var SysStd = xdc.useModule('xdc.runtime.SysStd');

var Fan = xdc.useModule('Tronlong.Driver.Fan');

System.SupportProxy = SysStd;

var SysStd = xdc.useModule('xdc.runtime.SysStd');

var Fan = xdc.useModule('Tronlong.Driver.Fan');

System.SupportProxy = SysStd;

/* 存储空间分配 */

Program.sectMap["SystemHeap"] = "DDR3_CORE0";

Program.sectMap[".const"] = "L2SRAM";

Program.sectMap[".switch"] = "L2SRAM";

Program.sectMap[".cinit"] = "L2SRAM";

Program.sectMap[".vecs"] = "L2SRAM";

Program.sectMap[".DDR3_0"] = "DDR3_CORE0";

Program.sectMap[".DDR3_1"] = "DDR3_CORE1";

Program.sectMap["SystemHeap"] = "DDR3_CORE0";

Program.sectMap[".const"] = "L2SRAM";

Program.sectMap[".switch"] = "L2SRAM";

Program.sectMap[".cinit"] = "L2SRAM";

Program.sectMap[".vecs"] = "L2SRAM";

Program.sectMap[".DDR3_0"] = "DDR3_CORE0";

Program.sectMap[".DDR3_1"] = "DDR3_CORE1";

var BIOS = xdc.useModule('ti.sysbios.BIOS');

//BIOS.heapSize = 32768;

//BIOS.heapSize = 32768;

/* 创建任务 */

var Task = xdc.useModule('ti.sysbios.knl.Task');

var tsk0 = Task.create('&tsk0_func');

tsk0.instance.name = "tsk0";

var Task = xdc.useModule('ti.sysbios.knl.Task');

var tsk0 = Task.create('&tsk0_func');

tsk0.instance.name = "tsk0";

/* 创建信号量 */

var Semaphore = xdc.useModule('ti.sysbios.knl.Semaphore');

Program.global.receive = Semaphore.create(1);

Program.global.process = Semaphore.create(0);

Program.global.sendimg = Semaphore.create(0);

Program.global.mutex = Semaphore.create(1);

var Semaphore = xdc.useModule('ti.sysbios.knl.Semaphore');

Program.global.receive = Semaphore.create(1);

Program.global.process = Semaphore.create(0);

Program.global.sendimg = Semaphore.create(0);

Program.global.mutex = Semaphore.create(1);

/* 配置核心名 */

var MultiProc = xdc.useModule('ti.sdo.utils.MultiProc');

var procNameAry = MultiProc.getDeviceProcNames();

MultiProc.setConfig(Program.global.procName, procNameAry);

/* IPC 配置 */

var Ipc = xdc.useModule('ti.sdo.ipc.Ipc');

var Notify = xdc.useModule('ti.sdo.ipc.Notify'); /* Notify */

var GateMP = xdc.useModule('ti.sdo.ipc.GateMP'); /* GateMP */

var SharedRegion = xdc.useModule('ti.sdo.ipc.SharedRegion'); /* shared region */

var MessageQ = xdc.useModule('ti.sdo.ipc.MessageQ'); /* MessageQ */

var HeapBufMP = xdc.useModule('ti.sdo.ipc.heaps.HeapBufMP');

var Ipc = xdc.useModule('ti.sdo.ipc.Ipc');

var Notify = xdc.useModule('ti.sdo.ipc.Notify'); /* Notify */

var GateMP = xdc.useModule('ti.sdo.ipc.GateMP'); /* GateMP */

var SharedRegion = xdc.useModule('ti.sdo.ipc.SharedRegion'); /* shared region */

var MessageQ = xdc.useModule('ti.sdo.ipc.MessageQ'); /* MessageQ */

var HeapBufMP = xdc.useModule('ti.sdo.ipc.heaps.HeapBufMP');

Ipc.procSync = Ipc.ProcSync_ALL; /* Ipc_start 里同步所有核心*/

Ipc.sr0MemorySetup = true;

Ipc.sr0MemorySetup = true;

GateMP.maxRuntimeEntries = 4;

GateMP.RemoteCustom1Proxy = xdc.useModule('ti.sdo.ipc.gates.GateMPSupportNull');

GateMP.RemoteCustom1Proxy = xdc.useModule('ti.sdo.ipc.gates.GateMPSupportNull');

/* 配置 SharedRegion #0 (IPC) */

var SHAREDMEM = 0x80000000;

var SHAREDMEMSIZE = 0x02000000;

var SHAREDMEM = 0x80000000;

var SHAREDMEMSIZE = 0x02000000;

SharedRegion.setEntryMeta(0,

{ base: SHAREDMEM,

len: SHAREDMEMSIZE,

ownerProcId: 0,

isValid: true,

name: "DDR2_RAM",

});

{ base: SHAREDMEM,

len: SHAREDMEMSIZE,

ownerProcId: 0,

isValid: true,

name: "DDR2_RAM",

});

for (var i = 0; i < MultiProc.numProcessors; i++) {

Ipc.setEntryMeta({

remoteProcId: i,

setupMessageQ: true,

});

}

Ipc.setEntryMeta({

remoteProcId: i,

setupMessageQ: true,

});

}

var Startup = xdc.useModule('xdc.runtime.Startup');

/******************************************************NDK 配置******************************************************/

Program.stack = 8192;

BIOS.startupFxns = ['&CacheInit'];

//启动时调用初始化函数

var Hwi = xdc.useModule('ti.sysbios.family.c64p.Hwi');

var HeapMem = xdc.useModule('ti.sysbios.heaps.HeapMem');

var SystemHeapParams = new HeapMem.Params;

SystemHeapParams.size = 16*16 *1024;

SystemHeapParams.sectionName = "SystemHeap";

Program.global.SystemHeap = HeapMem.create(SystemHeapParams);

var SystemHeapParams = new HeapMem.Params;

SystemHeapParams.size = 16*16 *1024;

SystemHeapParams.sectionName = "SystemHeap";

Program.global.SystemHeap = HeapMem.create(SystemHeapParams);

var Memory = xdc.useModule('xdc.runtime.Memory')

Memory.defaultHeapInstance = Program.global.SystemHeap;

Memory.defaultHeapInstance = Program.global.SystemHeap;

var Global = xdc.useModule('ti.ndk.config.Global');

Global.networkOpenHook = '&NetOpenHook';

Global.networkCloseHook = '&NetCloseHook';

Global.networkIPAddrHook = '&NetIPAddrChange';

Global.networkOpenHook = '&NetOpenHook';

Global.networkCloseHook = '&NetCloseHook';

Global.networkIPAddrHook = '&NetIPAddrChange';

var Ip = xdc.useModule('ti.ndk.config.Ip');

Ip.hostName = "TMS320C665x";

Ip.RestartIPTerm = true;

Ip.autoIp = false;

Ip.address = "192.168.1.30";

Ip.mask = "255.255.255.0";

Ip.hostName = "TMS320C665x";

Ip.RestartIPTerm = true;

Ip.autoIp = false;

Ip.address = "192.168.1.30";

Ip.mask = "255.255.255.0";

/* UIA */

var Logging = xdc.useModule('ti.uia.sysbios.LoggingSetup');

/* 实时分析 */

Logging.sysbiosHwiLogging = true;

Logging.sysbiosSwiLogging = true;

Logging.sysbiosHwiLoggingRuntimeControl = true;

Logging.sysbiosSwiLoggingRuntimeControl = true;

Logging.eventUploadMode = Logging.UploadMode_JTAGRUNMODE;

Task.defaultStackSize = 32768;

Task.defaultStackHeap = null;

Task.checkStackFlag = false;

cmd文件:

MEMORY

{

IPC o = 0x80000000 l = 0x10000000 /* 256MB 多核通信专用内存 */

DDR3_CORE0 o = 0x90000000 l = 0x08000000 /* 128MB 核心 0 专用 DDR3 内存 */

DDR3_CORE1 o = 0x98000000 l = 0x08000000 /* 128MB 核心 1 专用 DDR3 内存 */

}

{

IPC o = 0x80000000 l = 0x10000000 /* 256MB 多核通信专用内存 */

DDR3_CORE0 o = 0x90000000 l = 0x08000000 /* 128MB 核心 0 专用 DDR3 内存 */

DDR3_CORE1 o = 0x98000000 l = 0x08000000 /* 128MB 核心 1 专用 DDR3 内存 */

}

SECTIONS

{ /* C 语言入口 */

.text:_c_int00 > MSMCSRAM START(BootMagic)

}

{ /* C 语言入口 */

.text:_c_int00 > MSMCSRAM START(BootMagic)

}