1、 测试条件:

(1)PCIE链路:SPEED –> 2.5Gb/S、LANE WIDTH -> X2;

测试环境:A15@1GHz 运行linux

DSP@500MHz 运行TI-RTOS,配置PCIE驱动,作为RC端

FPGA 作为EP端

使用的测试程序由《C:\ti\pdk_am57xx_1_0_4\packages\ti\drv\pcie\example\sample》改造而成,驱动初始化、BAR空间配置等未做修改,只修改了应用部分。

2、 DSP连续写BAR空间:

测试类似: *(int *)0x21000100=0x1234;

*(int *)0x21000104=0x4567;等

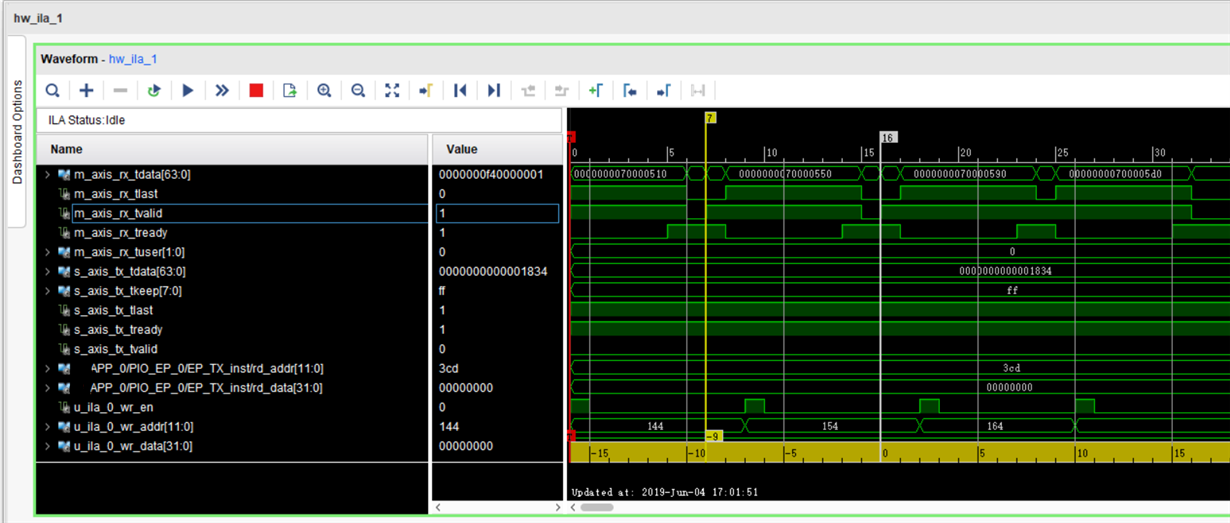

TLP报文间隔如下图所示:

M_axis_rx_xxx是DSP发送TLP包的总线,S_axis_tx_xxx是FPGA应答TLP包的总线,从上图可以看出,两个写TLP之间间隔是9个CLK(即9*8ns=72ns);

3、DSP连续读BAR空间:

测试类似: int A=*(int *)0x21000100;

int B=*(int *)0x21000104;

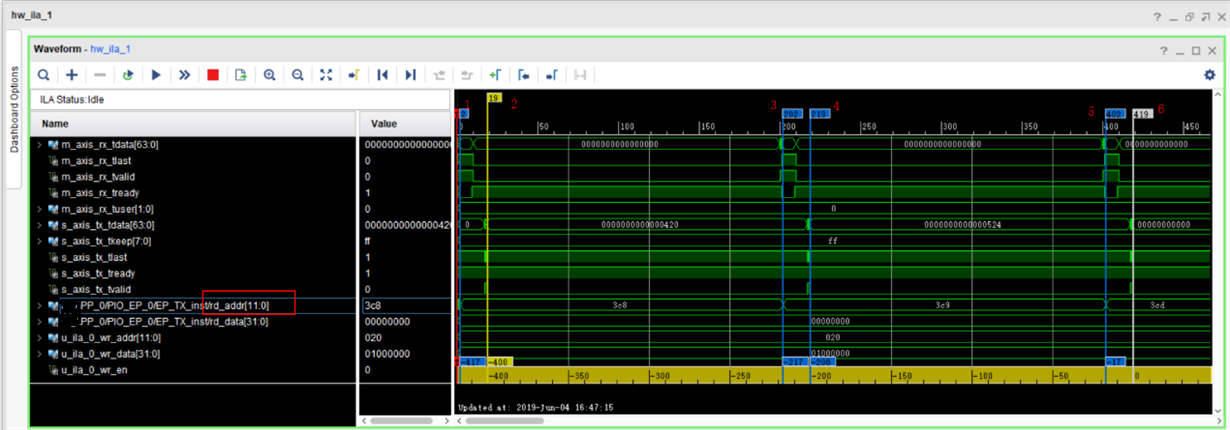

TLP包间隔如下:

M_axis_rx_xxx是DSP发送TLP包的总线,S_axis_tx_xxx是FPGA应答TLP包的总线,红色数字1,3,5是DSP分3次连续读BAR空间的TLP包的时刻,红色数字2,4,6是FPGA应答DSP的读申请的TLP包;

从上图可以看出,第一次DSP读申请,FPGA过了19-2=17个CLK(即17*8=136ns)就应答了DSP,但是DSP两次读申请的TLP包间隔(红色数字1,3)之间的差是202-2=200个clk,即1.6us