TI的专家,您好

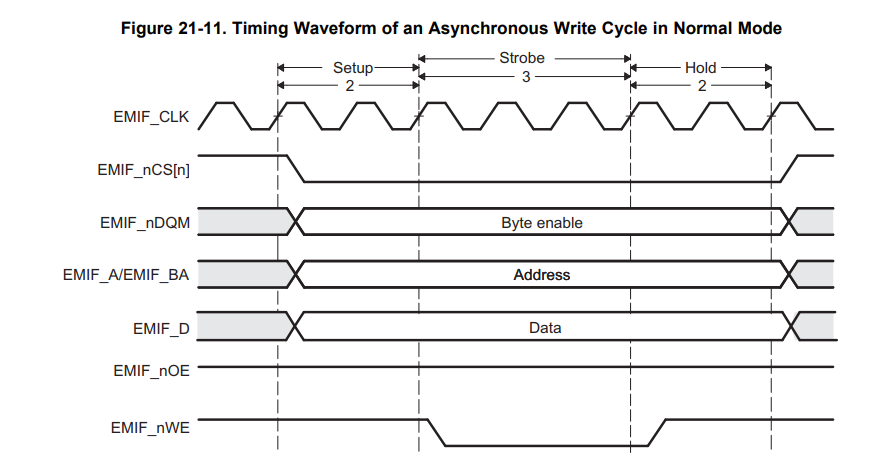

我们现使用的处理器是TMS570LC4357,处理器通过EMIF与FPGA通讯。总线配置为异步,16位,普通模式,详细配置的代码如下:

emifREG->CE3CFG = (0U << EMIF_BIT_SS) |

(0U << EMIF_BIT_EW) |

(1U << EMIF_BIT_W_SETUP) |

(14U << EMIF_BIT_W_STROBE) |

(0U << EMIF_BIT_W_HOLD) |

(15U << EMIF_BIT_R_SETUP) |

(15U << EMIF_BIT_R_STROBE) |

(0U << EMIF_BIT_R_HOLD) |

(1U << EMIF_BIT_TA) |

(1U << EMIF_BIT_ASIZE);

根据以往经验,读写过程中nDQM的时序是差不多的,nDQM01先拉低一段时间,拉高后隔一段时间nDQM2再拉低。

但是通过FPGA观察到的nDQM信号时序不正常。写入时,nDQM0和1被同时拉低;读取时,nDQM0先拉低一段时间,拉高后隔一段时间nDQM1再拉低。

我们查找手册并没有找到关于nDQM信号的设置部分,请问TMS570LC4357的nDQM信号正常的时序是怎样的?有没有寄存器来配置?

谢谢