你好 MSP430FR2433 P20 P21D当作普通 I/O口,不能 正常输出,其他口都正常。

void PIN_MANAGER_Initialize()

{ PM5CTL0 &= (~(LOCKLPM5+LPM5SW));

P1OUT = 0x00 ;

P1SEL1 = 0x00 ;

P1SEL0 = 0x00 ; //00000000 0=I/O function ,1=Peripheral

P1DIR = 0xA8; //10101000 P10 Motor_I , P11 KEY P12 Vibrant P13 Motor_dri P14 Batt_Sam P15 Power_control P16 Light_sensor P17 NC 10010100

P2OUT = 0x00 ; //

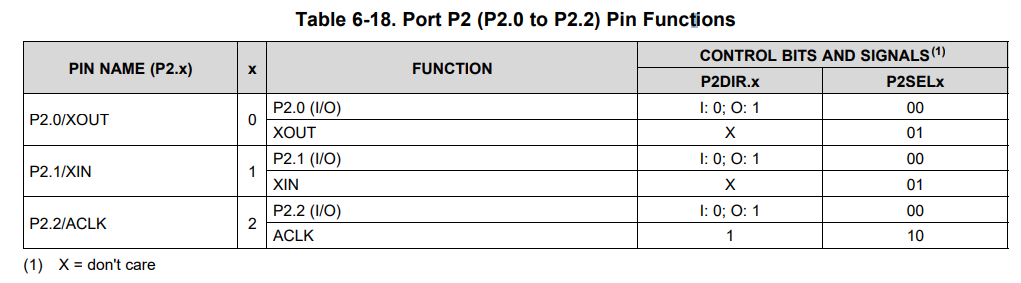

P2DIR = 0x7F; //01111101 p2.0 A7169_SCK, p2.1 A7169_SCS , p2.2 Press_Green , P2.3 match_led , p2.4 low_volt , p2.5 Led_HighTemp , p2.6 A7169_Power , p2.7 A7169_GIO1

P2SEL1 = 0 ; //00000000

P2SEL0 = 0 ;

P2IES = 0 ;

P3OUT = 0x00; //

P3SEL1 = 0x00; //00000000

P3SEL0 = 0 ;

P3DIR = 0xFF; //11111011 P3.0 Press_Yellow, p3.1 Press_red , P3.2 A7169_SDIO

asm("nop") ;

}