hello:

我想问一下SMCLK 和 HSMCLK 如果时钟配的是一致的, 比如都是48MHz, 都接的HFXT。

会产生什么影响呢,因为我看到手册上说SMCLK 最高频率要是HSMCLK 的一半。

但是我在实际使用中,尝试过将两个配置成一样的, 好像是可以配的。

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

hello:

我想问一下SMCLK 和 HSMCLK 如果时钟配的是一致的, 比如都是48MHz, 都接的HFXT。

会产生什么影响呢,因为我看到手册上说SMCLK 最高频率要是HSMCLK 的一半。

但是我在实际使用中,尝试过将两个配置成一样的, 好像是可以配的。

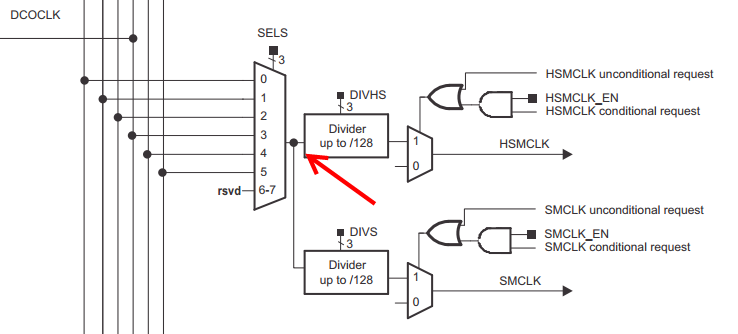

根据数据手册以及用户指南(第293页)中的Clock System图

我认为应该这样理解:

上图显示了生成SMCLK和HSMCLK的不同可能选项,其中生成的SMCLK和HSMCLK可以是相同或不同的频率,具体取决于DIVS和DIVHS时钟除数选择的值。

关于SMCLK是否必须限制频率,这取决于SELS位选择的时钟源的频率。这是因为SMCLK的最大允许频率为24 MHz(SMCLK可以为ADC14以外的所有外设提供时钟,但是最大都限制在24MHz)

例如:

-如果SELS位选择24 MHz时钟源,则SMCLK和HSMCLK都可能为24 MHz(DIVS和DIVHS均选择1分频)。

-如果SELS位选择48 MHz时钟源,则HSMCLK可能为48 MHz(DIVHS选择1分频),但SMCLK的最大值必须为24 MHz(DIVS选择2分频)。

总之,SMCLK 和 HSMCLK 时钟配的可以是一致的, 但是需要限制在24 MHz