# 前 言

作为世界领先的半导体产品供应商,TI 不仅在 DSP 的市场份额上有超过 65%占有率的绝对优势,在模拟产品领域,TI 也一直占据出货量世界第一的位置。而本手册是针对中国大学生创新活动的简化选型指南,帮助老师和同学们快速了解 TI 的模拟产品。需要提醒大家的是,这本手册仅仅涵盖了 TI 模拟产品的一小部分,如果您需要更为全面细致的选型帮助和技术文档,请访问 www.ti.com/analog 以获取运算放大器,数据转换器,电源管理,时钟,接口逻辑和 RF 等产品信息,访问 www.ti.com/mcu 以获得更多 MSP430,Tiva 和 C2000 的产品信息。

众人拾柴火焰高,如果你读过本手册的前面几个版本,一定会对其中略去的几个章节耿耿于怀,也会对其中草草结束的部分感到不满,今年在 TI 中国大学计划工程师团队的共同努力下,我们基于 2012 年的版本将本手册进行了第一阶段的充实工作。比如我们加入了原理部分,解读了放大器,数据转换器,电源的指标和选型方案;比如我们完善了应用技巧相关的章节,突出了实际操作中需要注意的问题,比如噪声控制,PCB 设计,等等;比如我们开始逐步强调模数混合系统设计的重要性,毕竟在现代的电子系统中,纯模拟的模块已经越来越少了。诸如这些改进,都是为了把更多的业界先进技术带给高校学生,加强同学们的工程实践能力,培养系统设计意识。

本手册将分为以下几部分介绍信号链和电源相关的知识及 TI 产品在大学生创新活动中的应用:

第一部分:运算放大器的原理和设计,由王沁工程师整理和编写:

第二部分:数据转换器的原理和设计,由崔萌工程师整理和编写,钟舒阳和谢胜祥两位 工程师也参与了其中的部分章节;

第三部分:线性电源和开关电源的原理和设计,由胡国栋工程师整理和编写,汪帅工程师也参与了其中的部分章节。

全书由黄争规划并进行了校对和修改。但是由于时间仓促,水平有限,手册中一定存在不少错漏,请大家积极给予反馈,提出宝贵意见。

德州仪器中国大学计划

### TI 概览

德州仪器公司,Texas Instruments,即 TI,是总部在美国德克萨斯州的一家高科技企业。实际上 TI 的中文名字并不是特别的"清晰明了",一方面是容易跟咱们的山东德州(因扒鸡而闻名)混淆;另一方面,我曾被问到,参加你们的大学计划,买示波器这类"仪器"打几折?在这些令人哭笑不得的问题背后,其实是 TI 近 80 年的悠久历史。德州是美国的主要石油产地, 1930 年 TI 的前身"Geophysical Service Inc."在德州成立时的主要目的是研发地震仪和石油探测仪器,因此 GSI 在 1950 年正式上市时就挑中了德州仪器这个名字。这也就是 TI 名字的由来。

在1958年,TI的工程师 Jack Kailby 先生发明了世界上首颗集成电路芯片,这项发明为人类进步做出了巨大的贡献, Jack Kailby 先生也因此在2000年获得了诺贝尔物理学奖。从此,半导体业务开始在TI发芽。但是,60/70年代的美国企业追求的是大而全,TI也不例外,拥有非常多的业务部门,这种情况一直持续到90年代中期。在这30年间,TI在半导体研发方面一直保持着创新,从第一颗单芯片微处理器,到最简单的数字语音合成芯片"spell & speak",到1982年的第一个单芯片数字信号处理器(DSP),到1993年发明的数字光源处理技术(DLP)片,半导体业务开始在TI的营收中占据着越来越重要的地位。在1995年的时候,TI的营收达到了130亿美元,成为过百亿美元的财富500强,但有些业务在市场的排名并不十分理想,比如,笔记本电脑排名第九,企业软件排名第十,打印业务排名第九,国防工业排名第十,惟一排到第一位的就是DSP业务。

面对更大的竞争和即将来临的网络时代,TI 高层锐意变革,在 90 年代初就非常有远见的提出了要做"数字时代的领导者"。1996 年 Tom Engibous 出任 TI 总裁,确定了 TI 的重点在半导体业务上,重中之重是 DSP 和 Analog。在 1996 年到 2000 年间,TI 连续卖出了 20 余家公司,又买入了 20 余家,完成了从多样化业务到半导体专营业务的转变。从此,TI 的半导体业务进入了高速发展期,在 DSP 方面,业界最快的 TMS320CC6000 系列、功耗最低的 TMS320C55xx 系列、第一颗运算速度超过 1GHz 的 C64x、第一颗 ADSL 调制解调芯片、ARM+DSP 双核架构的 OMAP 处理器等一系列领先产品的推出,使得 TI 在 DSP 领域奠定了世界第一的地位。

在模拟方面,TI 在 2000 年以当时创纪录的 60 亿美元收购了以设计和制造高端运放和数据转换器著称的 Burr-Brown 公司,这项收购非常大胆,因为当时 TI 的年收入也只有 130 亿美元。但是这也充分说明了模拟在 TI 战略中的重要性。接下来 TI 又收购了 Unitrode、Power Trends 等公司来壮大自己的电源方面的实力。在 2007 年,TI 收购了 Chipcon,在低功耗无线通信领域又占据了市场份额第一的位置。

在单片机方面,TI 在 90 年代末把 MSP430 从专供表类客户的应用中推到通用市场,其业界最低的功耗,集成的高性能模拟和数字外设都倍受客户青睐; C2000 数字信号控制器因为其 DSP的性能,单片机的价格被誉为实时单片机;而在 2009 年 TI 收购了 Luminary Micro,以最快的方式拥有了 Cortex M3 单片机家族,TI M3 因其低廉的价格,通用的架构,不俗的性能在单片机市场上迅速占领了一席之地。

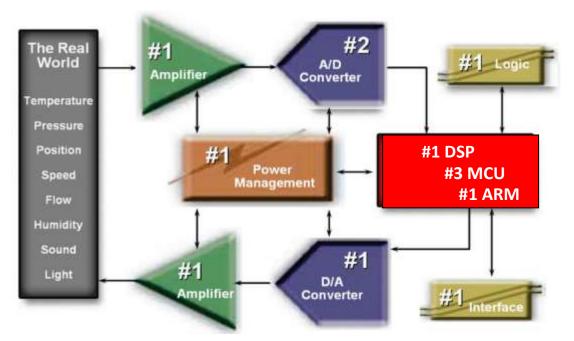

从下面的系统框图中,我们可以清楚看到 TI 在每一个电子系统的每一个角落都占据着业界数一数二的地位。而正因为持续不断的创新和进取,TI 连续 7 年被《财富》杂志评为全球和全美国最受尊敬的半导体公司,评分远超其他半导体企业。

数字信号处理是对理论和实践都要求极高的一门学科,采样理论,谱分析,滤波器设计,抽取,小信号提取,这些概念和算法包含了一大堆让人头晕眼花的数学公式。推导这些理论已经够让人头疼,那么怎么实现它们呢? TI 从第一颗 TMS32010 问世开始就一直致力于简化工程师实现数字信号处理算法的难度。1996 年 TI 进入中国设立办事处,当时中国熟悉 DSP 理论的人越来越多,但是如何使用硬件来实现这些理论却是个巨大的挑战。TI 管理层敏锐察觉到这个问题,抓住时机在中国高校中开展 TI DSP 大学计划,并在 1998 年和教育部签订谅解备忘录,承诺在中国高校中投资建立 100 个 DSP 实验室,帮助中国高校掌握和应用世界领先的 DSP 技术。2007 年10 月,TI CEO 理查德. 谭普顿先生来访中国,宣布核心大学计划在中国正式启动,这标志着 TI 将继续扩大对中国教育界的投入,比如 TI 中国大学计划将正式扩展到模拟技术和单片机领域,与高等学校进行合作,通过建立学生模拟创新实验室、对教师进行模拟技术和单片机相关的专业知识培训、支持学生参加各种电子设计竞赛等形式,强调模拟及模数混合电路的重要性。

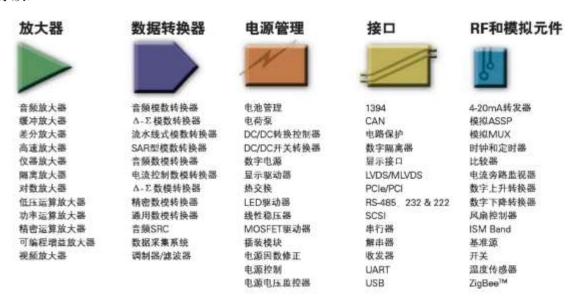

在现代电子设计中,模拟技术和数字技术相辅相成,因此在一系列电子设计竞赛中,TI 的 MSP430、M3 和 C2000 系列单片机作为系统的核心处理器和模拟器件一起在合作省市中推广。在 合作的过程中,我们深刻体会到学生对数字器件的感兴趣程度和掌握速度远远高于模拟技术。实际上,TI 各系列的 DSP 和单片机已做到高手遍布民间,学校实验室的技术一代传一代,很多还未毕业的学生就已经拥有了相当深的软硬件经验。相对于数字器件比较单一的硬件结构和编程思想,模拟器件的种类多指标细且用法灵活多变,很容易让人摸不着头脑,比如请看 TI 的模拟器件家族:

如何从上表中众多的放大器、数据转换器和电源中选取到合适的产品,又如何针对他们各自的特点发挥出最佳的性能?而这本选型手册的目的就是为了帮助大家做到这一点。

# 目 录

| 第一 | -章  | A   | DC                         |

|----|-----|-----|----------------------------|

| 1. | 1   | AD  | OC 基本原理(比较器和 FLASH型 ADC)1  |

| 1. | 2   | ΑD  | C 的基本分类3                   |

| 1. | 3   | 量位  | 化误差与分辨率3                   |

| 1. | 4   | 过   | 采样与欠采样5                    |

| 1. | 5   | 混   | 叠8                         |

| 第二 | .章  | A   | DC 性能指标13                  |

| 2. | 1   | 静   | 态精度13                      |

| 2. | 2   | 偏   | 置误差13                      |

|    | 2.2 | 2.1 | 增益误差14                     |

|    | 2.2 | 2.2 | 微分非线性14                    |

|    | 2.2 | 2.3 | 积分非线性16                    |

| 2. | 3   | 动   | 态指标16                      |

|    | 2.3 | 3.1 | 无杂波动态范围(SFDR)17            |

|    | 2.3 | 3.2 | 信噪比(SNR)18                 |

| 第三 | .章  | A   | DC 选型指南21                  |

| 3. | 1   | 常   | 见 ADC 结构特点与应用场景21          |

| 3. | 2   | SAF | R 型 ADC21                  |

|    | 3.2 | 2.1 | SAR 型 ADC 结构与原理            |

|    | 3.2 | 2.2 | 在运放和 SAR ADC 间插入 RC 组合     |

|    | 3.2 | 2.3 | $\triangle$ - $\Sigma$ ADC |

|    | 3.2 | 2.4 | 流水线型 ADC(Pipeline)33       |

|    | 3.2 | 2.5 | 应用场景总结37                   |

| 3.3 为: | 您的设计选择合适的 ADC              | 39 |

|--------|----------------------------|----|

| 3.3.1  | 确定 ADC 类型                  | 39 |

| 3.3.2  | 确定所需 ADC 的采样率,精度           | 40 |

| 3.3.3  | 选择并设计 ADC 的模拟输入            | 40 |

| 3.3.4  | 选择并设计 ADC 的参考输入            | 44 |

| 3.3.5  | 选择并设计高速数据采集系统中的时钟          | 48 |

| 3.3.6  | ADC 的数据输出捕获                | 49 |

| 第四章 D  | AC 简介与指标                   | 58 |

| 4.1 DA | AC 简介                      | 58 |

| 4.2 DA | AC 常见性能指标                  | 59 |

| 第五章 D  | AC 选型与指南                   | 60 |

| 5.1 常  | 见 DAC 结构与应用场景              | 60 |

| 5.1.1  | 电阻串型 DAC(R-String)         | 60 |

| 5.1.2  | 乘法型 DAC R-2R               | 64 |

| 5.1.3  | ΔΣ型 DAC                    | 70 |

| 5.1.4  | 电流引导型 DAC Current Steering | 71 |

| 5.1.5  | PWM DAC                    | 72 |

| 5.1.6  | DAC 应用场景总结                 | 79 |

| 5.2 DA | AC 选型与电路设计                 | 80 |

| 5.2.1  | 确定所需 DAC 的类型               | 80 |

| 5.2.2  | 确定所需的分辨率和建立时间              | 81 |

| 5.2.3  | 选择并设计 DAC 的模拟输出端           | 82 |

| 5.2.4  | 选择并设计 DAC 的参考电压输入端         | 83 |

| 5.2.5  | 选择并设计高速 DAC 的时钟            | 83 |

| 526    | DAC 的数据输入                  | 83 |

| 第六章 低 | ·吴···································   | 88  |

|-------|-----------------------------------------|-----|

| 6.1 精 | 密信号链中的噪声抑制                              | 88  |

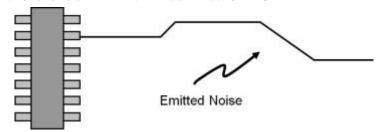

| 6.1.1 | 噪声来源                                    | 91  |

| 6.1.2 | 减少器件噪声                                  | 94  |

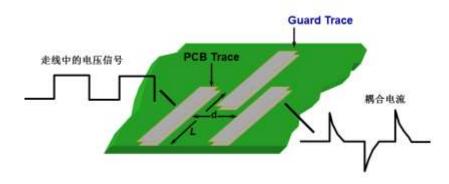

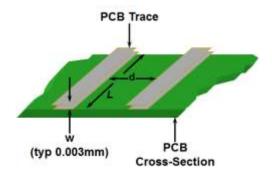

| 6.1.3 | 减少辐射噪声                                  | 94  |

| 6.1.4 | 减少传导噪声                                  | 98  |

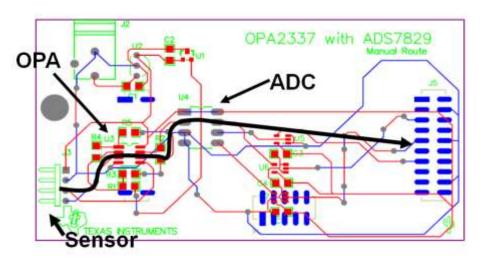

| 6.1.5 | PCB 优化指南                                | 101 |

| 6.2 利 | 用 Delte-Sigma ADC 简化电路设计                | 103 |

| 6.2.1 | 用 $\triangle$ - $\Sigma$ ADC 完成整个信号链的工作 | 104 |

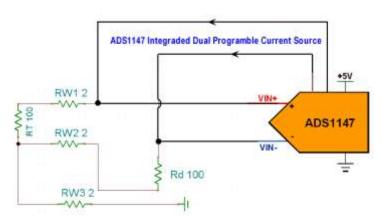

| 6.2.2 | 利用 ADS1147 完成对 3 线制 RTD 电阻的测量           | 105 |

| 第七章 高 | 5速信号链中 ADC 电路设计                         | 107 |

| 7.1 高 | 速数据采集系统中的时钟                             | 110 |

| 7.1.1 | 时钟抖动的影响                                 | 110 |

| 7.1.2 | 时钟幅度的影响                                 | 113 |

| 7.1.3 | 时钟同步的要求                                 | 116 |

| 7.2 驱 | 动高速 ADC 的模拟输入                           | 117 |

| 7.2.1 | 变压器驱动高速 ADC                             | 118 |

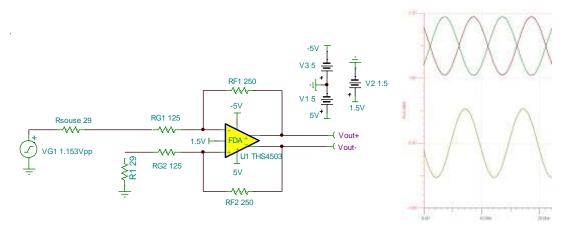

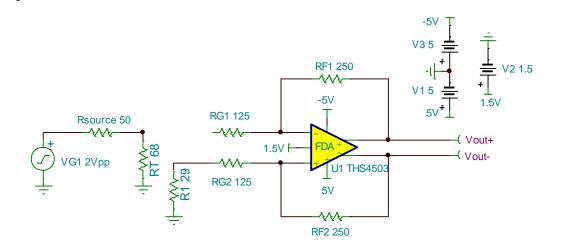

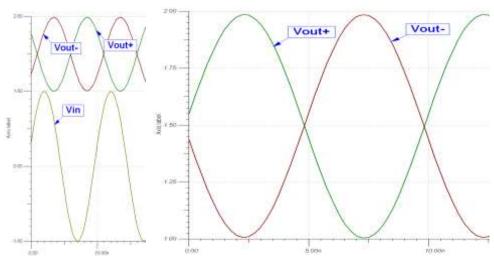

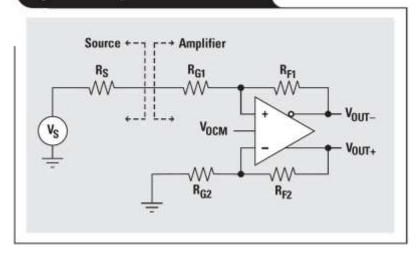

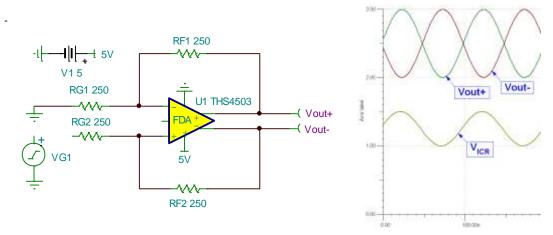

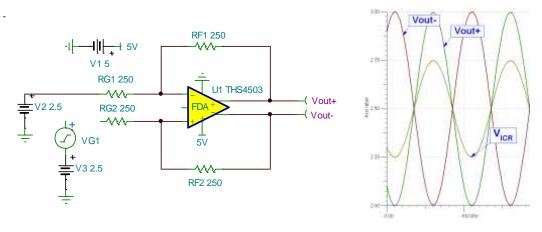

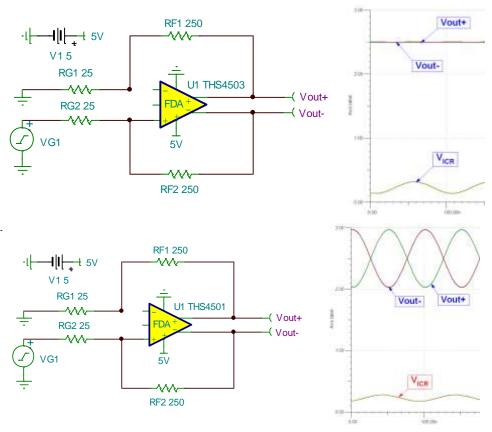

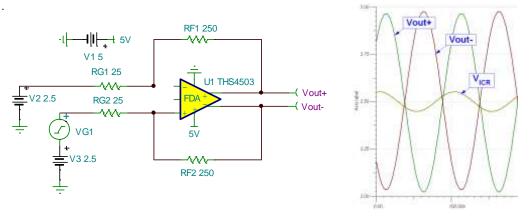

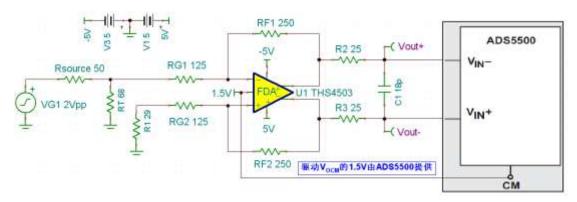

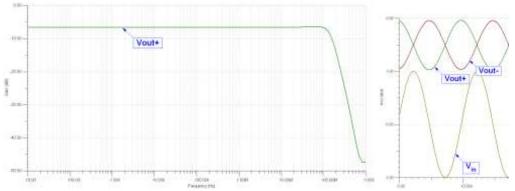

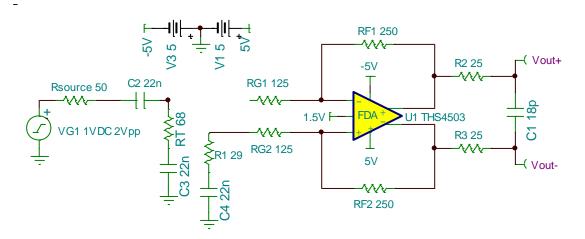

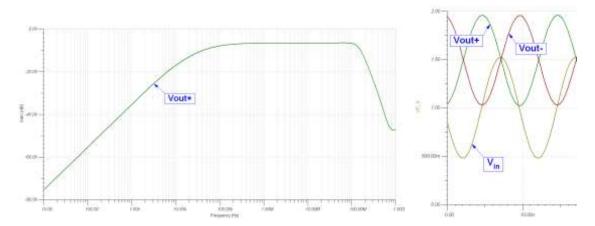

| 7.2.2 | 全差分放大器驱动高速 ADC                          | 119 |

| 7.3 使 | 用 FFT 测试高速 ADC                          | 133 |

| 附录——5 | ·<br>前用筆记                               | 135 |

# 第二部分 数据转换器

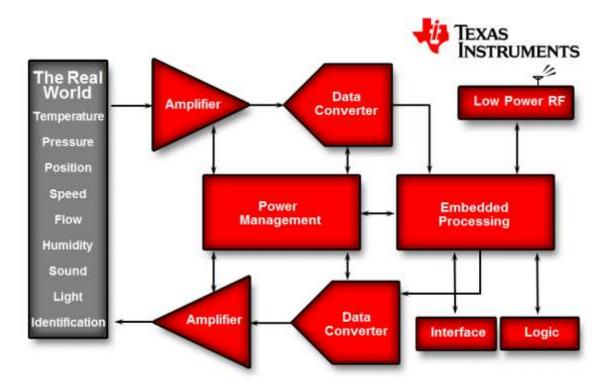

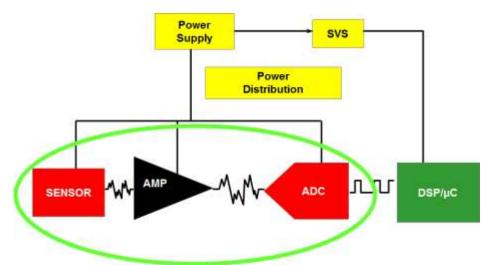

图 1 数据转换器在电路系统中的位置

数据转换器在整个电路系统设计中占据着十分重要的位置。如图 1 所示展示了现实世界和电子电路之前的交互,我们所感受到的是各种模拟量,例如温度,压力,湿度等等,而处理器需要对数字量进行处理,那这中间不可或缺的就是模/数转换器,Analog-Data Convertor,也就是 ADC; 当处理器对数字信号进行处理后,其结果如何以模拟量的形式反馈到现实世界中呢?这时数/模转换器,Data-Analog Convertor,也就是 DAC 则实现了将数字信号转换为可以被感受的模拟信号。从上面的描述中可以看出数据转换器,无论是 ADC 还是 DAC 在整个电路系统中扮演着桥梁的作用,贯通了模拟世界和数字世界,将冰冷的 0 和 1 数字量与丰富多彩的模拟量连接起来,从而实现了对现实生活的改变。

# 第一章 ADC

# 2.1 ADC 基本原理(比较器和 Flash 型 ADC)

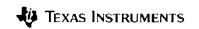

ADC, 顾名思义,实现的是将连续的模拟信号转换为时间离散,幅度离散的数字化信号,从而可以被数字信号处理器或微控制器使用。

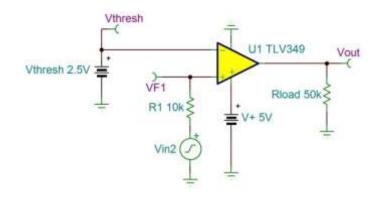

为了帮助大家理解,我们举一个最简单的 1bit ADC,也就是我们常见的比较器,做为例子。

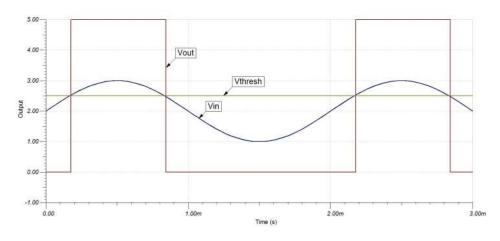

图 1-1 1bit ADC

从图 1-1 中我们看到,比较器成功的以 Vthresh 为阈值,把所有高于 Vthresh 的电压都量化为 1,把所有低于 Vthresh 的信号都量化为 0。这就是最简单的 1bit ADC,能输出 1 位数字信号。

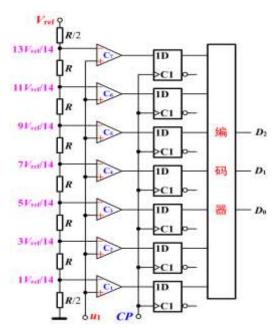

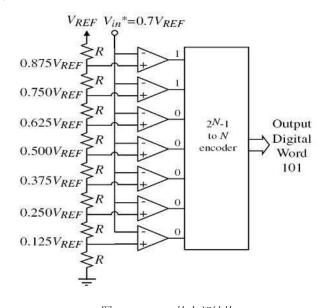

从这个最简单的 1 位 ADC 拓展开来,我们很容易得到一个 N 位的 ADC。图 1-2 是一个 3 位 ADC 为例,8 个电阻将参电压分成 8 个等级,其中 7 个等级的电压分别作为 7 个比较器的比较电平。输入的模拟电压经采样保持后与这些比较电平进行比较,当高于比较器的比较电平时,比较器输出为 1,当低于比较器的比较电平时,比较器输出为 0。比较器的输出状态由 D 触发器存储,并送给编码器,经过编码器编码得到数字输出量。3 位数字输出量表示 2^3 种不同的转换结果。

| AA N DE IN IN TH                                                | 157-157- | 比较器输出 |       |       |       |       |       | 数字输出 |       |       |

|-----------------------------------------------------------------|----------|-------|-------|-------|-------|-------|-------|------|-------|-------|

| 输入模拟信号                                                          | C7       | $C_6$ | $C_5$ | $C_4$ | $C_3$ | $C_2$ | $C_1$ | D,   | $D_1$ | $D_0$ |

| $0 < u_1 < V_{REF} / 14$                                        | 0        | 0     | 0     | 0     | 0     | 0     | 0     | 0    | 0     | 0     |

| $V_{\rm REF}/14 < u_1 < 3 V_{\rm REF}/14$                       | 0        | 0     | 0     | 0     | 0     | 0     | 1     | 0    | 0     | 1     |

| $3 V_{\text{REF}} / 14 < u_{\text{I}} < 5 V_{\text{REF}} / 14$  | 0        | 0     | 0     | 0     | 0     | 1     | 1     | 0    | 1     | 0     |

| 5 V <sub>REF</sub> /14< u <sub>1</sub> <7 V <sub>REF</sub> /14  | 0        | 0     | 0     | 0     | 1     | 1     | 1     | 0    | 1     | 1     |

| 7 V <sub>REF</sub> /14< u <sub>1</sub> <9 V <sub>REF</sub> /14  | 0        | 0     | 0     | 1     | 1     | 1     | 1     | 1    | 0     | 0     |

| 9 V <sub>REF</sub> /14< u <sub>1</sub> <11 V <sub>REF</sub> /14 | 0        | 0     | 1     | 1     | 1     | 1     | 1     | 1    | 0     | 1     |

| $11 \ V_{\rm REF} / 14 \le u_{\rm I} \le 13 \ V_{\rm REF} / 14$ | 0        | 1     | 1     | 1     | 1     | 1     | 1     | 1    | 1     | 0     |

| 13 V <sub>REF</sub> /14< u <sub>1</sub> < V <sub>REF</sub> /14  | 1        | 1     | 1     | 1     | 1     | 1     | 1     | 1    | 1     | 1     |

图 1-2 由比较器构成的 3bit ADC

图 1-2 所示的 ADC 结构即为 Flash ADC, 也称并行 ADC 的基本结构。Flash ADC 是目前转换速度最快的 ADC。对于 n 位输出二进制码,Flash ADC 需要 2n-1 个比较器。显然,随着

位数的增加,所需比较器数量将迅速增加。受到众多比较器之间存在大量的匹配误差的影响,加之电路成本和功耗的限制,Flash型 ADC的分辨率很难做到 10 位以上,Flahs型 ADC的分辨率一般为 6-8 位,适用于速度要求很高,而对时域分辨率要求较低的场合,比如示波器等仪器中。

## 2.2 ADC 的基本分类

在上一节中,我们介绍了 ADC 的基本结构,并引出了 Flash 型的 ADC。实际上,根据不同的转换方式,ADC 可以分为许多类型,分别适用于不同的使用环境。除并行 ADC (Flash 型)之外,现代常用的 ADC 包括:逐次逼近型(SAR 型)、流水线型(Pipeline型)、插值结构和折叠插值型、 $\Sigma$ - $\Delta$ 型等。

表 1.1 列出了几种常用类型 ADC 的特点,在后续章节中我们将详细介绍各种 ADC 的结构和原理,通常来说,在同样的结构下,ADC 的分辨率越高,转换速度就越低。

| 转换器结构                                                                                                       | 转换速度                                                           | 分辨率                                                         | 转换器类型                                                   |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|-------------------------------------------------------------|---------------------------------------------------------|

| Flash 型 SAR 型 ADS7xxx, ADS8xxx Pipeline 型 ADS7xxx, ADS8xxx ADS6xxx, 折叠插值型 ADC12Dxxxx, ADC10Dxxxx, ADC08Dxxx | ≤ 10GSPS  ≤ 16-bit  ≤ 18-bit  ≤ 200MSPS  ≤ 250MSPS  ≤ 1000MSPS | ≤ 10-bit  ≤ 4MSPS  ≤ 1.25MSPS  ≤ 16-bit  ≤ 14-bit  ≤ 12-bit | 瞬时值转换型——转<br>换对象是模拟信号在<br>采样时刻或前几个采<br>样时刻的抽样值,即<br>瞬时值 |

| Σ-Δ型<br>ADS11xx, ADS12xx                                                                                    | ≤ 4kSPS<br>≤ 4MSPS<br>≤ 10MSPS                                 | ≤ 31-bit<br>≤ 24-bit<br>≤ 16-bit                            | 平均值转换型——转<br>换对象是模拟信号在<br>一段时间内的平均值                     |

表 1.1 常见 ADC 对比

### 2.3 量化误差与分辨率

ADC 转换包括采样、保持、量化、编码 4 个步骤。其中,量化是指将信号的连续取值近似为有限多个离散值的过程。我们会发现量化的过程存在一个天生的缺陷,那就是离散的数字信号无法完整的对应每一个连续的模拟电压。以最简单的 1bit ADC(即比较器)为例,1.1节讲解了它的工作原理,即把所有高于阈值的电压都量化为 1,把所有低于阈值的信号都量化为 0。假设阈值为 2.5V,那么所有高于 2.5V 的电压都会被量化为 1,ADC 无法分辨 3V 和

3.3V 的区别:同理低于阈值时也有类似情况。

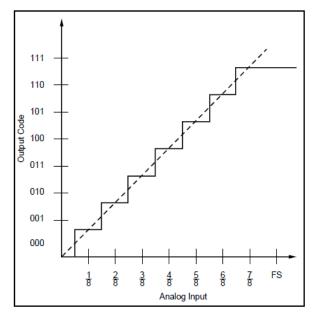

多个 bit 的 ADC 也有同样的问题。图 1-3 表示理想 3bit ADC 的转换结果,从图中可以看出转换结果为 8 个数字量,每个数字量分别对应一个模拟电平,我们将最低位数字量所对应的模拟电平称为称为最小有效位(Least Significant Bit,简称 LSB),即图 1-3 中横轴的一小格。图中的虚线代表输入模拟量,实线代表量化之后的数字量所对应的模拟值,二者之间有一定误差,这个误差就叫做量化误差。我们以横轴最左边一格为例,输入  $\leq$  1/2 LSB 时输出为 000b, 1/2 LSB < 输入  $\leq$  1 LSB 时输出为 001b,而实际输入范围是 0-1 LSB,ADC 无法分辨在 0 - 1/2 LSB,或是 1/2 LSB - 1 LSB 之间的输入。在最坏情况下,实际输入和量化之后的值之间有 1/2 LSB 的误差。也就是说 ADC 的量化误差为土1/2 LSB。

图 1-3 理想 3bit ADC

上面所述的 LSB 是 ADC 中一个重要的基本概念。还有两个概念也十分重要:满量程输入范围和分辨率。我们再看图 3,最小的数字量 000b 对应的模拟量为 0,最大的数字量 111b 对应的模拟量为满量程输入。最大输入和最小输入之间的差,称为满量程输入范围(Full Scale Input Range,简称 FS),FS 就是输入的模拟量的范围。而输出数字量的位数就是 ADC 的分辨率(Resolution),在这里就是 3 bit。

对比 1 bit ADC 和 3 bit ADC 不难发现,在满量程一定的情况下,ADC 的位数越高,量化误差越小。量化误差 eq 和 ADC 位数 N 之间有如下关系:

$$e_{q} = \frac{1}{2}LSB = 0.5 \times \frac{FS}{2^{N}}$$

量化误差可以看成是一种噪声作用,称为量化噪声,量化噪声将叠加到理想输出上。量 化噪声为白噪声,即噪声的随机变量在输出二进制码之间分布的平均值为 0,则其噪声功率 计算如下:

$$e_q^{rms} = \int_{-\frac{1}{2}LSB}^{\frac{1}{2}LSB} \left(\frac{e_q^2}{LSB}\right) de = \frac{LSB^2}{12}$$

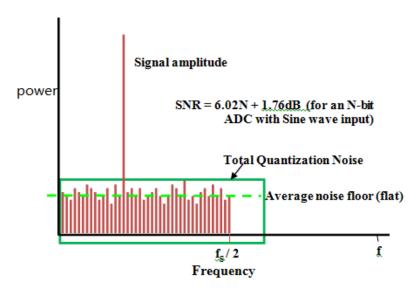

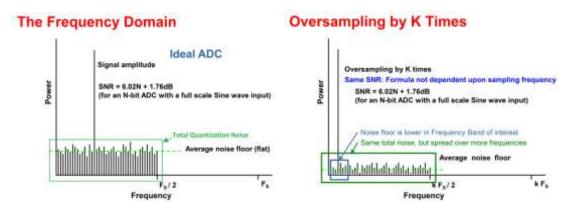

由此,我们看到当 ADC 的满量程输入和位数一定的情况下,将确定 ADC 的最小分辨率,从而确定了量化噪声功率。下图是从频域上看到的量化噪声功率的分布情况:

图 1-4 量化噪声在频域的分布情况

从图 1-4 中可以看到,量化噪声均匀的分布在从 0 到 fs/2 的频谱之间。对于 N-bit ADC 来说,信号功率和噪声功率之比称为信噪比(SNR),在只考虑量化噪声的情况下,信噪比的大小为:

$$SNR = 6.02N + 1.76dB$$

### 2.4 过采样与欠采样

在选择一个 ADC 时,采样频率 fs 是我们最优先考虑的参数。连续的模拟信号以时间间隔 ts = 1/fs 被采样,究竟什么样的采样频率才能保证精确地描述原始模拟信号?很显然,同一时间段内采样越多(采样频率越高),模拟信号的数字表示就越精确。如果采样较少(采样频率越低),则少到一定程度时,模拟信号的关键信息将因得不到采样而丢失。奈奎斯特(Nyquist)采样定律和香农(Shannon)采样定律阐述了对采样信号的频率要求,奠定了采

#### 样的数学基础。

#### 奈奎斯特采样定律:

- 如果采样频率小于最大感兴趣模拟信号频率的两倍,将会出现一种称为"混叠"的现象。如果不希望避免感兴趣的信号发生混叠现象,采样频率 f<sub>s</sub>至少是该信号所含最高频率 f<sub>b</sub>的两倍。

#### 香农采样定律:

- 对带宽为 f<sub>a</sub> 的信号进行采样,采样频率 f<sub>c</sub> 应不小于 2 倍的 f<sub>a</sub>,否则会导致信息的丢失。

- 信号带宽 fa 可以是从 0 (直流) 到 fa, 或从 fi 到 fb (带通信号), 此时 fa = fb fi。

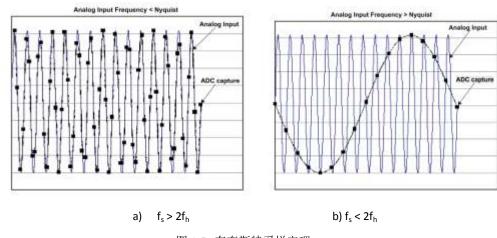

图 1-5 奈奎斯特采样定理

图 1-5 a)表示采样频率 fs > 2fh 时的情况,采样频率确保了每个模拟信号周期内有大于 2 个采样点,原信号的信息可以被正确还原,这种情况也称为过采样; 在图 5 b)中,采样频率 fs < 2fh,信号被重构为频率小于原频率的信号,这种情况也可被称作欠采样。欠采样时发生的频率偏移现象叫做混叠。

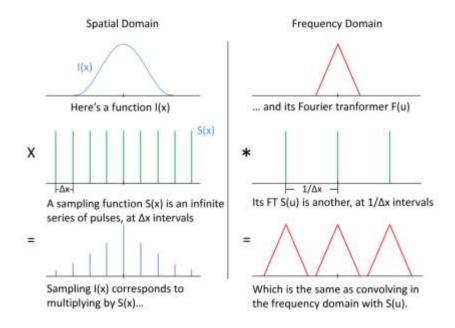

为了更好地理解采样与混叠,我们从频域上对采样定理做一些分析。图中上方是一个 DC 到 fh 的信号的时域波形, 右边是该信号相对应的频域信号波形。第一行 F(u)是被采样信号 I(x)的频域响应,第二行中 S(x)是采样信号的时域信号,是一组间隔为 $\Delta x$  的脉冲信号,它的频域响应 S(u)也是一组脉冲信号,但间隔变为  $1/\Delta x$ 。根据傅里叶变换的法则,时域中相乘相当于频域中做卷积,因此第三行中被采样之后的信号对应的频域响应成为了频域中的周期性重复信号,其间隔为  $1/\Delta x$  亦即采样频率 fs。也就是说时域中对信号进行离散化相当于频域中对信号周期化。图 1-6 表示的是过采样的情况,采样频率 fs > 2fh 保证了被周期化之后的频域没有出现频谱重叠。

图 1-6 过采样信号时域和频域对比

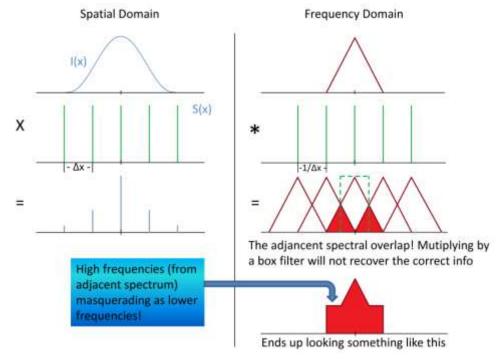

下面我们看一下 fs < 2fh 时的情况,如图 1-7 所示。

图 1-7 欠采样信号时域和频域对比

在图 1-7 中,由于采样频率 f<sub>s</sub> 较低,频域信号的周期间隔Δx(即 fs)也变小了。因此被 采样信号在周期化之后,两个相邻周期的信号出现了混叠,见图中红色部分。这种情况下, 出现混叠的信号在被还原时无法正确的还原出原信号的全部信息。

从上面的分析我们可以看到,时域上的等间距采样相当于频域里信号频谱的周期性搬移,这解释了混叠现象的发生。因此,对于 DC 到 f<sub>h</sub> 的信号采样来说,为确保正确还原出信号的全部信号,过采样是必须遵循的原则。而在对带通信号采样时,我们可以利用混叠来帮助我们降低系统的设计难度。下一节中我们就将介绍利用过采样与欠采样,以及他们各自的优缺点。

### 2.5 混叠

在上一节中我们介绍了过采样和欠采样的概念。实际上过采样与欠采样分别有各自的优 点和缺点,可以根据不同的需要分别加以利用。下面我们就将分别讨论过采样和欠采样各自 的优缺点,并着重讨论如何正确利用混叠。

#### 1) 过采样

图 1-5 上图中时域中黑点所代表的即是过采样所得到的数据波形,过采样时每个信号周期内采样次数大于 2 次。不难理解,每个信号周期内采样点越多,越能够真实还原被采样的信号。图 1-8 从频域的角度分析了过采样的主要优点:一是降低带内量化噪声,二是减小抗混叠滤波器的设计难度。

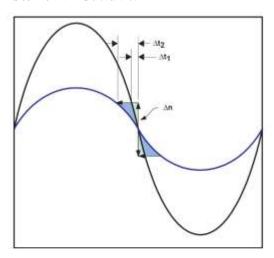

图 1-8 k 倍过采样的量化噪声频谱

图 1-8 分别给出了  $f_s$  及 K 倍  $f_s$  采样后得到的频谱。根据 1.3 节所讲的量化噪声的概念,在采样过程中产生的量化噪声均匀分布在从 0 到  $f_s/2$  的频域范围内,其功率为

$$e_q^{rms} = \frac{LSB^2}{12}$$

由上式可知,量化噪声功率只与最小分辨率有关,与采样频率无关,因此若我们将采样 频率增大到原来的 K 倍,由于量化噪声总功率仍保持不变而分布区间扩大到了 O - Kf./2,所 以量化噪声的功率谱密度减小为原来的 1/K, 如图 8 中绿框部分所示。因此如果我们对采样 后的数据应用一个数字低通滤波器到感兴趣的频带,就可以有效减少感兴趣频带的带内量化 噪声总量,从而有效提高带内的信噪比。如图 8 右图中蓝框部分所示。

在 AD 转换过程中,输入信号会夹杂噪声,其中部分噪声的频率可能大于奈奎斯特频 率。如果转换后我们感兴趣的信号频谱在 0 - f<sub>\*</sub>/2 内,大于奈奎斯特频率的噪声就会混叠到 0 - f<sub>6</sub>/2 内从而干扰或污染我们感兴趣的信号。因此在过采样应用中,我们一般要先用低通滤波 器将大于奈奎斯特频率的噪声过滤掉,再把信号送入 ADC 的输入端,这种滤波器叫做抗混叠 滤波器。

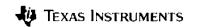

例如在图 1-9 上半部分中,要对一个 10MHz 的正弦波采样,采样率为 30MSPS,这时奈 奎斯特频率为 15MHz。我们看到频谱上 20MHz 处有一个毛刺,如果不使用抗混叠滤波器, 那么 20MHz 处的噪声就会混叠到 10MHz 上,污染我们感兴趣的信号。此时,我们必须使用 一个截止频率为 10MHz, 过渡带仅有 10 MHz(10MHz 到 20MHz)的一个低通滤波器来做为 抗混叠滤波器。如果你设计过低通滤波器,你就知道要在仅仅 2 倍频程的过渡带上设计一个 陡峭的滤波器是多么的不容易: 一个单极点的滤波器在 2 倍频程中只能提供 6dB 的衰减。因 此如果仅仅要求把 20MHz 处的噪声电压衰减 10 倍(-20dB),就已经需要一个 4 阶的低通滤 波器。而如果我们把采样率提高到 60MSPS,奈奎斯特频率提高到 30MHz,这次我们只需担 心 50MHz 的信号是否会混叠到感兴趣的 10MHz 信号上了,这时的抗混叠滤波器的过渡带为 10MHz 到 50MHz, 此时一个两阶的截止频率为 10MHz 的低通滤波器就可以完成将 50MHz 处的干扰信号衰减 10 倍(-20dB)的工作。模拟滤波器的设计难度被大大降低了。

#### 2) 欠采样

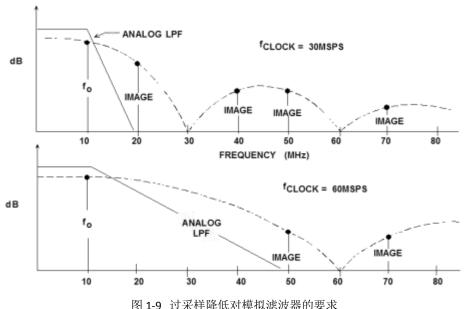

和过采样对应,欠采样是指  $f_h > f_s/2$  时的情况。利用混叠现象,我们可以实现利用较低的采样频率对高频带通信号进行采样,从而节省系统的成本、功耗、PCB 面积及模拟前端设计复杂度。

根据香农采样定理,采样频率  $f_s$  只要大于信号带宽  $f_a$  的 2 倍以上,信号的信息就可以完整的被保留下来。在这里,信号可以是一个带通信号,带宽为  $f_a$ =  $f_h$  —  $f_l$ ,以  $f_c$  为中心。也就是说信号  $f_h$  频率可以大于奈奎斯特频率  $f_s$ /2,只要保证带宽低于  $f_s$ /2 就可以采得完整的信号。b) BW = 135 - 180MHz,Fs = 90MSPS

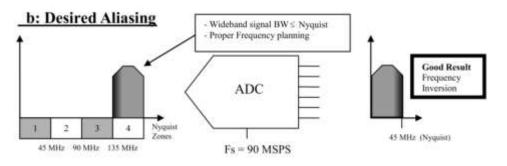

图 1-10 及所示的就是 4 种欠采样的情况,通过分析我们可以了解一个正确的欠采样所需的条件。

a) BW = 90 - 135MHz, Fs = 90MSPS

b) BW = 135 - 180MHz, Fs = 90MSPS

图 1-10 几种不同欠采样分析-正确的欠采样应用

在图 1-10 a)中,信号频率从 90MHz 到 135MHz,信号带宽  $f_a$ = 135-90 = 45MHz,如果用 90MHz 的采样频率进行采样,得到的信号频谱被搬移到了 0 - 45MHz 的范围内。这是我们期望的混叠。图 1-10 b)的情况类似,信号频率从 135MHz 到 180MHz,带宽仍为 45MHz,采样之后利用混叠在频域上得到的信号和 a)中的相同。实际上在采样后,由于混叠的特性,在每个  $Kf_s$ (K = 0, 1, 2, …)附近都会有信号的镜像,这就是欠采样的原理。

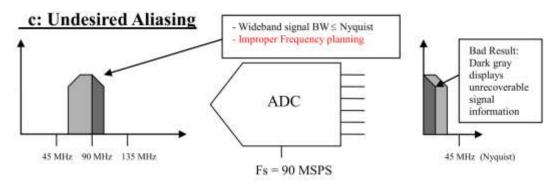

a) BW = 55 - 100MHz, Fs = 90MSPS

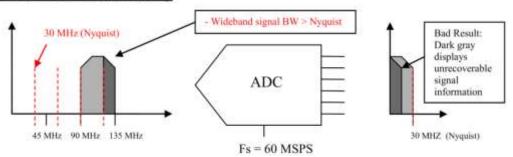

### d: Undesired Aliasing

b) BW = 90 - 135MHz, Fs = 60MSPS

图 1-11 几种不同欠采样分析-不合适的欠采样应用

但是欠采样必须满足两个条件,一个是选取的  $f_s$  不能导致被采样的带通信号跨越了  $Kf_s/2$  的分界线,我们称之为不正确的频域规划。如图 1-11 a)中,尽管带宽  $f_a$  仍为 45MHz,但信号分布在 60MHz 到 105MHz 的范围内,中间跨越了 90MHz 的分界线,采样的结果是不正确的,右边图形中带通信号重叠在一起,无法分开。另一个是选取的  $f_s$  必须大于两倍的信号带宽,b)中信号带宽为 45MHz,但采样频率变为 60MHz,这样被采样信号的带宽超过了  $f_s/2$ ,信号也无法被完整采样。从上面 2 个例子中可以总结出,要想让欠采样后的信号能够完整反映出被采样信号的信息,必须使满足如下两个条件:

1. f。必须大于两倍的信号带宽 fa:

2. 被采样的带通信号处在  $Kf_s/2$  到(K+1) $f_s/2$  的频段内,不能跨域  $Kf_s/2$  这条分界线。其中 K=0,1,2,...

本节对过采样和欠采样作出了分析,过采样的优点是: 1. 量化噪声功率总量被分摊到fs/2 的频域中,fs 越高,量化噪声的噪声功率谱密度越低,经过数字低通滤波器后的带内噪声总量越低; 2. 截止频率和干扰频率之间的过渡带较宽,利于简化滤波器的设计。而欠采样的优点是可以利用较低的采样频率对高频带通信号进行采样,节省系统成本、功耗、PCB 面积并简化模拟前端的设计。

# 第二章 ADC 性能指标

实际应用时,由于 ADC 并不是理想 ADC,所以我们在使用时需根据不同应用场景选择不同的 ADC。在这之前,首先了解 ADC 的各性能指标。

### 3.1 静态精度

静态误差,即就是那些在转换直流(DC)信号时影响转换器精度的误差,可以仅用 4 个术语描述整个静态误差。它们是偏置误差,增益误差,积分非线性误差以及微分非线性误差。每一个可以用 LSB 单元表示或者有时用 FSR 的百分比表示。例如,对于一个 8 位转换器 1/2 LSB 误差对应于 0.2% FSR。

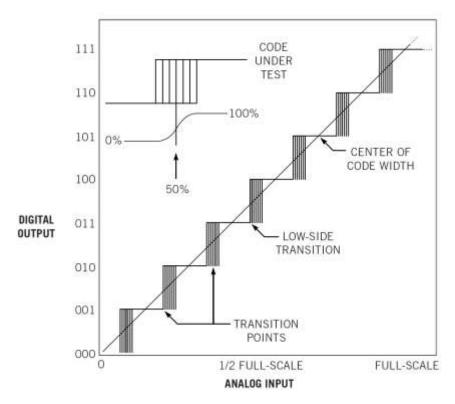

### 3.2 偏置误差

偏置误差为 1 位最低有效位的 3 位 A/D 转换器转换特性如图 3-1 所示。Y 轴对应输出码字,坐标 X 轴对应模拟输入信号幅度。在数量上,偏置误差为当输入等于 0.5 个最低有效位时,第一个码字转换(从 000 到 001)偏离理想位置的值。另一种求取偏置误差的方式是检查图中 X 与 Y 之间的截距,另外就是直线通过实际转换函数时所截取的 X 坐标。偏置误差引起整个函数曲线转换向 Y 轴方向移动(输出码是独立变量)。偏置误差通常用最低有效位、伏特或者是最大量程的百分数(%FSR)来表示。

图 3-1 1 个最低有效位的偏置误差

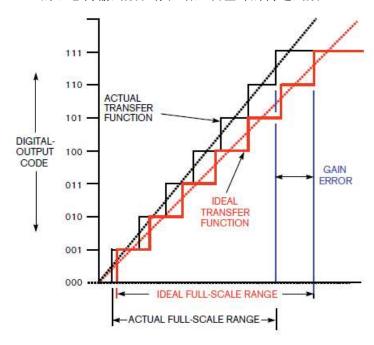

#### 3.2.1 增益误差

图 3-2 给出了具有增益误差的 3 位 A/D 转换器的转换函数,从图中可以看出,增益误差可以描述为直线通过转换函数曲线时,在满量程处的偏差。同时,它也可以描述为+1 的理想增益范围的偏差。虽然增益误差通常被表示成满量程的百分比(%FSR),但它也在电压或者最低有效位上有详细说明。增益误差由转换参考电压的误差所决定,因为参考值决定了器件的满量程。

图 3-2 正向增益误差

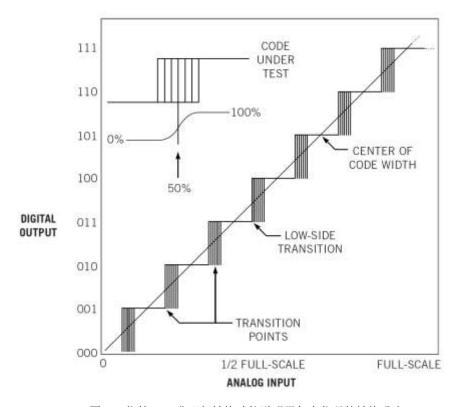

### 3.2.2 微分非线性

微分非线性通常用来描述在转换过程中发生码字跳转处的输入电压偏离理想转换电压的大小。图 3-3 给出了微分非线性误差的一个例子。每个码字转换应该发生在等效于一个最低有效位的间隔内。例如,对于一个 3 位的 A/D 转换器,如果第一次转换发生在 1/8 的满量程 (0.125 FSR)处,那么理想情况下,第二次转换应该发生在 0.250FSR 处。对于一个特定的码字,偏离理想转换的误差就是微分非线性误差。对于一个转换器来说,微分非线性误差应该描述成所有可能转换过程中最坏情况的转换误差。

图 3-3 微分非线性

当用最低有效位来衡量转换器的分辨率时,如果微分非线性误差大于等于-1LSB 的话就暗示有一个码字丢失了。大部分转换器在都指定了"无丢失码" 达到何等精度,一般情况下都有"无丢失码"精度等于 A/D 转换器的转换精度即位数。在某些情况下,无丢失码精度小于给定转换器的精度:例如,许多 16 位的转换器可以保证无丢失码精度达到 15 位。一个具有无丢失码字的 16 位的转换器有 65535 种可能的输出码字。如果微分非线性被指定的的无丢失码字是 16 位,那么所有的可能输出码字都必须存在。"无丢失码字"这个规格不能用户提供给出关于码字宽度的任何信息;简单地说,每个输出码字的一些部分都是存在的。如果一个 16 位的转换器的微分非线性误差大于等于-1LSB,那么在任何输出状态中只能保证15 位的信息是有效的。如果转换器指定了 15 位的无丢失码字,那么在任何给定输出范围中只能确保 15 位。正误差表示长码,它的值没有实际的限制,并且跟分辨率不相关。微分非线性的一个简单测试是:加输入电压直到转换开始时,此时测量出驱动转换开始所需的输入电压。然后,驱动下次转换开始的输入电压也可以测量出来,将这两次转换过程中的输入电压差减一个最低有效位后,将其定义成转换过程中的微分非线性误差。在这里,需要注意的一点是在测试微分非线性过程中,A/D 转换器中会产生噪声。由于噪声通常是高斯噪声,其平均值将接近于真实的微分非线性值。

#### 3.2.3 积分非线性

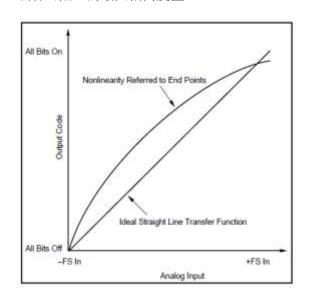

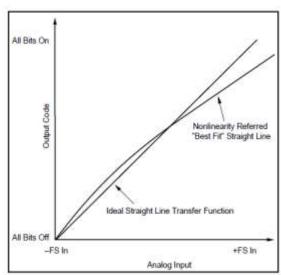

积分非线性用来描述 A/D 转换器转换函数的整体形状。这个误差通常被定义为静态线性 或者是绝对线性。图 3-4(a)给出了积分非线性与终点相关的一个例子,图 3-4(b)给出了 积分非线性与最佳直线相关的一个例子。对于线性的终点,在转换器的偏置和增益交叉点之 间画一条直线,那么转换函数曲线将背离那条直线。与那条直线之间的最大偏离是非线性积 分的最坏情况。对于一个最佳情况的例子,此转换在一个最小二乘估计中被用到,先绘制最 佳直线,那么转换函数曲线将背离此最佳直线。以终点线性为例,与最佳直线的最大偏离量 描述了转换器的积分非线性。积分非线性也能通过对同一极性的微分非线性误差进行求和或 者积分而得到。对于积分非线性的一个直接定义是 A/D 转换器中偏离所选直线(理想、最佳 或者终点)的最大偏离度量。

图 3-4 (a) 参考输入的非线性积分 (b) 参考最佳直线的非线性积分 ADC 分类

#### 动态指标 3.3

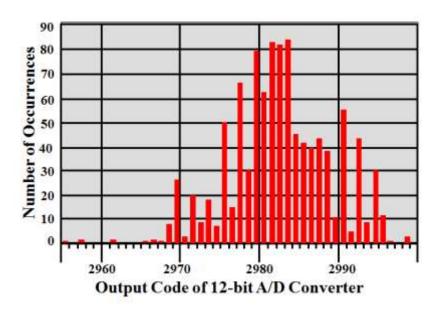

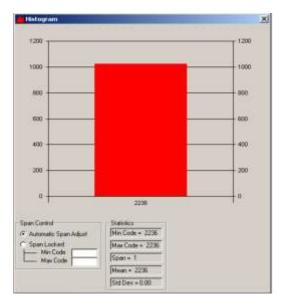

在精密信号链中,我们的 ADC 测试主要关注 ADC 的直流精度,包括其 DNL, INL, 失 调,最小分辨率和 ADC 的输入噪声。我们通常不会在频域来计算对直流采样 ADC 的 SNR, 这是因为频域计算基于一个单频正弦波,而我们在精密 ADC 采集中面对的常是变化非常缓 慢的信号。因此对于直流采样 ADC 来说,在时域上能达到的最小分辨率和系统噪声是我们 关注的焦点。

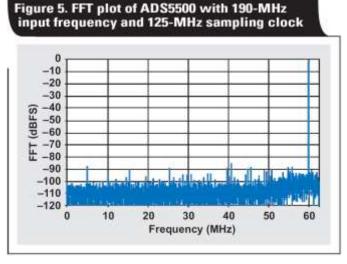

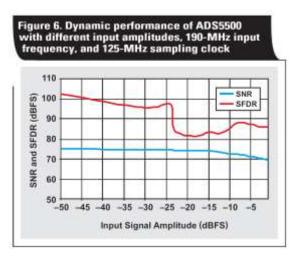

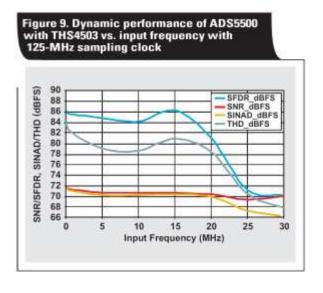

当然,这些 ADC 很多也拥有数百 KSPS 甚至数 MSPS 的采样率,在音频范围内的交流信号采样也是非常有用处的。这时我们需要从另一个角度来衡量 ADC 的表现。对交流信号采样的 ADC 来说,我们关注更多的是其可重复性,也即频域特性,ADC 的 INL 会显著的影响 ADC 输出的总谐波失真,采样抖动会显著的影响 ADC 的 SNR,我们常用的衡量高速 ADC 性能优良的几个指标就是采样率、输入-3dB 带宽、SFDR、SNR 和 ENOB。动态指标是在频域中来表征的,通常利用快速傅里叶变换(FFT)来得到动态规格。下文将通过一个实例来重点介绍后面三个指标。

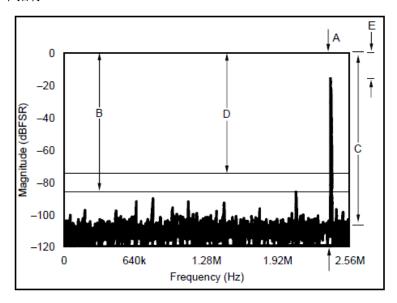

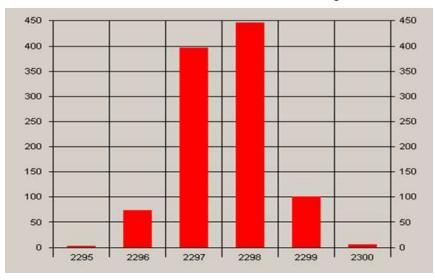

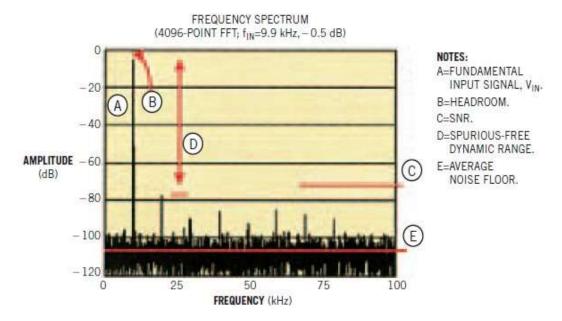

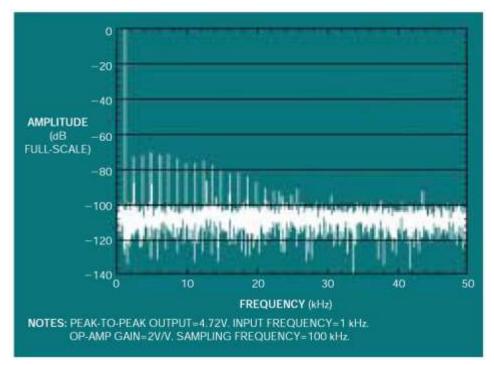

图 3-5 动态规则

如图 3-5 所示为一个 FFT 变换后的频域图,这个特定的 FFT 来自一个 ADS850,一个 14 位,采样频率为 10MHz 的 A/D 转换器。输入的测试信号频率为 2.35MHz 的正弦波。

基本输入信号(A)的频率是 2.35MHz,它也是模拟信号的输入频率。在目标频率处发现其强度低于 0dB,由于个余量出现,这就是净空(E),它通常用来避免当 A/D 转换器或信号源有偏差的时候产生限幅现象。净空在大部分 FFT 测试中设为 0.5dB。为了描述方便,图 3-5 将净空进行了一定的放大。

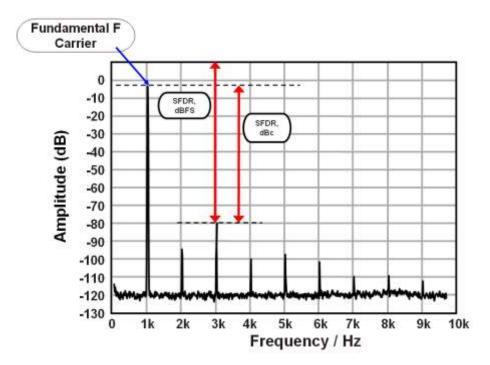

### 3.3.1 无杂波动态范围(SFDR)

转换器的无杂波动态范围(SFDR)定义为(B):在输出频谱中,基频分量与最大谐波间的距离(dBc),当然最大谐波不局限在基频产生的高次谐波分量上。输入信号谐波的寄生毛刺响应以谐波阶数来标记。这些谐波对应于输入采样保持放大器的非线性特性。从图中可以看出有一些寄生毛刺并非输入信号的谐波。这些寄生毛刺来自采样过程。

当使用运放来驱动ADC时,运放的谐波失真会影响到ADC的输出谐波失真。为了确定一个放大器+ADC系统的SFDR值,需要将放大器输出信号的频谱与ADC的频谱叠加,由于电气距离的不同导致了不同的相位位移,因此这两种信号源只有通过功率的型式相加。ADC输出的FFT是在一个特定的输入级别上计算,通常是-1dBFS。放大器的谐波也应该在这个级别上进行测量。然后放大器与ADC各自的谐波幅度将会被从dBc转化为标量并且相加。结果再转化为dBc,方程如下:

$$HDx_{Combined}(dBc) = 10 \times log_{10} \left[ 10^{\left(\frac{HDx\_Amp}{10}\right)} + 10^{\left(\frac{HDx\_ADC}{10}\right)} \right],$$

其中HDx Amp与 HDx ADC分别是放大器以及ADC属于谐波分量的寄生毛刺,以dBc表示。

一些简单的关系有助于在不需要任何数学计算的情况下快速的对系统进行分析。如果ADC和运放的谐波大小相等,则总的谐波大小加上3.01 dB。如果在不同的谐波级别之间差别大于10 dB,忽略较小的一个只会带来很小的误差。

对于一个线性放大器来说,最显著的寄生毛刺通常是二阶、三阶谐波。一般仅需评估这 两阶谐波即可。

#### 3.3.2 信噪比(SNR)

平均噪声基底(C)来源于 A/D 转换器的平均噪声和 FFT 本身。FFT 中理想的平均噪声基底可以描述为:

$$6.02n + 1.76 + 10\log(m/2)$$

这里, n 为 A/D 转换器的分辨率, m 为 FFT 的点数。

A/D 转换器的噪声特性 (D) 用信噪比 (SNR) 来衡量。SNR 中的 S 是输入基频的有效功率, N 是在奈奎斯特频带范围内除直流分量和基频以外的所有谐波的有效功率之和。理论上, SNR=6.02n+1.76, 这里 n 为分辨率。

那么, 这个理想表达式是从何而来的?对于一个实际的 ADC 而言,如何测量 SNR 的值?

SNR 是通过计算得到的值,它代表了信号的有效值和噪声的有效值之间的比值。然后,对这个比值取 log<sub>10</sub>,再乘以 20,从而得到 dB 形式的 SNR 的值。

推导上述公式,首先需要确定信号的有效值。假设输入信号是正弦信号,则信号的有效值等于 ADC 的满幅度量程除以 $\sqrt{2}$ 。如果 ADC 的增益为 1,你可以将信噪比的等式转换为用比特数表示:信号有效值= $\left(2^{(N-1)}\times q\right)/\sqrt{2}$ ,这里 q 表示最小比特步长(1LSB)。

所有 ADC 都会由量化误差而产生量化噪声((在理想情况下,ADC 的唯一噪声来源是其量化噪声)),由此而产生的噪声有效值等于  $q/\sqrt{12}$  。这个式子的得来如下:

任何 ADC 的不确定值的大小等于 $\pm 1/2$  LSB。当然,这种假设是基于 ADC 是没有差分非线性误差的理想 ADC。现在我们需要确定的是 1LSB 的有效值。我们可以认为量化误差是由模拟输入信号引起的三角波,而三角波信号的有效值等于信号幅度除以 $\sqrt{3}$ ,所以最终得到的噪声有效值= $\pm (LSB/2)/\sqrt{3} = q/\sqrt{12}$ 。

然后,对这些数字进行整理:

SNR(dB)=

$$20\log\frac{信号有效值}{噪声有效值}=20\log\left(\frac{\left(2^{N-1}\times q/\sqrt{2}\right)}{q/\sqrt{12}}\right)=6.02N+1.76$$

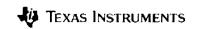

在一个 A/D 转换器中可接受的 SNR 值可以按下列规则计算:将分辨率乘以 6。例如,对于一个 8 位的 A/D 转换器,那么一个好的 SNR 是 48dB,对于一个 12 位的 A/D 转换器,那么一个好的 SNR 是 72dB。因为在高分辨率(高于 12 位)的 A/D 转换器系统中放大器的 1/f 噪声很难得以降低,在这些高分辨率转换器中难以确保"6倍"准则。

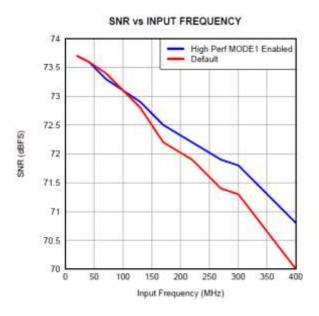

对于那些高分辨率的转换器,SNR 值在一定程度上依赖于输入信号的频率。对于一个给定的采样频率 fs,理论上讲,从直流到 fs/2 频率带宽范围内的有效功率量化噪声是给定的。此处 q 是一个 LSB 的代表的权值,n 是位数。当输入信号频率与采样频率之比增加时,那么量化噪声将分散在更加狭窄的带宽内,导致模拟输入带宽内噪声的增加。图 3-6 给出了采样

图 3-6 ADS4122 对于的输入频率的 SNR 值

率为 65MSPS 的 12 位 A/D 转换器(ADS4122)相对于输入频率的 SNR 值。当转换器的输入频率增加时,其 SNR 值缓慢下降。对于高速度或者高分辨率的转换器而言,随着输入频率的增加,那么 SNR 值下降的更加明显。在时钟抖动一章,我们会解释这个现象。

在实际测试中,正弦输入信号的噪声应小于 ADC 理想噪声的 1/3,在这种情况下,信号有效值才准确等于信号幅度除以 $\sqrt{2}$ 。

计算 SNR 的时候我们不把谐波能量计算到噪声中去:  $SNR = 10\log_{10}(P_s/P_N)$ , 这里, Ps 是基波信号功率, $P_N$  是所有噪声频率分量的功率之和; 而 SINAD(信号与噪声加谐波失真比)将将谐波功率包括在噪声的计算中:

$$SINAD = 10\log_{10}(\frac{P_s}{P_N + P_D})$$

, 这里,Ps 是基波信号功率,P<sub>N</sub> 是所有噪声频率分量的功

率之和, Pp 是所有失真频率分量的功率之和。因此 SINAD 肯定会小于 SNR 的值。

我们还可以利用 SINAD 来估算出 ADC 的有效位数(effect number of bits, 简称 ENOB): ENOB=(SINAD-1.76)/6.02;

运放+ADC组合系统的ENOB可以通过将放大器的有效位数以及ADC的ENOB以功率的方式相加来得到。如果放大器的ENOB与ADC的ENOB相等,则SINAD的数值也相等。在这种情况下,组合的SINAD将会降低3.01 dB,组合的ENOB将会减少0.5位。

# 第三章 ADC 选型指南

### 4.1 常见 ADC 结构特点与应用场景

现代常用的 ADC 分为逐次逼近型 ADC(SAR 型),Delta-Sigma 型,和流水线型 ADC(Pipeline 型)三类。他们各自有着不同的精度和速度范围,从而有着不同的应用领域。下面讲究 SAR 型 ADC,  $\Delta$   $\Sigma$ 型 ADC 以及 Pipeline 型 ADC 原理与结构分别进行阐述。

| ADC 类型   | 转换速率                                                                        | 分辨率                                                                        | 优缺点              |  |  |

|----------|-----------------------------------------------------------------------------|----------------------------------------------------------------------------|------------------|--|--|

| SAR      | ≤ 4Msps<br>≤ 1.25Msps                                                       | $\leq 16 - \text{bit}$<br>$\leq 18 - \text{bit}$                           | 操作简单,低成本,低<br>功耗 |  |  |

| ΔΣ       | ≤ 4ksps<br>≤ 4Msps<br>≤ 10Msps                                              | $\leq 31 - \text{bit}$<br>$\leq 24 - \text{bit}$<br>$\leq 16 - \text{bit}$ | 成本适中             |  |  |

| Pipeline | $\leq 200 \text{Msps}$<br>$\leq 250 \text{Msps}$<br>$\leq 1000 \text{Msps}$ | $\leq 16 - \text{bit}$<br>$\leq 14 - \text{bit}$<br>$\leq 12 - \text{bit}$ | 高速转换,价格高,功<br>耗大 |  |  |

表 4.1 四种常见 ADC 特性及应用

### 4.2 SAR 型 ADC

## 4.2.1 SAR 型 ADC 结构与原理

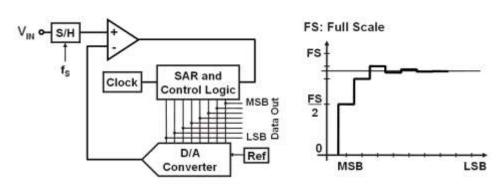

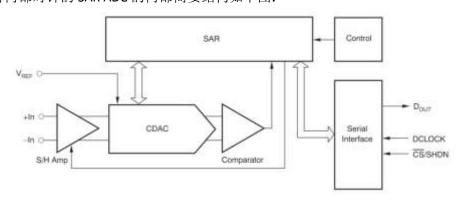

SAR 型 ADC,即逐次渐进逼近型 ADC,采用的是多次比较的方式来获得最终的输出结果,具有简单易用,功耗低的特点。我们先看图 4-1,这个老旧的结构可以帮助我们容易地理解SAR型 ADC 的工作过程:

图 4-1 经典 ADC 结构

如上图,假设输入信号的伪代码为 45, ADC 为一个 6 位的 ADC,满量程输出为 63。

- 1. 在采样阶段, ADC 将输入信号采样至采样保持器(S/H)中并保持住,即此时 S/H 中的值为 45,请记住 S/H 中实际是一个模拟电压, 45 是我们给它定义的代表它大小的伪代码;

- 2. 接下来,在转换的第一个时钟上升沿,SAR 寄存器首先将最高位至 1,即把 32 (半个满量程),送给一个 DA 转换器,DA 转换器输出的模拟信号和 S/H 中的模拟信号相比较,因为 45 大于 32,比较器输出为高,提示 SAR 的最高位应该置 1,在时钟的下降沿,ADC 就将输出最高位数据 (MSB)为 1;

- 3. 在第二个转换时钟的上升沿, SAR 会将 MSB-1 位置 1, 此时由于 MSB 已经固定为 1, SAR 寄存器中的值实际为 48(32+32/2),由于 48 大于 45,比较器输出为低,提示 SAR 寄存器的 MSB-1 位应该为 0,在时钟的下降沿,次高位的 0 也被输出,同时 SAR 寄存器也记住了次高位为 0 的事实;

- 4. 依次类推,最终可以得到输出结果为: 101101。

从上述过程中可以看出,SAR 寄存器的位数越多,逼近得越准确,但所需的转换时间越长。

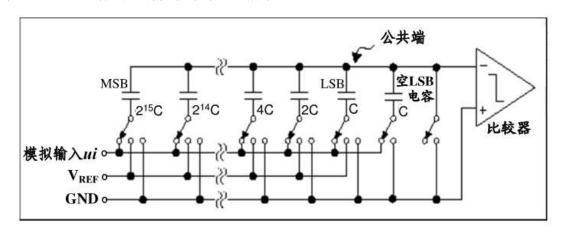

为提高 SAR 型 ADC 的总体转换速度,减少内部 DAC 的建立时间对速度的影响,现代的 SAR ADC 多数采用电荷重分配的 CDAC 输入结构,将采样保持与 DAC 合为一体。

若 SAR 型 ADC 的分辨率为 n 比特,则其内部由 n 个按照二进制加权排列的电容和外加一个 "空 LSB" 电容组成的阵列,如图 **4-2** 所示。

图 4-2 现代 ADC 电容式 DAC 结构

在采样阶段,电容阵列公共端,即比较器的输入端接地,自由端连接到模拟输入 ui 上,使得电容阵列上的电压与 ui 成正比。而在保持阶段,公共端与地断开,所有电容的自由 端接地,比较器输入电压等于-ui。由此可见电容阵列起到了采样保持功能。

图 4-3 采样阶段(左)和保持阶段(右)

其转换比较方法仍然采用对分法逐次逼近。我们发现图 4-2 中的电容网络从"空 LSB"电容开始,第一个 C 和第二个 C 并联,构成了一个 2C 的等效电容,而这个等效电容又和下一个 2C 电容并联,构成了 4C 的等效电容,依次类推,构成了一个电容分压网络,而且每向后一级(从左向右),其电压为上一级的 1/2。其对分法比较过程如下:

- 1. MSB 电容自由端接 Vref, 其余电容自由端接地,此时公共端的电压为 1/2Vref;

- 2. 如果输入电压 ui 大于 1/2Vref, 比较器输入为-ui+1/2Vref 仍然小于零, 此时比较器输出为逻辑"1";

- 3. 保持 MSB 电容与 Vref 相连,将下一个电容连接到 Vref,重复上面的判断过程,确定输出数字值:

- 4. 依次循环指导判定全部数字位。

从上述描述可以看出电容阵列的 SAR 型 ADC 好处在于减少了传统 SAR 型 ADC 中由于 DA 引入所需的建立时间。但同时,其内部的电容值随着 ADC 位数增长呈指数级增长,带来的后果是电容体积的增大,以及对芯片工艺要求的增高。这也就解释了为什么 SAR 型 ADC 的精度不会太高。

#### 4.2.1.1 使用运算放大器驱动 SAR型 ADC

对于一个 SAR 型 ADC,在设计其电路时应当首先考虑的是采样速度和外部信号源内阻。如果忽略这些基本参数,不管是微处理器中内置的还是外置的 ADC,都得不到最好的输出。

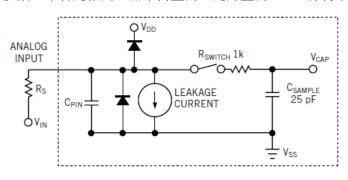

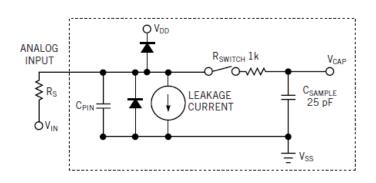

图 4-4 SAR 型 ADC 的输入级模型

首先我们来看 SAR ADC 的输入级,图 4-4 描述了一个典型的 SAR ADC 的输入级模型,从左向右来看,图中可以看出外部输入的阻抗为 Rs。通常如果用运算放大器来驱动 SAR ADC,运用运放阻抗变换的特点,这个阻抗可以小于数十欧姆(视运放的开环输出电阻和环路增益而定)。但如果采用电阻电桥这类高阻元件直接作为信号源,Rs 通常可以达到数千欧姆。信号经过 Rs 后进入 ADC 的模拟输入端。

进入 ADC 内部的信号遇到的第一个障碍就是输入引脚电容 C<sub>PIN</sub>和 ESD(静电放电保护)二极管。这些对输入信号的影响微乎其微,这里将忽略它们,同时忽略的还有输入漏电流。

接着,信号到达导通电阻为 RSWITCH 的开关,采样电容 C<sub>SAMPLE</sub>。当开关闭合时,可用 C<sub>SAMPLE</sub> 来代表主要的采样电路; 而输入信号源内阻 Rs, 开关导通电阻 R<sub>SWITCH</sub> 和采样电容 C<sub>SAMPLE</sub> 的联合作用构成了一个单极点的 RC 网络。而这个 RC 网络的时间常数可以表示为:

$$t_{RC} = (R_S + R_{SWITCH}) \times C_{SAMPLE}$$

假设在采样刚开始时候的采样电容上电压为 0,电容上的电压大小与上升时间关系可以 表示为:

$$V_{IN} = (1 - e^{-\frac{t}{(R_S + R_{SWITCH}) \times C_{SAMPLE}}})$$

通过这个方程,可以根据时间变化确定采样电容上的电压达到输入信号电压值的百分比。

如果你将这个思想应用到在一个如图 4-2 所示的 12 位 ADC 的应用中,就能确定已经从输入信号里采样到了多少位的数据(这里位数通过已经采得的电压占输入电压的百分比来换算,如下表,当采样电容上的电压为输入电压值的 99.32%时,将有 0.68%(剩余百分比)的电压无法准确获得,也就是说最小分辨率为 0.68%,这和 7.2 位的 ADC 的分辨率一致。其换算公式为log<sub>2</sub>(1/剩余百分比)。

| 时间常数个数                                      | 1     | 5     | 8       | 9        | 10       |

|---------------------------------------------|-------|-------|---------|----------|----------|

| $(R_s + R_{SWITCH}) \cdot C_{SAMPLE}(nSEC)$ | 25    | 125   | 200     | 225      | 250      |

| 流过 $C_{SAMPLE}$ 的百分比                        | 63. 2 | 99. 3 | 99. 966 | 99. 9877 | 99. 9955 |

| C <sub>SAMPLE</sub> 剩余百分比                   | 36. 8 | 0. 67 | 0. 034  | 0. 0123  | 0. 0045  |

| ADC 精度(位)                                   | 1. 4  | 7. 2  | 11.5    | 13       | 14. 43   |

根据这个表的计算,如果不能给 ADC 足够的采样时间会导致 ADC 的精度降低。举个例子,一个采样时间为 1.5 个时钟周期的 12 位 ADC,在时钟频率为 2MHz 时折算出的采样时间为 750ns。对比表 1,当 RS 为 0 时,采样电容上能获得远高于 12 位的精度,采样时间是足够的。但如果现在对信号源增加 5K Ω 内阻,然后可以得到:如果要达到 13bits 精度,转换器

需要 1350ns 的采样时间,750ns 的采样时间就不再那么保险了。这时,可以通过改变软件来降低 ADC 的采样率来获得更长的采样时间,这个是易于实现的。当然,可以通过添加运放缓冲来降低信号源内阻。这也是为什么我们要使用运放来驱动电容输入 ADC 的原因。

### 4.2.2 在运放和 SAR ADC 间插入 RC 组合

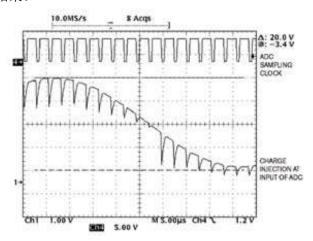

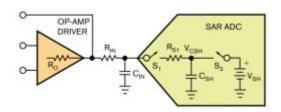

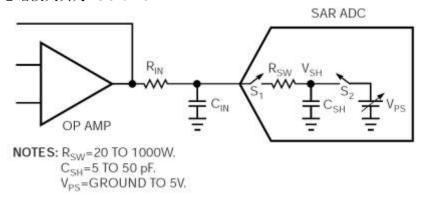

使用运算放大器来驱动 SAR-ADC 看起来是一个简单的任务,好像只要选一个带宽符合 ADC 输入信号要求的运放,然后直接把运放作为缓冲来跟 ADC 相连就可以了。但是不要高兴得太早,你的任务远远没有完成,因为你还没成功解决掉 ADC 输入端电荷注入效应对运放输出造成的影响,如图 4-5 所示。SAR-ADC 输入端的瞬间电流会干扰运放的输出电压,从而导致 AD 输出不准确的结果。

图 4-5 插入电阻后, ADC 电荷注入效应

为了分析 ADC 输入端对运放输出端造成的影响,我们对 SAR-ADC 的输入端进行建模。如图 2 所示,SAR-ADC 的输入端可以等效为一个开关 S1 连接着一个接地电容 CSH; 在电压采样前,CSH 通过开关 S2 连到电源、电压参考或地来进行预充电,预充电电压值由你自己的 ADC 电路决定。电压采样开始的时候,S2 打开而 S1 闭合。当 S1 闭合的时候,驱动电路从 CSH 注入或吸出电荷,而 ADC 需要一定的时间来采样信号。在这个采样时间里,ADC 需要从驱动电路汲取足够的电荷量给 CSH,使得系统达到 1/2-LSB 的精度范围之内。

图 4-6 在运放与 ADC 之间添加 RC 电路

为了使设计的电路精度达到更高,应该在运放与 ADC 之间添加一个电阻 RIN 和电容 CIN (如图 4-6 所示)。CIN 的角色是作为一个电荷存储器来为 ADC 的输入端提供足够的电荷,而 RIN 用于避免运放与的 CIN 直接连接并使得运放工作更加稳定。RIN 与 CIN 的结合至少要符合 ADC 采样时间的要求。最后,我们要选择一个带宽与 RINCIN 时间常数相匹配的运算放大器。

首先最重要的是,你需要给采样电容 CSH 充电足够长的时间使其上的电压达到被采样电压的 $\pm 0.5$ LSB 范围内。理论上来说,对 12 位转换器,充电时间应大于 8 倍 RSW×CSH。考虑到误差容限,器件参数变动,充电时间应取  $\pm 10^{-1}$ 15 倍 RSW×CSH。SAR ADC 需要一增益为 $\pm 1$ V/V 的运放和外接的 RIN 和 CIN 电阻/电容对。在采样期间,ADC 利用 CIN 保持信号稳定;电阻 RIN 将运放和 ADC 负载电容隔离。运放将 ADC 和高阻信号源隔离,同时方便在采样阶段对 CIN 和 CSH 进行快速充电。

设计这样一个看似简单的电路,应遵循以下方法。CIN 须是银云母(silver mica)电容或 COG 电容。这些电容能为 CSH 提供稳定的电压和频率性能。像 X7R,Z5U 这样有电压和频率 "记忆"效应的电容,会降低 ADC 的总谐波失真。另外,CIN 应大于 20 倍 CSH。接下来再利用 ADC 内部电阻,电容决定 RIN: 最终决定的 CIN 和 RIN 时间常数是 CSH 和 RSW 的 70%,RIN 阻值大小为  $50\,\Omega$  〈RIN〈2k  $\Omega$  。当最终 RIN 和 CIN 决定后,运放电路应该在驱动阶跃信号时也能及时稳定到期望的精度。

#### 4.2.2.1 TI SAR型 ADC

TI 提供广泛的 ADC 供用户选择。在登陆 TI 官网后进行数据转换器页面,可以看到页面的左边显示了产品结构树,罗列了不同特性,不同应用场景的数据转换器以及相关的器件。同时在页面可以看到一个数据转换器的快速搜索,单击进入后可以帮助用户更快地在众多ADC中选择适合开发的型号。

图 4-7 TI 网页上的数据转换器

在 SAR 型 ADC 中,TI 有众多不同转换速度,双极型以及同步多通道转换的产品供选择:

| 器件                    | 简介                                           | 封装    |

|-----------------------|----------------------------------------------|-------|

| ADS7 <b>882</b> IPFBT | 12 位,3MSPS,伪差分输入,并行输出 ADC                    | TQFP  |

| ADS7818P              | 12 位,500KSPS,伪差分输入,串行输出 ADC                  | DIP   |

| ADS7886SBDBVT         | 12 位,1MSPS,单端输入,串行输出 ADC                     | SOT23 |

| ADS8504IBDW           | 12 位, 250KSPS, 单端输入 VIN 范围可调(最大±10V)并<br>行输出 | SOIC  |

| ADS8508IBDW           | 12 位,250KSPS,单端输入 VIN 范围可调(最大±10V)串<br>行输出   | SOIC  |

| ADS7950SDBT           | 12 位,1MSPS,单端输入,4 通道选通输入,串行输出<br>ADC         | TSSOP |

| ADS7861E              | 12 位,500KSPS,差分输入,双通道同步采样,串行输出<br>ADC        | SSOP  |

| ADS8319IDGST          | 16 位,500KSPS,伪差分输入,串行输出 ADC                  | MSOP  |

| ADS8317IDGKT          | 16 位,250KSPS,差分输入,串行输出 ADC                   |       |

| ADS8326IDGKT          | 16 位,250KSPS,伪差分输入,串行输出 ADC                  |       |

| ADS8371IPFBT          | 16 位,750KSPS,伪差分输入,并行输出 ADC                  |       |

| ADS8412IPFBT          | 16 位,2MSPS,差分输入,并行输出 ADC                     | TQFP  |

| ADS8509IDW            | 16 位, 250KSPS, 单端输入 VIN 范围可调(最大±10V)串 行输出    | SOIC  |

| ADS8505IDW            | 16 位, 250KSPS, 单端输入 VIN 范围可调(最大±10V)并<br>行输出 | SOIC  |

| ADS8361IDBQ           | 16 位,500KSPS,差分输入,双通道同步采样,串行输出<br>ADC        | SSOP  |

| ADS8365IPAG           | 16 位,250KSPS,差分输入,六通道同步采样,并行输出<br>ADC        | TQFP  |

| ADS8341E              | 16 位,100KSPS,单端输入,4 通道选通输入,串行输出<br>ADC       | SSOP  |

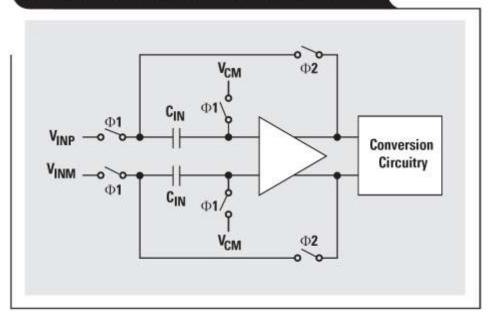

## 4.2.3 $\triangle - \Sigma$ ADC

## 4.2.3.1 △-∑ ADC 结构与原理

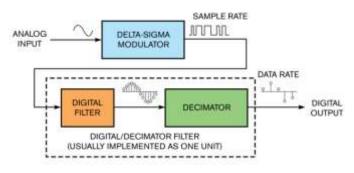

如图 4-8 所示,给出了 $\triangle$ - $\Sigma$  转换器的基本拓扑结构:

图 4-8  $\triangle$ - $\Sigma$  ADC 内部结构

其核心部分是一个 $\triangle$ - $\Sigma$  调制器级联一个数字滤波器。如果仔细探究 $\triangle$ - $\Sigma$  转换器,你会发现,尽管不同 $\triangle$ - $\Sigma$  ADC 的指标各有千秋,但是它们都是包含了这一基本的结构。下面将研究这两个模块的基本架构和功能。

△-Σ ADC 的输入信号是交流或者直流电压信号。我们不妨用一个单频正弦信号作为△-Σ 转换器的输入信号。如图 4-8 所示,转换器内的调制器使用一个 1bit 的 ADC 对输入信号进行采样,产生粗糙的量化输出信号。调制器把模拟输入信号转换成了高速的脉冲数字信号,脉冲的占空比反映了模拟输入电压的大小。尽管调制器产生了含有噪声的输出信号,但是这些噪声将被整形在输出频谱的高频部分,从而在数字滤波器的输出端得到低噪声、高精度的转换结果。

在调制器的输出端,数字滤波器处理高频噪声和高速采样率带来的数据吞吐率过高的问题。因为此时的信号位于数字域中,因此可以用低通数字滤波器来消弱高频噪声,并且用抽取滤波器来降低输出数据的速度。数字/抽取滤波器对调制器的高速 1bit 数据流进行滤波,形成低速的多比特编码。

大多数转换器只有一个采样率,但是△-Σ 转换器有两个:输入采样率(也称为调制器 采样率或过采样速率)和输出数据率。这两个变量之间的比值定义了系统的抽取率(也称为 降采样率)。抽取率与转换器的有效精度是紧密相连的,接下来的部分将研究调制器、数字/ 抽取滤波器和可调节抽取率是如何工作的。

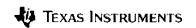

$\triangle$ - $\Sigma$  转换器中采样调制器的输出信号为一连串的 **1bit** 码流,这是由于输入信号通过高采样率的量化器而转换生成的。跟所有的量化器一样, $\triangle$ - $\Sigma$  调制器采样输入信号,产生数字码流表征输入电压。可以在时域或频域观察 $\triangle$ - $\Sigma$  调制器结构,时域下的一阶调制器结构如图 **4-9** 所示。

图 4-9 一阶调制器的调整过程: 时域

调制器利用一个差动放大器(Delta)得到输入模拟信号与反馈 DAC 输出的模拟信号之间的差值,积分器(Sigma)对差动放大器的输出模拟信号进行积分,并把积分的输出信号(斜坡信号)送入到比较器(1bit 的模数转换器)中,积分结果被转换成"1"或者"0"的数字信号。在系统时钟下,ADC 把 1 位的数字信号送到调制器的输出,与此同时,通过反馈环路,把该数字信号送入 1 位的 DAC 的输入端。

1 位 ADC 把输入信号量化成离散的输出编码,包含有转换器的量化噪声(e<sub>i</sub>)。调制器的输出等于输入加上量化噪声(e<sub>i</sub> -e<sub>i-1</sub>)。在上述公式中,量化噪声等于当前的量化误差信号(e<sub>i</sub>)减去调制器前一个周期的量化误差(e<sub>i-1</sub>),即 e<sub>i</sub> -e<sub>i-1</sub>,量化噪声被进一步降低了。时域下的输出信号是代表输入的脉宽信号,频率等于调制器采样频率 fs。如果把输出脉冲序列平均化,结果将等于输入信号。

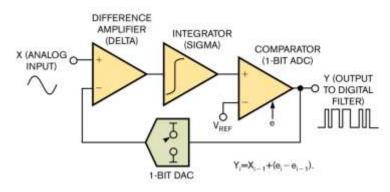

图 4-10 所示的结构框图从频域解释了调制器的工作原理。时域下的输出脉冲信号在频域下表现为输入信号的频谱加上被整形的噪声信号频谱。被整形的噪声特性(低频处的噪声被推到高频处)从频域上体现了调制器的关键作用。

图 4-10 频域上,调制器的关键作用是噪声整形

与一般的调制器不同, Δ-Σ 调制器中的积分器能够对量化噪声进行整形。调制器输出的噪声功率谱不是平坦的。更重要的是,通过频域分析,就可以清楚的看到调制器是如何把噪声整形到高频处,进而在感兴趣的频段得到高分辨率的结果。

在调制器输出中,量化噪声在 OHz 处是非常低的,然后随着频率的增加而急剧上升,并且在调制器采样频率处达到最大值。

在一阶调制器只积分一次的基础上,二阶调制器通过积分两次,来进一步降低低频量化噪声。很多 $\triangle$ - $\Sigma$  调制器的阶数甚至更高,如当前比较流行的 $\triangle$ - $\Sigma$  转换器通常会包含二阶、三阶、四阶、五阶或者六阶的调制器。高阶调制器能够把更多的量化噪声整形到高频处。

接在△-Σ 调制器后面的模块是数字/抽取滤波电路,它对调制器输出的 1bit 码流进行滤波和抽取。在调制器的输出端,高频噪声和高速采样率(意味着高速数据输出率)是两个难题。然而,由于此时的信号位于数字域中,因此,可以用一个低通滤波器来削弱噪声,同时,用抽取滤波器功能的电路来降低输出数据吞吐率。设计师常常把数字滤波器和抽取电路放在一起来设计。

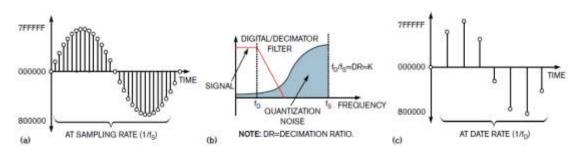

图 4-11 显示了信号在数字/抽取滤波器传输过程中的变化情况。数字滤波器的工作频率与调制器的采样速率是相同的(如图 4-11a 所示)。可以看出,24 位的代码流与原始信号波形一致。时域模型下,数字滤波器不仅降低了Δ-Σ 转换器的噪声从而提高了转换器分辨率,同时数字滤波器还降低了系统噪声,这是因为调制器将低频段的量化噪声整形到高频处,滤除高频噪声即可实现低频处的采样精度提升(如图 4-11b 所示)。

图 4-11 数字滤波器输出端产生一个高分辨率的结果(a),同时抑制了高频噪声(b)。抽取滤波器降低了输出码率(c)

数字滤波器的功能在于提供一个高分辨的数字信号来描述输入模拟信号,但是数据速度仍然因太快而不能利用。尽管看起来得到了大量的高采样速率下的高质量、多比特的采样信号,但是这些数据中大部分是用不着的。因此,数字/抽取滤波器的第二个功能就是降低数据吞吐率。抽取是一个把输出数字信号的高速率降低到系统的奈圭斯特频率的过程。一种实现降采样功能的简单方式就是对一组 24 位的数据进行平均化(如图 4-11c)。降采样器通过累加这些高分辨率的数据、每几个数据做一次平均、输出平均结果、并清空计算所用的数据开

始下一个平均过程。实现低功耗抽取功能的更为简单的方法就是,每 K 个样本抽出一个 24 位的结果(其中,K 等于抽取率或降采样比率,也有文章称为过采样比率。数值上都等于调制器采样速率与输出数据吞吐率的比,抽取率指与调制器频率比,输出数据速率被降低了 K 倍; 而过采样比率指与输出数据速率比,调制器采样频率高 K 倍),这样就不需进行累加和平均计算。

几乎所有的 $\triangle$ - $\Sigma$  转换器都包含一类平均滤波器,称之为 sinc 或者 FIR 滤波器,根据滤波器的频率响应来命名。许多 $\triangle$ - $\Sigma$  器件都用 sinc 滤波器来实现两级抽取。工业用途的低速 $\triangle$ - $\Sigma$  ADC 一般只用一个正弦滤波器。

在频域中,数字/抽取滤波器对于信号来说是个低通滤波器(如图 4-11b 所示)。通过这种方式,数字/抽取滤波器大大抑制了调制器的高频量化噪声。量化噪声被衰减后,感兴趣的信号将重新出现在时域中(在对调制器输出的数字信号滤波之前,数字化后的感兴趣低频信号淹没在高频噪声里,时域上很难分辨出来)。

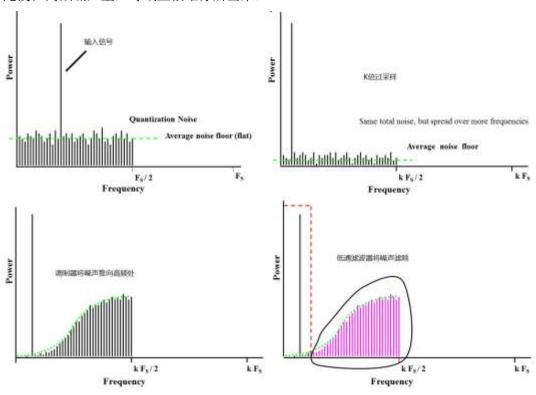

图 4-12  $\Delta \Sigma ADC$  通过过采样实现精度的提升

图 4-12 更加清晰地解释了  $\triangle$   $\Sigma$  ADC 如果通过过采样来实现精度的提升。从左到右,从上至下来看,首先第一张图为采用最小采样率还原 Fs/2 以内的信号,在这种情况下,我们知道信号的信噪比 SNR=6.02N+1.76dB,其中 N 为 ADC 的位数,所以为增加 ADC 的精度一个最直

接的方法就是增大 N,即增加 ADC 的位数。而  $\Delta \Sigma$  ADC 则采用的是另一个方法,使用一个 1 位 ADC,通过过采样,噪声滤波来提高精度。第二张图则为  $\Delta \Sigma$  ADC 的过采样,总体的噪声大小和采样没有关系,由于过采样增加了信号分布的带宽,所以平均在有效信号带宽内的噪声会明显减小。  $\Delta \Sigma$  ADC 内部的调制器会将噪声推向高频处(第三张图),噪声分布随频率不同,而总体的噪声是一定的,所以在低频处的噪声会更小,从而更加有效地提高 ADC 的精度。这时通过一个滤波器可以将带宽外的噪声滤除,提高带宽内信号的精度(第四张图)。

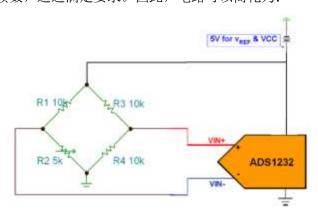

从上述分析可以看出 Delta-Sigma ADC 的几个基本特点:首先,它拥有全差分的输入级,Vin+和 Vin-都可以接受电源轨范围内的信号并进行相减,获得优秀的共模抑制能力,实际上在直流段,即使 $\triangle$ - $\Sigma$  ADC 的内部 PGA 设置为 1,其共模抑制比都可以达到 100dB 以上! 其次, $\triangle$ - $\Sigma$  ADC 拥有超高的精度,这是通过过采样、 $\triangle$ - $\Sigma$  调制和数字滤波三个方面结合起来实现的。

#### 4.2.3.2 TI $\triangle - \Sigma$ ADC

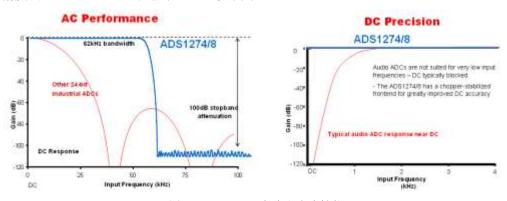

TI 拥有众多性能卓越的 $\triangle$ - $\Sigma$  型 ADC,在直流特性,带宽等方面都有显著的优势。TI $\triangle$ - $\Sigma$  ADC 主要有:高直流精度型,宽带宽型,通用型,带隔离 ADC,电流输入型以及集成有前端放大的 EEG/ECGADC。

高直流精度型主要针对专注于缓慢变化信号的直流精度的应用,例如温度,压力测量 ,负载传感以及过程控制等,宽带宽型主要针对对精度和动态范围特性同时有要求,而又允许对输入信号进行平均的应用场景,例如振动信号,音频信号,精密仪器等。通用型则适合低功耗,低成本和小板上面积的应用场景。TI 提供带隔离的  $\Delta \Sigma$  ADC,最高可提供高达 4kV 的峰值隔离。此外,针对生理信号,TI 推出专用 ADC,适合于大信号中微弱信号的提取,例如 EEG,ECG 信号。

| 器件          | 简介                                         | 封装    |

|-------------|--------------------------------------------|-------|

| ADS1232IPW  | 10SPS/80SPS, 50/60Hz 陷波器, 集成 PGA, 24 位 ADC | SS0P  |

| ADS1240E    | 15SPS, 50/60Hz 陷波器, 24位,集成 PGA, 4 通道       | SS0P  |

| ADS1246IPW  | 2ksps max, 24位,集成 PGA,单通道                  | TSS0P |

| ADS1247IPW  | 2ksps max,24位,带电流源,集成 PGA,双通道              | TSS0P |

| ADS1248IPW  | 2ksps max,24位,电流源和参考电压输出,集成PGA,<br>四通道     | TSS0P |

| ADS1252U    | 40KSPS,24 位 ADC,单通道                        | SOIC  |

| ADS1255IDBT | 30KSPS, 24 位 ADC,内部集成 PGA,双通道输入            | SS0P  |

| ADS1271IPW  | 105KSPS, 24 位 ADC, 单通道                     | TSS0P |

#### 续表

| 器件           | 简介                                         | 封装     |

|--------------|--------------------------------------------|--------|

| ADS1274IPAPT | 四通道的 ADS1271                               | HTQFP  |

| ADS1146IPW   | 2ksps max,16位,集成 PGA,单通道                   | TSS0P  |

| ADS1147IPW   | 2ksps max,16位,带电流源,集成 PGA,双通道              | TSS0P  |

| ADS1148IPW   | 2ksps max, 16 位, 电流源和参考电压输出,集成 PGA,<br>四通道 | TSS0P  |

| ADS1158IRTCT | 16 位 16 通道 125KSPS ∑-△型 ADC                | QFN    |

| ADS1174IPAPT | 16 位 4 通道 52KSPS 同步采样 Σ-△型 ADC             | HTQFP  |

| ADS1298IPAG  | 24 位 8 通道低功耗生物电位测量前端 ADC                   | TQFP   |

| LMP90077MH   | 16 位传感器前端 ADC                              | HTSS0P |

| ADS1202IPWT  | 16 位,带有分流器 ADC,40kSPS ADC                  | TSS0P  |

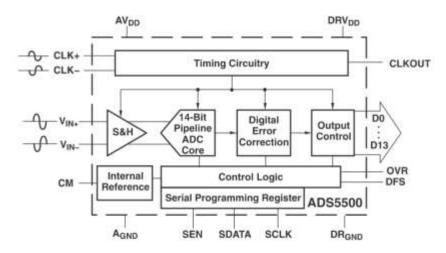

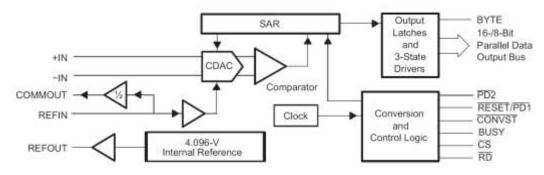

### 4.2.4 流水线型 ADC (Pipeline)

#### 4.2.4.1 流水线型 ADC (Pipeline) 结构与原理

前面分析了 SAR 和 $\triangle$ - $\Sigma$  型的 ADC,这些 ADC 由于自身结构限制,需要多个时钟周期才能产生一个数据。导致采样率较低,但是直流精度高,功耗低,在工业界应用广泛。在第一章我们就分析过采用 Flash 型的并行结构 ADC 是最快的 ADC,它在每个时钟周期都可以得到一个数据,随着模拟技术的发展,比较器的速度越来越快,Flash 型的 ADC 达到 GSPS 是轻松的事情,但是由于 n 位的 Flash 型 ADC 需要  $2^n$ 个比较器,各个比较器的直流特性,以及对时钟的响应都难以做到完美匹配,导致精度无法做高。Pipeline 型的 ADC 就是为了同时达到高速度和高精度的一个折中方案。Pipeline 是指的流水线,工厂中的流水线可以加快生产进度,同样信号处理中用到流水线也可以加快信号处理的速度。

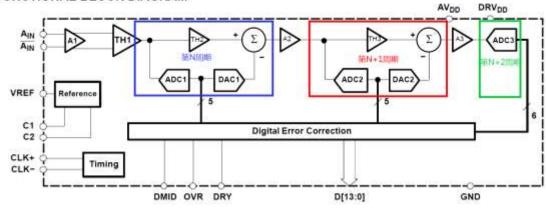

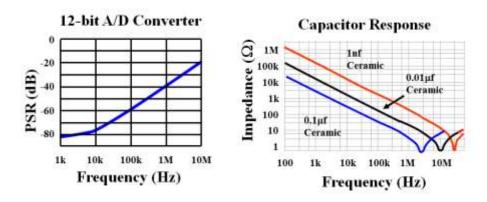

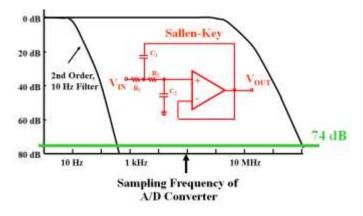

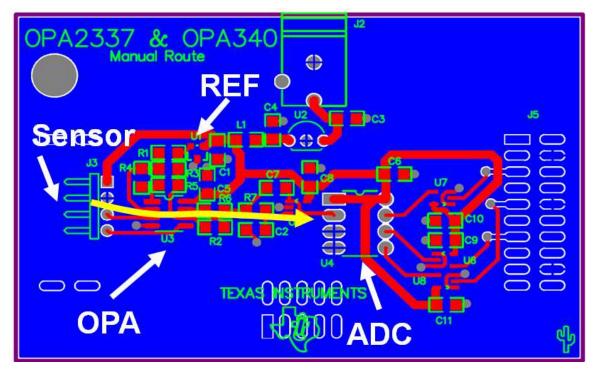

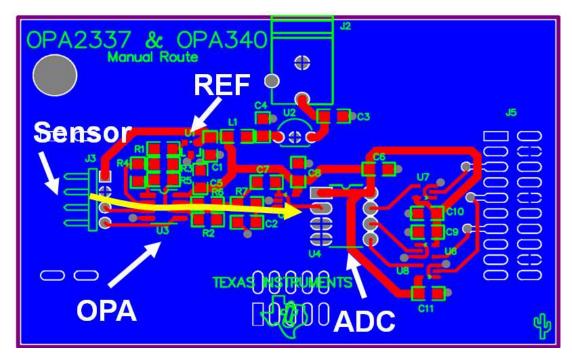

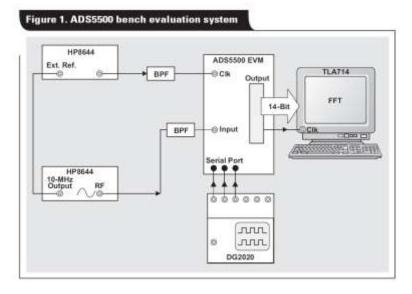

本节以 ADS5424 为例,介绍一下 pipeline 结构的 ADC。

先看一下 ADS5424 的基本性能: 采样率 105M,14bit 分辨率,信噪比 SNR=74db,无杂散动态范围 SFDR=93db,功耗 1.9W。可以看到 pipeline ADC 的功耗比 SAR 型和 $\triangle$ - $\Sigma$  型要大的多。例如 $\triangle$ - $\Sigma$  型 ADC ADS1118 的功耗在 0.5mW,SAR 型 ADC ADS8361 的功耗在 200mW。 Pipeline ADC 内部使用了多个高速 flash 型 ADC 增大了其功耗。

如下图,流水型 ADC 由若干级电路级联而成,每一级电路都包括采样/保持放大器,低分辨率的 ADC,DAC,求和电路以及可提供增益的放大器。那么,流水线型 ADC 是如何工作的呢?

#### **FUNCTIONAL BLOCK DIAGRAM**

图 4-13 ADS5424 原理框图

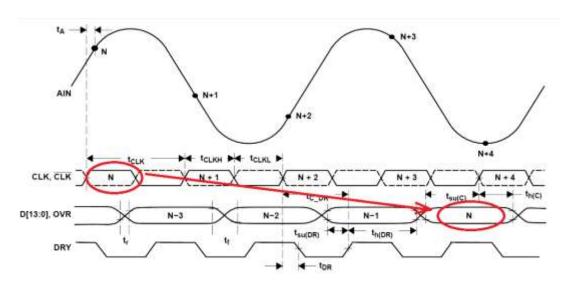

下面我们再来看看 ADS5424 内部的结构,了解 pipeline 结构 ADC 是如何实现高速采样的,这对理解其数据接口也很有帮助。

如图 4-13 所示,ADS5424 中有三级流水线,第一个时钟周期 ADC1 采样完毕并将数据给 DAC1,然后输入信号中减去 DAC1 的输出后交给第二级处理。第二个时钟周期 ADC2 采样相减后的信号并将数据给 DAC2,然后再次减去 DAC2 的输出。第 3 个时钟周期 ADC3 采样剩下的信号幅度。三个周期后即可完成采样,在第 N+3 时刻得到第 N 时刻的信号。

这个过程并不是说每次要等 3 个周期才能得到采样值,正是由于 pipeline 的特点,每一级都没有空闲时刻,例如在 N+1 周期里 ADC1 也没有空闲,它同时在处理信号以便在下个周期传递给 ADC2。用表格表示更为直观,如下表:

| clk | ADC1   | ADC2   | ADC3   | out    |

|-----|--------|--------|--------|--------|

| 1   | D(N)   | D(N+1) | D(N+2) | D(N+3) |

| 2   | D(N-1) | D(N)   | D(N+1) | D(N+2) |

| 3   | D(N-2) | D(N-1) | D(N)   | D(N+1) |

| 4   | D(N-3) | D(N-2) | D(N-1) | D(N)   |

| 5   | D(N-4) | D(N-3) | D(N-2) | D(N-1) |

| 6   | D(N-5) | D(N-4) | D(N-3) | D(N-2) |

可以看到流水线中的信号就像一行人传递水桶一样,刚开始的时候最后一个人在等待, 当每个人都有一桶水后,再往后的每个周期最后一个人都会接到一桶水。所以当流水线流动 起来后每个周期就会有一个采样点送出。流水线的方法在处理器中用的也很多,可以实现每 个时钟周期处理一条指令。

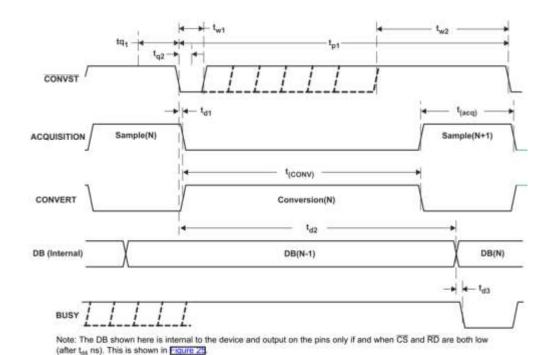

图 4-14 ADS5424 时序图

图 4-14 是 ADS5424 的时序图,通过上面的分析,可以清楚的理解其数据输出格式。由于 pipeline 结构,数据比真实采样时刻有 3 个周期的时延。

看到这里有的读者会问,为什么不将 ADC1 换成 14bit 的,一个周期就能处理完毕采样。 这就要看 ADC1 的内部结构了,ADC1 是使用的高速 flash 结构,由高速比较器和译码器组成,如图 4-15 所示:

图 4-15 ADC1 的内部结构

可以看到这个 flash 结构中需要多个精确匹配的 R 和比较器,这样才能保证 ADC 的线性。n 位的 flash ADC 就需要  $2^n$  个一样的 R 和比较器,各个电阻的阻值匹配,各个比较器的

直流特性以及对时钟的响应都难以做到完美匹配,导致精度无法做高。所以需要用多个 flash ADC 构成 pipeline 结构来实现高分辨率高速采样。

需要提到的是 pipeline 结构 ADC 中的各流水线上的 Flash 型 ADC 也无法完美匹配,其中间的拼合区间会出现非线性,如图 4-16 所示。

图 4-16 内部的各个 ADC 并不完全一致

要消除这种非线性则需要相应的处理算法,ADS5424 中集成了高速数据处理单元,用于完成这种非线性误差矫正。如下图所示。这些非线性误差直接影响 ADC 的 SNR,SFDR 等交流性能。工艺和算法的好坏决定了 ADC 的性能指标。

#### **FUNCTIONAL BLOCK DIAGRAM** DRVDD AV<sub>DD</sub> ADC1 DAC DAC VREF C1 Digital Error Correction C2 CLK+ Timing CLK-DMID OVR DRY D[13:0] GND

图 4-17 ADS5424 中的高速数据处理单元

#### 4.2.4.2 TI 流水线型 ADC

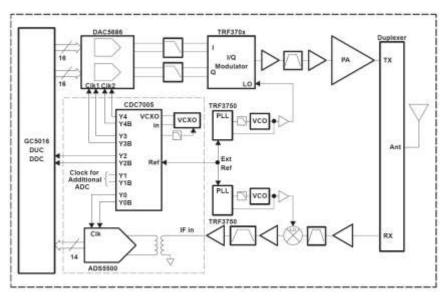

目前,流水线型 ADC 应用涵盖医疗影像采集,通信基础设施,雷达信号处理等领域,而趋势是往高速高精度发展。以通信基础设施为例,在 GSM 时代,12 位 61.44MSPS 的 ADC 就能胜任一些小型基站的需求,随着 WCDMA 等更宽带移动通信的发展和数字信号处理硬件速度的进步,对 ADC 的需求已经提高到 14 位甚至 16 位,采样率也提高到 200MSPS 以上,并且越来越倾向于向天线端靠拢。

图 4-18 TI 官网中的 pipeline 型 ADC

进入 TI 官网 www.ti.com 在产品目录中 high speed ADC 中可以看到数量众多的 pipeline 高速 ADC。这些 ADC 有着不同的分辨率和采样率和输入范围,通道数等,但是他们都有 pipeline 结构的基本特点。TI 拥有非常广的流水线型 ADC 家族,目前 TI 推出了 16 位 200MSPS 的产品和 12 位 500MSPS 的单片 ADC 产品,这都是产业界最高水平的器件。不过由于受美国商务部出口限制政策的约束,我们向大学只提供不需申请许可证的器件。

| 器件            | 简介                                   | 封装   |

|---------------|--------------------------------------|------|

| ADS62C15IRGCT | 双路 11 位 125MSPS,SNR@Boost = 77.5dBFS | VQFN |

| ADS62C17IRGCT | 双路 11 位 200MSPS,SNR@Boost = 79.8dBFS | VQFN |

| ADS62P15IRGCT | 双路 11 位 125MSPS,CMOS or DDR LVDS 输出  | VQFN |

| ADS5517IRGZT  | 双路 11 位 200MSPS,CMOS or DDR LVDS 输出  | VQFN |

| ADS6124IRHBT  | 12 位 105MSPS,CMOS or DDR LVDS 输出     | QFN  |

| ADS62P24IRGCT | 双路 12 位 105MSPS,CMOS or DDR LVDS 输出  | VQFN |

| ADS6123IRHBT  | 12 位 80MSPS,CMOS or DDR LVDS 输出      | QFN  |

| ADS62P23IRGCT | 双路 12 位 80MSPS,CMOS or DDR LVDS 输出   | VQFN |

| ADS6122IRHBT  | 12 位 65MSPS,CMOS or DDR LVDS 输出      | QFN  |

| ADS62P22IRGCT | 双路 12 位 65MSPS,CMOS or DDR LVDS 输出   | VQFN |

## 4.2.5 应用场景总结

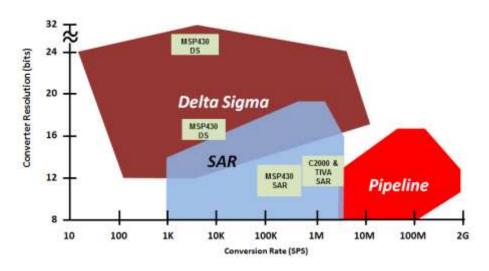

从前文对几种 ADC 的结构和特点分析,我们不难发现 这几种 ADC 在采样速度以及分辨率上各有优势,如图 4-19 所示。其中  $\Delta \Sigma$ 型 ADC 由于采用过采样、噪声整形和数字滤波来满足高精度,其有效采样速度受到限制,而分辨率相对则比较高; Pipeline 型 ADC 与之相反,其采样速度可以高达 2GSPS,而采样的精度则受到了限制;逐次逼近型 ADC,即 SAR 型 ADC 处于两者中间,具有高精度,低功耗的特点,其采样率一般最高可达 2-5MSPS。

图 4-19 Δ Σ ADC, SAR 型 ADC 以及 Pineline 型 ADC 采样速度和分辨率对比

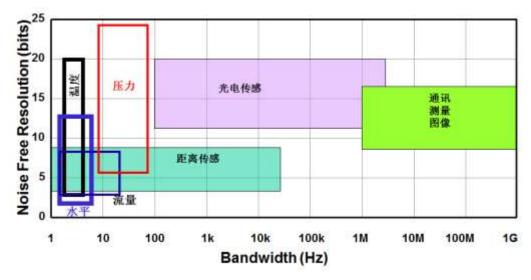

同样,不同的信号在带宽和精度上有不同的要求,如图 4-20 所示,可以看到不同的信号对带宽和精度有着不同的需求。结合以上两点,不同类型的 ADC 有着不同的应用场景。

图 4-20 不同信号的特点

根据不同 ADC 性能的特点,这三种 ADC 在应用场景上也会各有侧重。

| 应用场景           | 传感器信号                   | 医疗                        | 检测与测量                   | 音頻                          | 通信,图像                    |

|----------------|-------------------------|---------------------------|-------------------------|-----------------------------|--------------------------|

| 信号分类           | 温度,湿度,压<br>力,电压,电流<br>等 | 生理电信号                     | 工业探伤,颤<br>动检测,电机<br>控制等 | 交流信号                        | 宽带,高速                    |

| 信号特点           | 小信号,变化<br>慢,DC 为主       | Hz 级微弱信<br>号的提取,宽<br>动态范围 | 瞬时采样,DC-<br>KHz 信号      | 20-20KHz,宽<br>动态范围,低失<br>真度 | MHz 信号,大<br>带宽,宽动态<br>范围 |

| SAR 型 ADC      | +++                     | +                         | +++                     | +                           | -                        |

| Δ Σ型 ADC       | +++                     | +++                       | _                       | +++                         | -                        |

| Pinpline 型 ADC |                         |                           |                         |                             | +++                      |

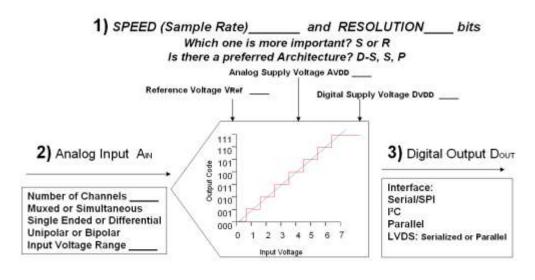

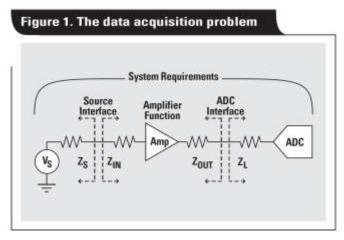

## 4.3 为您的设计选择合适的 ADC

在工业 PLC 系统里,我们绝大多数时候都与 SAR 型和 Delta-Sigma 型 ADC 打交道,他们的超高的直流精度、中等的采样率以及低功耗都符合我们的要求。在了解到 ADC 的基本分类之后,在实际设计中,我们如何来进行 ADC 的选型呢?在挑选 ADC 的时候,我们可以通过下面的 check list 来判断:

图 4-21 ADC 选型流程表

图 4-21 给出了我们在进行 ADC 设计时需要依次考虑的几个问题:

## 4.3.1 确定 ADC 类型

首先,根据需要采集信号的基本特点以及各类 ADC 的特点大致决定所需 ADC 的类型。参考下表,大致给出了三类 ADC 在不同方面的优势:

| 特性                    | SAR | ΔΣ  | Pipelined |

|-----------------------|-----|-----|-----------|

| 吞吐率                   | ++  | ++  | +++       |

| 分辨率                   | ++  | +++ | +         |

| 延迟                    | +++ | _   | +         |

| 非周期性多通道信号采<br>集(多路复用) | +++ | _   | _         |

| 功耗                    | 低   | 低   | 高         |

### 4.3.2 确定所需 ADC 的采样率,精度

#### 4.3.2.1 采样率

在大致确定选择 ADC 类型后,进一步根据感兴趣信号的频率和带宽确定所需的采样方式 (过采样还是欠采样?),从而确定 AD 转换所需的采样率。精密信号链中,通常采用过采样 的方式(通常远大于 2 倍信号频率)来确保时域的精确度,降低带内噪声,前端滤波器通常 采用低通滤波器;针对高中频的带通信号,我们通常采用欠采样的方式(采样率低于中频频 率,但是远大于信号带宽),把带通信号搬移到低频段进行处理,ADC 前端采用单通滤波器。

### 4.3.2.2 确定所需精度

ADC 的精度分为两种情况,高精度采样中关注信号的时域特性,比如在针对直流信号的采样中需要确保 ADC 的最小分辨率(LSB)和满量程输入范围要满足设计要求,同时要确保整个系统的噪声小于这个 LSB/2,这些噪声包括了驱动运放的噪声,PCB 布局布线中引来的噪声;例如,一个体重秤中的压力传感器在 0-200Kg 的输入压力下可以输出 20mV 的电压信号,为了满足体重秤精确到 100g 的要求(即提供 200Kg/100g = 2000 个读数),需要模拟处理电路和 ADC 在 20mV 的满量程输出电压信号中能划分出 2000 个区间,此时如果不将信号放大,我们需要的 ADC 的最小分辨率(LSB)为 20mV/2000 = 10uV,根据 ADC 最小分辨率的计算公式 LSB=FS/2°,如果选用的 ADC 满量程输入范围 FS 为 4.096V,那么可以反推出 n 应该取大于 18.65;如果我们将信号放大 100 倍,则所需的 ADC 的最小分辨率为 2V/2000 = 1mV,同样如果 ADC 的满量程输入范围 FS 为 4.096V,我们只需一颗 12 位的 ADC 就可以满足要求。

而高速应用中关注的是 ADC 的频域特性,即 ADC 的可重复性,这主要包括了 ADC 的频域指标 SINAD 和 SFDR。

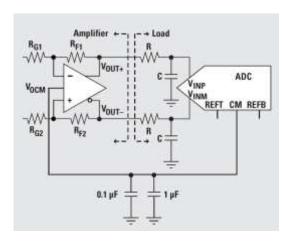

## 4.3.3 选择并设计 ADC 的模拟输入

接下来,需要看 ADC 模拟输入端的输入信号。在 ADC 的模拟输入端,我们需要考虑的问题有:

- ADC 的模拟输入端是单端输入, 伪差分输入还是差分输入?

- 信号的通道数,是否需要多通道同步采样,还是采用复用输入?

- 信号的极性和 ADC 输入的极性:

- 信号的大小和 ADC 满量程输入的范围等。

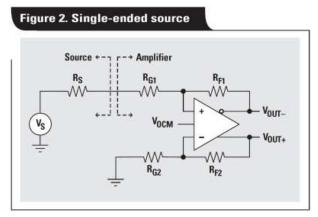

#### 4.3.3.1 单端, 伪差分和差分输入

单端输入即信号只有一个输入端口,很好理解。那么什么是伪差分和差分输入呢?

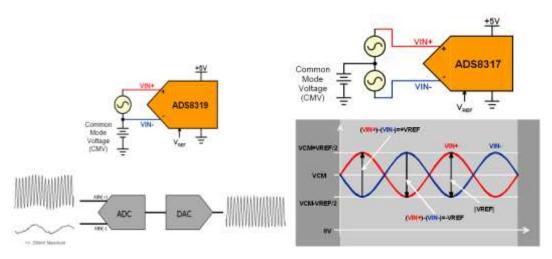

图 4-22 伪差分输入(左)和差分输入(右)

如图 4-22 左所示为伪差分输入,其实质上还是是单端输入,因为 VIN-上的信号并不被采样,保持和转换,而是做为共模抑制端用来消除 VIN+和地平面上的共模噪声,因此 VIN-上的电压输入范围一般在-0.2V 到+0.2V(即伪差分输入的共模输入范围是-0.2V 到+0.2V)。这是一个 VIN+上耦合的地平面噪声信号被伪差分输入抑制的例子。而右图所示为全差分输入,即差分输入级则拥有完整的共模抑制能力, VIN-和 VIN+拥有同样的输入信号范围。差分输入的 ADC 的满量程输入(VIN+-VIN-)一般是+VREF 到-VREF,因此 VIN-和 VIN+的输入通常要求含有 VREF 的直流偏置,以 VREF 为中心上下摆动(或 VIN-接入虚地)。因此差分输入的 $\Sigma-\Delta$  ADC 可以直接联接电桥输出,节省仪表放大器,并利用其高分辨率节省主放大器。而差分输入的高精度(16 位)SAR ADC 拥有非常卓越的动态特性,因为差分信号天生拥有共模噪声抑制特性,可抑制偶次谐波,并在相同满量程输入的条件减小差分对上的信号摆幅,从而减少失真。

16 位以下的 SAR 型 ADC 基本都采用伪差分输入,16 位以上的 SAR 型 ADC 和 Delta-Sigma ADC 都提供完整的差分输入级,从而提供极高的共模抑制能力。

### 4.3.3.2 多通道采样: 同步还是复用?

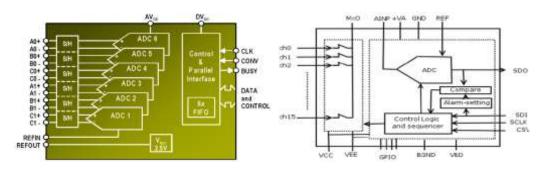

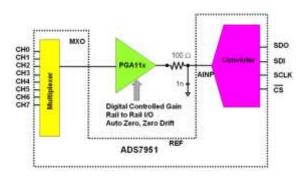

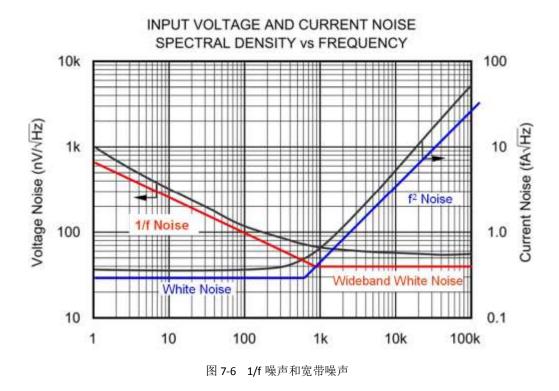

多通道采样分为同步采样和复用采样,在对各个输入通道的信号相位有严格同步要求时(比如三相交流电的电流和电压信号,其相位关系提供了瞬时功率、功率因数等信息),我们需要使用多个 ADC 在同一时刻采样,为简化用户设计,TI 提供一个封装中包含多个 ADC 内核的多通道同步采样产品,如图 4-23 左所示为 ADS8361 的内部示意图,它在三相电采样中得到广泛应用。在工业应用场合中,多数情况下各个通道的模拟信号间是没有相位关系的,比如温度,湿度,压力信号,他们无需用同步采样来保持相位信息,这时采用多路复用器配合一个的单通道 ADC 就可以满足多通道采样的需求,如图 4-23 右边所示为 ADS7950 的示意图,与前者不同的是,其多路复用器的输出和 ADC 的输入没有在芯片内部相连,这样可以在片外加入一个 PGA11x,简化模拟前端因为各个通道需要不同放大倍数带来的多个放大器。采用多路复用器和单 ADC 构建的多通道采样系统,应注意各个通道的建立时间和分配到各通道的采样速率是否足够,若使用 Delta-Sigma ADC,通道的切换与采样周期同步非常重要,否则会引起数字滤波器的建立错误。

图 4-23 ADS8361 的 6 通道同步采样(左)和 ADS795x 系列的多通道复用采样(右)

图 4-24 ADS7951 和外部放大器 (PGA11x) 构成各通道增益可调采样电路

## 4.3.3.3 输入信号极性及大小

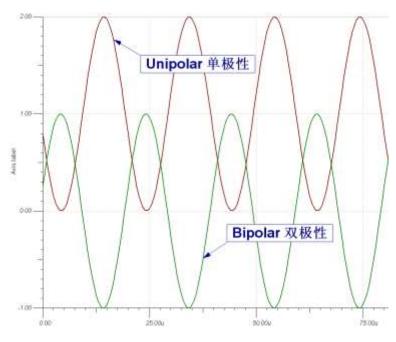

a. 输入信号的极性:

图 4-25 单极信号及双极信号

如图 4-25 所示,所谓单极性信号是指信号幅度范围均在 0V 以上,对应的单极性输入的 ADC 只能接受 0V 以上的信号输入,对于 0V 以下的信号则被忽略。大多数的 ADC 都是单极性输入的,TI 推出的少数一些可以对双极性信号进行直接采样的 ADC,如 ADS850x 系列,但是价格较高。因此在大多数场合下,我们需要对同时含有正负信号的双极性信号进行一些电平抬升等处理才能被单极性输入的 ADC 所接受。

## b. 信号的大小:

除了信号的极性,我们还应小心控制输入给 ADC 的信号幅度不超过 ADC 的满量程范围。通常,留出一定的净空是很好的设计习惯,虽然这样会损失一些动态范围,但是对控制运放的输出级失真和 ADC 输入级饱和/失真都有很好的帮助。

在某些情况下输入信号幅度超过 ADC 满量程,这时需要在送入 ADC 前对输入信号预先进行调理。例如,我们需要使用 4.096V 满量程输入的 ADC 来采集—10V 到+10V 的输入信号,我们需要使用下面的电路进行信号调理。如图 4-26 所示,峰峰值为 20V 的输入信号通过前级电路的调理,其输出信号为 0V 以上,即单极性信号,同时期幅度范围也调整为 ADC 满量程之内。从这个例子我们可以看出,对于输入信号的必要调理在 ADC 电路设计中也是非常重要的。

图 4-26 输入信号调整为 ADC 量程留出富余的净空

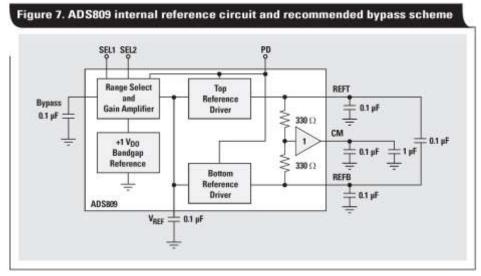

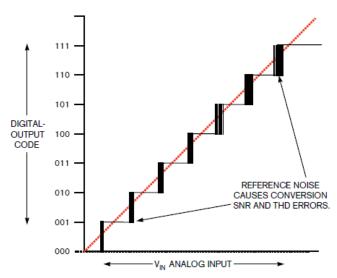

## 4.3.4 选择并设计 ADC 的参考输入

ADC 电路中的参考电压在整个数据转换中扮演着非常重要的位置,

$$V_{\text{out}} = \frac{N}{2^n} V_{\text{ref}}$$

上面的公式是在 AD 转换中非常重要的一个公式,我们知道 A/D 转换之后的结果是一个数字量,那这个数字量如何和实际的输入电平连接起来呢?参考电压,即  $V_{ref}$  就扮演着这样一个桥梁的作用。从这个公式中我们可以清晰地看出  $V_{ref}$  的准确程度,即参考电压电路提供的参考电压的精度一定程度上影响了 A/D 转换的精度。

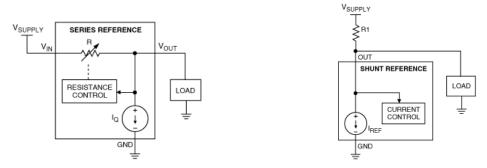

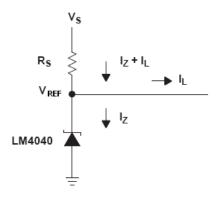

电压基准实际上是非常有用的电路,在 ADC 和 DAC 电路中,它为输入(或输出)模拟电压提供一个恒定参考,从而决定输出(或输入)数字信号的大小;在电源电路里,它给输出电压提供一个参考,结合负反馈电路使得输出恒定;在电压检测和比较电路中,它提供一个门限电压。电压基准分为串联型和并联型两种;

图 4-27 两种电压基准: (左) 串联型电压基准(右) 并联型电压基准

#### 1. 串联型

串联型电压基准具有三个端子:  $V_{IN}$ 、 $V_{OUT}$ 和 GND,类似于线性稳压器,但其输出电流较低,同时具有非常高的精度和非常低的温漂。串联型电压基准从结构上看与负载串联,可以当作一个位于  $V_{IN}$ 和  $V_{OUT}$ 端之间的压控电阻。其特点有:

- 类似于线性稳压器,输入电压和稳压输出必须有一个最低的压差;因此串联电压基准 会消耗功率,其最大功率出现在输入电压最高,同时负载最重的时候(压差最大,电流最 大);

- 输入电压过高时会损坏器件。 串联型电压基准输入电压通常范围不够宽:

- 空载时, 唯一的功耗是电压基准的静态电流;

- 相对于并联型电压基准,串联型电压基准通常具有更好的初始误差和温度系数,如果需要高于 0.1%的初始精度和 25ppm 的温度系数,一般应该选择串联型电压基准。

#### 2. 并联型

并联型电压基准有两个端子: OUT和GND。它在原理上和稳压二极管很相似,但具有更好的稳压特性。类似于稳压二极管,它需要外部电阻,与负载并联工作。并联型电压基准可以当作一个连接在OUT和GND之间的压控电流源,通过调整内部电流,使电源电压与电阻R1的压降之差(等于OUT端的基准电压)保持稳定。换一种说法,并联型电压基准通过使负载电流与流过电压基准的电流之和保持不变,来维持OUT端电压的恒定。并联型基准具有以下特点:

- 选择适当的 R1 保证符合功率要求,并联型电压基准对最高电源电压没有限制。在输入电压高于 40V 时,并联型电压基准可能是唯一的选择。

- 电源提供的最大电流与负载无关,流经负载和基准的电源电流需在电阻 R1 上产生适当的压降,以保持 0UT 电压恒定。

- 简单的 2 端器件,并联型电压基准可配置成一些新颖的电路,例如负电压稳压器、浮地稳压器、削波电路以及限幅电路。

以上为两种类型电压基准的介绍,下面将就这两种电压基准电路的功耗进行比较。

串联型电压基准需要一定的静态电流来保证空载时输出恒定,而串联型电压基准的静态电流通常在 100uA 到 1mA,性能越好,静态功耗越大。因此串联型电压基准工作时的功耗包括(静态电流+负载电流)×压降。所以串联电压基准的功耗是动态的,当负载重时,功耗大,负载轻时,功耗小。ADC 的参考电压的电流需求就是如此,当采样转换时,参考电压的电流需求大(如 1mA),空闲时,电流需求小(如 1uA)。

并联型电压基准外部需要加 RS 才能正常工作,因此考虑功耗时要将 RS 上的功耗一同考虑进去,如图 4-28 所示,整个电压基准电路的总功耗=(VS-VREF)<sup>2</sup>/RS+VREF×IZ。RS 值的确定非常重要:

图 4-28 电压基准电路示意图

RS 的作用是限定并联电压基准和负载的总电流,即: IL+IZ=(VS-VREF)/RS,选择 RS 的值时我们通常考虑两个极端: 一是最大的 VS 和最小的 IL,为防止 IZ 超过并联电压基准的最大允许电流(如 15mA),我们要保证 RS 足够大: RS  $\gt=(VSmax-VREF)/(ILmin+IZmax)$ ;二是最小的 VS 和最大的 IL,为保证 IZ 大于并联电压基准导通时所需的最小电流,我们要保证 RS 足够的小: RS  $\lt=(VSmin-VREF)/(ILmax+IZmin)$ 。由于选择的 RS 越大,整个电压基准电路的功耗越小,因此我们常取 RS =(VSmin-VREF)/(ILmax+IZmin),当然,别忘记留一点余量。

RS 确定后,并联电压基准和负载的总电流也确定了。这样,并联电压基准自身的功耗和负载成反比,负载重时,IL 大,电压基准上的电流 IZ 小,功耗小;空载时,IL=0,电压基准上的电流 IZ 最大,功耗最大。所以在宽电源电压变化范围或大动态负载条件下,并联型的耗散功率可能大大高于具有相同性能的串联型电压基准。比如驱动 ADC 的参考电压输入时,即使 ADC 空闲 IL 非常小,由于 IZ 此时最大,加上 RS 确定后其上不变的功耗,整个并联基准电路的功耗仍然很大,和空闲时动态功耗变化的串联型电压基准相比会大出很多。精密电流源在提供电流参考,测量电阻,激励 RTD 传感器方面也有着广泛的应用。

#### 推荐使用的 TI 电压基准和电流基准有:

| 器件             | 简介                                                      | 封装          |

|----------------|---------------------------------------------------------|-------------|

| REF3212AIDBVT  | 1.25V,4 ppm/°C,初始精度 0.2%,Series (Bandgap)<br>Reference  | SOT23       |

| REF3220AIDBVT  | 2.048V,4 ppm/°C,初始精度 0.2%,Series (Bandgap)<br>Reference | SOT23       |

| REF3225AIDBVT  | .2.5V,4 ppm/°C,初始精度 0.2%,Series (Bandgap)<br>Reference  | SOT23       |

| REF3230AIDBVT  | 3.0V,4 ppm/°C,初始精度 0.2%, Series (Bandgap)<br>Reference  | SOT23       |

| REF3233AIDBVT  | 3.3V,4 ppm/°C,初始精度 0.2%, Series (Bandgap)<br>Reference  | SOT23       |

| REF3240AIDBVT  | 4.096V,4 ppm/°C,初始精度 0.2%,Series (Bandgap)<br>Reference | SOT23       |

| REF5050AID     | 5V,3 ppm/°C,初始精度 0.1%,Series (Bandgap) Reference        | SOIC        |

| LM4040A10IDBZT | 10V,初始精度 0.1%, 100 ppm/°C, 并联型(Shunt Reference)         | SOT23       |

| LM4040A82IDBZT | 8.192V,初始精度 0.1%, 100 ppm/°C, 并联型(Shunt<br>Reference)   | SOT23       |

| LM4040A50IDBZT | 5V,初始精度 0.1%, 100 ppm/°C, 并联型(Shunt Reference)          | SOT23       |

| LM4040A41IDBZT | 4.096V,初始精度 0.1%, 100 ppm/°C, 并联型(Shunt<br>Reference)   | SOT23       |

| LM4040A30IDBZT | 3V,初始精度 0.1%, 100 ppm/°C, 并联型(Shunt Reference)          | SOT23       |

| LM4040A25IDBZT | 2.5V,初始精度 0.1%, 100 ppm/°C, 并联型(Shunt Reference)        | SOT23       |

| LM4040A20IDBZT | 2.048V,初始精度 0.1%, 100 ppm/°C, 并联型(Shunt<br>Reference)   | SOT23       |

| TLVH431BILP    | 1.24-18V,可调并联型电压基准,0.5%初始精度                             | TO-92<br>直插 |

| TL431BILP      | 2.495−36V,可调并联型电压基准,0.5%初始精度,34<br>ppm/°C               | TO-92<br>直插 |

| REF200AU       | 双路 50uA/100uA/200uA/400uA,精密电流源(Souce/Sink)             | SOIC        |

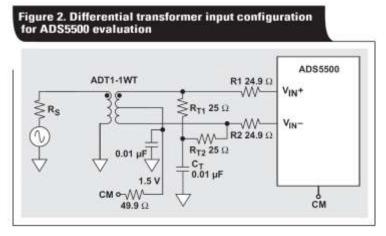

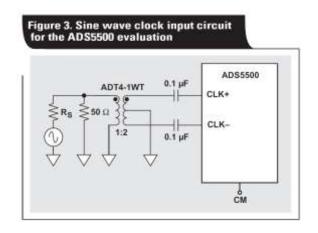

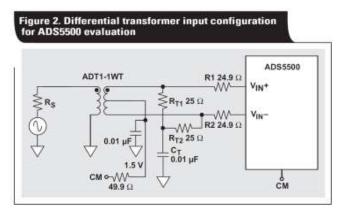

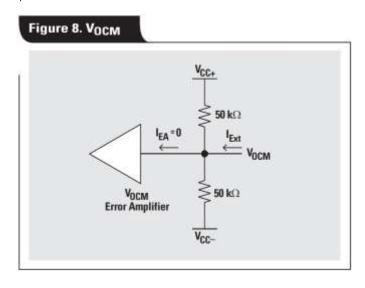

### 4.3.5 选择并设计高速数据采集系统中的时钟

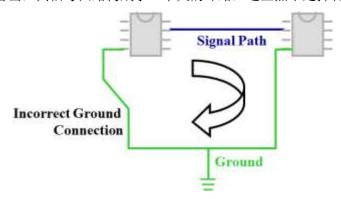

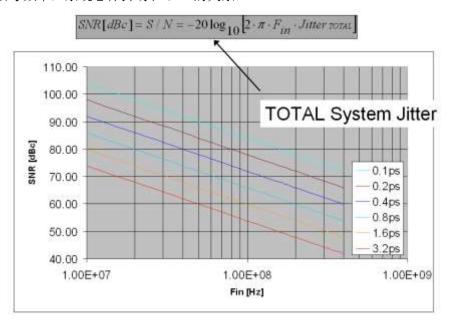

对于高速数据采集系统,我们还需要特别关注时钟。高速 ADC 的动态特性的最大瓶颈在于采样抖动(jitter),包括采样保持电路的孔径抖动(来自于 ADC 自身)和采样时钟的抖动(来自于采样时钟电路),这也是现代流水线型 12-14 位 ADC 的 ENOB 很难突破 12 位的主要原因(TI 新推出的 16 位 100MSPS+的数据转换器的 ENOB 可以接近 13 位)。

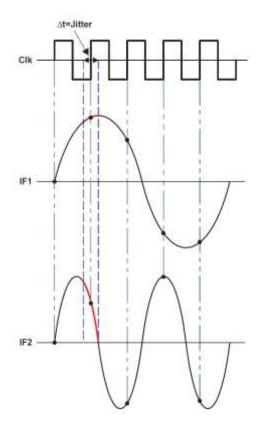

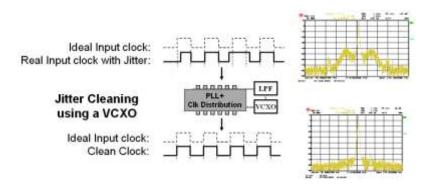

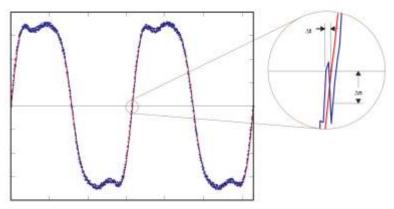

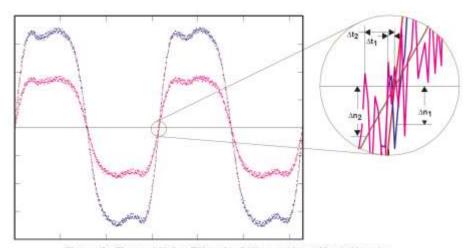

那么什么是抖动?抖动就是由于采样时刻的不确定性带来的采样误差,如图 4-29 所示,在每个时钟周期的采样时刻的不确定性,导致数字化后幅度的不确定性,这种不确定性导致 ADC 采样的可重复性大大降低,而可重复性就决定了 ADC 的频域性能。由此可见频域性能受 Jitter 的影响非常大。

图 4-29 时钟带来的采样周期不确定性

在实际进行 ADC 选型时,我们可以在数据手册中找到关于抖动的描述:

|                | PARAMETER                     | TEST CONDITIONS                               | MIN TYP MA | X UNIT |

|----------------|-------------------------------|-----------------------------------------------|------------|--------|

| SWIT           | CHING SPECIFICATION           |                                               |            |        |

| t <sub>A</sub> | Aperture delay                | Input CLK falling edge to data sampling point | 1          | ns     |

|                | Aperture jitter (uncertainty) | Uncertainty in sampling instant               | 300        | fs     |

ADC Internal S/H Circuit Jitter

图 4-30 数据手册中关于抖动的描述

如图 4-30 所示,可以看到该款 ADC(ADS5500)的内部采样抖动(jitter)为 300fs,已经非常地小了。当然这里我们看到的数据时芯片的参数,半导体厂商 TI 会在芯片级去尽量减小它(实际上,ADS5500 是 2004 年的产品,现在最新的 14 位 125MSPS 的 ADS6145 已经将这个数值减小到 150fs,从而获得了更加卓越的 SNR 和 SFDR)。同时,对于高速数据采集系统中时钟的考虑,我们更多能干预的是外部采样时钟的抖动性能。此外时钟幅度和时钟同步也是同样需要考虑的因素,这几点在后面电路优化的章节中会做详细的描述。

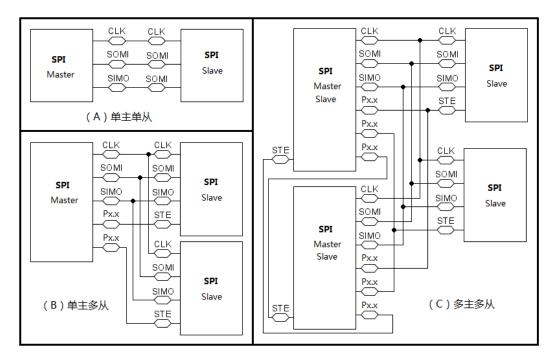

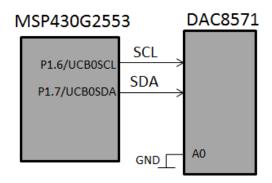

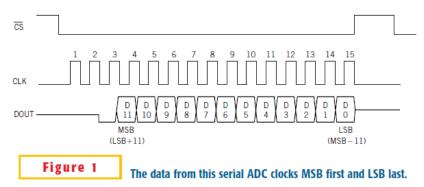

## 4.3.6 ADC 的数据输出捕获

最后,我们来看 ADC 的输出。从前面的描述,我们知道 ADC 是将模拟信号转换为数字信号,那这些数字信号与后续处理设备,如 MSP430 单片机之间是如何实现数据通讯的呢?现代的高精度 ADC 多数采用 SPI 串行输出格式,一些更低采样率的 Delta-Sigma 型 ADC 甚至采用更慢的 I2C 格式输出转换数据。当采样速率超过 2MSPS 后,所需的串行输出时钟太高,对 ADC 和接受端都是极大的挑战,这时才逐渐开始使用并行输出。因此,充分理解 SPI 和 I2C 的时序,理解 ADC 的采样和转换时序是非常重要的。

#### 4.3.6.1 SPI 接口 ADC

#### SPI 数据接口

SPI(Serial Peripheral Interface)串行外设接口的简称,它是一种同步全双工通信协议。 有 3 根或者 4 根数据线组成,包括 CLK、SOMI、SIMO、STE:

CLK 为时钟线,由主机控制输出。

SOMI 是 Slave output Master input 的缩写,如果设备被设定为主机,那么这就是输入口。如果设备被设定为从机,这个口就是输出口。这与 UART 的 Tx 和 Rx 方向恒定相区别。

SIMO 是 Slave input Master Output 的缩写,同样由配置为主或从模式决定是输入还是输出口。也就是器件内部是有读写切换开关的。

STE 是 Slave Transmit Enable 的缩写,在不同器件中也经常被写作片选 CS(Chip Select)和从机选择 SS(Slave Select),都是一个意思。

#### SPI 的通信模式

如图 4-31 所示, SPI 的通信模式分为单主单从、单主多从、多主多从三类。A 为三线制 SPI 通信; B 为四线制单主多从 SPI 通信; C 为四线制多主多从 SPI 通信。

三线和四线的区别是多出了一个被控制的 STE 信号,以使能从机。对于多主机通信,主机的 STE 也被控制,以决定是否为从机模式。无论主机从机的 STE 最终都是由额外的 IO 口来控制的。

图 4-31 SPI 通信的各种连接

从图 4-31 可以看出, SPI 通信要实现多机通信是以多占用 IO 来实现的。所以,用途最多的是 3 线 SPI 或者 1 主多从的四线制 SPI,而多主多从的 SPI 极少使用。

#### SPI 协议时序

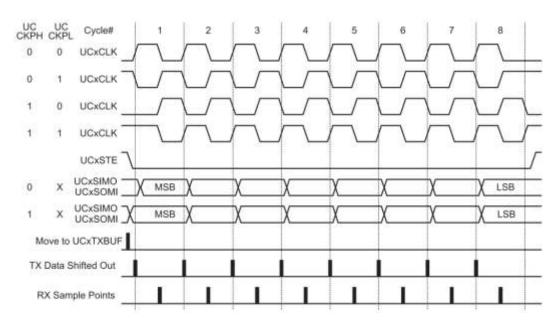

图 4-32 是 SPI 通信的时序图, 其中有两个控制位需要讲解一下:

- 1) CKPH 是 CLK 相位控制位, CKPL 是 CLK 极性控制位。

- 2) 两个位如何设置对通信协议没本质影响,只是用来约定在 CLK 的空闲状态和什么位置 开始采样信号。

- 3) CKPH=0, 意味着在以 CLK 第一个边沿开始采样信号, 反之则在第二个边沿开始。

- 4) CKPL=0 意味着时钟总线低电平位空闲, 反之则是时钟总线高电平空闲。

在标准 SPI 协议中,先发送的是 MSB 位,在 4 线制模式下,片选信号(STE/CS/SS)控制 传输的开始。在 3 线制模式中,则是从机始终激活,依靠时钟来判断数据传输开始。

图 4-32 SPI 通信协议时序图

图 4-33 数据流表达方式

#### SPI 型 ADC 数据输出

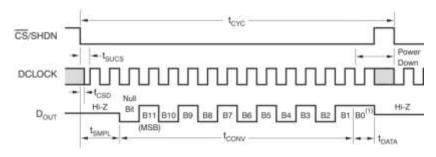

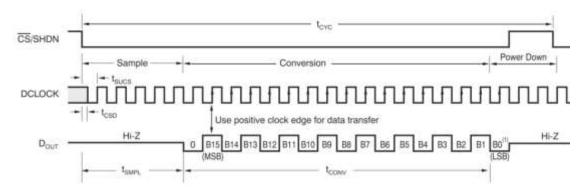

ADS7950 是一款最高采样率 1MHz,具有串行接口的 SAR 型 ADC。由于其低功耗的特点,常用在电池供电系统中,此外也常用在医疗仪器,触摸屏控制,高速信号采集系统等中。在数字接口方面,ADS7950 通过 $\overline{CS}$ 和 SCLK 和微处理器或 DSP 进行串行通讯。

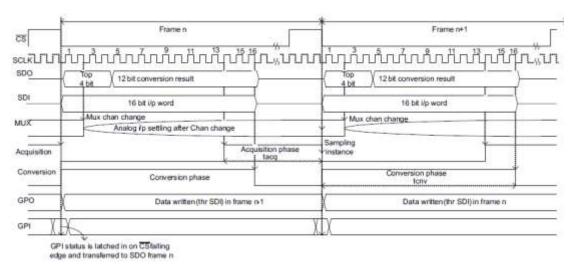

$\overline{CS}$ 信号作为 SPI 通讯的激活信号,只有当该引脚信号被拉低后,通信才会开始,当 $\overline{CS}$ 为高电平时,信号输出引脚表现为高阻状态,此时,通过串口进行的读写操作都会被忽略。 SCLK 为串口通讯提供了时钟信号,SCLK 的上升沿和下降沿改变分别对应数据的输出和输入。

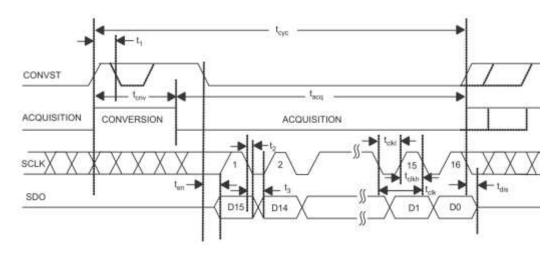

图 4-34 ADS7950 串行通讯时序图

如图 4-34 所示为 ADS7950 进行数据传输时的时序图: 首先 CS拉低意味着 SPI 通讯的激活和开始,在经过一个固定的配置时间(tCSSC)之后,时钟信号 SCLK 第一个上升沿之后为传输的第一个数据,高位优先。如果是进行 AD 转换数据的传输,在 16 个时钟周期内,AD 采样的 16 个数据将被顺序通过 DOUT 引脚传输。

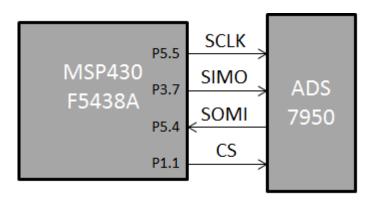

SPI 接口的 ADC 在使用时时序相对比较简单,也容易理解。配合集成有 SPI 模块的控制器,例如 MSP430,用户可以方便地实现 ADC 的控制和数据的读取。如图 4-35 所示,为 MSP430F5438A 与 ADS7950 的连接示意图,采用 3 线 SPI,其中 P1.1 作为片选信号线与 ADS7950 相连。MSP430F5438A 内部集成有多个 SPI 模块,这里选择 UCB1。

图 4-35 MSP430F5438A 与 ADS7950 接口示意图

在配置相应的 IO 口之后,对 SPI 模块进行初始化配置,参考(SPI\_Init 函数)。在这里给出一个读取 ADC 输出数据的示例:首先软件拉低片选信号,由主机,即 MSP430 向 ADS7950 发送一个读数指令,同时完成 ADS7950 处采样得到的数据的读取,完成之后再将片选信号拉低。至此,完成一次完整的采样数据读取和保存。

```

void SPI Init(void)

{

UCB1CTL1 |= UCSWRST;

// 复位操作

UCB1CTL0 |= UCMST+UCSYNC+UCCKPH+UCMSB; // 选择430为3线8位SPI主机

// 时钟上升沿有效, MSB

// 选择系统时钟

UCB1CTL1 |= UCSSEL 2;

UCB1BR0 = 0x04;

UCB1BR1 = 0;

UCB1CTL1 &= ~UCSWRST;

// 初始化USCI

delay cycles(100);

// 等待从机初始化

}

void ADS_Test(unsigned int Data[])

//数据发送和接收

// CS置低电平

P10UT &=~ 0x02;

ModeControlReg Init = 0x1980;

// 发送工作模式请求

// 通道3, 工作电压2.5V

Data[0] = WriteSPI(ModeControlReg Init); // 向 ADS7950写数据

P10UT |= 0x02;

// CS置高

```

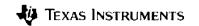

利用示波器观察相应引脚的时序,图 4-36 所示为观测到的时钟和发送信号线上的信号。因为 MSP430 的 SPI 模块数据发送以一个字节,即 8bit 为单位,所以在一次 ADC 读数周期中需由两次 SPI 发送和读取组成。从第二组波形,即 ADC 返回的采样值可以读出 AD 转换的数据。根据 ADS7950 的数据手册,前四位为 AD 的通道数,我们程序选择读取第三通道,所以我们读到的返回值前四位为通道数信息,后面的 12 位为实际采样的数据。同时从 MSP430 发

送数据的波形,即第三通道,可以清晰得出发送的数据: 0x19 和 0x80,即 00011001 10000000。

图 4-36 数据读取时的时钟信号(通道 1), ADC 发送的数据波形(通道 2)

以及 MSP430 发送的数据波形 (通道 3)

#### 4.3.6.2 I2C 接口 ADC

#### I2C 原理

SPI 的特点就是简单,速度快,从原理上最不需要动脑子。但是由于 SPI 所用数据线实在太多,多一个从机就得多一条线,而且多主机实现起来也要加线。于是 I2C (Inter-Integrated Circuit) 这个只用两根线,几乎无限主从机的协议诞生了。

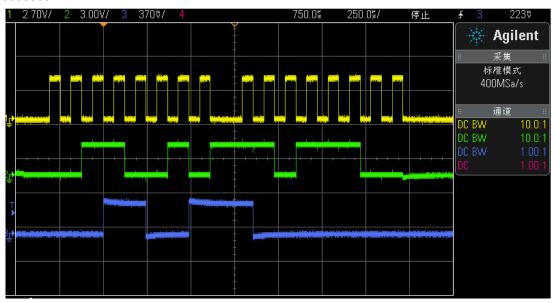

I2C 是"线与"输出的标志性电路,将"线与"的优点完整展现出来。如图 4-37 所示的 I2C 总线硬件连接中,一共有两条总线,串行时钟线和串行数据线。两条总线都被上拉电阻 拉到 VCC,所有 I2C 设备都挂载在总线上,各设备的地位对等,都可作为主机或从机。从分配地址来看,最多挂载设备可有 1024 个,实际挂载设备数量受总线电容限制。

线与逻辑的规则是,每个设备都可以把总线接到地拉低,却不许把总线电平直连 VCC 而置高。把总线电平拉低称为占用总线,总线电平为高等待被拉低则称为总线被释放。利用线与结构,I2C 制定了"神乎其技"的协议规范,仅用 2 根线就完成任意多主多从双向通信中的所有难题。

图 4-37 I2C 总线硬件连接

#### I2C 协议的基本规范

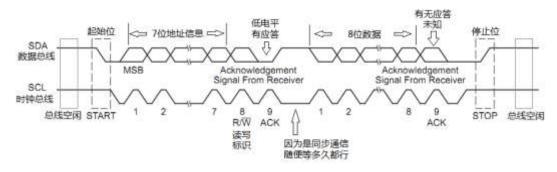

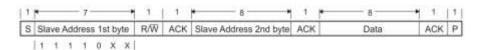

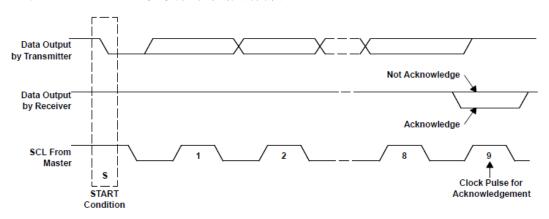

如图 4-38 所示, I2C 协议的完整帧包括起始位、地址位、读写位、应答位、数据位、应答位...数据位、应答位、停止位。

- 1) 从起始位到停止位之间所有的数据都是主机与符合地址位的从机之间进行的通信。

- 2) 从起始位开始每帧数据都是 9 位,其中第一帧是 7 位从机地址+1 位读写标识位+1 位数据接收方应答位组成。后续的每帧都是 8 位数据+1 位数据接收方应答。

- 3) 如果读写标识  $R/\overline{W}=0$ ,表示主机向从机发送数据,则应答位 ACK 由从机负责拉低。从机在完整收到地址或数据后拉低 SDA 数据总线,表示正确接收。不应答表示数据接收错误。

- 4) 如果读写标识 R/W=1,表示主机自从机接收数据,则应答位 ACK 由主机负责拉低。

- 5) 主机发出第一帧地址和读写位后,地址符合的从机拉低总线,产生 ACK 应答信号。主机开始收或发(视 R/W) 下一帧,直到产生停止位。这期间,其他从机不接收数据,仅判断停止位是否出现,等待下一次比对地址通信的机会。

图 4-38 12C 协议的帧格式

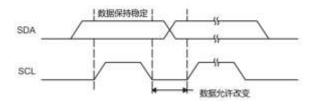

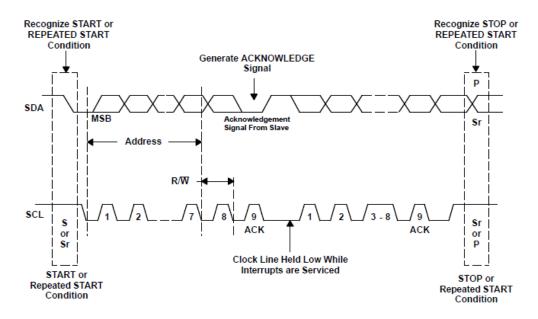

### 12C 协议的起止位

I2C 协议的数据线电平仅允许在时钟低电平时才允许改变。为什么要这么规定,反过来规定行不行?

- 1) 低电平时允许改变数据,高电平时读取数据,这意味着数据的传输时刻在上升沿。

- 2) 线与逻辑是, 谁都能拉低时钟总线产生下降沿, 而产生上升沿却要"大家"都同意。

- 3) 这样一来, 主机就不能强行收发数据, 一定要从机"同意"才行, 也就是如果从机"没空"收发数据, 就可以拉低 CLK, 让时钟线产生不了上升沿。

- 4) 试想一下,如果改为下降沿传输数据,那么主机就可以不顾从机的反对"强买强卖数据"了。

数据线电平在时钟低电平时改变是正常传输数据的状态,那么时钟线高电平时改变数据 线电平就可以赋予其他含义,这是非常巧妙的设计。

- 1) 在时钟线高电平时,数据线下降沿代表了起始位 START。

- 2) 在时钟线高电平时,数据线上升沿代表了停止位 STOP。

图 4-39 I2C 协议数据允许改变时刻

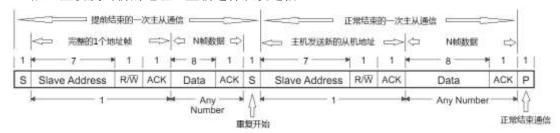

试想这样一种情况,从机往主机发送信息,主机突然就该主意了打算和其他从机通信,怎么办?如图 4-40 所示,主机可以直接重新给起始信号,称为 Repeated Start。Repeated Start 后,主机发出新的地址,重新选择从机通信。

图 4-40 Repeated Start 模式

### I2C 的地址规范

I2C 总线的地址位分为 7 位和 10 位两种,实际上能够挂载的器件数量受总线最大电容 400pF 的限制。为什么地址位会有 7 位呢? 7 位地址+1 位读写标识+1 位应答构成 9 位帧和普通数据帧 9 位所兼容。至于 10 位地址,则可表达 1024 位地址,按 400pF 的总线电容限制,每个器件能引入的电容仅 0.4pF,已是极限。所以 10 位地址足够。而 7 位地址已经可表示 128 个器件,能满足绝大多数需求。

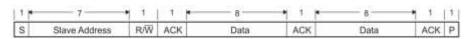

1) 7 位地址模式:如图 4-41 所示,起始位后的首帧为 7 位地址+1 位读写位标识位+1 位应答位,后续帧均为数据帧,直到停止位出现(或者是重复起始 repeat start)。

图 4-41 7位地址模式

2) 10 位地址模式:如图 4-42 所示,起始位后的首帧中前 5 位固定为 11110 (非表示地址),后面仅跟 2 位地址,然后是读写标识和应答。第二帧的 8 位数据作为地址的后 8 位。

图 4-42 10 位地址模式

3) 这种方式可以做到 7 位地址与 10 位地址兼容, 10 位地址不过是把第 2 帧的数据继续当后续地址罢了。

处理器作为从机好说,看上哪个地址用哪个,只要地址不冲突,吱一声的事。外设从机 的地址如何设定?

有的 I2C 协议的芯片由于引脚匮乏,其 I2C 从机地址被固化在了芯片内部,同一型号芯片有若干种 I2C 从机地址的子型号出售,以芯片后缀来区分,这类芯片在购买时一定要看清子型号,买了再退货就难了。

有的 I2C 协议的芯片则是在外部有数目不等的专用地址引脚,可以依靠对地址引脚上拉、下拉、高阻来设定地址。

### I2C型 ADC数据输出

略,请参考 6.2.6

# 第四章 DAC 简介与指标

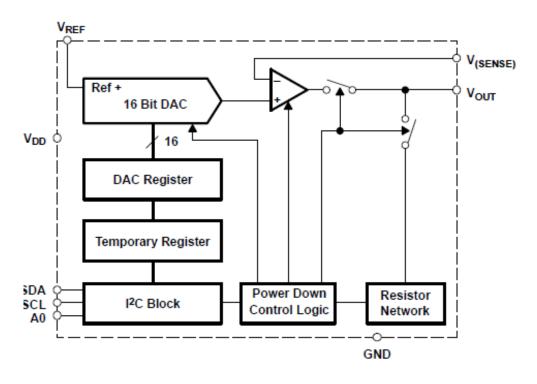

## 5.1 DAC 简介

DAC 即数字模拟转换器,和 ADC 相反,它主要实现的是将数字量转换为模拟量。最简单的 DAC 结构可以通过一个单刀双掷开关实现 1 位的 D/A 变换。当开关与 VCC 相连的时候输出高电平,即 1,当开关与 GND 相连的时候,输出低电平,即 0。这种简单的结构是实现 DA 变换的一个基础。在后面的章节中会具体介绍现在流行的集中 DAC 结构及其基本原理与应用。

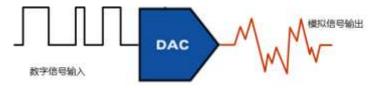

图 5-1 DAC 将数字信号转换为模拟信号

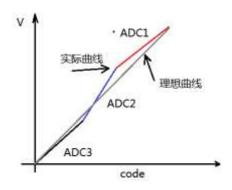

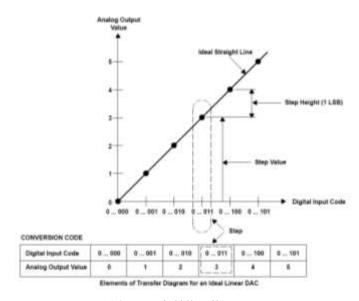

理论上 DAC 理想的转换函数应该也是一条具有无限阶梯数的线,但是实际上是一系列落在这条理想直线上的点,如图 5-2 所示。实际上,DAC 把一个数目有限的离散数字输入编码转换成相应数目的离散模拟输出值。对于 DAC, 1 LSB 相应于连续模拟输出之间的步长高度,它的值与 ADC 中的定义相同。DAC 可以被视为一个数字控制的电位计,它的输出是数字输入编码决定的模拟电压总标度的一小部分。

图 5-2 理想转换函数 (DAC)

## 5.2 DAC 常见性能指标

与 ADC 类似, DAC 也会有静态误差和动态误差,在这里仅做简单的介绍。

#### • 偏置误差

同样,DAC 中偏置误差也被定义为标准偏置点和实际偏置点之间的差值。在 DAC 中,偏置点为数字输入为零时的步长值。这种误差可以通过增加外围电路的方法加以修正,如添加参考电压的方法。

#### • 增益误差

增益误差在 DAC 中表现为在偏置误差调整为零后,DAC 数字输入量为满量程时,实际的输出值和理论值之间的误差。通常这种误差同样可以通过修正的方法进行调整。

#### • 分辨率

与 ADC 类似,DAC 的分辨率以其能分辨的最小模拟输出量来衡量。一般我们说一个 DAC 是 n 位的,表明其所能分辨的最小电压增量为满量程的 $^{1}/_{2n}$ 。例如,一个满量程为 10V 的 DAC,如果是 8 位的则其分辨率为 $^{10}\times\frac{1}{2^{8}}=39$ mV,而同样的 10VDAC 若其为 16 为,则可以达到 153uV 的分辨率输出。

#### • 输出电压

理解为 DAC 输出的电压范围,不同型号的 DAC,输出电压范围相差很大。对于电压输出型 DAC,一般范围在 5-10V,高者可达 30V;对于电流输出型 DAC,输出电流一般在 20mA 左右,高者可达 3A。

#### • 转换时间

指输入的数字信号转换为模拟输出所需要的时间。

# 第五章 DAC 选型与指南

## 6.1 常见 DAC 结构与应用场景

精密型 DAC 包含通用型(General Purpose)和双极型(Bipolar)两种,根据 V<sub>REF</sub> 输入范围和带宽的不同来划分,一般来说通用型 DAC 采用电阻串(R-String)结构,其 V<sub>REF</sub> 不跨越正负电源,通常在一个较窄的范围内,比如 2.5V 左右,并且带宽窄,一般在 1MHz 以下; 双极型 DAC 的 V<sub>REF</sub> 范围跨越正负电源,包含地电平; V<sub>REF</sub> 的带宽较宽,在某些码字下甚至可达到 10MHz,幅度可达±18V,我们习惯将这类双极型 DAC 称为乘法器型(Multiplying) DAC 或MDAC。因 MDAC 使用灵活,操作简单,同时精度卓越而在产业界受到广泛应用,在大学生电子设计竞赛中也经常出现乘法器型 DAC 的身影。

| DAC 技术        | 建立时间/转换速度     | 分辨率           | 备注            |

|---------------|---------------|---------------|---------------|

| 通用型(R-string) | 通常在 10 µ s 左右 | 最高可达 16bit    | 操作简单,低成本,低功耗  |

| 双极型(MDAC)     | 大于 0.2 μ s    | 最高可达 16-18bit | 高精度           |

| 电流引导型         | 小于 1GSPS      | 最高可达 16bit    | 快速,宽带,价格高,功耗高 |

## 6.1.1 电阻串型 DAC (R-String)

R-String DAC,即电阻串型 DAC,采用模拟开关加电阻串的方式对参考输入电压分压,再通过运放缓冲分压结果输出:

图 6-1 一个 3 位电阻串型 DAC 示意图

如图 6-1 所示为一个简单的 3 位电阻串型 DAC 的示意图。我们知道 3 位数字共有 8 种状态( $2^3=8$ ),为实现这 8 种状态的控制,要求提供的分压为 $V_{REF}$ /8的倍数,因而最简单的方法,有 8 个电阻对 $V_{REF}$ 进行分压,即图 6-1 中所示。通过一个 3 线译码器对 3 组开关的状态进行控制,从而实现不同电压的输出。图中,开关的状态量为 101,对照电路的通断,发现实际输入端是与第三个电阻相连(从上至下),换算到电压值为  $5/8V_{REF}$ 。这和数字编码 101,对应十进制为 5,是一一对应的。

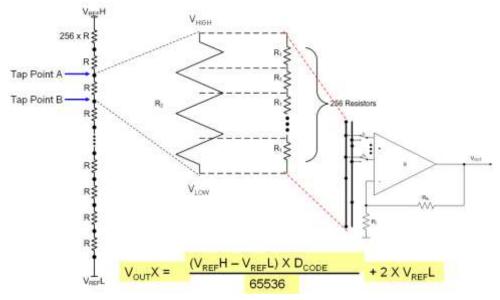

在此基础上,可以扩展到 N 位的 DAC。一个 N 位的电阻串型 DAC 需要  $2^N-1$  个电阻,匹配困难,精度很难做得很高。因此,在 12 位及以上的 DAC 中,通常采用 2 级 R String 的方式来减少电阻器的数量:

图 6-2 2 段型电阻串型 DAC

如图 6-2,是一颗 16 位电阻串型 DAC 的内部示意图,其实是由两组 8 位电阻串型 DAC 来实现的,前一组 256 颗电阻形成一个 8 位 DAC,对输入参考电压进行粗分;后面的 8 位 DAC 对粗分后的电压进行细分,最终达到 16 位的精度。通过分段的方法,可以很大程度上减少电阻的数量。

电阻串型 DAC 的缓冲运放内置在芯片内部,通常采用轨到轨输入/输出运放来实现最大的动态范围,并有时提供 2 倍的增益从而在低参考电压的条件下获得大输出动态范围。但是,因为运放的供电和 DAC 供电联系在一起,为单电源供电,因此无法输出负电平,也就不能接受负参考电压输入。

电阻串型的 DAC 有一个最大的好处就是其传递函数天生是单调的,也就是说在输入编码和输出电压间可以保持一直上升的斜率,不会有拐点出现。在一些要求苛刻的闭环精密控制场合,要求 DAC 必须是单调的。

| 我们推荐使用的 TI | 由阳串型     | DAC 有. |

|------------|----------|--------|

|            | T 17 T T |        |

| 器件           | 简介                                | 封装     |

|--------------|-----------------------------------|--------|

| TLV5638ID    | 双通道的 TLV5636                      | SOIC   |

| TLV5636ID    | 12 位,建立时间 1uS,串行 DAC,内/外部<br>参考   | SOIC   |

| DAC8550IDGKT | 16 位,超低转换脉冲干扰,串行 DAC,外部参考         | MSOP   |

| DAC8552IDGKT | 双通道版本的 DAC8550, 建立时间 10uS         | MSOP   |

| DAC8554IPW   | 四通道版本的 DAC8550                    | TSSOP  |

| DAC7571      | 低功耗,轨至轨输出,12位,I2C接口               | SOT-23 |

| DAC8571      | 16 位,低功耗,电压输出,I2C 接口              | MSOP   |

| DAC7311      | 12 位,SPI 接口,单通道,供电电压 2.0-<br>5.5V | SC70   |

| DAC8411      | 16 位,SPI 接口,单通道,供电电压 2.0-<br>5.5V | SC70   |

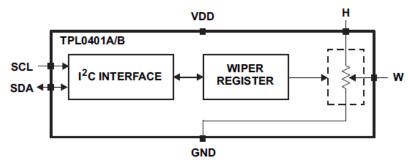

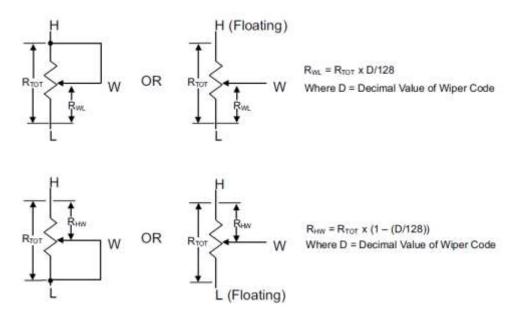

### 数字电位器

上述结构简化后可以设计为一个数字电位器。以 TI TPL0401 为例,从图 6-3 的结构框图可以看到数字电位器的组成比较简单。首先其电位器功能有一个电阻串组成,见功能框图的右侧,这个和 R-string 型 DAC 内部的电阻串功能块是类似的,将电阻串的高端和低端引出来由用户进行连接,同时输出也直接引出来。其实,可以看出这就是一个电位器,之所以这个电位器被称作数字电位器,是因为其调节方式是由左侧的 wiper 寄存器来控制。TPL0401 提供 I2C 标准通讯接口,实现微控制器和 DAC 之间的通讯和控制。

图 6-3 TPL0401 内部功能框图

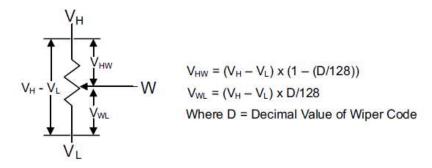

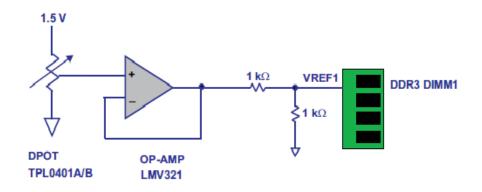

从数字电位器内部结构的介绍,我们可以看出数字电位器可以用作数字电压的输出,实际上,在 TI 的网站上可以看到数字电位器是分类在 DAC 家族中的。在用作电压输出时,数字电位器的作用是将输入电压按照一定比例进行衰减。如图 6-4 所示,W 端与高端(H),低端(L)的电压差可以根据图中的公式计算得到,其中 D 即为用户定义的数字输入值。在该模式下 TPL0401 的一个重要应用场景就是 DDR3 的电压参考。

图 6-4 数字电位器 TPL0401 工作在电压分压模式

图 6-5 TPL0401 用作 DDR3 电压参考电路示意

除了电压输出模式之外,数字电位器区别于一般 DAC 的是其可以当做电位器来用。在数据手册中会给出特定型号数字电位器的电阻宗旨,即 H 端到 L 端的总阻值,如在 TPL0401中,电阻值为 10kΩ。此时需要查阅数字电位器的数据手册,判断该数字电位器内部 H 和 L 端的连接方式。在数字电位器内部一般会将 H 端或 L 端悬空(Floating),如果 L 端悬空,一般会与 GND 相连。这时,在实际使用时有效的电阻值需要对照连接的一端,如图 6-6 所示。另外,在这种情况下还需要格外注意的一点是电阻阻值的精度。在数字电位器中内部电阻的精度一般不高,例如 TPL0401,查看数据手册,我们发现其电阻有±20%的容差。这也就意味着,尽管可以通过数字输入精准控制 R<sub>HW</sub> 和 R<sub>LE</sub> 的比例,但是这两个电阻的绝对值的误差仍然会很大。

图 6-6 不同内部连接的数字电位器输出阻值不同

TI 提供多种型号数字电位器供用户选择:

| 器件                    | 简介                                        | 封装            |

|-----------------------|-------------------------------------------|---------------|

| TPL0401 <i>SA-1</i> 0 | 128taps 数字电位器,I2C 接口,10k 电阻               | SC-70         |

| TPL0501-100           | 256taps 数字电位器,单通道,SPI 接口,100k 电阻          | SC-70         |

| TPL0102-100           | 256taps 数字电位器,双通道,I2C 接口,100k 电阻          | 8SOT-23       |

| TPL8002-25            | 64taps 数字电位器,指数型控制。并行接口,8M 带宽,<br>2.5k 电阻 | 14QFN/14TSSOP |

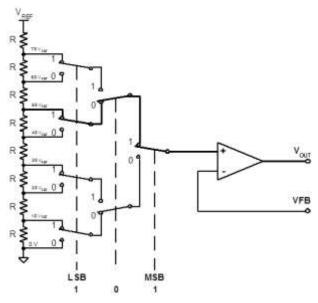

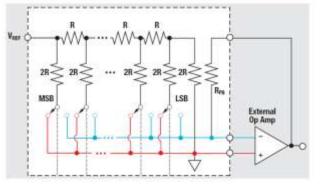

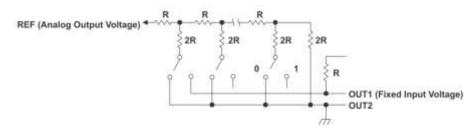

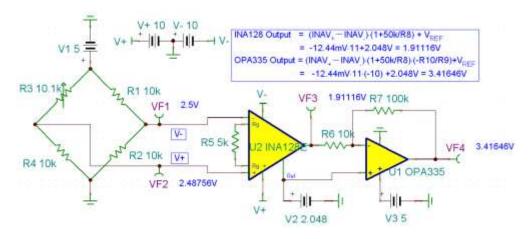

## 6.1.2 乘法型 DAC R-2R

MDAC 采用 R-2R 的正向结构,如图 6-7 所示,是一个 12 位 MDAC 的示意图。下面以 TI DAC7811 为例来对 R-2R 型 DAC 工作过程进行说明。

图 6-7 MDAC 结构示意图

$$\begin{split} &\frac{V_{REF}}{R} \times \frac{Code}{4096} = -\frac{Vout}{R_{FB}} \\ &R_{FB} = R \\ &Vout = -V_{REF} \times \frac{Code}{4096} \end{split}$$

- 1. 12 个选通开关由 SPI 协议控制,使得 2R 的下端接入 lout1(蓝线,接运放反相端)或者 lout2(红线,接运放同相端)

- 2. 外部运放的 Vin+,接地,这时红色的线都接地。

- 3. 应用运放的"虚短"理论(理想运放工作在线性状态下时,Vin-和 Vin+的电压相等),我们可以看做蓝色的线和红色的线连在一起。这时,最右边的两个 2R 相当于并联,阻值等于 R,这个等效电阻 R 会与红圈圈出的 R 串联,形成一个 2R 的等效电阻,这个 2R 等效电阻会与右边第三个 2R 并联……,以此类推,最后,从 V<sub>REF</sub> 端看进去,整个 R-2R 电阻网络的阻值为恒定的 R。

- 4. 于是,我们可以得到,流入 V<sub>REF</sub>端的恒定的总电流为 I<sub>TOTAL</sub>=V<sub>REF</sub>/R

- 5.  $I_{TOTAL}$  在整个 R-2R 电阻网络中的 2R 支路上被分流,流入每个开关的支路电流大小为:  $I_{TOTAL}/2^n$ , 对于 12 位的 DAC7811 来说,n=1-12。MSB 位的开关上的流过的电流最大,为  $I_{TOTAL}/2$ ,以后每个开关上的电流为前一个 2R 的 1/2。

- 6. 每一路 2R 上的电流,由开关选通,决定是流入 Vin-还是 Vin+,流入 Vin-的电流总和,对于 DAC7811 来说,将为:

$$I_{-} = \frac{V_{REF}}{R} \times \frac{C \text{ode}}{4096}$$

这里 CODE 即为写入 DAC7811 的控制字的值。

7. 记住 Vin+是接地的,流入 Vin+的电流对输出信号没有贡献。对于流入 Vin-的电流,由运放的"虚断"理论(理想运放工作在线性放大状态时,流入 Vin-或 Vin+的电流总和为 0,即没有电流进入 Vin-或 Vin+)可知,流入 Vin-的电流将等于运放的输出电压 V<sub>out</sub> 在 R<sub>FB</sub> =上产生的电流,方向相反:

$$I_{-} = -\frac{V_{\text{out}}}{R_{\text{FR}}} = \frac{V_{REF}}{R} \times \frac{C \text{ode}}{4096}$$

在设计 DAC7811 时, TI 会把 R<sub>FB</sub>做到和 R 相等, 于是, 最终我们得到:

$$V_{out} = -V_{REF} \times \frac{Code}{4096}$$

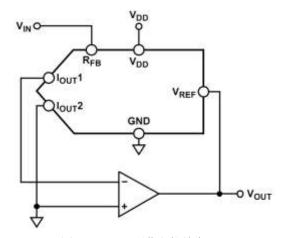

这样,就成功将 MDAC 用作程控衰减。如果把 R-2R 网络放在运放的反馈回路中,如图 6-8,即可得到一个程控放大器:

图 6-8 MDAC 用作程控放大器

其推导过程同上, 只是输入和输出相反, 得到计算公式为:

$$V_{\rm out} = -V_{\rm in} \times \frac{4096}{Code}$$

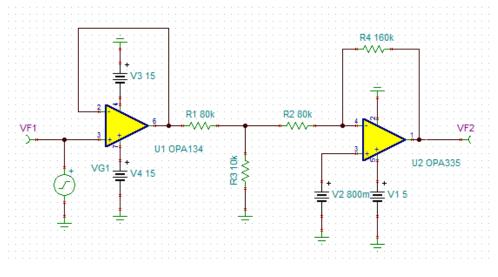

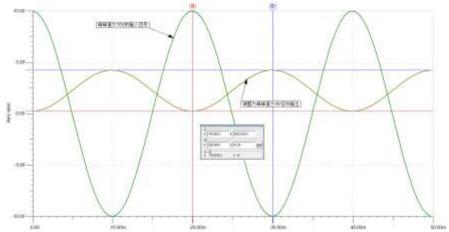

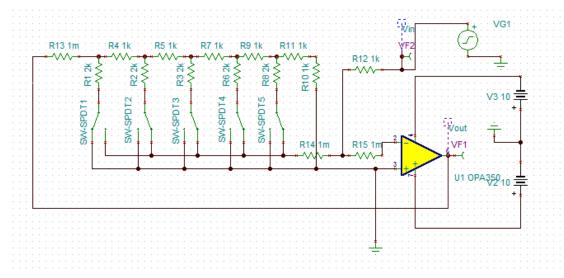

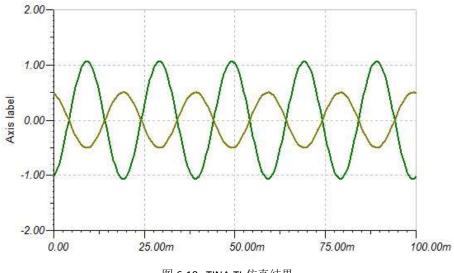

如图 6-9 为在 TINA-TI 中用多路开关模拟一个 5 位的 MDAC 用作程控增益。其中 VF2 为输入, VF1 为输出。输入电压为峰峰值为 1V 的正弦波形。当开关打在图示位置时,通过上面的分析,我们知道理论的增益倍数为 2, 其仿真结果如图图 6-10 所示。

图 6-9 TINA-TI 中多路开关模拟 MDAC

图 6-10 TINA-TI 仿真结果

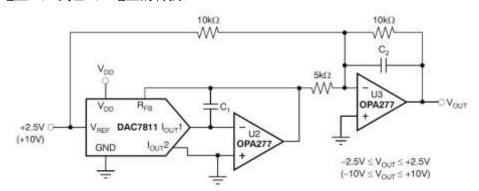

对于 MDAC 来说,输入的 V<sub>REF</sub> 实际上是被换算成流入或流出 VREF 脚的电流,只要外部运放采用正负电源供电,即使 MDAC 采用 3.3V 单电源供电,MDAC 也可以实现双极性电压输入和输出。这对我们的设计带来极大的便利。下面我们看看如果利用 MDAC 和外部运放来实现恒定电压 10V 到±10V 电压的转换:

图 6-11 外部电路实现双极性输出

如图 6-11,DAC7811 通过第一个 OPA277 产生的输出为一10V 到 0V 可调;第二个 OPA277 实现的是一个反相加法器处,10V 的参考电压产生的输出为一10V 到 0V,而 DAC7811 和第一个 OPA277 的输出在第二个 OPA277 上产生的输出为 0V 到+20V,相加后即得到一10V 到+10V 的输出范围,最终的计算公式为:  $V_{OUT}=2*V_{REF}*$ (Code/4096)一 $V_{REF}$ 。

注意在使用外部运放时,由于 DAC7811 的输出电容较大,需要在反馈回路中接入一个并 联电容来帮助外部运放稳定,同时确保外部运放的带宽和压摆率满足要求。可以在 DAC78xx 的数据手册中找到针对不同应用推荐的对应外部运放型号。 还值得注意的是  $V_{out} = -V_{REF}^*$  Code/2<sup>N</sup> 表明 MDAC 在这种配置下产生的是衰减的输出,输出是小于输入的。因此,可以利用 MDAC 的这种特性完成程控衰减器的工作。同理,我们把 MDAC 放在运放的反馈回路中,可以得到一个程控放大器,在用做程控放大器时,应保证外部运放的增益带宽积和压摆率等指标。

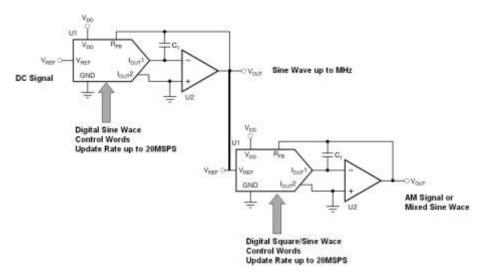

注意到 MDAC 的 VREF 引脚常常拥有±15V 及以上的电压输入范围和 10MHz 的-3dB 带宽,同时并行输入的 MDAC 拥有 20MHz 的刷新率,因此可以利用 MDAC 来进行一些 kHz 量级的波形和各种调幅信号:

图 6-12 利用 DAC 实现调幅信号

如图 6-12, 前一只 MDAC, 例如 DAC7822, 输入一个固定的参考电压 10V, 用数字化的 正弦波刷新 DAC, 通过外部运放可以产生单极性或双极性的正弦波; 将生成的正弦波输入第 二个 MDAC 的输入端, 用期望的调幅信号刷新 DAC 就可以实现调幅信号输出了。

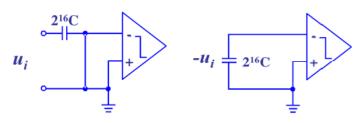

在 MDAC 应用中,R-2R 电阻网络都是正向工作的,也就是说总是有信号从 VREF 脚流入,利用 VREF 端输入电阻恒定的特性实现电压到电流的转换,因此正向 R-2R DAC 的输出是电流,在 DAC 外部还需要一只运放来完成从电流到电压的转换。我们可以将 R-2R 电阻网络用在反向配置中,这时实现的是电压进电压出:

图 6-13 反向配置实现电压输出

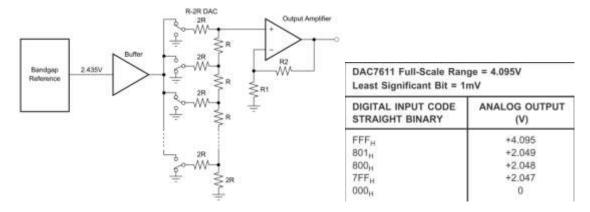

如图 6-13,参考电压 V<sub>1</sub>从 OUT1 输入,OUT2 接地,此时的输出电压为 V<sub>0</sub>=V<sub>1</sub>\*Code/2<sup>N</sup>。 反向 R-2R 型 DAC 利用了 R-2R 电阻少,精度高的特点,但损失了大带宽和宽电压范围,因此采用这种结构的 DAC 通常采用内置的固定参考电压源,如图 6-14,DAC7611 就是一颗反向 R-2R 的 DAC,它内建了一个 2.435V 的固定参考电压和一个增益为 1.682 倍的输出运放,这样 DAC7611 的数字输入和模拟输出一一对应,即输入数字 N,即输出 NmV 的电压。

图 6-14 DAC7611

### 我们推荐使用的 TI MDAC 有:

| 器件            | 简介                                           | 封装    |

|---------------|----------------------------------------------|-------|

| DAC7811IDGS   | 12 位,串行,建立时间 0.2Us,±15V,10MHz                | MSOP  |

| DAC7821IPW    | 12 位,并行,刷新率 20MSPS,建立时间 0.2Us,±15V,<br>10MHz | TSSOP |

| DAC7822IRTAT  | 双通道的 DAC7821                                 | QFN   |

| DAC8801IDGKT  | 14 位,串行,土18V,10MHz,建立时间 0.5uS                | MSOP  |

| DAC8802IPW    | 双通道的 DAC8802                                 | TSSOP |

| DAC8805QDBT   | 双通道的 DAC8806                                 | TSSOP |

| DAC8806IDB    | 14 位,串行,刷新率 20MSPS,±18V,10MHz,建立时间 0.5uS     | SSOP  |

| DAC8811IBDGKT | 16 位,串行,建立时间 0.5uS,±15V,MDAC                 | MSOP  |

| DAC8820IBDB   | 16 位,并行,刷新率 20MSPS,建立时间 0.5uS,±15V,<br>MDAC  | SSOP  |

| DAC8812IBPW   | 双通道的 DAC8811                                 | TSSOP |

| DAC8822QBDBT  | 双通道的 DAC8820                                 | TSSOP |

## 6.1.3 ΔΣ型 DAC

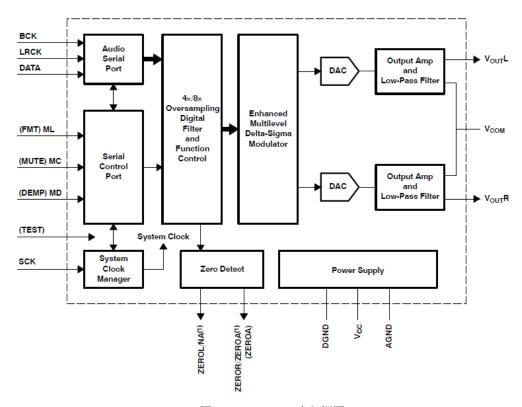

与  $\Delta \Sigma$  ADC 相似,有一类 DAC 也会采用 delta-sigma 技术以提高转换的精度。一般来讲多数的音频 DAC 会采用  $\Delta \Sigma$  技术以提高音频的输出的质量。如图 6-15 所示,为 24 位过采样音频 DA 转换器 PCM175x 的内部模块框图。

图 6-15 PCM175x 内部框图

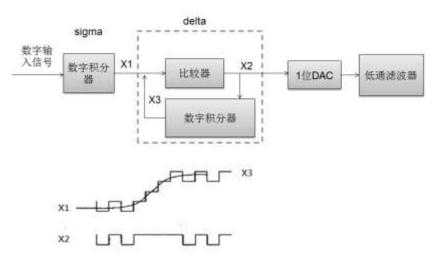

$\Delta \Sigma DAC$  内部包括插值滤波器和  $\Delta \Sigma$ 调制器(包含数字积分器、量化器的和反馈回路的模块),开关电容 DAC 和模拟低通滤波器。其关键模块为  $\Delta$  调制器,基本工作原理和  $\Delta \Sigma$  ADC 相似。其核心部分是一个  $\Delta$  调制器,见图 6-16。输入信号 X1 通过  $\Delta$  调制器被调制成 X2,在调制器内部,首先对输入信号进行积分,当积分后的值大于输入信号 X1,X2 输出即为正,反之,X2 输出为负。经过这样的调理,我们可以发现,对 X2 进行积分的结果即为 X3。对于 X2 信号经过一个 1 位的开关电容 DAC 转换为模拟信号,通过积分即可还原出原始数字输入信号对应的模拟信号,再经过低通滤波滤除高频噪声,将信号平滑,即可得到高精度的模拟输出信号。在实际的 DAC 中,后面的积分工作会移到信号的开始,即 X1 之前进行。这样做可以避免  $\Delta$  调制器对较快变化的输入信号相应的延迟,以及对直流的无法相应。

图 6-16 Δ Σ DAC 基本工作原理

TI 提供的音频  $\Delta \Sigma$  DAC 有:

| 器件         | 简介                            | 封装   |

|------------|-------------------------------|------|

| PCM1753DBQ | 24 位,192KSPS,SNR=106dB,音频 DAC | SSOP |

| PCM1804DB  | 24 位,192KSPS,SNR=116dB,音频 ADC | SSOP |

| PCM1803ADB | 24 位,96KSPS,SNR=103dB,音频 ADC  | SSOP |

## 6.1.4 电流引导型 DAC Current Steering

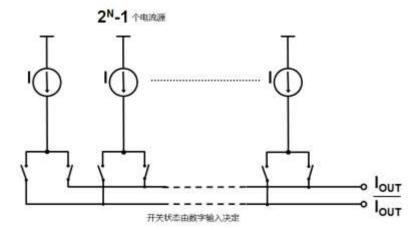

和高速ADC对应,高速DAC被广泛使用在波形产生,测试设备及无线基础设施中,当代高速DAC的制造是基于亚微米CMOS或BiCMOS的工艺,已经达到了一个全新的性能水准,实现了1GSPS的刷新率以及14位,甚至16位的分辨率。为了达到如此高的刷新率和分辨率,DAC采用了一种带分段(segmented)电流源的电流导引型(current steering)架构。

图 6-17 电流引导型 DAC 中的电流源阵列

此类单片电路DAC的核心单元是电流源阵列(array),其设计用于输送出满刻度输出电流,典型值为20mA。内置的解码器在每次DAC刷新的时刻驱动(addresses)差分电流开关。如图 6-17所示,该电流源阵列有两个电流输出,两路输出互补,使得输出的电流总量为一个恒定值。数字输入导引源自各个电流源的电流,输出到相应信号输出电流的差分输出端。相较于电压输出,这种方法可以保证更高的速度。

在此采用差分信号是为了改善动态性能,同时降低负载电阻上承载的输出电压的摆动。 理想情况下,此类信号电压摆幅是越小越好,以确保DAC有最适宜的线性度。此信号电压的 上限,以及相关的负载电阻,通过输出电压所遵循的规格实现定义。分段电流引导架构的意 义在于降低了电路复杂性,并因此降低了杂散脉冲的能量。这些,都从整体上改善了DAC的 线性度及交流性能。作为一种全新的系统架构,其高刷新率和卓越的动态性能,使得其输出 频率的合成能力达到百兆赫兹的范围,而这种方式通常被称为"直接中频"。

| 我们推荐使用的 TI | 高速 DAC 有: |

|------------|-----------|

|            | 1         |

| 器件          | 简介                                 | 封装    |

|-------------|------------------------------------|-------|

| DAC902E     | 12 位 165MSPS,高速 DAC                | TSSOP |

| DAC5662IPFB | 双路 12 位 275MSPS,高速 DAC             | TQFP  |

| DAC904E     | 14 位 165MSPS,高速 DAC                | TSSOP |

| DAC5672IPFB | 双路 14 位 275MSPS,高速 DAC             | TQFP  |

| DAC5687IPZP | 双路 16 位 500MSPS,1x/2x/4x/8x 插值 DAC | HTQFP |

#### 6.1.5 PWM DAC

在很多嵌入式的控制应用中,会用控制器内部集成DAC模块或独立的DAC芯片来产生模拟信号。但是,采用控制器的PWM (Pulse Width Modulation,脉冲宽度调制)信号来实现D/A 变换也是一种常见的方法,在低成本设计中应用非常广泛,我们将讨论如何使用PWM来产生模拟信号,和PWM DAC的精度。

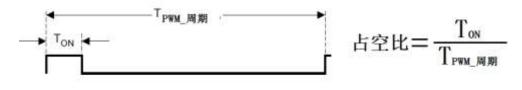

PWM(Pulse Width Modulation,脉冲宽度调制)是一个周期固定但占空比可调的信号,如图 6-18所示。

图 6-18 PWM 信号

在整个 PWM 周期中,高电平持续时间(T<sub>ON</sub>)所占的比例,称为占空比。显然,T<sub>ON</sub>时间将直接影响该周期的直流电压均值,T<sub>ON</sub>时间越长,直流电压均值越大。该对应关系可理解为直流电压均值和 PWM 的占空比是成线性关系的。

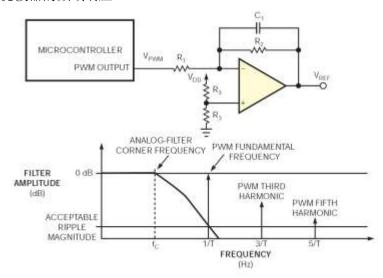

如果在微控制器输出端对 PWM 信号进行合适的滤波,我们可以产生可变的直流参考电压。在图 6-19 中,FFT(快速傅里叶变换)将 PWM 的方波信号变换为等效频域信号,同时图中也给出了低通滤波器的频域响应。

图 6-19 PWM 波形在频域等效信号

PWM 信号转换成直流信号的硬件实现:利用控制器产生 PWM 信号; PWM 经过一阶模 拟低通滤波器产生 dc 电压。在 FFT 图上,发生器产生的 PWM 信号基频为 1/T,T 为 PWM 的 周期;当设计模拟低通滤波器时,基频(fPWM)和信号频率之间的过渡带宽窄是设计关键; 所使用的模拟滤波器的截止频率,决定了 PWM DAC 的带宽。

图 6-20 通过低通滤波将 PWM 信号转换为直流信号

图 6-20 给出了 PWM 信号产生直流电平的时域波形, PWM 信号通过模拟低通滤波器, 会产生一个带纹波的直流电压信号。电压纹波的形成是由于滤波电容的充电(在 PWM ON 期间)和放电(在 PWM OFF 期间)。这就是最基本的 PWM 产生直流电平的原理。

用 PWM 信号产生模拟电平的另一个好处是可以利用数字方法传输模拟信号,从而在需要隔离的地方使用数字隔离器件,毕竟数字隔离器件比模拟隔离器便宜了许多。

### 6.1.5.1 PWM DAC 的性能参数

本节将讨论影响 PWM DAC 分辨率的参数以及这些参数间的关系,以便获得更好性能的 PWM DAC。其中最为关键的两个设计要素是占空比分辨率和低通滤波器设计。

### 1. 占空比分辨率

首先,DAC 分辨率是指 DAC 的数字模块加 1 时,模拟电压输出的最小增长单位。在 PWM DAC 中,可理解为占空比的最小时间单位加 1 时,模拟输出的最小增长单位。因此就 PWM DAC 而言,PWM 占空比的分辨率直接影响 DAC 的分辨率。

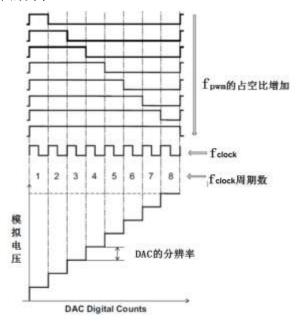

用 fpwm 表示输入到低通滤波器的 PWM 信号频率,该频率信号可使用 MCU 的定时器模块产生。fclock 表示定时器所用时钟源的频率,即让定时/计数器模块加 1 的时间间隙。N 为 PWM 占空比分辨率,用比特位表示。fpwm、fclock 和 PWM DAC 占空比分辨率的关系如下:

$$2^{N} = \frac{\text{fclock}}{\text{fpwm}} = \text{PWM}$$

占空比的步数 = DAC 的输出电平数

下面将举一个简单的例子。

如图所示,在一个 fpwm 周期里,有 8 个 fclock 周期,fclock =8×fpwm。因此,PWM 的占空比可以有 8 种变化,如上图的上半部分表示的 8 种变化。而 PWM 的占空比直接影响 DAC 的电压输出,可得出 DAC 的电平输出可以有 8 种变化(8=23),即分辨率为 3bits。

根据式子  $2^N = \frac{\text{fclock}}{\text{fowm}}$ ,要增加 PWM DAC 的分辨率,要么提高 fclock,要么降低 fpwm。

结合后端的低通滤波电路考虑,更高的 fpwm 频率可以降低滤波电路的复杂度。高阶的滤波器需要更多的外围器件,这会增加系统的成本和空间。降低低通滤波器的阶数,会影响DAC 的带宽。综上,为获得更高 fpwm 占空比分辨率的限制因素是 PWM 信号的时钟源fclock。

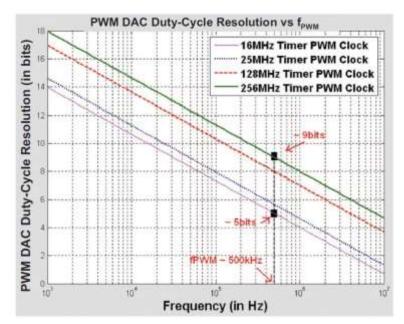

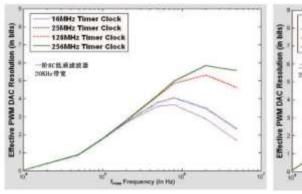

拥有常规定时器模块(TimerA 或 TimerB)的 MSP430 单片机的 fclock 最大为系统的时钟 频率(F2xx 为 16MHz,F5xx/F6xx 为 25MHz);而拥有 TimerD 模块的 MSP430 单片机的 PWM 信号时钟源 fclock 高达 256MHz,这使得在给定的 fpwm 频率下,能提供更高的分辨率。

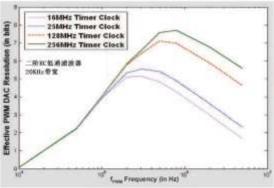

图 6-21 PWM DAC 占空比分辨率和 fpwm 的关系

从图 6-21 中可以看出,给予给定的 fclock (图中 4 条直线任选一条), fpwm 频率越高,能够完成的 DAC 分辨率越低。

为获取更高占空比分辨率的 DAC,可以通过提高 fclock 的频率来完成。拥有 TimerD 模块的 MSP430 设备,通过高分辨率定时器可以产生 256MHz 的频率 fclock。如图,给予给定的 PWM 频率, fpwm=500KHz, fclock=16MHz→DAC 的占空比分辨率为 5bits; 而 fclock=256MHz,DAC 占空比分辨率可达 9bits。

### 2. 谐波失真和电压输出的不确定度

上节描述的占空比分辨率,是影响 PWM DAC 分辨率的一个重要因素。另一个影响因素是低通滤波器未完全滤波而造成的谐波失真。 谐波是某一基波频率的整数倍,就 PWM DAC 而言,谐波是 fpwm 频率的整数倍。

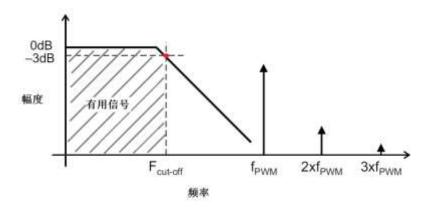

图 6-22 低通滤波器幅频特性

实际低通滤波器的幅频特性如图 6-22 所示,-3db 点对应的频率为截止频率 Fcut-off, 截止频率左侧的阴影部分为我们所需要的有用信号可以出现的位置,即 PWM DAC 的带宽。当 PWM 的占空比保持恒定时,滤波得到的是一直流信号,出现在上图中的横轴 0 坐标处;当 PWM 的占空比以频率小于 Fcut-off 的正弦波规律变化时,滤波得到的是一正弦信号,出现在上图中的阴影范围中。从图中可以看出,要减小谐波等无用信号,可以加大滤波器的衰减斜率(减小滤波器的过渡带),或者降低模拟滤波器的截止频率,也可以增大 fpwm 的频率。

要使滤波器的过渡带变窄,需要使用更加复杂的高阶滤波器,这个会增加系统的成本。 降低滤波器的截止频率意味着减小 DAC 或信号的带宽。增大 fpwm 的频率会影响 PWM DAC 的占空比分辨率。

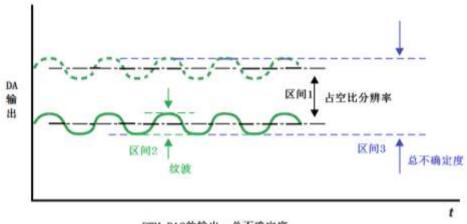

综上所述,占空比分辨率决定了 DAC 的输出电压在某一范围内是一个定值,如图中的区间 1。由于谐波而造成的纹波(图中的区间 2)会叠加在该输出上。占空比分辨率和谐波波动一起构成了 PWM DAC 输出的总不确定度(图中的区间 3)。

PWM DAC的输出一总不确定度

### 6.1.5.2 模拟滤波器设计

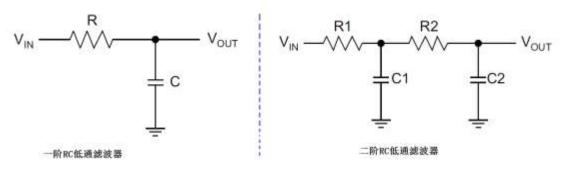

PWM DAC 的性能,很大程度上依赖于模拟低通滤波器的选择和设计。DAC 的输出是将fpwm 载波频率通过模拟低通滤波器过滤后得到的稳定的模拟电压。相对于有源滤波器,无源滤波器具有低成本、设计简易、稳定性也有保证。因此,本节仅讨论使用无源滤波器,一阶 RC 低通滤波器和二阶 RC 低通滤波器的电路结构如下图。

图 6-23 一阶 RC 低通滤波器和二阶 RC 低通滤波器

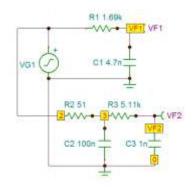

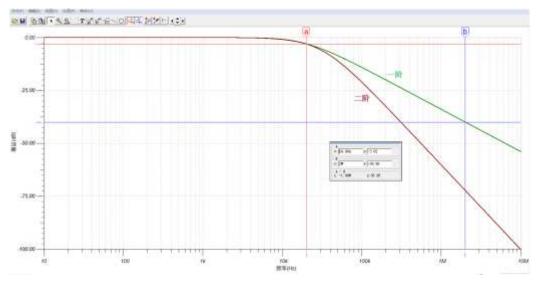

结合元器件的实际参数,我们比较下实际应用中一阶、二阶 RC 低通滤波器的性能表现,两者的带宽均设计为 20KHz:

- 一阶 RC 低通滤波器的参数选择: R=1.69k  $\Omega$  , C=4.7nF; => BW = 20KHz;

- 二阶 RC 低通滤波器参数选择: R1=51 $\Omega$ , R2=5.11k $\Omega$ , C1=100nF, C2=1nF; => BW = 20KHz:

将 MSP430 产生 3Vp-p 和 50%占空比的 PWM 信号,输入到以上两种滤波器,分析 DAC 的输出。对于 4 种 fclock(16MHz/25MHz/128MHz/256MHz),每种 fclock 对应 fpwm 从 10kHZ 到 5MHz 进行变化时 PWM DAC 的有效分辨率曲线如下图所示。

从上面两图我们可以看到,在给定截止频率和阶数的滤波器下,随着 PWM 的基频升高,等效 DAC 的分辨率升高,这是由于该滤波器对频率越高的 PWM 基频滤波效果越好;而转折点发生在 1MHz 左右,这时开始 PWM 的占空比分辨率对等效 DAC 的精度开始占据主导位置: PWM 的基频越高,在给定 Timer 主频的条件下,占空比分辨率越低。

对比左右两图,我们可以看到,带宽同样是 20KHz 的低通滤波器,为什么二阶比一阶获得的效果好得多?因为二阶滤波器的过渡带比一阶滤波器的过渡带更窄,可以更大程度地衰减 PWM 的基频和谐波分量。这个可以借助 TI 的仿真工具 Tina-TI 来分析。

在 Tina-TI 中放置如上图所示的元器件并设置相应的参数,选择"分析/交流分析/交流传输特性",可以分析 RC 滤波器的传输特性,如下图所示,两个滤波器在 20KHz 处的截止频率处均提供了-3dB 的衰减,而一阶低通滤波器的下降率为-20dB/10 倍频程,所以在 2 个 10 倍频程的 2MHz 处,总共能提供约 40dB 的衰减;而二阶 RC 滤波器的下降率能达到-40dB/10 倍频程,所以在 2MHz 处,能提供约 80dBd 的衰减;从而能把 PWM 的基频和谐波滤得更加干净。

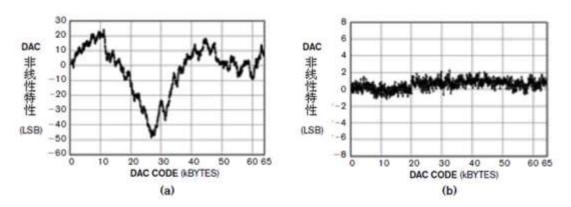

## 6.1.6 DAC应用场景总结

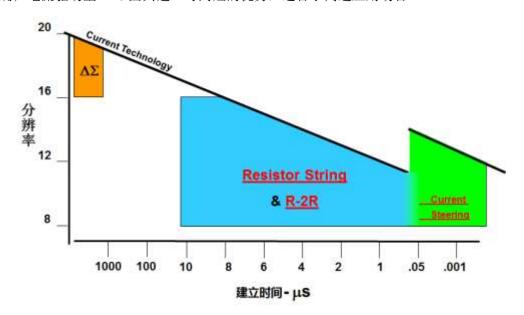

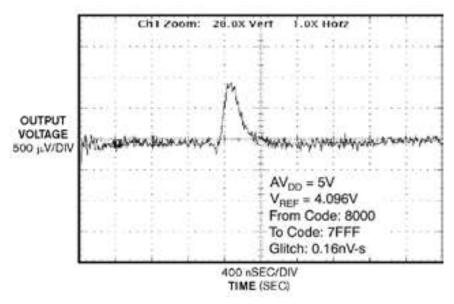

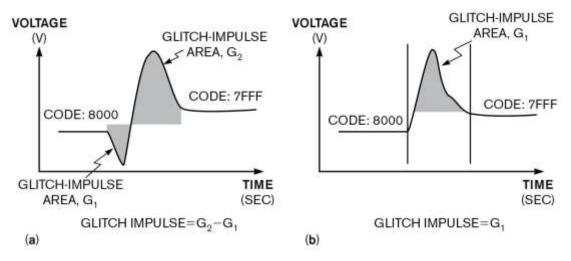

从前文对几种 ADC 的结构和特点分析,我们不难发现 这几种 DAC 在转换时间以及分辨率上各有优势,如图 6-24 所示。其中  $\Delta \Sigma$ 型 DAC 有高转换精度的优点,但相对建立时间较长,一般常用在对精度要求高,但时间要求不高的场合,常见的音频用 DAC 为  $\Delta \Sigma$  结构;电阻串型以及 R-2R 型 DAC 的建立时间一般在 us 级别,其中电阻串型相对比较便宜,R-2R 型更为精确;电流驱动型 DAC 因其建立时间短的优势,适合于高速应用场合。

图 6-24  $\Delta \Sigma DAC$ ,电阻串型 DAC 以及电流引导型 DAC 建立时间和分辨率对比

根据不同 DAC 性能的特点,在不同的应用场合应选择不同的 DAC。

| 应用场景              | 传感器信号                   | 检测与测量                   | 音频                          | 通信,图像                    |

|-------------------|-------------------------|-------------------------|-----------------------------|--------------------------|

| 信号分类              | 温度,湿度,压<br>力,电压,电流<br>等 | 工业探伤,颤动<br>检测,电机控制<br>等 | 交流信号                        | 宽带,高速                    |

| 信号特点              | 小信号,变化<br>慢,DC 为主       | 瞬时采样,DC-<br>KHz 信号      | 20-20KHz,宽<br>动态范围,低失<br>真度 | MHz 信号,大<br>带宽,宽动态<br>范围 |

| ΔΣ型 DAC           |                         |                         | +++                         | -                        |

| 电阻串/R-2R 型<br>DAC | +++                     | +++                     | +++                         | -                        |

| 电流驱动型<br>DAC      |                         |                         |                             | +++                      |

# 6.2 DAC 选型与电路设计

在设计 DAC 时,我们可以参考下面的指标:

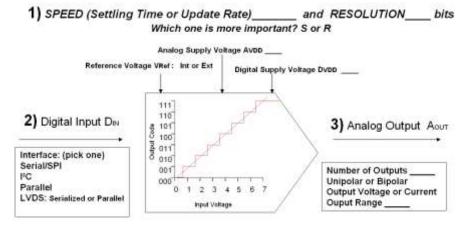

图 6-25 DAC 选型参考对照图

这张图和之前 ADC 选型时的图非常类似,其实 ADC 和 DAC 是两个对称相反的过程:对于 DAC 的输入——数字信号,对应着 ADC 的输出,所以我们需要关心数字信号的输入方式,即接口; DAC 的模拟输出则对应着 ADC 的模拟输入,需要考虑单极性、双极性、单端和差分、多通道等特性;和驱动 ADC 的输入一样,在 DAC 之后也必须放置一个低通滤波器来消除高次谐波,这对 DAC 来说有一个专用的名称,叫做重建滤波器。

## 6.2.1 确定所需 DAC 的类型

在前面的应用场景中已经对各种不同结构的 DAC 对应的应用场景做了简单的介绍。

一般来所,在高精度控制回路应用中,DAC 多采用 R-2R MDAC。这种结构能完成高电压输出。MDAC 厂商能设计高精度(16-bit)的器件,达到 1LSB 积分非线性和微分非线性误差。MDAC 还要求外置一只快速建立时间(小于 0.3 微秒)、乘法带宽(multiplying bandwidth)大于 10MHz、电流输入电压输出的运算放大器。

反向 R2R DAC 最适合工业应用。在反向 R2R DAC 中,每个单刀双掷开关控制 2R 支路连接到 Vref-h,或是 Vref-l。这种结构生产工艺相对简单。R2R 结构具有一条并行数据输入总线。对于带有串行接口器件而言,在 DAC 进行数据转换之前,使用内部串并寄存器,进行串并转换。在很多情况下,各个开关的切换时序歪斜(不同步)都表现为 DAC 的 输出端毛刺。反向 R2R DAC 和 MDAC 一样,通常具有出色的低噪声、INL 以及 DNL 性能,而且具有不错的建立时间。

电阻串 DAC 适用于便携式仪表、闭环伺服控制、过程控制和数据采集系统。电阻串 DAC 可确保在整个输入编码范围内的模拟输出的单调性(monotonicity),不错的 DNL 性能和非常低的功耗。这种 DAC 产生的毛刺干扰通常要低于其他类型的 DAC。但是,INL 性能取决于电阻阵列匹配,并受芯片布局影响较大;而且电阻串 DAC 的噪声也取决于电阻串阵列的热噪声,而且噪声相对较高(因为较 R-2R 型 DAC 而言,电阻串 DAC 的电阻数量较多)。

## 6.2.2 确定所需的分辨率和建立时间

DAC 的刷新速度和建立时间和 ADC 的采样速度和建立时间有相近的含义。对于刷新速度(或采样速度) $F_S$ 来说,在产生(或采集)交流信号 F 时是非常重要的指标, $F_S$  必须高于两倍的  $F_F$  否则无法重建信号。这一点大家都很好理解,并且也得到足够多的重视。

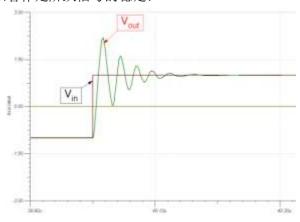

建立时间在直流测量中是一个非常重要的指标,对于 ADC 来说,对采样保持器上的电容充电到期望精度需要一定的时间,如果建立时间大于采样时间,那么得不到真正准确的结果;对于 DAC 来说,缓冲运放的输出达到期望精度也是需要时间的,如果在信号建立到期望精度之前就被后端系统获取,可能会产生误动作;对于多通道系统来说,在各个通道间切换的时候可能会产生阶跃信号,阶跃信号稳定到期望的精度上也需要一定的时间。对于这三种情况来说,我们都可以看作是阶跃信号的稳定:

图 6-26 建立时间与稳定有效信号输出

如图 6-26 所示,当输入或输出信号发生跳变时(比如 ADC 开始一个新的采样周期或 DAC 的数字输入改变),信号需要一定时间才能稳定到所需的精度上(指定了稳定精度的建立时间才有意义,比如定义输出达到输入 99.999%所需的时间为建立时间才是有效的)。因此,对于关注于直流精度,通常用来产生控制电平的电阻串型 DAC 来说,建立时间常常在数据手册中比刷新速率占据更重要的位置。

## 6.2.3 选择并设计 DAC 的模拟输出端

同样的,使用 DAC 时,也需要小心设计它们的模拟接口。

DAC 的模拟输出可能是电压或电流,如果对电压输出进行了缓冲,则输出阻抗将很低。 而电流输出和未缓冲的电压输出将存在较高的阻抗,并还可能具有电抗性分量以及纯粹的电 阻性分量。在有些 DAC 架构的输出结构中,输出阻抗与 DAC 上的数字码字成函数关系。

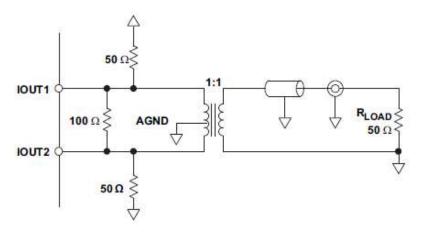

理论上,电流输出应当连接到电阻为零欧姆的地电位。在实际应用中,该输出将采用非零阻抗和电压。适合视频、RF 或 IF 应用的大多数高速 DAC 具有电流输出,旨在直接驱动源和负载端接电缆。例如,20-mA 电流输出 DAC 可以在  $25\Omega$ 负载(相当于  $50\Omega$ 源和负载端接电缆的直流电阻)上产生 0.5V 的电压。

差分输出可以直接驱动变压器的初级绕组,并且通过将输出绕组的一侧接地,可以在次级绕组处产生单端信号。与简单地从 DAC 电流输出之一直接获取输出信号并将其他输出接地相比,这种方法通常可以在高频率下获得更加失真性能。现代电流输出 DAC 通常具有数个差分输出,以便实现高共模抑制并减少偶数阶失真产物。常见的满量程输出电压范围为 2mA 至 30mA。

在许多应用中,需要将 DAC 的差分输出转换成适合驱动同轴线路的单端信号。可用高速运放(可参考应用笔记 SLAA135),也可用变压器设计模拟输出接口,最后在单端信号输出端进行滤波。