各位TI的工程师,请问,tlv320aic3204 做从设备,时钟采样配置为48000,16bit, INR3/INL3 输入,时钟这样的配置正确吗?

aic3204_write(0, 0x0); // Select page 0

aic3204_write(27, 0x1); // BCLK and WCLK is set as input AIC3204(slave) 00: audio InteRFace = i2s

aic3204_write(28, 0x0); // Data ofset = 0

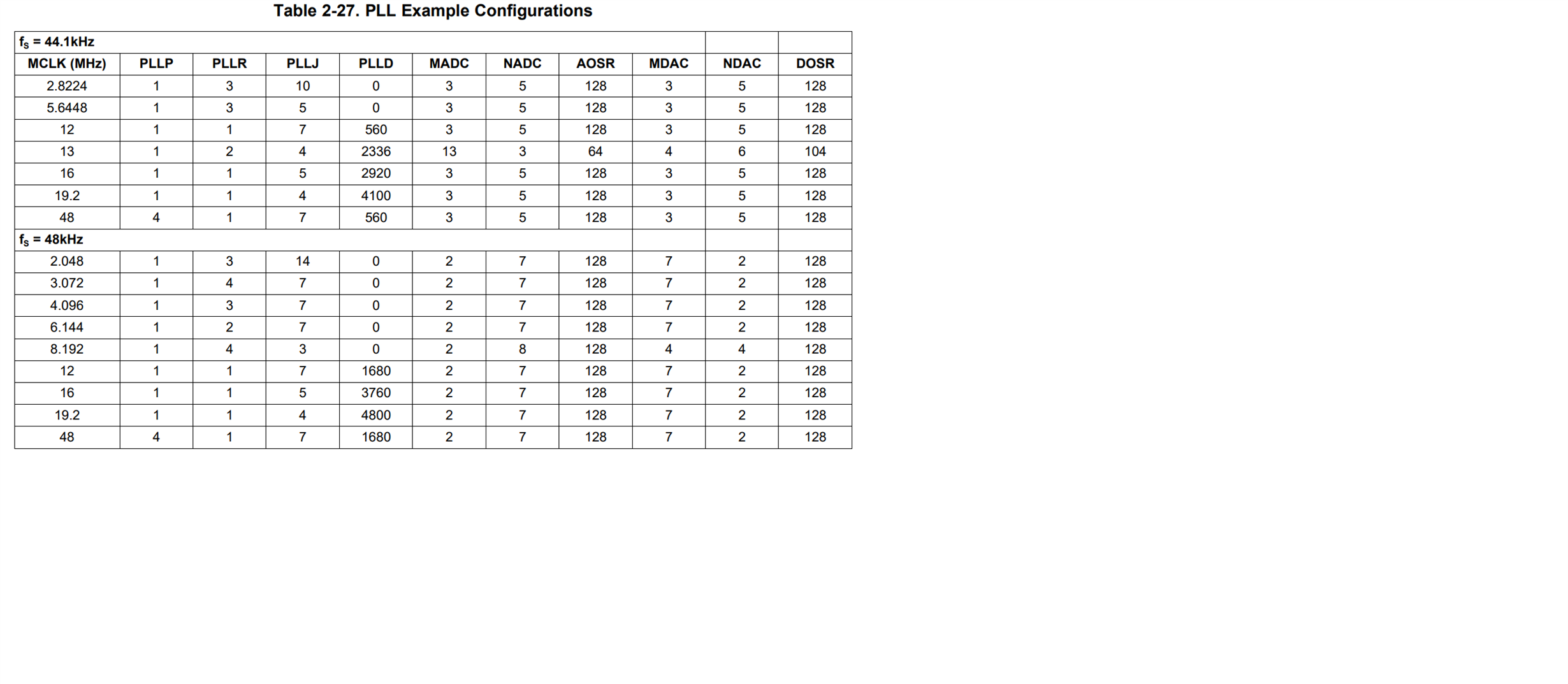

aic3204_write(4, 0x3); // PLL setting: PLLCLK <- MCLK, CODEC_CLKIN <-PLL CLK

aic3204_write(6, 0x8); // **PLL setting: J=8 (comment does not match)

aic3204_write(7, 0x7); // PLL setting: HI_BYTE(D)

aic3204_write(8, 0x80); // PLL setting: LO_BYTE(D)

aic3204_write(30, 0x80); // For 32 bit clocks per frame in Master mode ONLY (make sure that BCLK >= [ (# bits per channel) * 2 ]

aic3204_write(5, 0x91); // PLL setting: Power up PLL, P=1 and R=1

aic3204_write(13, 0x01); // Hi_Byte(DOSR) for DOSR = 256 decimal or 0x01080 DAC oversamppling

aic3204_write(14, 0x00); // Lo_Byte(DOSR) for DOSR = 256 decimal or 0x0100

aic3204_write(20, 0x00); // AOSR for AOSR = 256 decimal or 0x0000 for decimation filters 1 to 6

aic3204_write(11, 0x86); // Power up NDAC and set NDAC value to 3 (comments below differ from the values)

aic3204_write(12, 0x88); // Power up MDAC and set MDAC value to 8 (comments below differ from the values)

aic3204_write(18, 0x88); // Power up NADC and set NADC value to 8 (comments below differ from the values)

aic3204_write(19, 0x86); // Power up MADC and set MADC value to 6 (comments below differ from the values)

aic3204_write(60, 0x19); // Power up PRB_P25 for beep generator Selects the ADC (recording) signal processing block

aic3204_write(61, 0x01); // ADC Singal Processing Block PRB_R1 ADC Signal Processing Block Control Register

aic3204_write(48, 0xff); // Power up MADC and set MADC value to 6 (comments below differ from the values)

aic3204_write(49, 0xff); // Power up PRB_P25 for beep generator