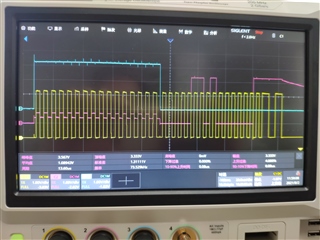

和这个贴子描述一样,时钟刚输出13个,数据已经输出完了,少了后面几位数据,请高手分析解决,万分感谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

看datasheet 中9.4.1.1 3-Wire CS Mode最后一句话:

DOUT goes to 3-state after the 16th SCLK falling edge or when CONVST goes high, whichever occurs first

这两种情况可以使DOUT输出三态,16个SCLK 是够了,但是看到CONVST信号线上有干扰,那么很可能是CONVST上的干扰造成了DOUT输出三态。可以在CONVST信号线串几十欧姆电阻和对地并联电阻,看CONVST信号线上的干扰是否可以滤除?

还有一种情况是,最后三位是不是本来就是高电平,然后受到了SCLK时钟的串扰;可以看下输出数据0时,是不是最后三位也是这种状态?

你好!你说的方法有一定效果。

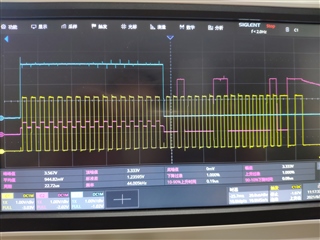

我现在在CONVST信号线串270欧或更大电阻,或者对地接几十到几百PF电容,有一定效果,但还是没解决问题,具体是这样:

当加的电阻或电容比较大时,比如电阻470欧或电容100PF以上,数据输出会达到18位,也就是会多出两位数据,随后才会变回3态,

当加的电阻电阻或电容比较小时,比如加120欧或10PF电容,数据输出会少于16位,也就是会少出1-2位数据,随后才会变回3态,

我反复调了电阻电容值大小,结果数据位不是多了就是少了,怎么芯片会对这个这么敏感吗?我现在搞蒙了,请高手指点迷津!!!

图片见下图:

后面两个黄色宽脉冲是第17、18号脉冲,是为了让芯片数据输出干净额外多发的脉冲!!!!!!!!!!!!!!!!!!!!!

您测得所有波形都是在ADS8866的输入管脚处测得的吗?我奇怪为什么会输出18bits数据,不知道是不是由于CONVST信号上的RC延迟了它的下降沿造成的

您用示波器实测VREF电压是稳定的吗?VREF管脚处有10uF或以上的电容吗?您是怎样产生的VREF?我担心ADC的VREF电压降过大,可能会导致后几位损坏