您好,

我使用FPGA将24 路并行像素信号 传送给dlpc3479进行处理显示。

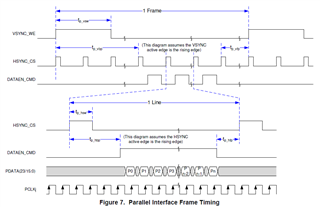

请问 1. DATAEN_CMD/VSYNC_WE/HSYNC_CS/PCLK 这四路频率信号都是要我的FPGA产生,然后传给dlpc3479吗?

2. DATAEN_CMD 信号的作用是什么?

3. 像素时钟PCLK 代表的是在时钟的每个上升沿有一个像素点传输吗?

4. 像素时钟(PCLK)和 VSYNC_WE、HSYNC_CS 三者的关系是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

我使用FPGA将24 路并行像素信号 传送给dlpc3479进行处理显示。

请问 1. DATAEN_CMD/VSYNC_WE/HSYNC_CS/PCLK 这四路频率信号都是要我的FPGA产生,然后传给dlpc3479吗?

2. DATAEN_CMD 信号的作用是什么?

3. 像素时钟PCLK 代表的是在时钟的每个上升沿有一个像素点传输吗?

4. 像素时钟(PCLK)和 VSYNC_WE、HSYNC_CS 三者的关系是什么?

你好:

1,是的。

2,Data valid输入脚,即信号有效脚,一般接前端的Data Enable。可以参考DLPC3479的reference design:https://www.ti.com/tool/TIDA-080005#technicaldocuments

3,是的。

4,Pclk是视频信号的像素时钟,和Vs,Hs的关系具体可以参考相关视频timing标准定义如VESA。1080p@60Hz 的Pclk一般在148.5Mhz。