Other Parts Discussed in Thread: DLP7000, DLPLCR70EVM, DLP9500

你好!

1. DLPC410的datasheet写明1bit的刷新率可以达到32KHz,在目前的EVM上可以实现吗?

2. 如果第1个问题回答是否定的,那么如何设计才能达到高刷新率?

3.EVM上的内存是DDR2,如果提升为DDR3或者DDR4是否可以提高刷新率?

谢谢!

sunny

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

你好!

1. DLPC410的datasheet写明1bit的刷新率可以达到32KHz,在目前的EVM上可以实现吗?

2. 如果第1个问题回答是否定的,那么如何设计才能达到高刷新率?

3.EVM上的内存是DDR2,如果提升为DDR3或者DDR4是否可以提高刷新率?

谢谢!

sunny

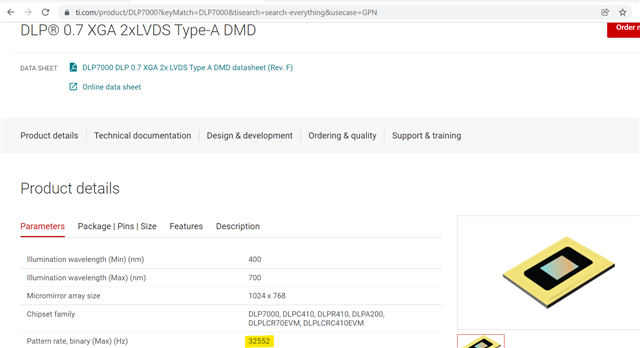

你好。DLP7000可以支持最高32KHz的pattern rate,如下图。对应的EVM是DLPLCR70EVM:https://www.ti.com/tool/DLPLCR70EVM

DDR2和这个pattern rate没有关系。32KHz是由DMD的load time决定的。

你好。我个人认为,pattern都是缓存在DDR2的。即使DMD本身可以支持高刷新率,但是数据都是要从DDR2读出来传给它,这个地方的带宽是否足够满足DMD本身的高刷新率?

可以满足要求的。一般1bit的pattern都是单行或单列图像组成,这样图片本身的带宽并不高。DDR memory的型号通常由APPSFPGA类型来定,而pattern rate一般是DMD和DLPC这些chipset硬件以及工作模式等决定。

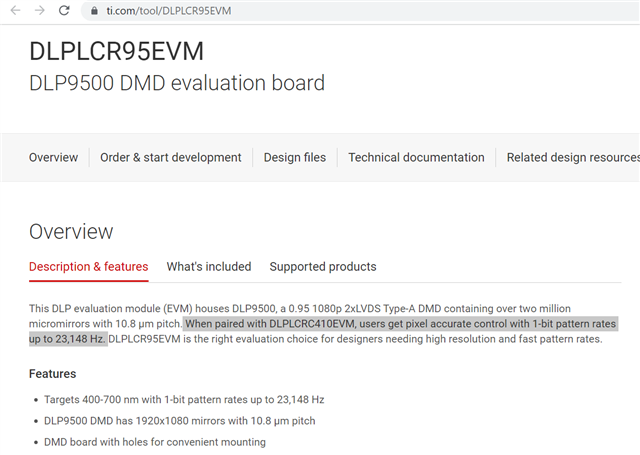

MengAo,你好。我换个问法问吧。DLP9500的1bit刷新率最高是23148Hz。以目前的410EVM是支撑不到这么高的刷新率。那么我们需要修改哪些地方可以尽可能接近目标,比如是更换更高芯能的FPGA,又或是改成DDR3,又或是其它方面的修改提升?谢谢。

DLPLCRC410搭配DLP9500可以做到1bit pattern rate 23148HZ。如果要更改FPGA方案和DDR型号,这个需要你自行研究或是咨询Xilinx

你俩好像没有说在一个点上,两人说的都对,但是差异点主要在于显示图形数量上。

MengAo 所说的,DMD刷新速率和DDR没有关系,是出于少量pattern直接存储在APPSFPGA内部,load时间很短,直接可以以32KHz来显示。

User5911856认为,DMD显示图形需要从DDR上去load,这个load时间太长,会导致DMD显示速度也下降,这个说法也没错。

工程上通常有2种做法:

1、集成高速大容量flash,预先将pattern存储在flash上,以达到高速显示的目的。

2、内置高性能图形芯片,直接给矢量图,通过图形运算芯片直接将矢量图实时运算,再通过高速接口传输给DMD,已达到高速显示的目的。

以下推荐一种现成的方案,集成了高速大容量flash,最高可以20Khz显示,如果有需求,可以联系。