Other Parts Discussed in Thread: TMDSCNCD28388D

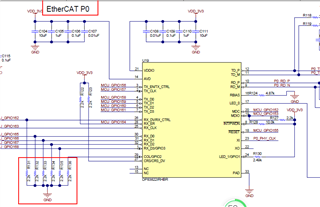

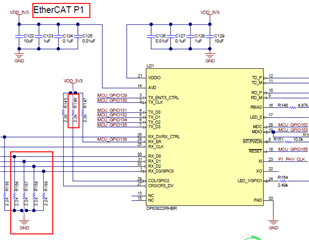

TMDSCNCD28388D的EtherCAT 设计中使用了DP83822I,对于PHY地址的疑问如下

上图为TMDSCNCD28388D设计EtherCAT Port0部分设计,按照PHY手册,上电后,PHY的地址由RX[3:0]+COL决定,COL为LSB。

其中RX[3:0]为PHY芯片内部有下拉的管脚,COL为PHY芯片内部有上拉的管脚。

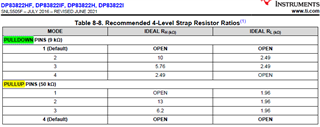

以上管脚的外部上下拉电阻及模式对应关系为:

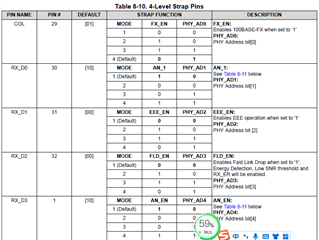

PHY芯片地址与管脚模式之间的关系为:

按照设计,EtherCAT Port0 PHY的地址应设置为0x0。

问题1.对于内部有下拉的RX[3:0]四个管脚,根据表8-8及8-10的规则,是不是悬空也是可以的,在表8-8中,对于内部有下拉的管脚,并没有RH = OPEN,RL = 2.2K的选择项

对于内部有上拉的COL管脚,按照表8-10,应该设置为MODE 1,即将PHY的地址LSB设置为0,按照表8-8,COL管脚的RH = OPEN , RL = 1.96K。

问题2.COL的下拉电阻是不是应该为1.96K,而不是合计中的2.2K

上图为Port1的设计,RX[3:0]与Port0中的设计疑问相同。

问题3.需要设计为地址为1的PHY,对于COL,按照表8-8及8-10,应该是悬空就可以吧即R146不焊接,模式选择中对于内部有上拉的管脚,没有RH = 2.2K,RL = OPEN的选择。