TI AFE:

您好!

我司的产品使用了贵司的MLVDS芯片SN65MLVD040,不同于LVDS信号(在同一对差分信号的接收器端并联端接一个100Ω的电阻),MLVDS信号要求在同一对差分信号的最远两端分别并联端接一个100Ω的电阻,两个100Ω的电阻并联后为50Ω,那么在设计PCB时,MLVDS差分信号线的差分特性阻抗应该是按照50Ω进行设计还是100Ω?

由于我司在第一版硬件设计中,并没有做阻抗设计和控制,导致信号反射严重,所以急需进行硬件改版设计,在线急等,谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

TI AFE:

您好!

我司的产品使用了贵司的MLVDS芯片SN65MLVD040,不同于LVDS信号(在同一对差分信号的接收器端并联端接一个100Ω的电阻),MLVDS信号要求在同一对差分信号的最远两端分别并联端接一个100Ω的电阻,两个100Ω的电阻并联后为50Ω,那么在设计PCB时,MLVDS差分信号线的差分特性阻抗应该是按照50Ω进行设计还是100Ω?

由于我司在第一版硬件设计中,并没有做阻抗设计和控制,导致信号反射严重,所以急需进行硬件改版设计,在线急等,谢谢!

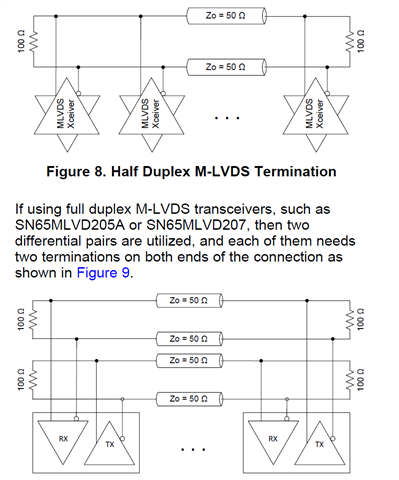

您好,由于LVDS不支持multipoint多点连接, 所以只是在靠近接收端接100ohm匹配电阻就好。

而MLVDS支持多点应用,就和RS485一样,在两个最远端需要同时端接100ohm匹配电阻。

那对于差分线来说,其实还是走的100ohm阻抗,对于单端信号来说,走的是50ohm阻抗,如下: