我用的是DP83848K芯片,用FPGA的程序配置PHY相关寄存器;目前出现问题如下:

1、LED模式为模式2,未配置任何寄存器,上电后连接两块板子后,显示自协商通信完成;但link灯是闪的,speed灯是灭的,此时对应寄存器应该是10Mbps模式,但我读到的是100Mbps的工作速率;

2、写寄存器值写不进去,写入的值与读出的值不一致;

3、是否有FPGA驱动此款PHY芯片的例程可供参考?或是否有配置此款PHY芯片寄存器的步骤说明?

谢谢!

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好,

1、您可以附上原理图吗?

2、这里建议您看下读写波形,看是否为期望的波形时序

3、下面链接的 Linux driver 希望对您有帮助:

https://git.kernel.org/pub/scm/linux/kernel/git/torvalds/linux.git/tree/drivers/net/phy/dp83848.c

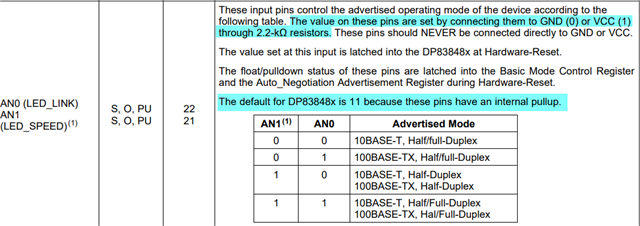

1、看到您原理图中 AN0、AN1都下拉至地了,您是需要配置在AN0=0、AN1=0模式下吗?这样的话,需要接下拉电阻2.2K,而不是2K,因为其内部集成了上拉电阻,如果下拉电阻值选择不合适,会影响模式的选择。

如果AN0=0、AN1=0,那么将工作在10BASE-T,speed灯是灭的,这是正常的,不太确定是不是下拉电阻值使用的不合适造成的 您读到的是100Mbps的工作速率?建议您将下拉电阻值更改为2.2K,再看工作速率是否还为100Mbps?

2、是的,具体看datasheet时序图 Figure 6-2和Figure 6-3

3、这个问题是什么意思,可以详细说明吗?