主题中讨论的其他器件: OPA838、 THS4561、 THS4551、 THP210、 THS4541、 ADC3683

您好!

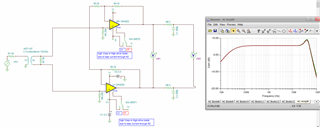

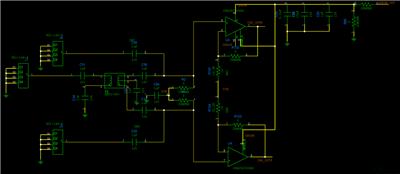

我们为18位65MSPS SAR ADC 构建了一个 EVM、为此、我们在以下电路配置中使用 ADT1-6T+变压器和 OPA2625来驱动 ADC 的差分输入。

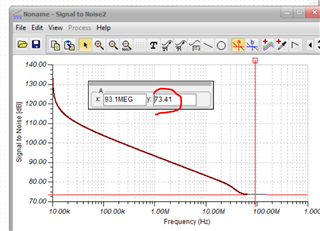

ADC 的理论本底噪声(SNR)约为-85dBFS。 我们希望输入驱动电路具有更好的噪声性能、以便它不会限制整个系统的本底噪声。 它还必须具有良好的失真性能(我们主要关注的是 HD2和 HD3)。 ADC 输入必须为3.2V 峰间值。 根据这些限制、选择 OPA2625时考虑了数据表中指定的噪声、HD2和 HD3值。 运算放大器在高驱动模式下运行。

在上面的电路中、反馈电阻器 R102和 R103设置为3K 欧姆、电阻器 R101、R104设置为1K 欧姆、以获得4的增益。 该设置正在以200kHz 的输入频率和22MSPS 至50MSPS 的 ADC 采样频率进行测试。 下面是我们尝试过的许多其他配置:

-改变增益(我们希望保持增益更大、以避免必须提供较大的射频输入振幅。 此外、当运算放大器的输入需要高摆幅以补偿较低增益时、我们会看到性能较差)

-保持增益不变,但将电阻器的绝对值从低值更改为高值

-改变电源轨值(与数据表中提到的相反、我们在 Vs+= 3V 和 Vs-= 0V 的电源下获得更好的性能)

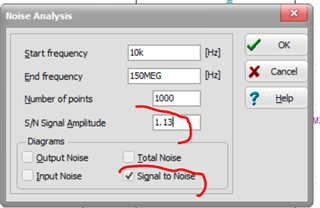

-在运算放大器的输出端添加了一个低通 RC 滤波器(R = 5欧姆、C = 200pF 接地)、以限制噪声带宽

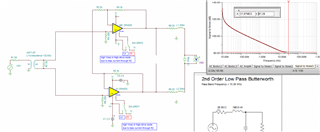

-添加了一个与反馈电阻器并联的60pF 电容器(限制了放大器的增益必须在 RC 滤波器的截止频率之前滚降)、以便最大限度地减小放大器输出上的负载。 我们的想法是、与4K 欧姆电阻器相比、电容器开始主导反馈的速度越快、其对输出端热噪声的影响就越早消失。

不幸的是,上述案件都没有取得丰硕成果。 SNR 不超过-72dBFs、在最佳情况下、HD2和 HD3约为-75dBc。 更糟糕的是、完全移除运算放大器并仅使用变压器驱动 ADC 输入可将我们的结果提高到-77dBF、HD2为-105dBc、HD3为-90dbC。 但是、最终在输入路径中使用变压器是不可行的、因为我们也希望提供直流采样能力。

请建议您对电路进行任何更改、以便我们能够实现比现在更好的性能。 在这种情况下、也可以考虑更改运算放大器、请提供合适的建议(我确实收到过一些文章、建议将电流反馈运算放大器作为比电压反馈更好的 ADC 驱动器。 如果是,请详细说明理由。)