了解有关数据传输后 DMA 引擎状态的问题。

具体情况如下:

在 SPI 模式下。

SPI2 TX 主时钟和 SIMO 连接到 SPI3 RX 从器件。

时钟为15Mbps: VClk /5

SP2 TX 使用通道3。

SP3 RX 使用通道2。

两个 FIFO 都被旁路。

没有其它 DMA 处于活动状态。

SPI 字符为16位、不使用 CS。

SPI3 RX 使 DMA 为接收数据做好准备。

SPI2 TX 被使能、它将请求发送到 DMA 控制器。

两个系统都使用 BTC 中断。

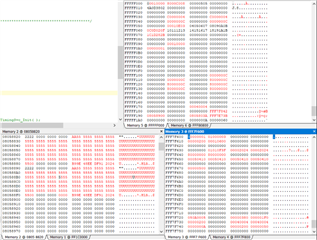

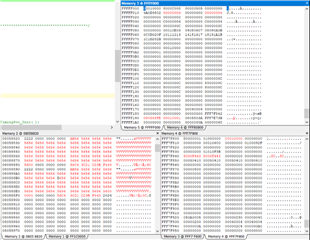

第一次完全传输有效:两个 BTC 中断都出现、并且存储器中没有数据丢失。

在这种情况下、为了验证目的、我在帧的末尾还有一个 CRC64。

Q1)第一个问题是、尽管 DMA 传输已完全完成、为什么挂起寄存器指示 TX 通道上的一个挂起请求?

Q2)为什么通道14和15显示待处理的请求、但尚未启用并参与此传输?

Q3)为什么 DMA 通道2 (SPI3 RX)有效控制数据包显示的是计数2而不是1?

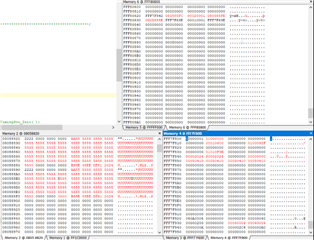

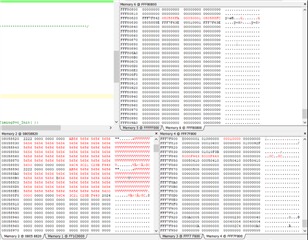

这是以下第二个传输结果。

RX BTC 缺失。 传输完成。 RX 结果缓冲区显示缺少0x5656条目。

Q4)为什么第一个传输始终有效、而第二个类似的传输在传输中的同一个位置缺少字符?

-此处的示波器显示没有丢失的数据,并且发送了所有数据。 仅缺少一个字符、导致 RX BTC 中断丢失。

-不会在线路上产生噪声、所有缺失字符之前和之后的数据都是可以的。

我准备回答其他设置问题、但请记住、尽管 DMA 状态很奇怪、它仍以7.5Mbps 运行。