您好、

一年以来、我们使用 DMA 模块来触发2个 ADC 通道。 到目前为止、它的效果非常好。

两个通道都位于 ADC 组2中、并由组转换触发。

我们在组转换中增加了2个 ADC 通道。 几个小时后、前2个 ADC 通道的数据不正确。 我们遇到了由该数据导致的错误。

当我们添加了一个通过 CAN 发送的附加调试变量时、遗憾的是我们无法使用调试变量重现错误行为。

我们的 ADC 通道:

| 说明 | ADC 通道 | ADC 端口 | DMA 通道 | 缓冲器大小 | 缓冲区类型 |

| ADC_First1 | 18 | A | 3. | 100 | uint16 |

| ADC_First2 | 20. | A | 4. | 100 | uint16 |

| ADC_Additional1 | 4. | A | 1 | 30 | uint16 |

| ADC_Additional2 | 12. | A | 2. | 30 | uint16 |

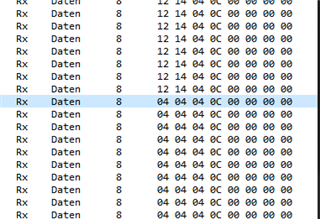

控制寄存器的配置:ADG2DMACR

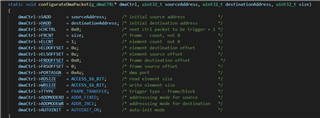

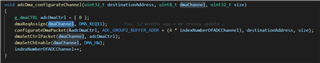

下面是我们的配置和函数、我们将如何配置 DMA 数据包。

_________________________________________

我们有两个问题:

1) 1)当我们验证数据并在之后再次激活数据时、停用会产生什么影响? 在添加额外的 ADC 通道之前、我们在验证缓冲区中的数据之前停用了 DMA 通道。

dmaREG->HWCHENAS =(uint32) 1U <<通道;

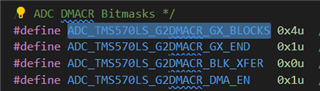

2) 2) ADC_TMS570LS_G2DMACR_GX_Blocks 的影响是什么?

我们有一个软件、其中 ADC_TMS570LS_G2DMACR_GX_Blocks 设置为2。 在现场测试中、尽管我们有4个 ADC 通道、该通道将由 DMA 触发、但该配置更稳定。

此致、

Thorben