我已经实现了一个基数2和基数4解码算法、该算法在具有 ARM Cortex-R4F 的 TI RM46L852芯片上运行裸机。 我还实施了和的优化版本、对于基数4、我得到的加速几乎与我预测的完全相同、但对于基数2、我实际上有一个性能回归。

然后、我在汇编语言中实现了基数2和优化基数2设计、并使用 PMU 性能计数器来查找回归的原因。 我的优化主要是在输入值为0时跳过30条指令。 分支预测器可以很好地完成工作、正确预测所有分支中约96%的分支、其余4%不会考虑性能回归。 除了在优化设计中指令缓冲器停转高25倍之外、每个其他 PMU 计数器值大致相同。

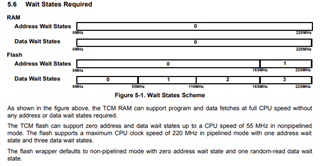

查看文档、它只说这可能是由于指令缓存缺失所致、但该芯片没有任何 I$或 D$、并且具有单周期片上 RAM。 我找不到任何其他说明指令缓冲器到底是什么以及可能是什么原因的文档。 有人有解释吗?