主题中讨论的其他器件:TIDA-00778、 LM3S8971、 UCC27714、 LM94022、 TMS320F28027

大家好、

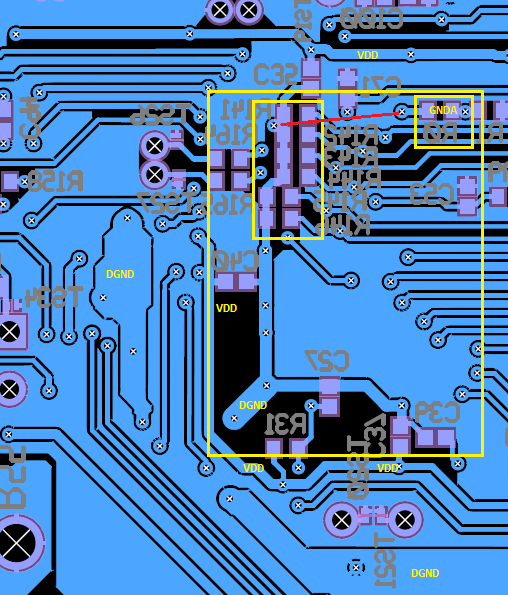

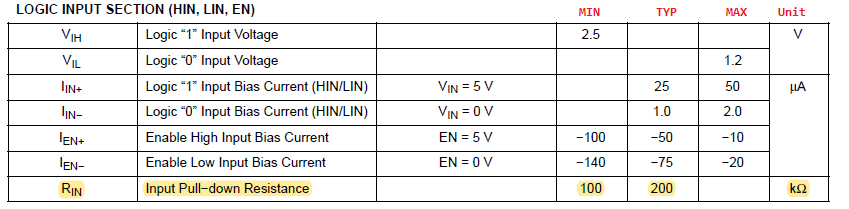

我曾考虑过 ADC SNR 的影响、即在连接到数字接地的 MCU 引脚附近的20K 下拉电阻、6个 PWM 输出。 PWM 输出迹线会导致模拟驱动器100k 内部下拉电阻2英寸远。 并联电阻20K 可将100k 的内部输入下拉电阻降低至大约16k 的总电阻。 这种向模拟栅极驱动器添加10-20k 下拉电阻的做法似乎是接地高频 PWM 的一个重要方面。

这对 ADC 采样的 SNR 和稳定性有何影响? TI 工程师 TIDA-00778似乎添加了10K 下拉电阻器、这可能是由于 POR 引脚悬空、是否猜测? 通常情况下、栅极驱动器在输入端具有100k 至200k 的内部下拉电阻、因此为什么添加任何并联电阻并抑制 GPIO 电流压摆? TI 是否进行过任何研究来展示 PWM 信号注入 MCU 接地会或将会如何导致 ADC 问题?

在20Khz 时、大约167µV 50µs μ A 的电流倾至数字接地 x 6个 GPIO 引脚或每 μ A 1.002mA。 如果低阻抗电阻未直接放置在 MCU 封装引脚附近、GPIO 引脚是否在 POR 期间出现毛刺脉冲或更改状态?

添加任何并联电阻下拉的一个合理的原因是、如果 GPIO 毛刺应该随机发生、那么是否降低布线阻抗? LM3S8971电机 RDK 上也存在向 GPIO 添加20k 下拉电阻的这种做法、但仅在栅极驱动器输入附近的低侧也有400k 内部下拉电阻。