主题中讨论的其他器件:MSP432E401Y

尊敬的团队:

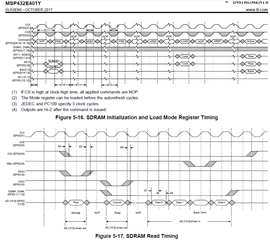

在我们的 MSP432E401Y 定制设计 中、SDRAM 与 EPI 总线接口相连。 但与 SDK 的给定 SDRAM 示例代码相比、引脚发生了单次变化。

变化如下:

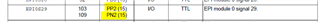

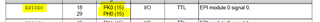

EPIOS0的以下 GPIO 示例代码

ROM_GPIOPinConfigure (GPIO_PH0_EPI0S0);

我们的定制设计包含 用于 EPIOS0的 GPIO

我所做的更改如下:

ROM_GPIOPinConfigure (GPIO_PK0_EPI0S0);

MAP_GPIOPinTypeEPI (GPIO_PORTK_base、(GPIO_PIN_5|GPIO_PIN_0));

3.需要进行哪些更改才能使 SDRAM 正常工作。

此致、

Naga Narasimha Rao