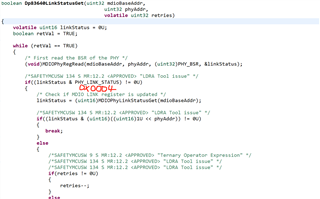

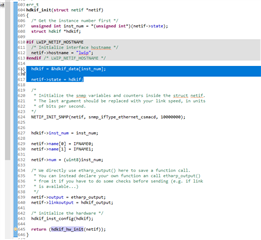

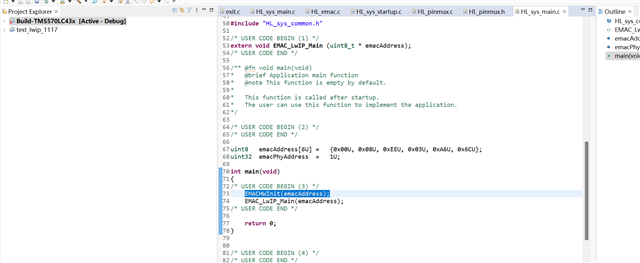

这是我的代码调试屏幕截图。 当运行函数以获取 PHY ID 时、USERACCESS0寄存器中的数据始终保持为0。 我无法确定原因。

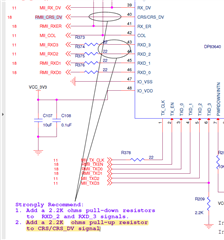

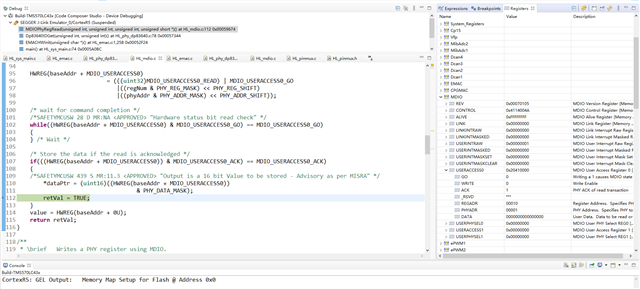

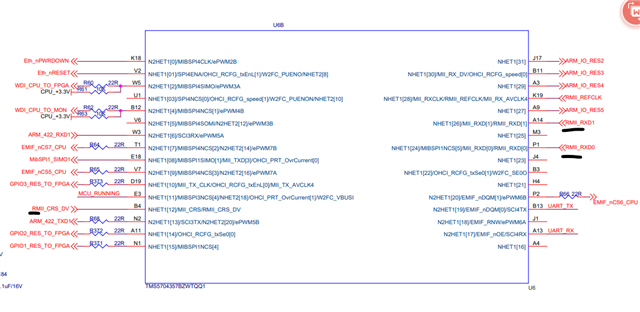

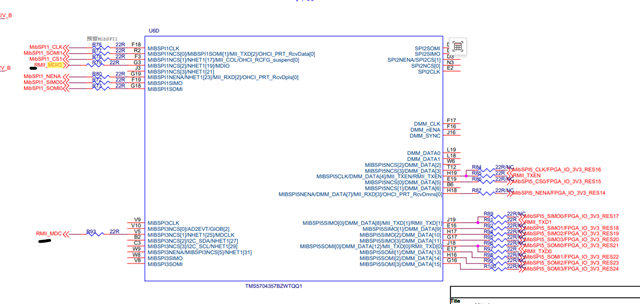

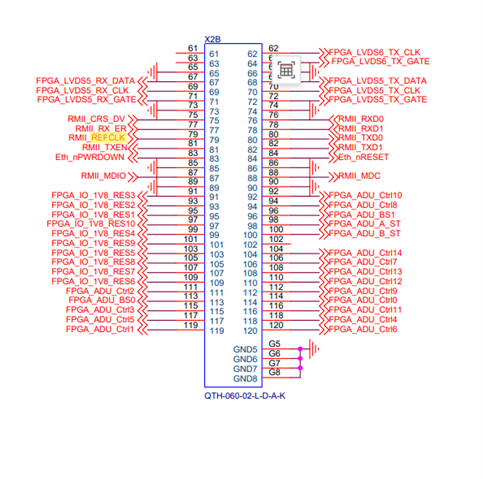

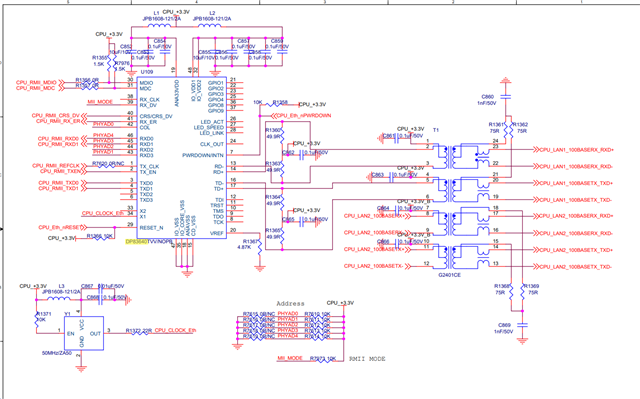

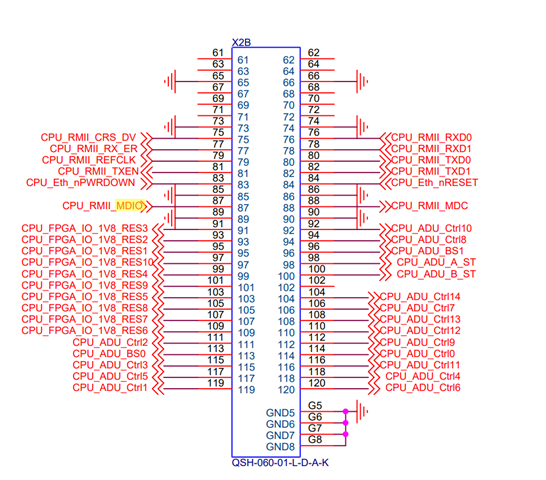

这是我的硬件原理图。 TMS570LC4357芯片通过连接器连接到 PHY 芯片。 请帮助我检查硬件是否有任何错误。

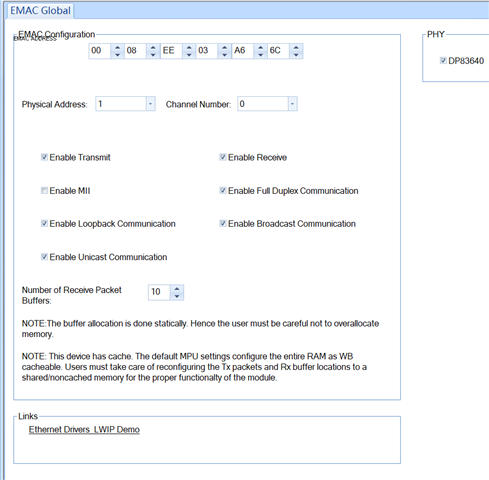

我的代码使用的是官方示例项目 v00.04..00。 我EMACHWInit(emacAddress);在main函数中添加了代码、但无法成功初始化、并且无法获取 PHYID。

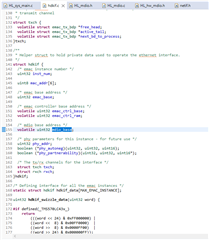

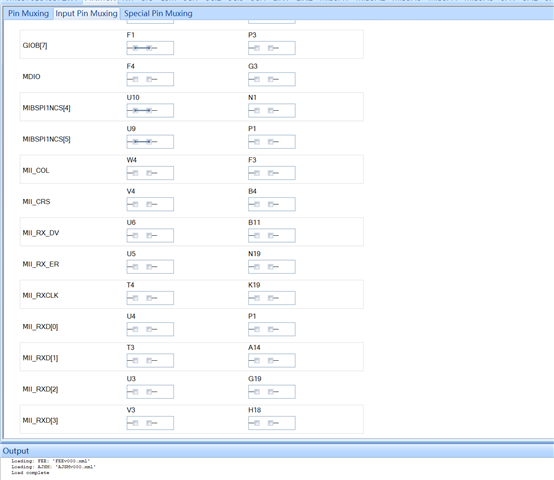

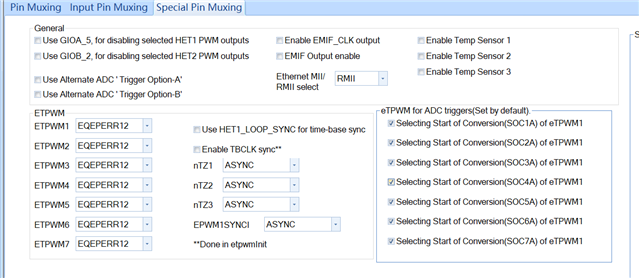

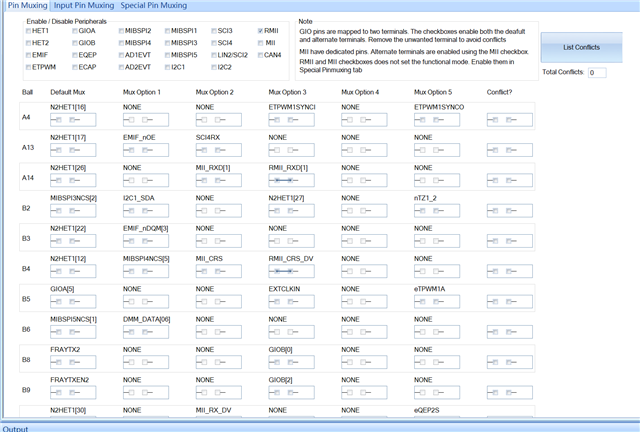

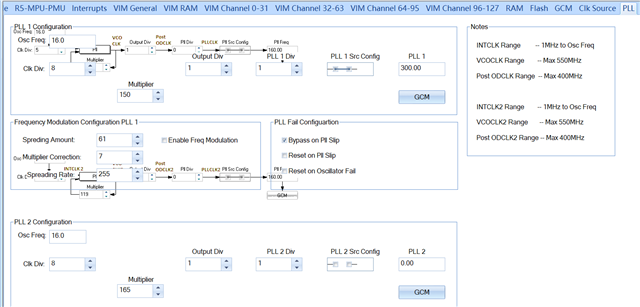

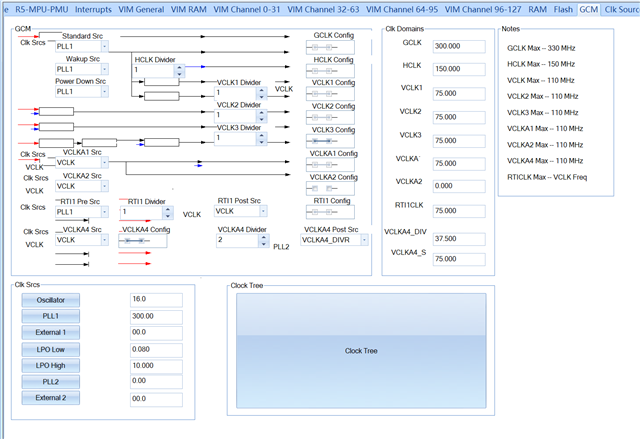

在上述项目中、使用 HCG 所做的修改如下:

英文译本、我看到 PHY 芯片的 X1引脚的频率是50MHz、MDIO 引脚的频率是1MHz、用一个示波器。'